#### August 1997

### Features

- 16-Bit/14-Bit Binary Three-State Latched Outputs Plus Polarity and Overrange

- Ideally Suited for Interface to UARTs and Microprocessors

- · Conversion on Demand or Continuously

- Guaranteed Zero Reading for 0V Input

- True Polarity at Zero Count for Precise Null Detection

- Single Reference Voltage for True Ratiometric

Operation

- Onboard Clock and Reference

- Auto-Zero, Auto-Polarity

- Accuracy Guaranteed to 1 Count

- All Outputs TTL Compatible

- ±4V Analog Input Range

- Status Signal Available for External Sync, A/Z in Preamp, Etc.

# ICL8052/ICL7104, ICL8068/ICL7104

14-Bit/16-Bit, Microprocessor-Compatible, 2-Chip, A/D Converter

# Description

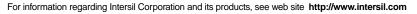

The ICL7104, combined with the ICL8052 or ICL8068, forms a member of Intersil' high performance A/D converter family. The ICL7104-16, performs the analog switching and digital function for a 16-bit binary A/D converter, with full three-state output, UART handshake capability, and other outputs for easy interfacing. The ICL7014-14 is a 14-bit version. The analog section, as with all Intersil' integrating converters, provides fully precise Auto-Zero, Auto-Polarity (including ±0 null indication), single reference operation, very high input impedance, true input integration over a constant period for maximum EMI rejection, fully rationmetric operation, over-range indication, and a medium quality built-in reference. The chip pair also offers optional input buffer gain for high sensitivity applications, a built-in clock oscillator, and output signals for providing an external Auto-Zero capability in preconditioning circuitry, synchronizing external multiplexers, etc.

# **Ordering Information**

| PART NUMBER   | TEMP.<br>RANGE ( <sup>o</sup> C) | PACKAGE      | PKG.<br>NO. |

|---------------|----------------------------------|--------------|-------------|

| ICL8052CPD    | 0 to 70                          | 14 Ld PDIP   | E14.3       |

| ICL8052CDD    | 0 to 70                          | 14 Ld CERDIP | F14.3       |

| ICL8052ACPD   | 0 to 70                          | 14 Ld PDIP   | E14.3       |

| ICL8052ACDD   | 0 to 70                          | 14 Ld CERDIP | F14.3       |

| ICL8068CDD    | 0 to 70                          | 14 Ld CERDIP | F14.3       |

| ICL8068ACDD   | 0 to 70                          | 14 Ld CERDIP | F14.3       |

| ICL8068ACJD   | 0 to 70                          | 14 Ld CERDIP | F14.3       |

| ICL7104-14CPL | 0 to 70                          | 40 Ld PDIP   | E40.6       |

| ICL7104-16CPL | 0 to 70                          | 40 Ld PDIP   | E40.6       |

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. 1-888-INTERSIL or 321-724-7143 | Copyright © Intersil Corporation 1999

# Pin Descriptions

| PIN NO. | SYMBOL           | OPTION     | DESCRIPTION                                                                                                                                                                                                                    |

|---------|------------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | V++              |            | Positive Supply Voltage: Nominally +15V.                                                                                                                                                                                       |

| 2       | GND              |            | Digital Ground: 0V, ground return.                                                                                                                                                                                             |

| 3       | STTS             |            | Status Output: HI during integrate and deintegrate until data is latched. LO when analog section is in auto-zero configuration.                                                                                                |

| 4       | POL              |            | Polarity: Three-state output. HI for positive input.                                                                                                                                                                           |

| 5       | OR               |            | Over Range: Three-state output.                                                                                                                                                                                                |

| 6       | BIT 16<br>BIT 14 | -16<br>-14 | Most Significant Bit (MSB).                                                                                                                                                                                                    |

| 7       | BIT 15<br>BIT 13 | -16<br>-14 | DATA Bits: Three-state outputs. See Table 3 for format of ENABLES and bytes. HIGH = true.                                                                                                                                      |

| 8       | BIT 14<br>BIT 12 | -16<br>-14 |                                                                                                                                                                                                                                |

| 9       | BIT 13<br>BIT 11 | -16<br>-14 |                                                                                                                                                                                                                                |

| 10      | BIT 12<br>BIT 10 | -16<br>-14 |                                                                                                                                                                                                                                |

| 11      | BIT 11<br>BIT 9  | -16<br>-14 |                                                                                                                                                                                                                                |

| 12      | BIT 10<br>NC     | -16<br>-14 |                                                                                                                                                                                                                                |

| 13      | BIT 9<br>NC      | -16<br>-14 |                                                                                                                                                                                                                                |

| 14      | BIT 8            |            |                                                                                                                                                                                                                                |

| 15      | BIT 7            |            |                                                                                                                                                                                                                                |

| 16      | BIT 6            |            |                                                                                                                                                                                                                                |

| 17      | BIT 5            |            |                                                                                                                                                                                                                                |

| 18      | BIT 4            |            |                                                                                                                                                                                                                                |

| 19      | BIT 3            |            |                                                                                                                                                                                                                                |

| 20      | BIT 2            |            |                                                                                                                                                                                                                                |

| 21      | BIT 1            |            | Least Significant Bit (LSB).                                                                                                                                                                                                   |

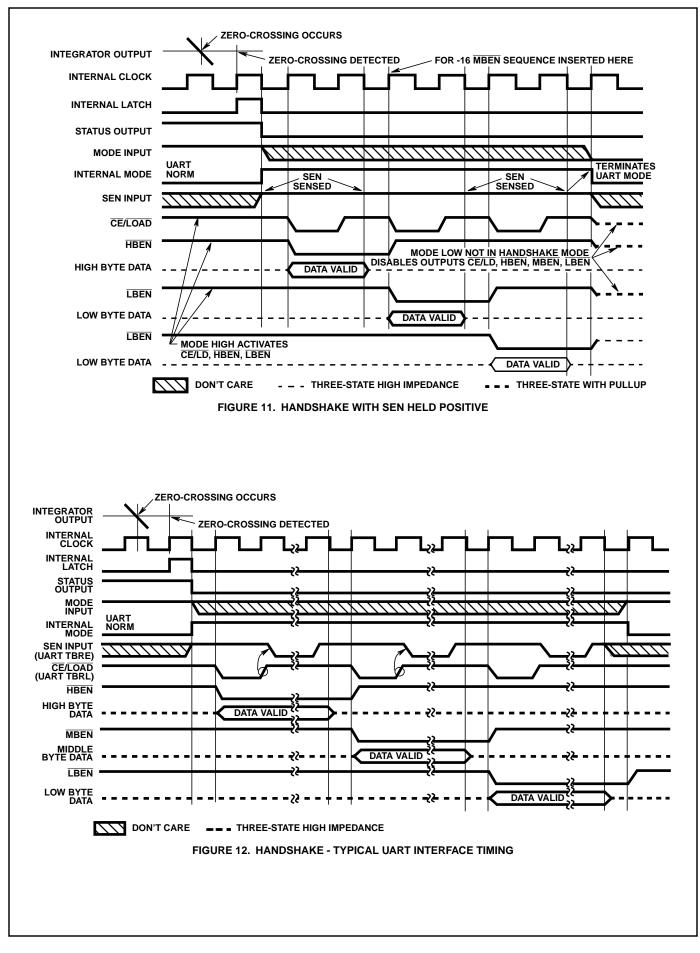

| 22      | LBEN             |            | LOW BYTE ENABLE: If not in handshake mode (see pin 27) when LO (with CE/LD, pin 30) activates low-order byte outputs, BITS 1-8. When in handshake mode (see pin 27), serves as a low byte flag output. See Figures 11, 12, 13. |

| 23      | MBEN             | -16        | MID BYTE ENABLE: Activates Bits 9-16, see LBEN (pin 22)                                                                                                                                                                        |

|         | HBEN             | -14        | HIGH BYTE ENABLE: Activates Bits 9-14, POL, OR, see LBEN (pin 22)                                                                                                                                                              |

| 24      | HBEN             | -16        | HIGH BYTE ENABLE: Activates POL, OR, see LBEN (pin 22).                                                                                                                                                                        |

|         | CLOCK3           | -14        | RC oscillator pin: Can be used as clock output.                                                                                                                                                                                |

| PIN NO. | SYMBOL           | OPTION | DESCRIPTION                                                                                                                                                                                                                                                                                                                                    |

|---------|------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

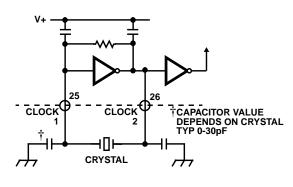

| 25      | CLOCK 1          |        | Clock Input: External clock or ocsillator.                                                                                                                                                                                                                                                                                                     |

| 26      | CLOCK 2          |        | Clock Output: Crystal or RC oscillator.                                                                                                                                                                                                                                                                                                        |

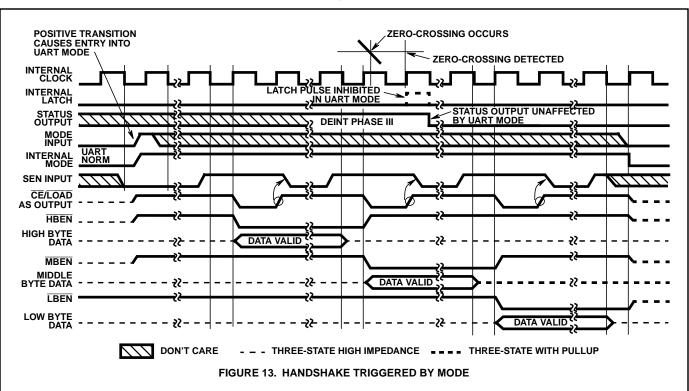

| 27      | MODE             |        | INPUT LO: Direct output mode where CE/LD, HBEN, MBEN and LBEN act as inputs directly controlling byte outputs. If pulsed HI causes immediate entry into handshake mode (see Figure 13). If HI, enables CE/LD, HBEN, MBEN and LBEN as outputs. Handshake mode will be entered and data output as in Figures 11 and 12 at conversion completion. |

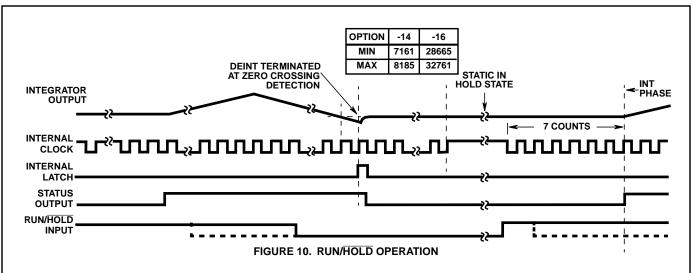

| 28      | R/H              |        | RUN/HOLD: Input HI conversions continuously performed every 2 <sup>17</sup> (-16) or 2 <sup>15</sup> (-14) clock pulses. Input LO conversion in progress completed, converter will stop in Auto-Zero 7 counts before input integrate.                                                                                                          |

| 29      | SEN              |        | SEND ENABLE: Input controls timing of byte transmission in handshake mode. HI indicates 'send'.                                                                                                                                                                                                                                                |

| 30      | CE/LD            |        | CHIP ENABLE/ LOAD: WITH MODE (PIN 27) LO, CE/LD serves as a master output enable when HI, the bit outputs and POL, OR are disabled. With MODE HI, pin serves as a LOAD strobe (-ve going) used in handshake mode. See Figures 11 and 12.                                                                                                       |

| 31      | V+               |        | Positive Logic Supply Voltage: Nominally +5V.                                                                                                                                                                                                                                                                                                  |

| 32      | AN I/P           |        | Analog Input: High Side.                                                                                                                                                                                                                                                                                                                       |

| 33      | BUF IN           |        | Buffer Input: Buffer Analog to analog chip (ICL8052 or ICL8086).                                                                                                                                                                                                                                                                               |

| 34      | REFCAP2          |        | Reference Capacitor: Negative Side.                                                                                                                                                                                                                                                                                                            |

| 35      | AN. GND          |        | Analog Ground: Input low side and reference low side.                                                                                                                                                                                                                                                                                          |

| 36      | A-Z              |        | Auto-Zero node.                                                                                                                                                                                                                                                                                                                                |

| 37      | V <sub>REF</sub> |        | Voltage Reference: Input (positive side).                                                                                                                                                                                                                                                                                                      |

| 38      | REFCAP1          |        | Reference Capacitor: Positive side.                                                                                                                                                                                                                                                                                                            |

| 39      | COMP-IN          |        | Comparator Input: From 8052/8068.                                                                                                                                                                                                                                                                                                              |

| 40      | V-               |        | Negative Supply Voltage: Nominally -15V.                                                                                                                                                                                                                                                                                                       |

#### **Absolute Maximum Ratings**

#### ICL8052, ICL8068

| Supply Voltage ±18V<br>Differential Input Voltage             |

|---------------------------------------------------------------|

| (8068) ±30V                                                   |

|                                                               |

| (8052)                                                        |

| Input Voltage (Note 2) ±15V                                   |

| Output Short Circuit Duration All Outputs (Note 3) Indefinite |

| ICL7104                                                       |

| V+ Supply (GND to V+) 12V                                     |

| V++ to V                                                      |

| Positive Supply Voltage (GND to V++) 17V                      |

| Negative Supply Voltage (GND to V-)                           |

| Analog Input Voltage (Pins 32 - 39)(Note 4) V++ to V-         |

| Digital Input Voltage                                         |

| (Pins 2 - 30) (Note 5) (GND - 0.3V) to (V+ + 0.3V)            |

| Thermal Resistance (Typical, Note 1)    | θ <sub>JA</sub> ( <sup>o</sup> C/W) | θ <sub>JC</sub> ( <sup>o</sup> C/W)    |

|-----------------------------------------|-------------------------------------|----------------------------------------|

| 14 Ld PDIP Package                      | 100                                 | N/A                                    |

| 40 Ld PDIP Package                      | 60                                  | N/A                                    |

| 14 Ld CERDIP Package                    | 75                                  | 20                                     |

| Maximum Junction Temperature (Ceramic F | Package)                            | 175 <sup>0</sup> C                     |

| Maximum Junction Temperature (Plastic F | Package)                            | 150 <sup>0</sup> C                     |

| Maximum Storage Temperature Range       | 65                                  | 5 <sup>o</sup> C to 150 <sup>o</sup> C |

| Maximum Lead Temperature (Soldering, 1  | 0s)                                 |                                        |

#### **Operating Conditions**

CAUTION: Stresses above those listed in "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress only rating and operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied.

#### NOTES:

- 1.  $\theta_{JA}$  is measured with the component mounted on an evaluation PC board in free air.

- 2. For supply voltages less than  $\pm$ 15V, the absolute maximum input voltage is equal to the supply voltage.

- 3. Short circuit may be to ground or either supply. Rating applies to 70°C ambient temperature.

- 4. Input voltages may exceed the supply voltages provided the input current is limited to  $\pm 100 \mu$ A.

- 5. Connecting any digital inputs or outputs to voltages greater than V+ or less than GND may cause destructive device latchup. For this reason it is recommended that the power supply to the ICL7104 be established before any inputs from sources not on that supply are applied.

| ICL7104 Electrical Specifications V+ = +5 | V, V++ = +15V, V- = -15V, $T_A = 25^{\circ}C$ , $f_{CLOCK} = 200$ kHz |

|-------------------------------------------|-----------------------------------------------------------------------|

|-------------------------------------------|-----------------------------------------------------------------------|

| PARAMETER                                                                                                                                              | SYMBOL          | TEST<br>CONDITIONS            | MIN | ТҮР    | МАХ | UNITS |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|-------------------------------|-----|--------|-----|-------|--|

| Clock Input, CLK 1                                                                                                                                     | I <sub>IN</sub> | V <sub>IN</sub> = +5V to 0V   | ±2  | ±7     | ±30 | μA    |  |

| Comparator I/P, COMP IN (Note 6)                                                                                                                       | I <sub>IN</sub> | $V_{IN} = 0V \text{ to } +5V$ | -10 | ±0.001 | 10  | μA    |  |

| Inputs with Pulldown, MODE                                                                                                                             | Чн              | V <sub>IN</sub> = +5V         | 1   | 5      | 30  | μA    |  |

|                                                                                                                                                        | I <sub>IL</sub> | V <sub>IN</sub> = 0V          | -10 | ±0.01  | 10  | μA    |  |

| Inputs with Pullups                                                                                                                                    | Чн              | V <sub>IN</sub> = +5V         | -10 | ±0.01  | 10  | μA    |  |

| SEN, R/H<br>LBEN, MBEN, HBEN, CE/LD (Note 7)                                                                                                           | liL             | V <sub>IN</sub> = 0V          | -30 | -5     | -1  | μA    |  |

| Input High Voltage, All Digital Inputs                                                                                                                 | VIH             |                               | 2.5 | 2.0    | -   | V     |  |

| Input Low Voltage, All Digital Inputs                                                                                                                  | VIL             |                               | -   | 1.5    | 1.0 | V     |  |

| Digital Outputs Three-Stated On,<br>IBEN, MBEN (16 Only), HBEN, CE/LD<br>BIT n, POL, OR (Note 8)<br>Digital Outputs Three-Stated Off<br>Bits a POL, OP | V <sub>OL</sub> | I <sub>OL</sub> = 1.6mA       | -   | 0.27   | 0.4 | V     |  |

|                                                                                                                                                        | V <sub>OH</sub> | I <sub>OH</sub> = -10μA       | -   | 4.5    | -   | V     |  |

|                                                                                                                                                        | V <sub>OH</sub> | I <sub>OH</sub> = -240μA      | 2.4 | 3.5    | -   | V     |  |

| Digital Outputs Three-Stated Off<br>Bit n, POL, OR                                                                                                     | I <sub>OL</sub> | $0 \le V_{OUT} \le V_{+}$     | -10 | ±0.001 | +10 | μΑ    |  |

| Non Three-State Digital Output                                                                                                                         |                 |                               |     |        |     |       |  |

| STTS                                                                                                                                                   | V <sub>OL</sub> | I <sub>OL</sub> = 3.2mA       | -   | 0.3    | 0.4 | V     |  |

|                                                                                                                                                        | V <sub>OH</sub> | I <sub>OH</sub> = -400μA      | 2.4 | 3.3    | -   | V     |  |

| Clock 2                                                                                                                                                | V <sub>OL</sub> | I <sub>OL</sub> = 320μA       | -   | 0.5    | -   | V     |  |

|                                                                                                                                                        | V <sub>OH</sub> | I <sub>OH</sub> = -320μA      | -   | 4.5    | -   | V     |  |

| Clock 3 (-14 Only)                                                                                                                                     | V <sub>OL</sub> | I <sub>OL</sub> = 1.6mA       | -   | 0.27   | 0.4 | V     |  |

|                                                                                                                                                        | V <sub>OH</sub> | I <sub>OH</sub> = -320μA      | 2.4 | 3.5    | -   | V     |  |

| PARAMETER                                                           | SYMBOL              | TEST<br>CONDITIONS | MIN | ТҮР | мах | UNITS |

|---------------------------------------------------------------------|---------------------|--------------------|-----|-----|-----|-------|

| Switch                                                              |                     |                    |     |     |     |       |

| Switch 1                                                            | r <sub>DS(ON)</sub> |                    | -   | 25k | -   | Ω     |

| Switches 2, 3                                                       | r <sub>DS(ON)</sub> |                    | -   | 4k  | 20k | Ω     |

| Switches 4, 5, 6, 7, 8, 9                                           | r <sub>DS(ON)</sub> |                    | -   | 2k  | 10k | Ω     |

| Switch Leakage                                                      | I <sub>D(OFF)</sub> |                    | -   | 15  | -   | pА    |

| Clock Frequency (Note 9)                                            | fclock              |                    | DC  | 200 | 400 | kHz   |

| Supply Currents<br>+5V Supply Current<br>All outputs high impedance | l+                  | Frequency = 200kHz | -   | 200 | 600 | μA    |

| +5V Supply Current                                                  | l++                 | Frequency = 200kHz | -   | 0.3 | 1.0 | mA    |

| -5V Supply Current                                                  | l-                  | Frequency = 200kHz | -   | 25  | 200 | μA    |

| Supply Voltage Range<br>Logic Supply                                | V+                  | Note 10            | 4   | -   | 11  | V     |

| Positive Supply                                                     | V++                 |                    | 10  | -   | 16  | V     |

| Negative Supply                                                     | V-                  |                    | -16 | -   | -10 | V     |

NOTES:

6. This specification applies when not in Auto-Zero phase.

7. Apply only when these pins are inputs, i.e., the mode pin is low, and the 7104 is not in handshake mode.

8. Apply only when these pins are outputs, i.e., the mode pin is high, or the 7104 is in handshake mode.

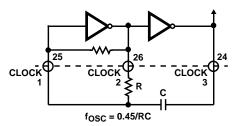

9. Clock circuit shown in Figures 14 and 15.

10. V+ must not be more positive than V++.

#### ICL8068 Electrical Specifications $V_{SUPPLY} = \pm 15V$ , Unless Otherwise Specified

|                                                                   | TEST             |                    | ICL8068 |      |     | ICL8068A |      |      |       |

|-------------------------------------------------------------------|------------------|--------------------|---------|------|-----|----------|------|------|-------|

| PARAMETER                                                         | SYMBOL           | CONDITIONS         | MIN     | ТҮР  | МАХ | MIN      | TYP  | MAX  | UNITS |

| EACH OPERATIONAL AMPLIFIER                                        | -                |                    |         |      |     |          |      | -    |       |

| Input Offset Voltage                                              | V <sub>OS</sub>  | $V_{CM} = 0V$      | -       | 20   | 65  | -        | 20   | 65   | mV    |

| Input Current (Either Input) (Note 11)                            | I <sub>IN</sub>  | $V_{CM} = 0V$      | -       | 175  | 250 | -        | 80   | 150  | pА    |

| Common-Mode Rejection Ratio                                       | CMRR             | $V_{CM} = \pm 10V$ | 70      | 90   | -   | 70       | 90   | -    | dB    |

| Non-Linear Component of Common-<br>Mode Rejection Ratio (Note 12) |                  | $V_{CM} = \pm 2V$  | -       | 110  | -   | -        | 110  | -    | dB    |

| Large Signal Voltage Gain                                         | A <sub>V</sub>   | $R_L = 50k\Omega$  | 20,000  | -    | -   | 20,000   | -    | -    | V/V   |

| Slew Rate                                                         | SR               |                    | -       | 6    | -   | -        | 6    | -    | V/µs  |

| Unity Gain Bandwidth                                              | GBW              |                    | -       | 2    | -   | -        | 2    | -    | MHz   |

| Output Short-Circuit Current                                      | I <sub>SC</sub>  |                    | -       | 5    | -   | -        | 5    | -    | mA    |

| COMPARATOR AMPLIFIER                                              |                  |                    |         |      |     |          |      |      |       |

| Small-Signal Voltage Gain                                         | A <sub>VOL</sub> | $R_L = 30k\Omega$  | -       | 4000 | -   | -        | -    | -    | V/V   |

| Positive Output Voltage Swing                                     | +V <sub>O</sub>  |                    | 12      | 13   | -   | 12       | 13   | -    | V     |

| Negative Output Voltage Swing                                     | -V <sub>O</sub>  |                    | -2.0    | -2.6 | -   | -2.0     | -2.6 | -    | V     |

| VOLTAGE REFERENCE                                                 |                  | •                  | -       |      |     | =        | -    | •    |       |

| Output Voltage                                                    | Vo               |                    | 1.5     | 1.75 | 2.0 | 1.60     | 1.75 | 1.90 | V     |

| Output Resistance                                                 | R <sub>O</sub>   |                    | -       | 5    | -   | -        | 5    | -    | Ω     |

|                         |                     | TEST       | I   | CL8068 |     | IC  | CL8068A |     |                     |

|-------------------------|---------------------|------------|-----|--------|-----|-----|---------|-----|---------------------|

| PARAMETER               | SYMBOL              | CONDITIONS | MIN | ТҮР    | MAX | MIN | ТҮР     | МАХ | UNITS               |

| Temperature Coefficient | тс                  |            | -   | 50     | -   | -   | 40      | -   | ppm/ <sup>o</sup> C |

| Supply Voltage Range    | V <sub>SUPPLY</sub> |            | ±10 | -      | ±16 | ±10 | -       | ±16 | V                   |

| Supply Current Total    | ISUPPLY             |            | -   | -      | 14  | -   | 8       | 14  | mA                  |

## ICL8068 Electrical Specifications V<sub>SUPPLY</sub> = ±15V, Unless Otherwise Specified (Continued)

# ICL8052 Electrical Specifications V<sub>SUPPLY</sub> = $\pm$ 15V, Unless Otherwise Specified

|                                                                   |                     | TEST               | ICL8052 |      |     | IC     |      |      |                     |

|-------------------------------------------------------------------|---------------------|--------------------|---------|------|-----|--------|------|------|---------------------|

| PARAMETER                                                         | SYMBOL              | CONDITIONS         | MIN     | ТҮР  | МАХ | MIN    | ТҮР  | МАХ  | UNITS               |

| EACH OPERATIONAL AMPLIFIER                                        |                     |                    |         |      |     |        |      |      |                     |

| Input Offset Voltage                                              | V <sub>OS</sub>     | $V_{CM} = 0V$      | -       | 20   | 75  | -      | 20   | 75   | mV                  |

| Input Current (Either Input) (Note 11)                            | I <sub>IN</sub>     | $V_{CM} = 0V$      | -       | 5    | 50  | -      | 2    | 10   | pА                  |

| Common-Mode Rejection Ratio                                       | CMRR                | $V_{CM} = \pm 10V$ | 70      | 90   | -   | 70     | 90   | -    | dB                  |

| Non-Linear Component of Common-<br>Mode Rejection Ratio (Note 12) |                     | $V_{CM} = \pm 2V$  | -       | 110  | -   | -      | 110  | -    | dB                  |

| Large Signal Voltage Gain                                         | A <sub>V</sub>      | $R_L = 50k\Omega$  | 20,000  | -    | -   | 20,000 | -    | -    | V/V                 |

| Slew Rate                                                         | SR                  |                    | -       | 6    | -   | -      | 6    | -    | V/µs                |

| Unity Gain Bandwidth                                              | GBW                 |                    | -       | 1    | -   | -      | 1    | -    | MHz                 |

| Output Short-Circuit Current                                      | I <sub>SC</sub>     |                    | -       | 20   | -   | -      | 20   | -    | mA                  |

| COMPARATOR AMPLIFIER                                              |                     | •                  |         |      |     |        |      |      |                     |

| Small-Signal Voltage Gain                                         | A <sub>VOL</sub>    | $R_L = 30k\Omega$  | -       | 4000 | -   | -      | -    | -    | V/V                 |

| Positive Output Voltage Swing                                     | +V <sub>O</sub>     |                    | 12      | 13   | -   | 12     | 13   | -    | V                   |

| Negative Output Voltage Swing                                     | -V <sub>O</sub>     |                    | -2.0    | -2.6 | -   | -2.0   | -2.6 | -    | V                   |

| VOLTAGE REFERENCE                                                 |                     |                    |         |      |     |        |      |      |                     |

| Output Voltage                                                    | Vo                  |                    | 1.5     | 1.75 | 2.0 | 1.60   | 1.75 | 1.90 | V                   |

| Output Resistance                                                 | R <sub>O</sub>      |                    | -       | 5    | -   | -      | 5    | -    | Ω                   |

| Temperature Coefficient                                           | тс                  |                    | -       | 50   | -   | -      | 40   | -    | ppm/ <sup>o</sup> C |

| Supply Voltage Range                                              | V <sub>SUPPLY</sub> |                    | ±10     | -    | ±16 | ±10    | -    | ±16  | V                   |

| Supply Current Total                                              | ISUPPLY             |                    | -       | 6    | 12  | -      | 6    | 12   | mA                  |

NOTES:

11. The input bias currents are junction leakage currents which approximately double for every  $10^{\circ}$ C increase in the junction temperature, T<sub>J</sub>. Due to limited production test time, the input bias currents are measured with junctions at ambient temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation, P<sub>D</sub>. T<sub>J</sub> = T<sub>A</sub> + R<sub>0JA</sub>P<sub>D</sub> where R<sub>0JA</sub> is the thermal resistance from junction to ambient. A heat sink can be used to reduce temperature rise.

12. This is the only component that causes error in dual-slope converter.

|                                                                                                     | TEST                                                                                             | ICL80  | 68A/ICL7 | 104-14 | ICL80  |        |        |                     |

|-----------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------|----------|--------|--------|--------|--------|---------------------|

| PARAMETER                                                                                           | CONDITIONS                                                                                       | MIN    | ТҮР      | MAX    | MIN    | ТҮР    | MAX    | UNITS               |

| Zero Input Reading                                                                                  | $V_{IN} = 0V, V_{REF} = 2V$                                                                      | -00000 | ±00000   | +00000 | -00000 | ±00000 | +00000 | Counts              |

| Ratiometric Error (Note 13)                                                                         | $V_{IN} = V_{REF} = 2V$                                                                          | -1     | 0        | 1      | -1     | 0      | 1      | LSB                 |

| Linearity Over ± Full Scale (Error of Reading from Best Straight Line)                              | $-4V \le V_{IN} \le +4V$                                                                         | -      | 0.5      | 1      | -      | 0.5    | 1      | LSB                 |

| Differential Linearity (Difference<br>between Worst Case Step of Adjacent<br>Counts and Ideal Step) | $-4V \le V_{IN} \le +4V$                                                                         | -      | 0.01     | -      | -      | 0.01   | -      | LSB                 |

| Rollover Error (Difference in Reading<br>for Equal Positive & Negative Voltage<br>Near Full Scale)  | $-V_{IN} = +V_{IN} \cong 4V$                                                                     | -      | 0.5      | 1      | -      | 0.5    | 1      | LSB                 |

| Noise (P-P Value Not Exceeded 95% of Time)                                                          | V <sub>IN</sub> = 0V,<br>Full Scale = 4V                                                         | -      | 2        | -      | -      | 2      | -      | μV                  |

| Leakage Current at Input (Note 14)                                                                  | $V_{IN} = 0V$                                                                                    | -      | 100      | 165    | -      | 100    | 165    | pА                  |

| Zero Reading Drift                                                                                  | V <sub>IN</sub> = 0V,<br>0°C to 70°C                                                             | -      | 0.5      | -      | -      | 0.5    | -      | μV/ <sup>o</sup> C  |

| Scale Factor Temperature Coefficient<br>(Note 15)                                                   | V <sub>IN</sub> = 4V,<br>0 <sup>o</sup> C to 50 <sup>o</sup> C<br>ext. ref. 0ppm/ <sup>o</sup> C | -      | 2        | 5      | -      | 2      | 5      | ppm/ <sup>o</sup> C |

System Electrical Specifications: ICL8068/ICL7104 V++ = +15V, V+ = +5V, V- = -15V, f<sub>CLOCK</sub> = 200kHz (Note 16)

#### System Electrical Specifications: ICL8052/ICL7104 V++ = +15V, V+ = +5V, V- = -15V, f<sub>CLOCK</sub> = 200kHz (Note 16)

|                                                                                                      | TEST                                                                                             | ICL80  | 52A/ICL7 | 104-14 | ICL80  |        |        |                     |

|------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------|----------|--------|--------|--------|--------|---------------------|

| PARAMETER                                                                                            | CONDITIONS                                                                                       | MIN    | TYP      | MAX    | MIN    | TYP    | MAX    | UNITS               |

| Zero Input Reading                                                                                   | $V_{IN} = 0V, V_{REF} = 2V$                                                                      | -00000 | ±00000   | +00000 | -00000 | ±00000 | +00000 | Counts              |

| Ratiometric Error (Note 15)                                                                          | $V_{IN} = V_{REF} = 2V$                                                                          | -1     | 0        | 1      | -1     | 0      | 1      | LSB                 |

| Linearity Over ± Full Scale (Error of Reading from Best Straight Line)                               | $-4V \le V_{IN} \le +4V$                                                                         | -      | 0.5      | 1      | -      | 0.5    | 1      | LSB                 |

| Differential Linearity (Difference<br>between Worst Case Step of Adjacent<br>Counts and Ideal Step)  | $-4V \le V_{IN} \le +4V$                                                                         | -      | 0.01     | -      | -      | 0.01   | -      | LSB                 |

| Rollover Error (Difference in Reading<br>for Equal Positive and Negative<br>Voltage Near Full Scale) | $-V_{IN} = +V_{IN} \approx 4V$                                                                   | -      | 0.5      | 1      | -      | 0.5    | 1      | LSB                 |

| Noise (Peak-to-Peak Value Not<br>Exceeded 95% of Time)                                               | V <sub>IN</sub> = 0V,<br>Full Scale = 4V                                                         | -      | 30       | -      | -      | 30     | -      | μV                  |

| Leakage Current at Input (Note 14)                                                                   | $V_{IN} = 0V$                                                                                    | -      | 20       | 30     | -      | 20     | 30     | pА                  |

| Zero Reading Drift                                                                                   | $V_{IN} = 0V,$<br>$0^{\circ}C$ to $70^{\circ}C$                                                  | -      | 0.5      | -      | -      | 0.5    | -      | μV/ <sup>o</sup> C  |

| Scale Factor Temperature Coefficient                                                                 | V <sub>IN</sub> = 4V,<br>0 <sup>o</sup> C to 50 <sup>o</sup> C<br>ext. ref. 0ppm/ <sup>o</sup> C | -      | 2        | -      | -      | 2      | -      | ppm/ <sup>o</sup> C |

#### NOTES:

13. Tested with low dielectric absorption integrating capacitor.

- 14. The input bias currents are junction leakage currents which approximately double for every  $10^{\circ}$ C increase in the junction temperature, T<sub>J</sub>. Due to limited production test time, the input bias currents are measured with junctions at ambient temperature. In normal operation the junction temperature rises above the ambient temperature as a result of internal power dissipation, P<sub>D</sub>. T<sub>J</sub> = T<sub>A</sub> + R<sub>0JA</sub>P<sub>D</sub> where R<sub>0JA</sub> is the thermal resistance from junction to ambient. A heat sink can be used to reduce temperature rise.

- 15. The temperature range can be extended to 70<sup>o</sup>C and beyond if the Auto-Zero and Reference capacitors are increased to absorb the high temperature leakage of the 8068. See note 14 above.

- 16. System Electrical Specifications are not tested; for reference only.

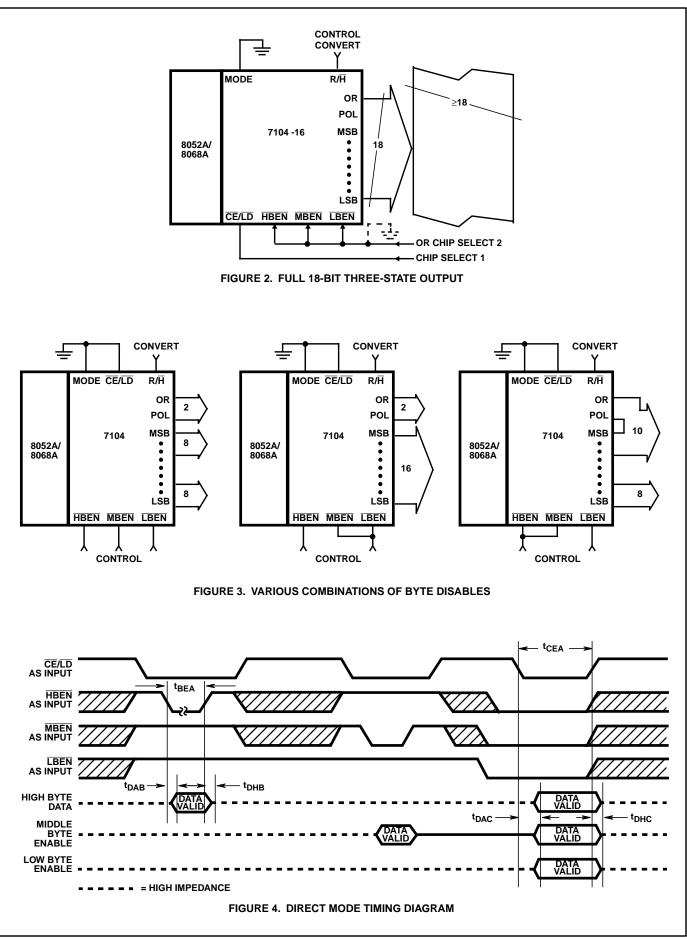

|                  |                              | (   |      |     |      |

|------------------|------------------------------|-----|------|-----|------|

| SYMBOL           | DESCRIPTION                  | MIN | ТҮР  | МАХ | UNIT |

| t <sub>BEA</sub> | XBEN (Min) Pulse Width.      | -   | 300  | -   | ns   |

| <sup>t</sup> DAB | Data Access Time from XBEN.  | -   | 300  | -   | ns   |

| tDHB             | Data Hold Time from XBEN.    | -   | 200  | -   | ns   |

| <sup>t</sup> CEA | CE/LD Min. Pulse Width.      | -   | 350  | -   | ns   |

| <sup>t</sup> DAC | Data Access Time from CE/LD. | -   | 350  | -   | ns   |

| <sup>t</sup> DHC | Data Hold Time from CE/LD.   | -   | 280  | -   | ns   |

| <sup>t</sup> CWH | CLOCK 1 High Time.           | -   | 1000 | -   | ns   |

#### TABLE 1. DIRECT MODE TIMING REQUIREMENTS (Note: Not tested in production)

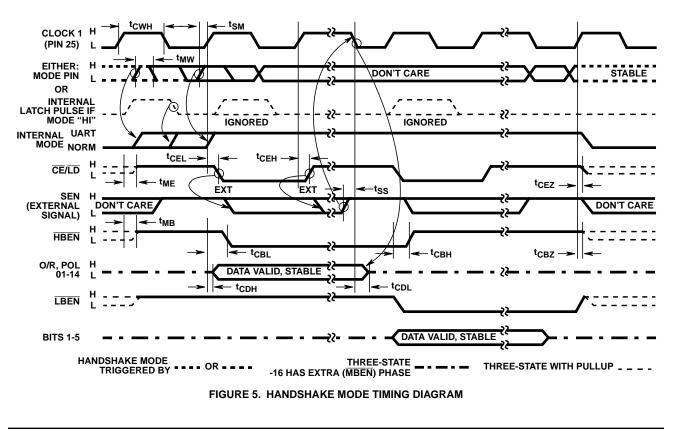

## TABLE 2. HANDSHAKE TIMING REQUIREMENTS (Note: Not tested in production)

| SYMBOL           | DESCRIPTION                                                      | MIN  | ТҮР  | МАХ | UNIT |

|------------------|------------------------------------------------------------------|------|------|-----|------|

| t <sub>MW</sub>  | Mode Pulse (Min).                                                | -    | 20   | -   | ns   |

| t <sub>SM</sub>  | Mode Pin Set-Up Time.                                            | -    | -150 | -   | ns   |

| t <sub>ME</sub>  | Mode Pin High to Low Z $\overline{CE}/\overline{LD}$ High Delay. | -    | 200  | -   | ns   |

| t <sub>MB</sub>  | Mode Pin High to $\overline{XBEN}$ Low Z (High) Delay.           | -    | 200  | -   | ns   |

| <sup>t</sup> CEL | Clock 1 High to CE/LD Low Delay.                                 | -    | 700  | -   | ns   |

| <sup>t</sup> CEH | Clock 1 High to $\overline{CE}/\overline{LD}$ High Delay.        | -    | 600  | -   | ns   |

| <sup>t</sup> CBL | Clock 1 High to XBEN Low Delay.                                  | -    | 900  | -   | ns   |

| <sup>t</sup> СВН | Clock 1 High to XBEN High Delay.                                 | -    | 700  | -   | ns   |

| <sup>t</sup> CDH | Clock 1 High to Data Enabled Delay.                              | -    | 1100 | -   | ns   |

| <sup>t</sup> CDL | Clock 1 Low to Data Disabled Delay.                              | -    | 1100 | -   | ns   |

| tss              | Send ENABLE Set-Up Time.                                         | -    | -350 | -   | ns   |

| <sup>t</sup> CBZ | Clock 1 High to XBEN Disabled Delay.                             | -    | 2000 | -   | ns   |

| <sup>t</sup> CEZ | Clock 1 High to CE/LD Disabled Delay.                            | -    | 2000 | -   | ns   |

| <sup>t</sup> CWH | Clock 1 High Time.                                               | 1250 | 1000 | -   | ns   |

# **Detailed Description**

#### ANALOG SECTION

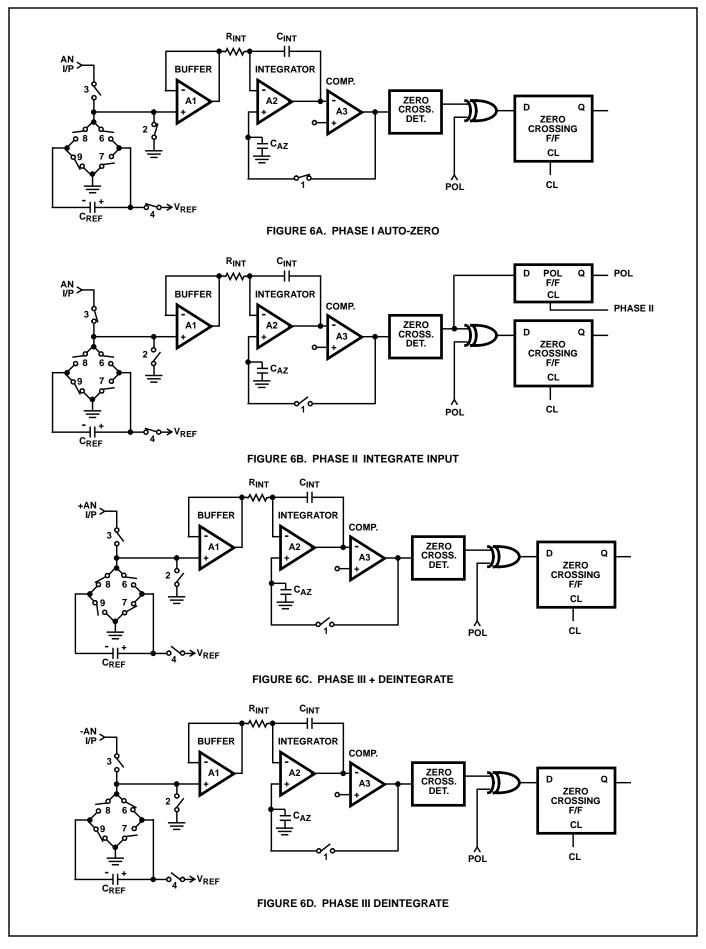

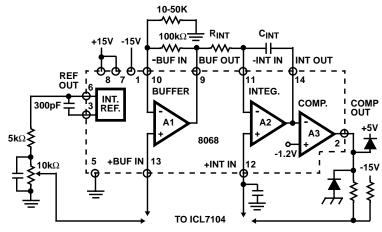

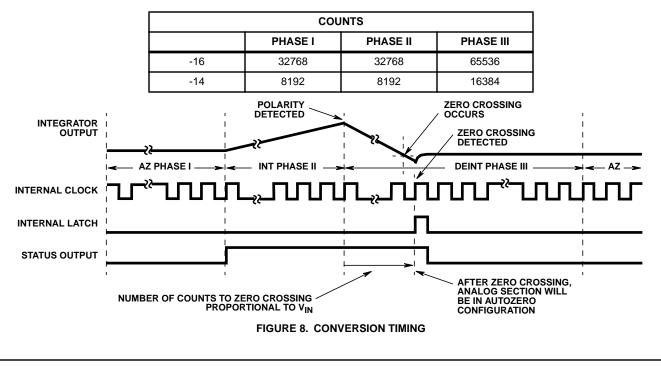

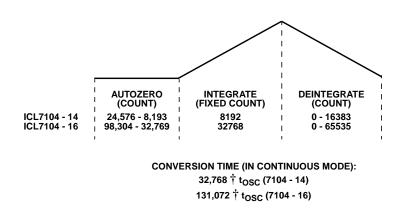

Figure 6 shows the equivalent Circuit of the Analog Section of both the ICL7104/8052 and the ICL7104/8068 in the 3 different phases of operation. If the Run/Hold pin is left open or tied to V+, the system will perform conversions at a rate determined by the clock frequency: 131,072 for - 16 and 32,368 for - 14 clock periods per cycle (see Figure 8 conversion timing).

#### Auto-Zero Phase I (Figure 6A)

During Auto-Zero, the input of the buffer is shorted to analog ground thru switch 2, and switch 1 closes a loop around the integrator and comparator. The purpose of the loop is to charge the Auto-Zero capacitor until the integrator output no longer changes with time. Also, switches 4 and 9 recharge the reference capacitor to  $V_{\mathsf{REF}}$ .

#### Input Integrate Phase II (Figure 6B)

During input integrate the Auto-Zero loop is opened and the analog input is connected to the buffer input thru switch 3. (The reference capacitor is still being charged to  $V_{REF}$  during this time.) If the input signal is zero, the buffer, integrator and comparator will see the same voltage that existed in the previous sate (Auto-Zero). Thus the integrator output will not change but will remain stationary during the entire Input Integrate cycle. If  $V_{IN}$  is not equal to zero, an unbalanced condition exists compared to the Auto-Zero phase, and the integrator will generate a ramp whose slope is proportional to  $V_{IN}$ . At the end of this phase, the sign of the ramp is latched into the polarity F/F.

#### **Deintegrate Phase III** (Figures 6C and 6D)

During the Deintegrate phase, the switch drive logic uses the output of the polarity F/F in determining whether to close switches 6 and 9 or 7 and 8. If the input signal was positive, switches 7 and 8 are closed and a voltage which is  $V_{REF}$  more negative than during Auto-Zero is impressed on the buffer input. Negative inputs will cause  $+V_{REF}$  to be applied to the buffer input via switches 6 and 9. Thus, the reference capacitor generates the equivalent of a (+) reference or a (-) reference from the single reference voltage with negligible error. The reference voltage returns the output of the integrator to the zero-crossing point established in Phase I. The time, or number of counts, required to do this is proportional to the input voltage. Since the Deintegrate phase can be twice as long as the Input integrate phase, the input voltage required to give a full scale reading =  $2V_{REF}$ .

NOTE: Once a zero crossing is detected, the system automatically reverts to Auto-Zero phase for the leftover Deintegrate time (unless RUN/HOLD is manipulated, see RUN/HOLD input in detailed description, digital section).

| i          | TABLE 3. THREE-STATE BYTE FORMATS AND ENABLE PINS |     |     |      |     |     |     |     |     |            |    |     |    |      |    |    |    |    |

|------------|---------------------------------------------------|-----|-----|------|-----|-----|-----|-----|-----|------------|----|-----|----|------|----|----|----|----|

|            | HBEN MBEN                                         |     |     |      |     |     |     |     |     |            |    |     |    | LBEN |    |    |    |    |

| ICL7104-16 | POL                                               | O/R | B16 | B15  | B14 | B13 | B12 | B11 | B10 | B9         | B8 | B7  | B6 | B5   | B4 | B3 | B2 | B1 |

|            |                                                   |     |     | HBEN |     |     |     |     |     |            |    |     |    | LB   | EN |    |    |    |

| ICL7104-14 |                                                   |     | POL | O/R  | B14 | B13 | B12 | B11 | B10 | B9         | B8 | B7  | B6 | B5   | B4 | B3 | B2 | B1 |

| ICL/104-14 |                                                   |     | PUL | 0/R  | ы4  | ыз  | ЫΖ  | БП  | ыо  | <u>Б</u> 9 | DØ | • Г | D0 | БЭ   | Б4 | D3 | Б2 | В  |

**TABLE 4. TYPICAL COMPONENT VALUES** (V++ = +15V, V+ = 5V, V- = 5V, V- = -15V, f<sub>CLOCK</sub> = 200kHz)

| ICL8052/8068 WITH          |      | ICL7104-16 |      | ICL71 | UNIT |     |

|----------------------------|------|------------|------|-------|------|-----|

| Full scale V <sub>IN</sub> | 200  | 800        | 4000 | 100   | 4000 | mV  |

| Buffer Gain                | 10   | 1          | 1    | 10    | 1    | V/V |

| R <sub>INT</sub>           | 100  | 43         | 200  | 47    | 180  | kΩ  |

| C <sub>INT</sub>           | 0.33 | 0.33       | 0.33 | 0.1   | 0.1  | μF  |

| C <sub>AZ</sub>            | 1    | 1          | 1    | 1     | 1    | μF  |

| C <sub>REF</sub>           | 10   | 1          | 1    | 10    | 1    | μF  |

| V <sub>REF</sub>           | 100  | 400        | 2000 | 50    | 2000 | mV  |

| Resolution                 | 3.1  | 12         | 61   | 6.1   | 244  | μV  |

FIGURE 7. ADDING BUFFER GAIN TO ICL8068

#### **Buffer Gain**

At the end of the auto-zero interval, the instantaneous noise voltage on the auto-zero capacitor is stored, and subtracts from the input voltage while adding to the reference voltage during the next cycle. The result is that this noise voltage effectively is somewhat greater than the input noise voltage of the buffer itself during integration. By introducing some voltage gain into the buffer, the effect of the auto-zero noise (referred to the input) can be reduced to the level of the inherent buffer noise. This generally occurs with a buffer gain of between 3 and 10. Further increase in buffer gain merely increases the total offset to be handled by the auto-zero loop, and reduces the available buffer and integrator swings, without improving the noise performance of the system. The circuit recommended for doing this with the ICL8068/ICL7104 is shown in Figure 7. With careful layout, the circuit shown can achieve effective input noise voltages

on the order of 1 to  $2\mu$ V, allowing full 16-bit use with full scale inputs of a low as 150mV. Note that at this level, thermoelectric EMFs between PC boards, IC pins, etc., due to local temperature changes can be very troublesome. For further discussion, see Application Note AN030.

#### ICL8052 vs ICL8068

The ICL8052 offers significantly lower input leakage currents than the ICL8068, and may be found preferable in systems with high input impedances. However, the ICL8068 has substantially lower noise voltage, and for systems where system noise is a limiting factor, particularly in low signal level conditions, will give better performance.

## **Component Value Selection**

For optimum performance of the analog section, care must be taken in the selection of values for the integrator capacitor and resistor, auto-zero capacitor, reference voltage, and conversion rate. These values must be chosen to suit the particular application.

#### **Integrating Resistor**

The integrating resistor is determined by the full scale input voltage and the output current of the buffer used to charge the integrator capacitor. This current should be small compared to the output short circuit current such that thermal effects are kept to a minimum and linearity is not affected. Values of 5 to  $40\mu$ A give good results with a nominal of  $20\mu$ A. The exact value may be chosen by:

$$R_{INT} = \frac{\text{full scale voltage (see note)}}{20 \mu A}$$

NOTE: If gain is used in the buffer amplifier then  $R_{\text{HVT}} = \frac{(BufferGain) \text{ (full scale voltage)}}{(BufferGain) \text{ (full scale voltage)}}$

#### **Integrating Capacitor**

The product of integrating resistor and capacitor is selected to give 9 volt swing for full scale inputs. This is a compromise between possibly saturating the integrator (at +14 volts) due to tolerance build-up between the resistor, capacitor and clock and the errors a lower voltage swing could induce due to offsets referred to the output of the comparator. In general, the value of  $C_{INT}$  is given by:

$$C_{INT} = \frac{\binom{(32768 \text{ for - 16})}{(8192 \text{ for -14})} \times 20 \mu A \times \text{clock period}}{\text{Integrator Output Voltage Swing}}$$

A very important characteristic of the integrating capacitor is that it have low dielectric absorption to prevent roll-over or

ratiometric errors. A good test for dielectric absorption is to use the capacitor with the input tied to the reference.

This ratiometric condition should read half scale (100...000) and any deviation is probably due to dielectric absorption. Polypropylene capacitors give undetectable errors at reasonable cost. Polystyrene and polycarbonate capacitors may also be used in less critical applications.

#### Auto-Zero and Reference Capacitor

The size of the auto-zero capacitor has some influence on the noise of the system, a large capacitor giving less noise. The reference capacitor should be large enough such that stray capacitance to ground from its nodes is negligible.

NOTE: When gain is used in the buffer amplifier the reference capacitor should be substantially larger than the auto-zero capacitor. As a rule of thumb, the reference capacitor should be approximately the gain times the value of the auto-zero capacitor. The dielectric absorption of the reference cap and auto-zero cap are only important at power-on or when the circuit is recovering from an overload. Thus, smaller or cheaper caps can be used here if accurate readings are not required for the first few seconds of recovery.

#### **Reference Voltage**

The analog input required to generate a full scale output is  $V_{\text{IN}}$  = 2V\_{\text{REF}}.

The stability of the reference voltage is a major factor in the overall absolute accuracy of the converter. The resolution of the ICL7104 at 16 bits is one part in 65536, or 15.26ppm. Thus, if the reference has a temperature coefficient of 50ppm/C (on board reference) a temperature change of 1/3C will introduce a one-bit absolute error. For this reason, it is recommended that an external high quality reference be used where the ambient temperature is not controlled or where high-accuracy absolute measurements are being made.

# **Detailed Description**

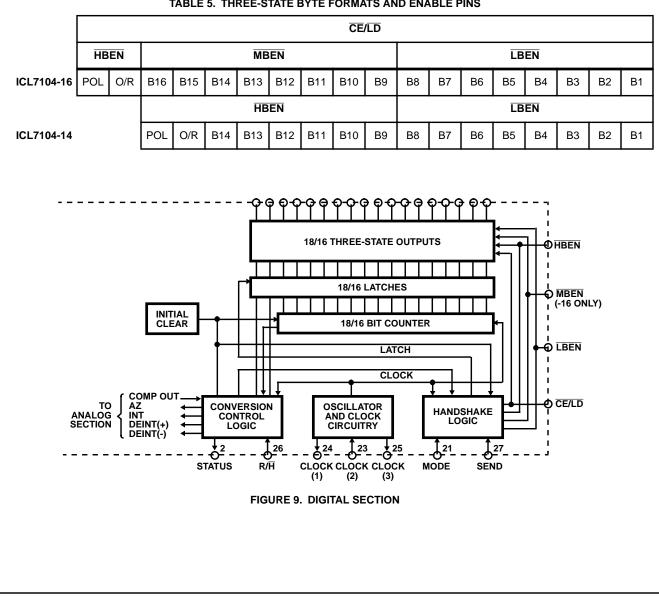

#### **DIGITAL SECTION**

The digital section includes the clock oscillator circuit, a 16-bit or 14-bit binary counter with output latches and TTLcompatible three-state output drivers, polarity, over-range and control logic and UART handshake logic, as shown in the Block Diagram Figure 9 (16-bit version shown).

Throughout this description, logic levels will be referred to as "low" or "high". The actual logic levels are defined under "ICL7104 Electrical Specification". For minimum power consumption, all inputs should swing from GND (low) to V+ (high). Inputs driven from TTL gates should have 3 -  $5k\Omega$ pullup resistors added for maximum noise immunity.

#### **MODE Input**

The MODE input is used to control the output mode of the converter. When the MODE pin is connected to GND or left open (this input is provided with a pulldown resistor to

ensure a low level when the pin is left open), the converter is in its "Direct" output mode, where the output data is directly accessible under the control of the chip and byte enable inputs. When the MODE input is pulsed high, the converter enters the UART handshake mode and outputs the data in three bytes for the 7104-16 or two bytes for the 7104-14 then returns to "direct" mode. When the MODE input is left high, the converter will output data in the handshake mode at the end of every conversion cycle. (See section entitled "Handshake Mode" for further details).

#### STATUS Output

During a conversion cycle, the STATUS output goes high at the beginning of Input Integrate (Phase II), and goes low one-half clock period after new data from the conversion has been stored in the output latches. See Figure 8 for details of this timing. This signal may be used as a "data valid" flag (data never changes while STATUS is low) to drive interrupts, or for monitoring the status of the converter.

#### TABLE 5. THREE-STATE BYTE FORMATS AND ENABLE PINS

#### **Run/Hold Input**

When the Run/Hold input is connected to V+ or left open (this input has pullup resistor to ensure a high level when the pin is left open), the circuit will continuously perform conversion cycles, updating the output latches at the end of every Deintegrate (Phase III) portion of the conversion cycle (See Figure 8). (See under "Handshake Mode" for exception.) In this mode of operation, the conversion cycle will be performed in 131,072 for 7104-16 and 32768 for 7104-14 clock periods, regardless of the resulting value.

If Run/Hold goes low at any time during Deintegrate (Phase III) after the zero crossing has occurred, the circuit will immediately terminate Deintegrate and jump to Auto-Zero. This feature can be used to eliminate the time spent in Deintegrate after the zero-crossing. If Run/Hold stays or goes low, the converter will ensure a minimum Auto-Zero time, and then wait in Auto-Zero until the Run/Hold input goes high. The converter will begin the Integrate (Phase II) portion of the next conversion (and the STATUS output will go high) seven clock periods after the high level is detected at Run/Hold. See Figure 10 for details.

Using the Run/Hold input in this manner allows an easy "convert on demand" interface to be used. The converter may be held at idle in Auto-Zero with Run/Hold low. When Run/Hold goes high the conversion is started, and when the STATUS output goes low the new data is valid (or transferred) to the UART - see Handshake Mode). Run/Hold may now go low terminating Deintegrate and ensuring a minimum Auto-Zero time before stopping to wait for the next conversion. Alternately, Run/Hold can be used to minimize conversion time by ensuring that it goes low during Deintegrate, after zero crossing, and goes high after the hold point is reached. The required activity on the Run/Hold input can be provided by connecting it to the CLOCK3 (-14), CLOCK2 (-16) Output. In this mode the conversion time is dependent on the input value measured. Also refer to Intersil Application Bulletin A030 for a discussion of the effects this will have on Auto-Zero performance.

If the Run/Hold input goes low and stays low during Auto-Zero (Phase I), the converter will simply stop at the end of the Auto-Zero and wait for Run/Hold to go high. As above, Integrate (Phase II) begins seven clock periods after the high level is detected.

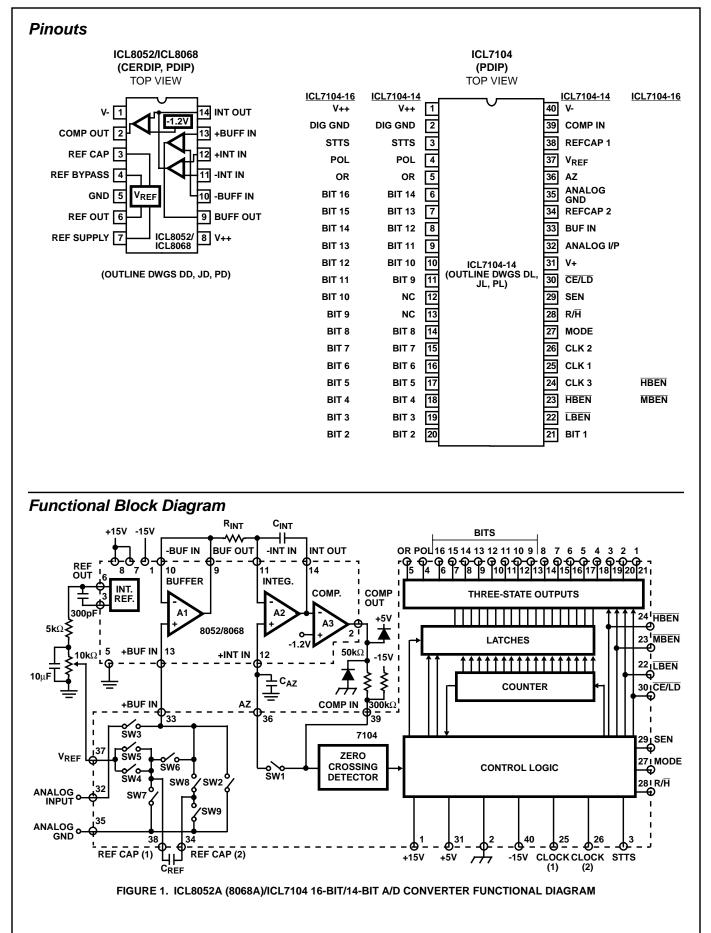

#### **Direct Mode**

When the MODE pin is left at a low level, the data outputs [bits 1 through 8 low order byte, See Table 3 for format of middle (-16) and high order bytes] are accessible under control of the byte and CHIP ENABLE terminals as inputs. These ENABLE inputs are all active low, and are provided with pullup resistors to ensure an inactive high level when left open. When the CHIP ENABLE input is low, taking a byte ENABLE input low will allow the outputs of that byte to become active (three-stated on). This allows a variety of parallel data accessing techniques to be used. The timing requirements for these outputs are shown under AC Specifications and Table 1.

It should be noted that these control inputs are asynchronous with respect to the converter clock - the data may be accessed at any time. Thus it is possible to access the data while it is being updated, which could lead to scrambled data. Synchronizing the access of data with the conversion cycle by monitoring the STATUS output will prevent this. Data is never updated while STATUS is low. Also note the potential bus conflict described under "Initial Clear Circuitry".

#### Handshake Mode

The handshake output mode is provided as an alternative means of interfacing the ICL7104 to digital systems, where the A/D converter becomes active in controlling the flow of data instead of passively responding to chip and byte ENABLE inputs. This mode is specifically designed to allow a direct interface between the ICL7104 and industry-standard UARTs (such as the Intersil CMOS UARTs, IM6402/3) with no external logic required. When triggered into the handshake mode, the ICL7104 provides all the control and flag signals necessary to sequence the three (ICL7106-16) or two (ICL7104-14) bytes of data into the UART and initiate their transmission in serial form. This greatly eases the task and reduces the cost of designing remote data acquisition stations using serial data transmission to minimize the number of lines to the central controlling processor.

Entry into the handshake mode will occur if either of two conditions are fulfilled; first, if new data is latched (i.e., a conversion is completed) while MODE pin (pin 27) is high, in which case entry occurs at the end of the latch cycle; or secondly, if the MODE pin goes from low to high, when entry will occur immediately (if new data is being latched, entry is delayed to the end of the latch cycle). While in the handshake mode, data latching is inhibited, and the MODE pin is ignored. (Note that conversion cycles will continue in the normal manner). This allows versatile initiation of handshake operation without danger of false data generation; if the MODE pin is held high, every conversion (other than those completed during handshake operations) will start a new handshake operation, while if the MODE pin is pulsed high, handshake operations can be obtained "on demand."

When the converter enters the handshake mode, or when the MODE input is high, the chip and byte ENABLE terminals become TTL-compatible outputs which provide the control signals for the output cycle. The Send ENABLE pin (SEN) (pin 29) is used as an indication of the ability of the external device to receive data. The condition of the line is sensed once every clock pulse, and if it is high, the next (or first) byte is enabled on the next rising CLOCK 1 (pin 25) clock edge, the corresponding byte ENABLE line goes low, and the CHIP ENABLE / LOAD pin (pin 30) (CE/LD) goes low for one full clock pulse only, returning high.

On the next falling CLOCK 1 clock pulse edge, if SEN remains high, or after it goes high again, the byte output lines will be put in the high impedance state (or three-stated off). One half pulse later, the byte ENABLE pin will be cleared high, and (unless finished) the  $\overline{CE}/\overline{LD}$  and the next byte ENABLE pin will go low. This will continue until all three (2 in the case of the 14-bit device) bytes have been sent. The bytes are individually put into the low impedance state i.e.: three-stated on during most of the time that their byte ENABLE pin is (active) low. When receipt of the last byte has been acknowledged by a high SEN, the handshake mode will be cleared, re-enabling data latching from conversion, and recognizing the condition of the MODE pin again. The byte and CHIP ENABLE will be three-stated off, if MODE is low, but held by their (weak) pullups. These timing relationships are illustrated in Figures 11, 12, and 13, and Table 2.

Figure 11 shows the sequence of the output cycle with SEN held high. The handshake mode (Internal MODE high) is entered after the data latch pulse (since MODE remains high the CE/LD, LBEN, MBEN and HBEN terminals are active as outputs). The high level at the SEN input is sensed on the same high to low internal clock edge. On the next to high internal clock edge, the CE/LD and the HBEN outputs assume a low level and the high-order byte (POL and OR, and except for -16, Bits 9 - 14) outputs are enabled. The CE/LD output remains low for one full internal clock period only, the data outputs remain active for  $1^{1}/_{2}$  internal clock periods, and the high byte ENABLE remains low for two clock periods. Thus the  $\overline{CE}/\overline{LD}$  output low level or low to high edge may be used as a synchronizing signal to ensure valid data, and the byte ENABLE as an output may be used as a byte identification flag. With SEN remaining high the converter completes the output cycle using CE/LD, MBEN and

LBEN while the remaining byte outputs (see Table 3) are activated. The handshake mode is terminated when all bytes are sent (3 for -16, 2 for -14).

Figure 12 shows an output sequence where the SEN input is used to delay portions of the sequence, or handshake, to ensure correct data transfer. This timing diagram shows the relationships that occur using an industry-standard IM6402/3 CMOS UART to interface to serial data channels. In this interface, the SEN input to the ICL7104 is driven by the TBRE (Transmitter Buffer Register Empty) output of the UART, and the  $\overline{CE/LD}$  terminal of the ICL7104 drives the TBRL (Transmitter Buffer Register Load) input to the UART. The data outputs are paralleled into the eight Transmitter Buffer Register inputs.

Assuming the UART Transmitter Buffer Register is empty, the SEN input will be high when the handshake mode is entered after new data is stored. The CE/LD and HBEN terminals will go low after SEN is sensed, and the high order byte outputs become active. When  $\overline{CE}/\overline{LD}$  goes high at the end of one clock period, the high order byte data is clocked into the UART Transmitter Buffer Register. The UART TBRE output will now go low, which halts the output cycle with the HBEN output low, and the high order byte outputs active. When the UART has transferred the data to the Transmitter Register and cleared the Transmitter Buffer Register, the TBRE returns high. On the next ICL7104 internal clock high to low edge, the high order byte outputs are disabled, and one-half internal clock later, the HBEN output returns high. At the same time, the CE/LD and MBEN (-16) or LBEN outputs go low, and the corresponding byte outputs become active. Similarly, when the CE/LD returns high at the end of one clock period, the enabled data is clocked into the UART Transmitter Buffer Register, and TBRE again goes low. When TBRE returns to a high it will be sensed on the next ICL7104 internal clock high to low edge, disabling the data outputs. For the 16-bit device, the sequence is repeated for LBEN. One-half internal clock later, the handshake mode will be cleared, and the chip and byte ENABLE terminals return high and stay active (as long as MODE stays high).

With the MODE input remaining high as in these examples. the converter will output the results of every conversion except those completed during a handshake operation. By triggering the converter into handshake mode with a low to high edge on the MODE input, handshake output sequences may be performed on demand. Figure 13 shows a handshake output sequence triggered by such an edge. In addition, the SEN input is shown as being low when the converter enters handshake mode. In this case, the whole output sequence is controlled by the SEN input, and the sequence for the first (high order) byte is similar to the sequence for the other bytes. This diagram also shows the output sequence taking longer than a conversion cycle. Note that the converter still makes conversions, with the STATUS output and Run/Hold input functioning normally. The only difference is that new data will not be latched when in handshake mode, and is therefore lost.

#### **Initial Clear Circuitry**

The internal logic of the 7104 is supplied by an internal regulator between V++ and Digital Ground. The regulator includes a low-voltage detector that will clear various registers. This is intended to ensure that on initial power-up, the control logic comes up in Auto-Zero, with the 2nd, 3rd, and 4th MSB bits cleared, and the "mode" F/F cleared (i.e., in "direct" mode). This, however, will also clear these registers if the supply voltage "glitches" to a low enough value. Additionally, if the supply voltage comes up too fast, this clear pulse may be too narrow for reliable clearing. In general, this is not a problem, but if the UART internal "MODE" F/F should come up set, the byte and chip ENABLE lines will become active outputs. In many systems this could lead to bus conflicts, especially in non-handshake systems. In any case, SEN should be high (held high for non-handshake systems) to ensure that the MODE F/F will be cleared as fast as possible (see Figure 11 for timing). For these and other reasons, adequate supply bypass is recommended.

#### Oscillator

The ICL7104-14 is provided with a versatile three terminal oscillator to generate the internal clock. The oscillator may be overdriven, or may be operated as an RC or crystal oscillator.

Figure 14 shows the oscillator configured for RC operation. The internal clock will be of the same frequency and phase as the voltage on the CLOCK 3 pin. The resistor and capacitor should be connected as shown. The circuit will oscillate at a frequency given by f = 0.45/RC. A 50 -  $100k\Omega$  resistor is recommended for useful ranges of frequency. For optimum 60Hz line rejection, the capacitor value should be chosen such that 32768 (-16), 8192 (-14) clock periods is close to an integral multiple of the 60Hz period.

NOTE: Clock 3 has the same output drive as the bit outputs. FIGURE 14. RC OSCILLATOR (ICL7104-14 ONLY)

As a result of pin count limitations, the ICL7104-16 has only CLOCK 1 and CLOCK 2 available, and cannot be used as an RC oscillator. The internal clock will correspond to the inverse of the signal on CLOCK 2. Figure 15 shows a crystal oscillator circuit, which can be used with both 7104 versions. If an external clock is to be used, it should be applied to CLOCK 1. This internal clock will correspond to the signal applied to this pin.

FIGURE 15. CRYSTAL OSCILLATOR

# **Power Supply Sequencing**

Because of the nature of the CMOS process used to fabricate the ICL7104, and the multiple power supplies used, there are certain conditions of these supplies under which a disabling and potentially damaging SCR action can occur. All of these conditions involve the V+ supply (Norm +5V) being more positive than the V++ supply. If there is any possibility of this occurring during start-up, shut down, under transient conditions during operation, or when inserting a PC board into a "hot" socket, etc., a diode should be placed between V+ and V++ to prevent it. A germanium or Schottky rectifier diode would be best, but in most cases a silicon rectifier is adequate.

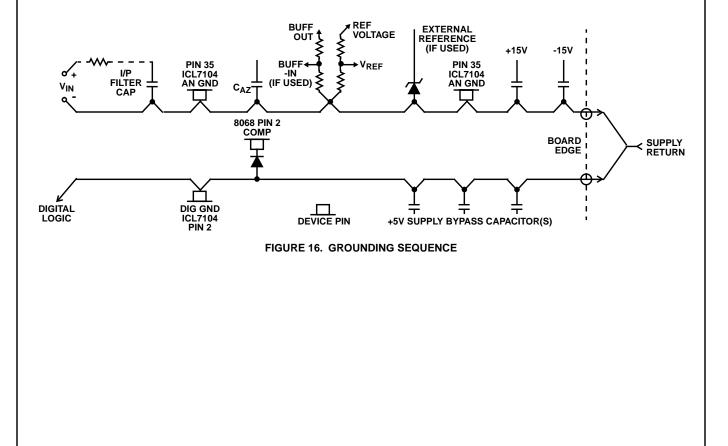

# Analog and Digital Grounds

Extreme care must be taken to avoid ground loops in the layout of ICL8068 or ICL8052/7104 circuits, especially in 16-bit and high sensitivity circuits. It is most important that return currents from digital loads are not fed into the analog ground line. A recommended connection sequence for the ground lines is shown in Figure 16.

# **Application Notes**

Some application notes that may be found useful are listed here:

| NOTE # | DESCRIPTION                                                                           | AnswerFAX<br>DOC. # |

|--------|---------------------------------------------------------------------------------------|---------------------|

| AN016  | "Selecting A/D Converters", by Dave<br>Fullagar                                       | 9016                |

| AN017  | "The Integrating A/D Converter", by Lee Evans                                         | 9017                |

| AN018  | "Do's and Don'ts of Applying A/D<br>Converters," by Peter Bradshaw and Skip<br>Osgood | 9018                |

| AN030  | "Building a Battery-Operated Auto<br>Ranging DVM with the ICL7106"                    | 9030                |

#### ICL7104 with ICL8052/8068 Integrating A/D Converter Equations

Oscillator

$\begin{array}{l} \mbox{CRYSTAL or RC (RC on -14 Part Only)} \\ f_{OSC} (Typ) 200 \mbox{Hz} \\ f_{OSC} = 0.45/\mbox{RC (ICL7104-14 Only)} \\ \mbox{C}_{OSC} > 50 \mbox{F and } \mbox{R}_{OSC} > 50 \mbox{K} \end{array}$

Oscillator Period

$t_{OSC} = 1/f_{OSC}$

Integration Clock Frequency

fclock = fosc

• Integration Period

$t_{INT} = 8192 \times t_{OSC} (7104-14)$  $t_{INT} = 32768 \times t_{OSC} (7104-16)$

60/50Hz Rejection Criterion

t<sub>INT</sub>/t<sub>60Hz</sub> or t<sub>INT</sub>/t<sub>50Hz</sub> = Integer

Optimum Integration Current

$I_{INT} = 20\mu A$

Full Scale Analog Input Voltage

$V_{INFS}$  (Typ) = 200mV to 2V = 2 $V_{REF}$

Integrate Resistor

$\mathsf{R}_{\mathsf{INT}} = \frac{(\mathsf{BufferGain}) \times \mathsf{V}_{\mathsf{INFS}}}{\mathsf{I}_{\mathsf{INT}}}$

Integrate Capacitor

$$C_{INT} = \frac{(t_{INT})(I_{INT})}{V_{INT}}$$

• Integrator Output Voltage

$$V_{INT} = \frac{(t_{INT})(I_{INT})}{C_{INT}}$$

Output Count

Count = 8192×

$$\frac{V_{IN}}{V_{REF}}$$

(7104-14)

Count =  $32768 \times \frac{V_{IN}}{V_{REF}}$  (7104-16)

• Output Type:

Binary Amplitude with Polarity and Overrange Bits.

• Power Supply: ±15V, +5V

V++ = +15V V- = -15V V+ = +5V V<sub>REF</sub>  $\cong$  1.75V If V<sub>REF</sub> not used, float output pin.

• Auto Zero Capacitor Values

$0.01 \mu \mathsf{F} < \mathsf{C}_{\mathsf{AZ}} < 1 \mu \mathsf{F}$

• Reference Capacitor Value

$C_{REF}$  = (Buffer Gain) x  $C_{AZ}$

FIGURE 17.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.