## 16-BIT SYNCHRONOUS 2:1 MUX/DEMUX SWITCH

## IDT74FST163232 ADVANCE INFORMATION

### FEATURES:

- Bus switches provide zero delay paths

- Extended commercial range of -40°C to +85°C

- Low switch on-resistance:

- FST163xxx  $4\Omega$

- TTL-compatible input and output levels

- ESD > 2000V per MIL-STD-883, Method 3015;

> 200V using machine model (C = 200pF, R = 0)

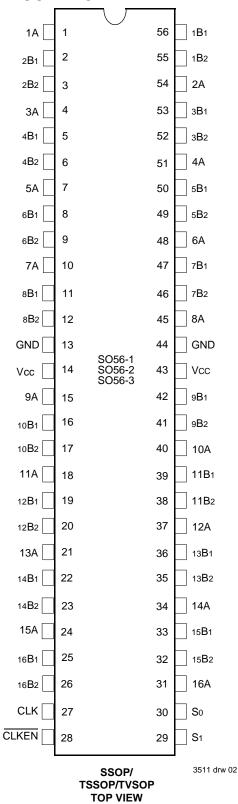

- Available in SSOP, TSSOP and TVSOP

## **DESCRIPTION:**

The FST163232 belong to IDT's family of Bus switches. Bus switch devices perform the function of connecting or isolating two ports without providing any inherent current sink or source capability. Thus they generate little or no noise of their own while providing a low resistance path for an external driver. These devices connect input and output ports through an n-channel FET. When the gate-to-source junction of this FET is adequately forward-biased the device conducts and the resistance between input and output ports is small. Without adequate bias on the gate-to-source junction of the FET, the FET is turned off, therefore with no Vcc applied, the device has hot insertion capability.

The low on-resistance and simplicity of the connection between input and output ports reduces the delay in this path to close to zero.

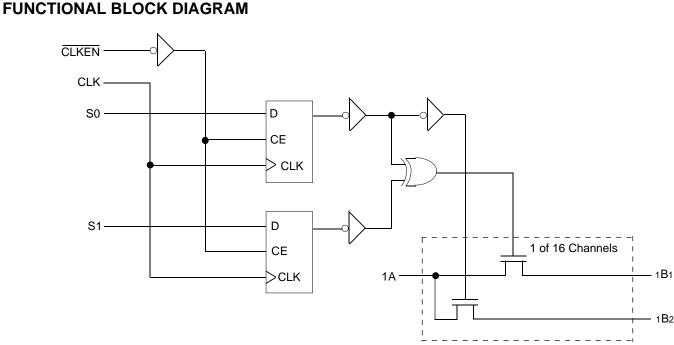

The FST163232 provides three 16-bit TTL- compatible ports that support 2:1 multiplexing. The S0,1 pins control mux select and switch enable/disable. The S0,1 inputs are synchronous and clocked on the rising edge of CLK when CLKEN is low.

Port A can be connected to port B1 or port B2 or both ports B1 and B2.

### **PIN DESCRIPTION**

| Pin Names    | I/O | Description                                |

|--------------|-----|--------------------------------------------|

| A            | I/O | Bus A                                      |

| B1, B2       | I/O | Buses B1, B2                               |

| <b>S</b> 0,1 | I   | Control Pins                               |

| CLK          | I   | Clock Input. Clocks S0,1 on<br>Rising Edge |

| CLKEN        | I   | Clock Enable Input                         |

3511 tbl 01

The IDT logo is a registered trademark of Integrated Device Technology, Inc.

#### **COMMERCIAL TEMPERATURE RANGE**

©1997 Integrated Device Technology, Inc.

1

## PIN CONFIGURATION

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol                                     | Description                          | Max.         | Unit |  |  |  |

|--------------------------------------------|--------------------------------------|--------------|------|--|--|--|

| VTERM <sup>(2)</sup>                       | Terminal Voltage with Respect to GND | -0.5 to +7.0 | V    |  |  |  |

| Tstg                                       | Storage Temperature                  | -65 to +150  | °C   |  |  |  |

| IOUT Maximum Continuous Channel<br>Current |                                      | 128          | mA   |  |  |  |

| NOTES                                      | NOTES: 3511 tbl 02                   |              |      |  |  |  |

NOTES:

1. Stresses greater than those listed under ABSOLUTE MAXIMUM RAT-INGS may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating condiitions for extended periods may affect reliability.

2. Vcc, Control and Switch terminals.

## CAPACITANCE<sup>(1)</sup>

| Symbol                                  | Parameter                 | Conditions <sup>(2)</sup> | Тур. | Unit |

|-----------------------------------------|---------------------------|---------------------------|------|------|

| CIN                                     | Control Input Capacitance |                           | 4    | pF   |

| CI/O Switch Input/Output<br>Capacitance |                           | Switch Off                |      | pF   |

| NOTES: 3511 tbl 0                       |                           |                           |      |      |

NOTES:

1. Capacitance is characterized but not tested

2. TA = 25°C, f = 1MHz, VIN = 0V, VOUT = 0V

### **FUNCTION TABLE**

| So | CLK                                | CLKEN                                                                                                       | Description                                                                                                                                                                                                    |

|----|------------------------------------|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Х  | Х                                  | Н                                                                                                           | Last state                                                                                                                                                                                                     |

| L  | $\uparrow$                         | L                                                                                                           | Disconnect                                                                                                                                                                                                     |

| Н  | $\uparrow$                         | L                                                                                                           | A to B1 and A to B2                                                                                                                                                                                            |

| L  | $\uparrow$                         | L                                                                                                           | A to B1 or B1 to A                                                                                                                                                                                             |

| Н  | $\uparrow$                         | L                                                                                                           | A to B2 or B2 to A                                                                                                                                                                                             |

|    | <b>S0</b><br>X<br>L<br>H<br>L<br>H | S₀      CLK        X      X        L      ↑        H      ↑        L      ↑        H      ↑        H      ↑ | S₀      CLK      CLKEN        X      X      H        L      ↑      L        H      ↑      L        H      ↑      L        H      ↑      L        H      ↑      L        H      ↑      L        H      ↑      L |

511 tbl 04

## DC ELECTRICAL CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified: Commercial: TA =  $-40^{\circ}$ C to  $+85^{\circ}$ C, VCC =  $5.0V \pm 10\%$

| Symbol | Parameter                           | Test Conditions <sup>(1)</sup>           |              | Min. | Typ. <sup>(2)</sup> | Max. | Unit     |

|--------|-------------------------------------|------------------------------------------|--------------|------|---------------------|------|----------|

| Vih    | Input HIGH Voltage                  | Guaranteed Logic HIGH for Control Inputs |              | 2.0  | _                   | -    | V        |

| VIL    | Input LOW Voltage                   | Guaranteed Logic LOW for Co              | ntrol Inputs | _    | —                   | 0.8  | V        |

| Іін    | Input HIGH Current                  | Vcc = Max.                               | VI = VCC     | _    | _                   | ±1   | μΑ       |

| lı∟    | Input LOW Voltage                   |                                          | VI = GND     | _    | —                   | ±1   |          |

| lozн   | High Impedance Output Current       | Vcc = Max.                               | Vo = Vcc     | _    | _                   | ±1   | μΑ       |

| Iozl   | (3-State Output pins)               |                                          | Vo = GND     | _    | _                   | ±1   |          |

| los    | Short Circuit Current               | Vcc = Max., Vo = GND <sup>(3)</sup>      |              | _    | 300                 | _    | mA       |

| Vik    | Clamp Diode Voltage                 | Vcc = Min., IIN = -18mA                  |              | _    | -0.7                | -1.2 | V        |

| Ron    | Switch On Resistance <sup>(4)</sup> | Vcc = Min. VIN = 0.0V                    |              | —    | 4                   | 7    | Ω        |

|        |                                     | ION = 64mA                               |              |      |                     |      |          |

|        |                                     | VCC = Min. VIN = 0.0V                    |              | —    | 4                   | 7    | Ω        |

|        |                                     | ION = 32mA                               |              |      |                     |      |          |

|        |                                     | Vcc = Min. VIN = 2.4V                    |              | _    | 6                   | 15   | Ω        |

|        |                                     | ION = 15mA                               |              |      |                     |      |          |

| IOFF   | Input/Output Power Off Leakage      | Vcc = 0V, VIN or Vo $\leq 4.5$ V         |              | _    | —                   | ±1   | μΑ       |

| Icc    | Quiescent Power Supply Current      | Vcc = Max., VIN = GND or Vcc             |              | _    | 0.1                 | 3    | μA       |

| TES:   | -                                   | ·                                        |              |      | -                   |      | 3511 tbl |

NOTES:

1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.

2. Typical values are at Vcc = 5.0V, +25°C ambient.

3. Not more than one output should be tested at one time. Duration of the test should not exceed one second.

4. Measured by voltage drop between ports at indicated current through the switch.

### **POWER SUPPLY CHARACTERISTICS**

| Symbol | Parameter                                         | Test Con                                                            | ditions <sup>(1)</sup> | Min. | Typ. <sup>(2)</sup> | Max. | Unit                  |

|--------|---------------------------------------------------|---------------------------------------------------------------------|------------------------|------|---------------------|------|-----------------------|

| ∆lcc   | Quiescent Power Supply Current<br>TTL Inputs HIGH | Vcc = Max.<br>$VIN = 3.4V^{(3)}$                                    |                        |      | 0.5                 | 1.5  | mA                    |

| ICCD   | Dynamic Power Supply<br>Current <sup>(4)</sup>    | Vcc = Max.<br>Outputs Open<br>Enable Pin Toggling<br>50% Duty Cycle | VIN = VCC<br>VIN = GND | _    | 30                  | 40   | μΑ/<br>MHz/<br>Switch |

| Ic     | Total Power Supply Current <sup>(6)</sup>         | Vcc = Max.<br>Outputs Open<br>CLK Pin Toggling                      | VIN = VCC<br>VIN = GND | —    | 4.8                 | 6.4  | mA                    |

|        |                                                   | (16 Switches Toggling)<br>fi = 10MHz<br>50% Duty Cycle              | VIN = 3.4<br>VIN = GND |      | 5.1                 | 7.2  |                       |

3511 tbl 06

NOTES:

1. For conditions shown as Max. or Min., use appropriate value specified under Electrical Characteristics for the applicable device type.

- 2. Typical values are at Vcc = 5.0V, +25°C ambient.

- 3. Per TTL driven input ( $V_{IN} = 3.4V$ ). All other inputs at Vcc or GND.

4. This parameter is not directly testable, but is derived for use in Total Power Supply Calculations.

- 5. Values for these conditions are examples of the lcc formula. These limits are guaranteed but not tested.

- 6. IC = IQUIESCENT + INPUTS + IDYNAMIC

$IC = ICC + \Delta ICC DHNT + ICCD (fiN)$

Icc = Quiescent Current

$\Delta$ Icc = Power Supply Current for a TTL High Input (VIN = 3.4V)

DH = Duty Cycle for TTL Inputs High

NT = Number of TTL Inputs at DH

ICCD = Dynamic Current Caused by an Input Transition Pair (HLH or LHL)

fi = Input Frequency

N = Number of Switches Toggling at fi

All currents are in milliamps and all frequencies are in megahertz.

### SWITCHING CHARACTERISTICS OVER OPERATING RANGE

Following Conditions Apply Unless Otherwise Specified:

#### Commercial: TA = $-40^{\circ}$ C to $+85^{\circ}$ C, VCC = 5.0V $\pm 10\%$

| Symbol        | Description                                             | Condition <sup>(1)</sup> | Min. <sup>(2)</sup> | Тур. | Max. | Unit |

|---------------|---------------------------------------------------------|--------------------------|---------------------|------|------|------|

| <b>t</b> PLH  | Data Propagation Delay                                  | CL = 50pF                |                     | _    | 0.25 | ns   |

| <b>t</b> PHL  | A to B, B to A <sup>(3,4)</sup>                         | RL = 500Ω                |                     |      |      |      |

| tCEWS         | Clock Enable Set-Up Time                                |                          |                     | —    | —    | ns   |

|               | CLKEN to CLK Low-to-High                                |                          |                     |      |      |      |

| <b>t</b> CENH | Clock Enable Hold Time                                  |                          |                     | —    | —    | ns   |

|               | CLKEN to CLK Low-to-High                                |                          |                     |      |      |      |

| tBX           | Switch Multiplex Delay                                  |                          | 1.5                 | _    | 6.5  | ns   |

|               | CLK to A, B                                             |                          |                     |      |      |      |

| <b>t</b> PZH  | Switch Turn on Delay                                    |                          | 1.5                 | _    | 6.5  | ns   |

| tPZL          | CLK to A, B                                             |                          |                     |      |      |      |

| tPHZ          | Switch Turn off Delay                                   |                          | 1.5                 | _    | 7    | ns   |

| tPLZ          | CLK to A, B                                             |                          |                     |      |      |      |

| Qci           | Charge Injection, Typical <sup>(5,7)</sup>              |                          |                     | 1.5  | —    | рС   |

| QDCI          | Differential Charge Injection, Typical <sup>(6,7)</sup> |                          | _                   | 0.5  |      |      |

3511 tbl 07

NOTES:

1. See test circuit and waveforms.

2. Minimum limits guaranteed but not tested.

3. This parameter is guaranteed by design but not tested.

4. The bus switch contributes no propagation delay other than the RC delay of the on resistance of the switch and the load capacitance. The time constant for the switch alone is of the order of 2.5ns for 50pF load. Since this time is constant and much smaller than the rise/fall times of typical driving signals, it adds very little propagation delay to the system. Propagation delay on the bus switch when used in a system is determined by the driving circuit on the driving side of the switch and its interaction with the load on the driven side.

5. Measured at switch turn off, load = 50 pF in parallel with 10 M $\Omega$  scope probe, VIN = 0.0 volts.

6. Measured at switch turn off through bus multiplexer, (e.g. - A to B1 = >A to B2), load = 50 pF in parallel with 10 MΩ scope probe, VIN at A = 0.0 volts. Charge injection is reduced because the injection from the turn off of the A to B1 switch is compensated by the turn on of the A to B2 switch.

7. Characterized parameter. Not 100% tested.

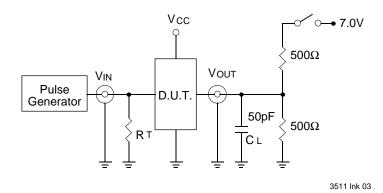

## **TEST CIRCUITS AND WAVEFORMS TEST CIRCUITS FOR ALL OUTPUTS**

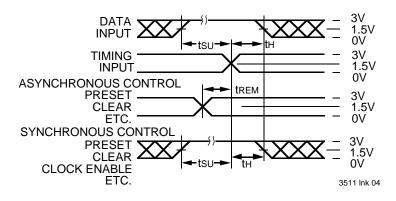

## SET-UP, HOLD AND RELEASE TIMES

## SWITCH POSITION

| Test                      | Switch      |

|---------------------------|-------------|

| Open Drain<br>Disable Low | Closed      |

| Enable Low                |             |

| All Other Tests           | Open        |

| DEFINITIONS               | 3511 lnk 08 |

#### **DEFINITIONS:**

CL= Load capacitance: includes jig and probe capacitance.

RT = Termination resistance: should be equal to ZOUT of the Pulse Generator.

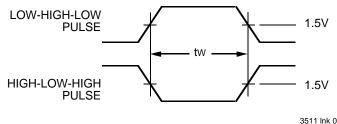

## **PULSE WIDTH**

3511 lnk 05

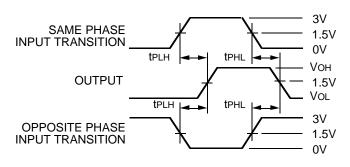

### **PROPAGATION DELAY**

3511 lnk 06

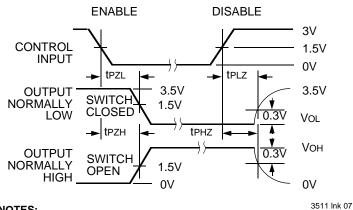

## ENABLE AND DISABLE TIMES

#### NOTES:

1. Diagram shown for input Control Enable-LOW and input Control Disable-HIGH

2. Pulse Generator for All Pulses: Rate  $\leq$  1.0MHz: tF  $\leq$  2.5ns: tR  $\leq$  2.5ns

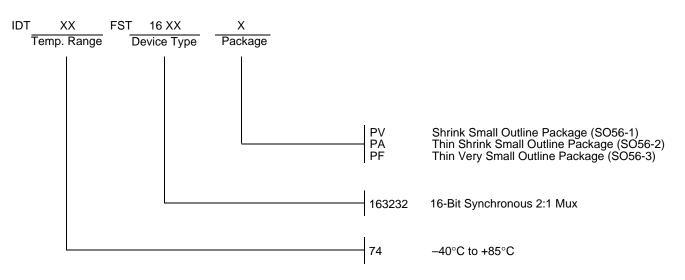

### **ORDERING INFORMATION**

3511 ldrw 08

Integrated Device Technology, Inc. reserves the right to make changes to the specifications in this data sheet in order to improve design or performance and to supply the best possible product.

# **Integrated Device Technology, Inc.**

2975 Stender Way, Santa Clara, CA 95054-3090

Telephone: (408) 727-6116

FAX 408-492-8674