### Dual stage IF amplifier for cable tuners

#### Features

- Single chip solution for tuner IF gain and AGC

- Contains 34 dB of AGC shared between two AGC stages

- Design optimised for high signal handling with low inter-modulation spurious generation

- I/O ports optimised to interface with standard SAW filters

- ESD protection (Normal ESD handling procedures should be observed)

### **Applications**

- Cable Network interface modules and tuners

- Data communications systems

### Description

The SL2009 is a dual IF amplifier intended for application in cable tuners, and integrates all of the IF gain and AGC required to deliver 1Vp-p in a standard tuner configuration.

DS5507

SL2009

March 2002

### ISSUE 1.4 Ordering Information

SL2009/KG/NP1T (Tape and Reel) SL2009/KG/NP1S (Tubes)

The devices includes two stages of IF gain which are both optimised to interface with inter-stage filters. Both stages contain independent AGC facility, and the first stage contains a level detect for control of the tuner AGC.

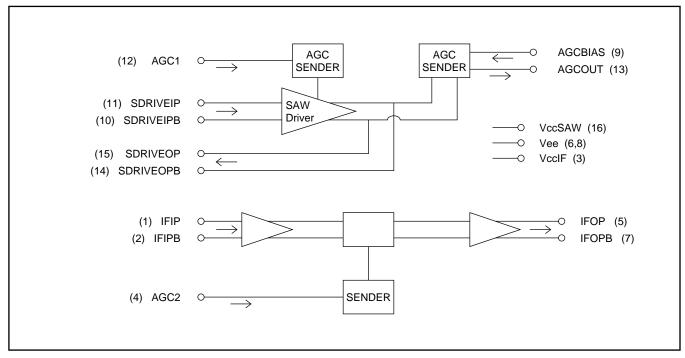

Figure 2 - Block diagram

| Characteristics                    |         | Units |

|------------------------------------|---------|-------|

| SAWF driver stage                  |         |       |

| Input operating range              | 30 - 50 | MHz   |

| Input NF, referred to $2k\Omega$   | 4       | dB    |

| OPIP3                              | 4       | dBV   |

| Gain                               | 14 - 28 | dB    |

| IF Amplifier stage                 |         |       |

| Input operating range              | 30 - 50 | MHz   |

| Input NF, referred to 2 k $\Omega$ | 6       | dB    |

| OPIP3                              | 8       | dBV   |

| Gain                               | 20 - 40 | dB    |

Table 1 - Quick reference data

### **Functional Description**

The SL2009 is an IF amplifier intended primarily for application in cable tuners, and requiring a minimum external component count to integrate the IF gain, AGC facility and level detect.

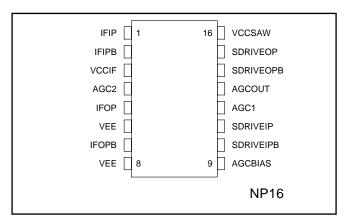

The pin allocation is contained in figure (1) and the block diagram in figure (2)

### SAWF driver stage

In normal application the IF output of the tuner, which is typically in the region of 30-50 MHz, is interfaced to input preamplifier of the SAWF driver stage, which is optimised for both signal handling and NF referred to 2 k $\Omega$ .

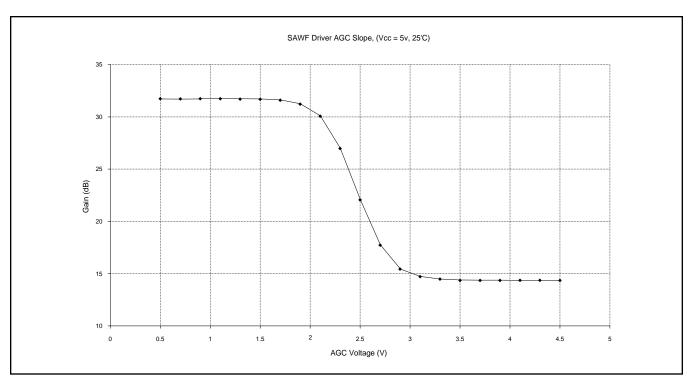

The input preamplifier interfaces with the variable gain stage, which is under control of the first AGC sender and provides for 14 dB of gain control. The typical gain characteristic is contained in figure (3).

The AGC stage then interfaces with the output buffer amplifier, which presents a balanced 50  $\Omega$  drive to the IF SAW filter and offers high signal handling to minimise intermodulation distortions.

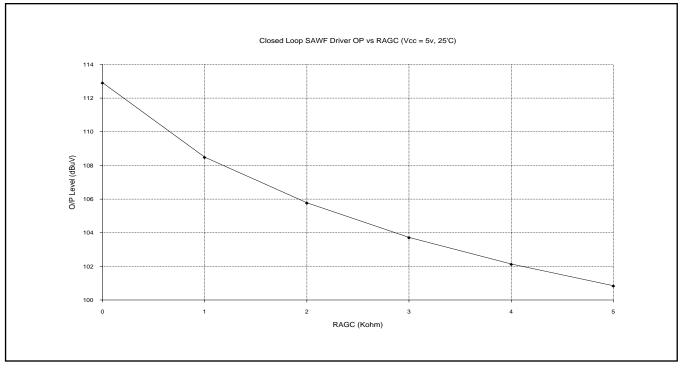

The SAWF amplifier also incorporates a level detect block whose output AGCOUT, can be used to control the gain of the SAWF amplifier or other gain stages in front of the SL2009. This AGC characteristic can be set up by a "current set" resistor connected between the AGCBIAS input and Vee. The typical characteristic curve for AGC set, output level under different AGCBIAS conditions is contained in figure (4).

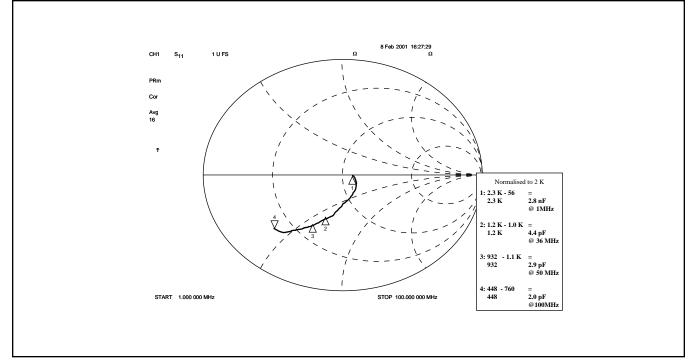

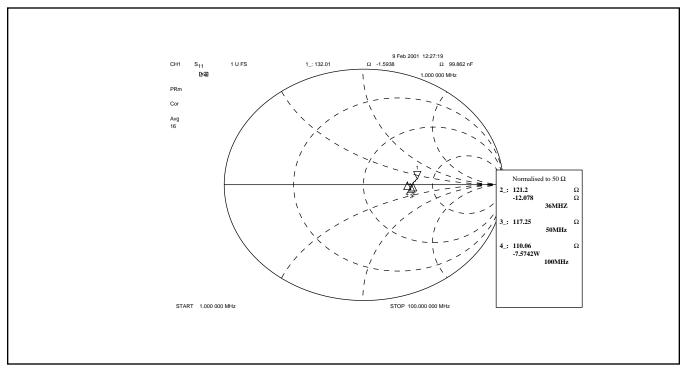

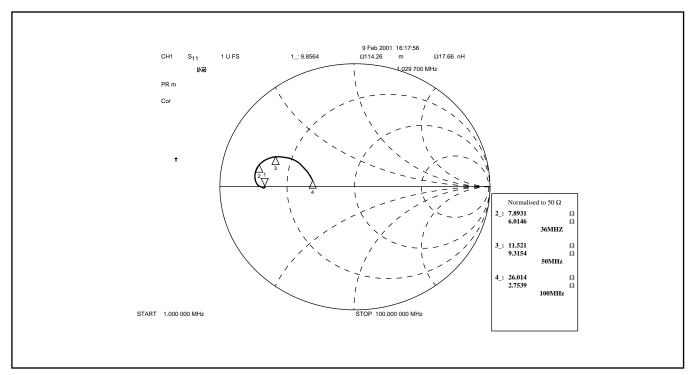

See figures (5) and (6) for SAW amplifier input and output impedances respectively.

### IF amplifier section

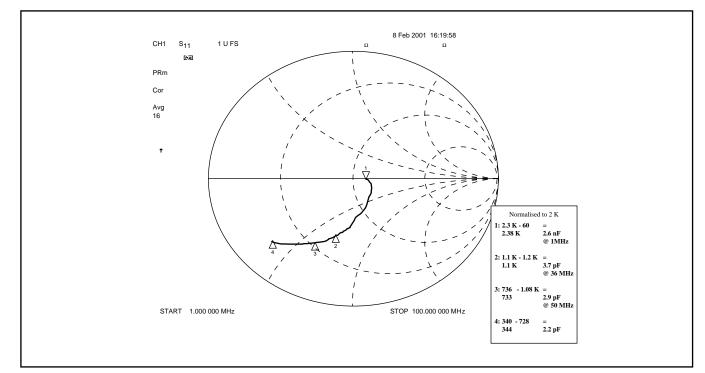

In normal application the output of the SAW filter is coupled differentially to the input preamplifier of the IF amplifier, which presents a differential 2 k $\Omega$  3 pF load to the SAW filter and is optimised for both signal handling and NF. See figure (8) for IF amplifier input impedance.

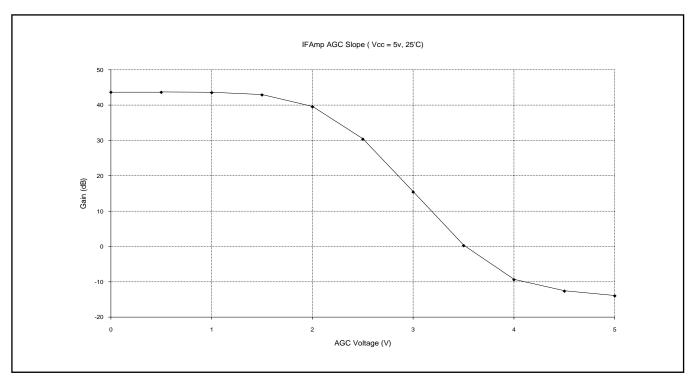

The input preamplifier, then interfaces with the variable gain stage which is under control of the second AGC sender and this provides for 20 dB of gain control. The typical AGC characteristic is contained in figure (7)

The AGC output is then connected to the output driver stage, which presents a low differential output impedance, see figure (9) and is optimised for output signal handling.

The typical key performance data at 5V Vcc and 25 deg C ambient are shown in the table entitled 'QUICK REFERENCE DATA'.

Figure 3 - Typical SAWF driver stage AGC characteristic

Figure 4 - AGCOUT characteristic versus AGCBIAS resistor

Figure 5 - Typical SAWF driver input impedance, single-ended

Figure 6 - Typical SAWF driver output impedance, single-ended

4

Figure 7 - Typical IF amplifier stage AGC characteristic

## SL2009

Figure 8 - Typical IF amplifier input impedance, single-ended

Figure 9 - Typical IF amplifier output impedance, single-ended

### **Electrical Characteristics**

#### Test conditions (unless otherwise stated)

Tamb = -40° to 85°C,  $V_{ee}$ = 0V,  $V_{cc}IF$  = 5V+-5%,  $V_{cc}SAW$  =5V+-5% These characteristics are guaranteed by either production test or design. They apply within the specified ambient temperature and supply voltage unless otherwise stated.

| Characteristics                     | pin   | min         | typ | max      | units    | Conditions                                                                                                            |

|-------------------------------------|-------|-------------|-----|----------|----------|-----------------------------------------------------------------------------------------------------------------------|

| Supply current                      | 3,16  |             | 50  | 70       | mA       | Pin (3) VccIF and pin (16)<br>VccSAW are isolated on<br>chip.                                                         |

| Operating frequency                 |       | 30          |     | 50       | MHz      |                                                                                                                       |

| Gain Flatness                       |       |             |     | 1dB      |          | Over specified output range.<br>Excluding SAW filter<br>contributions. 8MHz B/W.<br>See note (4)                      |

| SAWF driver                         |       |             |     |          |          |                                                                                                                       |

| Input impedance                     | 10,11 |             | 2   |          | kΩ       | Differential, see figure (5)                                                                                          |

|                                     |       |             | 3   |          | pF       |                                                                                                                       |

| Noise Figure                        |       |             | 4   | 6        | dB       | Tamb=27 °C, referred to source impedance of 2 k $\Omega$ conversion gain set at 28 dB                                 |

| Variation in NF with gain<br>adjust |       |             |     | -1       | dB/dB    |                                                                                                                       |

| Output referred IP3                 |       | 3           |     |          | dBV      | Over specified gain range, see note (1) and (4)                                                                       |

| Gain                                |       |             |     |          |          | Voltage conversion gain from 2 k $\Omega$ differential source to 1 k $\Omega$ //10 pF single-ended load, see note (4) |

| Maximum<br>Minimum                  |       | 25.5<br>8.5 |     | 32<br>15 | dB<br>db | Vagc1=1.5V<br>Vagc1=3.5V<br>AGC monotonic from $V_{ee}$ to<br>V <sub>cc</sub> . See Figure (3)                        |

| Output impedance                    | 14,15 |             | 50  |          | Ω        | Single-ended, see figure (6)                                                                                          |

| Output return loss                  | 14,15 |             | 9   |          | dB       |                                                                                                                       |

| Output limiting                     | 14,15 | 1.8         |     |          | Vp-p     | Single-ended into 1 k $\Omega$ // 10 pF load 3 <sup>rd</sup> Harmonic of wanted output signal better than 10dBC.      |

| AGC1 Leakage current                | 12    | -110        |     | 110      | μA       | Vee<=Vagc1<=V <sub>cc</sub>                                                                                           |

|                                     |       | -50         |     | 50       | μA       | 1.5V<=Vagc1<=3.5V                                                                                                     |

| AGCOUT charging current             | 13    | 150         | 200 | 350      | μA       | Source and sink                                                                                                       |

| AGCOUT voltage range                | 13    | 0.5         |     | 3.5      | V        | See note (3), max load<br>current 50 μA                                                                               |

| AGC output level set                |       |             |     |          |          | See figure (4)                                                                                                        |

**Table 2 - Electrical Characteristics**

# SL2009

| Characteristics                     | pin | min  | typ | max | units | Conditions                                                                                                                           |

|-------------------------------------|-----|------|-----|-----|-------|--------------------------------------------------------------------------------------------------------------------------------------|

| IF amplifier                        |     |      |     |     |       |                                                                                                                                      |

| Input impedance                     | 1,2 |      | 2   |     | kΩ    | Differential, see figure (8)                                                                                                         |

|                                     |     |      | 3   |     | pF    |                                                                                                                                      |

| Noise Figure                        |     |      | 4   | 6   | dB    | Tamb=27°C, referred to source impedance of 2 k $\Omega$ conversion gain set at 40 dB                                                 |

| Variation in NF with gain<br>adjust |     |      |     | -1  | dB/dB |                                                                                                                                      |

| Output referred IP3                 | 5,7 | 5    |     |     | dBV   | With gains of 24dB and above, see note (2)                                                                                           |

|                                     |     | 4    |     |     | dBV   | With gains from 20dB to 24dB, see note (2)                                                                                           |

| Gain                                |     |      |     |     |       | Voltage conversion gain from 2 k $\Omega$ differential source to 1 k $\Omega$ // 15 pF single-ended load, see figure (7)             |

| Maximum                             |     | 38   |     |     | dB    | Vagc2=1.0V                                                                                                                           |

| Minimum                             |     |      |     | 20  | dB    | Vagc2=4.25V                                                                                                                          |

|                                     |     |      |     |     |       | AGC monotonic from $V_{ee}$ to $V_{cc}$                                                                                              |

| Output impedance                    | 5,7 |      |     | 25  | Ω     | Single-ended, see figure (9)                                                                                                         |

| Output limiting                     | 5,7 | 1.8  |     |     | Vp-p  | Single-ended into to $1 \text{ k}\Omega \text{ //} 15 \text{ pF}$ load. $3^{rd}$ Harmonic of wanted output signal better than 10dBC. |

| AGC2 leakage current                | 4   | -110 |     | 110 | μA    |                                                                                                                                      |

Table 2 - Electrical Characteristics (continued)

### Notes:

- (1) Two output tones at 104  $dB\mu V$  within operating range

- (2) Two output tones at 108  $dB\mu V$  within operating range

- (3) When controlling external AGC the current load on AGCOUT should be minimised

- (4) For maximum performance, capacitive load should be resonated with appropriate inductance at chosen IF frequency.

Absolute Maximum Ratings

All voltages are referred to Vee at 0V, and VccIF=VccSAW

### **Absolute Maximum Ratings**

All voltages are referred to  $V_{ee}$  at 0V, and  $V_{cc}\text{IF=VccSAW}$

| Characteristics                             | min  | max     | units | conditions                       |

|---------------------------------------------|------|---------|-------|----------------------------------|

| Supply voltage                              | -0.3 | 7       | V     |                                  |

| All I/O port DC offsets                     | -0.3 | Vcc+0.3 | V     |                                  |

| Storage temperature                         | -55  | 150     | °C    |                                  |

| Junction temperature                        |      | 150     | °C    |                                  |

| Package thermal resistance, chip to case    |      | 32.2    | °C    |                                  |

| Package thermal resistance, chip to ambient |      | 108.1   | °C/W  |                                  |

| Power consumption at 5.25V                  |      | 368     | mW    |                                  |

| ESD protection                              | 2    |         | kV    | Mil-std 883B method 3015<br>cat1 |

Table 3 - Absolute Maximum Ratings

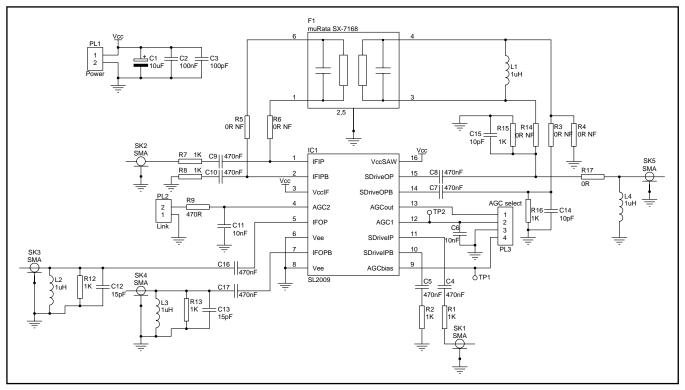

Figure 10 - Evaluation Board Schematic

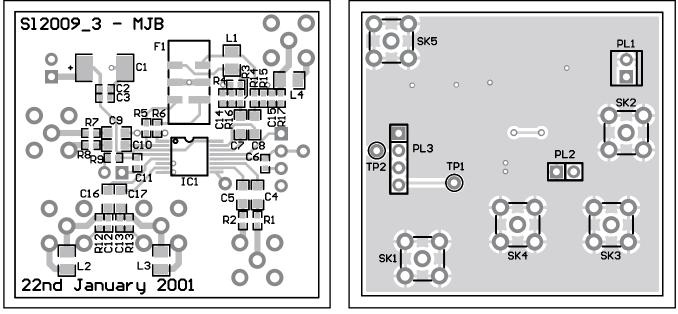

Figure 11 - Top Layout

Figure 12 - Bottom Layout

Notes:

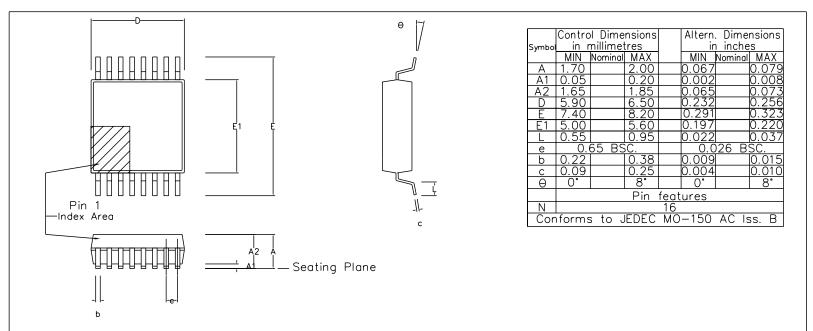

- 1. A visual index feature, e.g. a dot, must be located within the cross-hatched area.

- 2. Controlling dimension are in millimeters.

- Dimensions D and E1 do not include mould flash or protusion. Mould flash or protusion shall not exceed 0.20 mm per side. D and E1 are maximum plastic body size dimensions including mould mismatch.

Dimension b does not include dambar protusion/intrusion. Allowable dambar protusion shall be 0.13 mm total in excess of b dimension. Dambar intrusion shall not reduce dimension b by more than 0.07 mm.

| © Zarlink Semiconductor 2002 All rights reserved. |         |         | ts reserved. |         |               |                        | Package Code                       |  |

|---------------------------------------------------|---------|---------|--------------|---------|---------------|------------------------|------------------------------------|--|

| ISSUE                                             | 1       | 2       | 3            | 4       |               | Previous package codes | Package Outline for                |  |

| ACN                                               | 201031  | 201932  | 205235       | 212434  | SEMICONDUCTOR | NP / N                 | 16 lead SSOP<br>(5.3MM Body Width) |  |

| DATE                                              | 10Sep96 | 27Feb97 | 25Sep98      | 25Mar02 |               |                        |                                    |  |

| APPRD.                                            |         |         |              |         |               |                        | GPD00140                           |  |

# For more information about all Zarlink products visit our Web Site at

### www.zarlink.com

Information relating to products and services furnished herein by Zarlink Semiconductor Inc. or its subsidiaries (collectively "Zarlink") is believed to be reliable. However, Zarlink assumes no liability for errors that may appear in this publication, or for liability otherwise arising from the application or use of any such information, product or service or for any infringement of patents or other intellectual property rights owned by third parties which may result from such application or use. Neither the supply of such information or purchase of product or service conveys any license, either express or implied, under patents or other intellectual property rights owned by Zarlink or licensed from third parties by Zarlink, whatsoever. Purchasers of products are also hereby notified that the use of product in certain ways or in combination with Zarlink, or non-Zarlink furnished goods or services may infringe patents or other intellectual property rights owned by Zarlink.

This publication is issued to provide information only and (unless agreed by Zarlink in writing) may not be used, applied or reproduced for any purpose nor form part of any order or contract nor to be regarded as a representation relating to the products or services concerned. The products, their specifications, services and other information appearing in this publication are subject to change by Zarlink without notice. No warranty or guarantee express or implied is made regarding the capability, performance or suitability of any product or service. Information concerning possible methods of use is provided as a guide only and does not constitute any guarantee that such methods of use will be satisfactory in a specific piece of equipment. It is the user's responsibility to fully determine the performance and suitability of any equipment using such information and to ensure that any publication or data used is up to date and has not been superseded. Manufacturing does not necessarily include testing of all functions or parameters. These products are not suitable for use in any medical products whose failure to perform may result in significant injury or death to the user. All products and materials are sold and services provided subject to Zarlink's conditions of sale which are available on request.

Purchase of Zarlink's I<sup>2</sup>C components conveys a licence under the Philips I<sup>2</sup>C Patent rights to use these components in and I<sup>2</sup>C System, provided that the system conforms to the I<sup>2</sup>C Standard Specification as defined by Philips.

Zarlink, ZL and the Zarlink Semiconductor logo are trademarks of Zarlink Semiconductor Inc.

Copyright Zarlink Semiconductor Inc. All Rights Reserved.

TECHNICAL DOCUMENTATION - NOT FOR RESALE