### Eight-Channel Programmable DC-DC Power Managers with Battery Charger

### **FEATURES & APPLICATIONS**

- Digital programming of all major parameters via I<sup>2</sup>C interface and non-volatile memory

- Output voltage setpoint/margining

- Sequencing & digital soft start

- o Enable/Disable outputs independently

- o Input/Output UV/OV voltage thresholds

- PWM/PFM mode

- · Eight programmable regulator channels

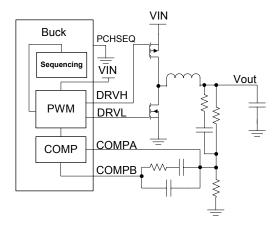

- Three synchronous step-down (Buck) with internal PFETs

- One configurable step-up (Boost) or synchronous stepdown (Buck)

- o Two step-up (Boost)

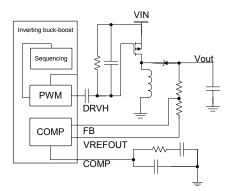

- One configurable step-up (Boost) or inverting stepup/down (Buck-Boost)

- One adjustable output voltage LDO

- Programmable Linear Li-Ion Battery Charger

- Precharge/fast charge/termination current

- Fast Charge voltage threshold

- Float Voltage

- +2.7V to +6.0V Input Range (Higher system voltages supported)

- Built-in current limiting, UV/OV, and thermal protection

- Highly accurate reference and output voltage (<1.5%)

- 1MHz PWM frequency and automatic power-saving PFM mode

- 96 bytes of user configurable nonvolatile memory

### **Applications**

- Portable Media Players

- · Digital camcorders/still cameras

- Smart PDA/Camera phones

- Handheld GPS/PDAs

- Portable Equipment

### INTRODUCTION

The SMB122 and SMB122X are highly integrated and flexible eight-channel power managers designed for use in a wide range of portable applications. The built-in digital programmability allows system designers to custom tailor the device to suit almost any multi-channel power supply application from digital camcorders to mobile phones.

The SMB122 and SMB122X integrate all the essential blocks required to implement a complete eight-channel power subsystem including three synchronous step-down "Buck" converters, one configurable step-up "Boost" or step-down synchronous "Buck" converter, two step-up (Boost) converters, one configurable step-up "Boost" or inverting step-up/down "Buck-Boost" converter, one linear regulator (LDO) and a fully programmable Li-lon battery charger.

Additionally sophisticated power control/monitoring functions required by complex systems are built-in. These include digitally programmable output voltage setpoint, power-up/down sequencing, enable/disable, margining, dynamic voltage management, and UV/OV input/output monitoring on all channels. By incorporating a second ENABLE input and 7-level dynamic voltage control, the SMB122X is ideal for powering systems based on Xscale TM and other similar processors.

The integration of features and built-in flexibility of the SMB122 and SMB122X allows the system designer to create a "platform solution" that can be easily modified via software without major hardware changes. Combined with the re-programmability of the SMB122 and SMB122X, this facilitates rapid design cycles and proliferation from a base design to futures generations of product.

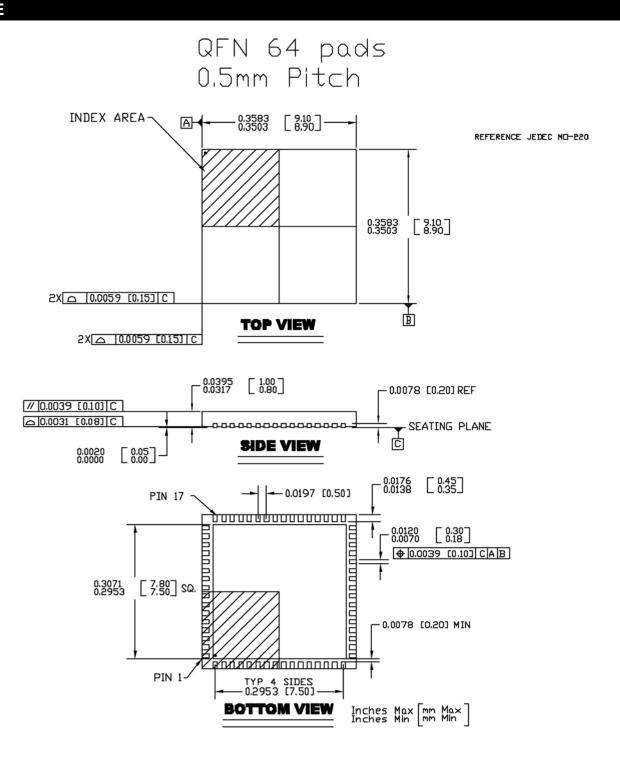

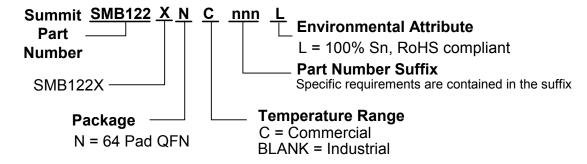

The SMB122 and SMB122X are suited to battery-powered applications with an input range of +2.7V to +6.0V and provide a very accurate voltage regulation (<1.5%, typical). Communication is accomplished via the industry standard  $\rm l^2C$  bus. All user-programmed settings are stored in non-volatile EEPROM of which 96 bytes may be used for general-purpose memory applications. The commercial operating temperature range is 0C to +70C, the industrial operating range is - 40C to +85C, and the available package is a 64-pad 9mm x 9mm QFN.

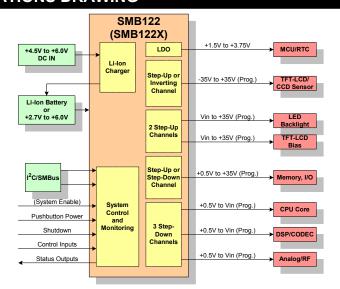

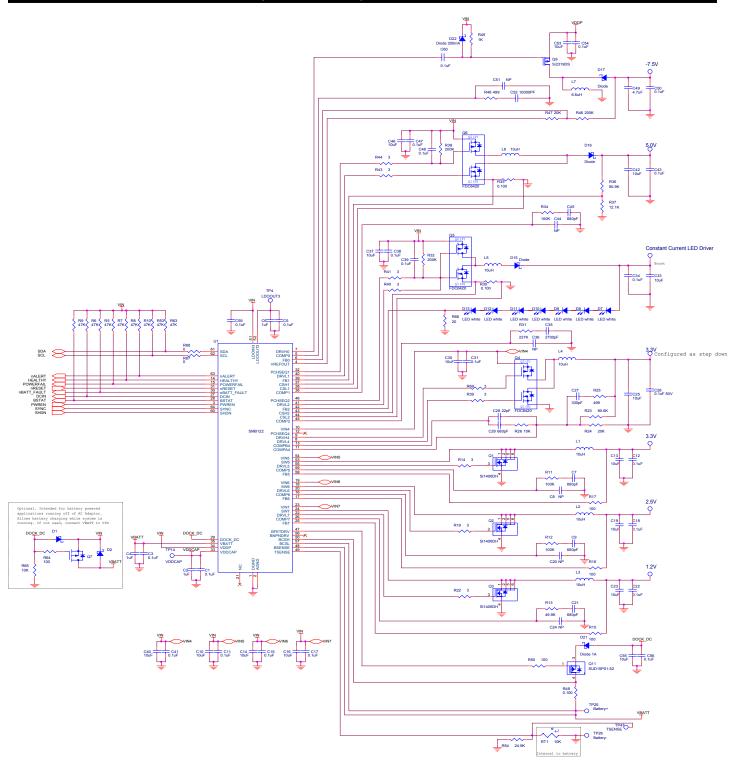

### SIMPLIFIED APPLICATIONS DRAWING

Figure 1 – Applications block diagram featuring the SMB122/X eight-channel, programmable DC/DC converters. This integrated power supply and battery manager provides precision regulation, monitoring, cascade sequencing, output margining and battery charging.

### **GENERAL DESCRIPTION**

The SMB122 and SMB122X are fully-programmable power supply and battery managers that regulate, sequence, monitor, and margin, an entire power subsystem while controlling the charging of a lithium-ion battery pack. They have 8 voltage outputs, consisting of: three synchronous PWM "Buck" step-down converters, one configurable PWM "Boost or Buck" converter, two "Boost" step-up converters, one configurable PWM "Boost" step-up or inverting "Buck-Boost" converter, one Low Dropout (LDO) linear regulator, and a fully programmable Li-lon battery charger.

The SMB122 and SMB122X regulate each of the eight output channels to an accuracy of  $\pm 1.5\%$  (typical). The output is individually programmed and can be reprogrammed via the I²C interface. In addition, several sophisticated power management functions are built-in. The SMB122 and SMB122X are capable of power-on/off cascade sequencing where each channel can be assigned one of eight sequence positions. Supplies may also be individually powered on/off through an I²C command or by assertion of one or two (for SMB122X) general purpose enable pins. Cascade sequencing, unlike time based sequencing, uses feedback to ensure that each output is valid before the next channel is enabled.

Each output voltage and the battery are monitored for under-voltage and over-voltage conditions, using a comparator based scheme. In the event of a fault, all supplies may be sequenced down or immediately disabled. Multiple output status pins are provided to notify host processors or other supervisory circuits of system faults.

The SMB122 and SMB122X feature an Under-voltage Lockout (UVLO) circuit to ensure the IC will not power up until the battery voltage has reached a safe operating voltage. The UVLO function exhibits hysteresis, ensuring that noise on the supply rail does not inadvertently cause faults on the internally regulated supply.

In the event of a system fault, all monitored supplies may trigger fault actions such as power-off, or force-shutdown operations. Each output on the SMB122 and SMB122X may also be turned off individually at any point through an I<sup>2</sup>C command or by a programmable enable pin.

When used in portable applications, the SMB122 and SMB122X are powered from the main system battery. This input is continuously monitored for under-voltage conditions.

There are two under-voltage settings for this supply; both are user programmable and have a corresponding status pin. When the first threshold level is reached, the POWER\_FAIL pin is asserted and latched. When the second threshold level is reached on the main supply, the nBATT FAULT pin is asserted.

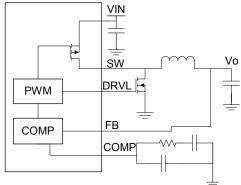

The SMB122 and SMB122X are equipped with three synchronous Buck outputs and one "Buck-or-Boost" output that use a 1000kHz oscillator frequency. The feedback circuitry on each step-down channel is simplified by an internal programmable resistor divider (Buck-or-Boost uses external resistor divider).

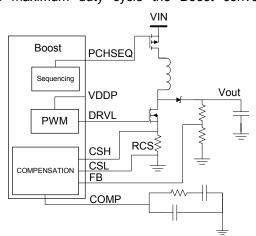

The SMB122 and SMB122X are equipped with two Boost outputs and an inverting Buck-Boost output. Each Boost output uses a 1000kHz oscillator, and an asynchronous topology reducing the necessity for an additional external MOSFET driver. All Boost outputs use an external p-channel sequencing MOSFET to isolate load from the battery when not needed.

A Low Dropout (LDO) linear regulator with an adjustable 1.5V to 3.75V output provides a small dropout voltage and ripple free supply that is optimal for "always on" microcontrollers. The LDO has a separate input supply pin.

The SMB122 and SMB122X provide margining control over all of their output voltages. Through an  $\rm I^2C$  command, all outputs can be margined by up to  $\pm 10\%$  of the nominal output voltage. The SMB122X also offers the ability to dynamically change output voltage level (7 steps) for two of its channels. In addition, each output is slew rate limited by soft-start circuitry that is user programmable and requires no external capacitors.

All programmable settings on the SMB122 and SMB122X are stored in non-volatile registers and are easily accessed and modified over an industry standard I<sup>2</sup>C serial bus. For fastest possible production times Summit offers an evaluation card and a Graphical User Interface (GUI).

Summit Microelectronics, Inc 3.0 10/8/2008 2

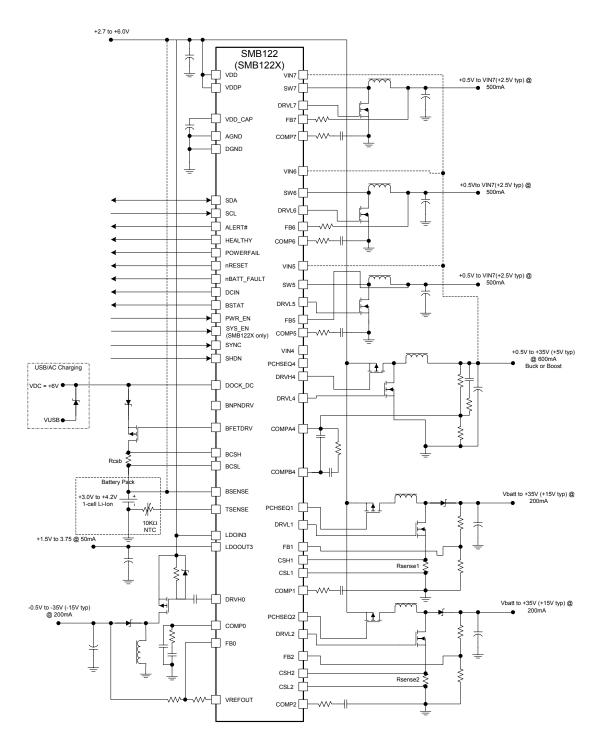

### **TYPICAL APPLICATION**

Figure 2 – Typical application schematic of the SMB122/SMB122X (QFN-64) showing external circuitry necessary to configure the output channels as: step-up, LDO, step-down, inverting and battery charger.

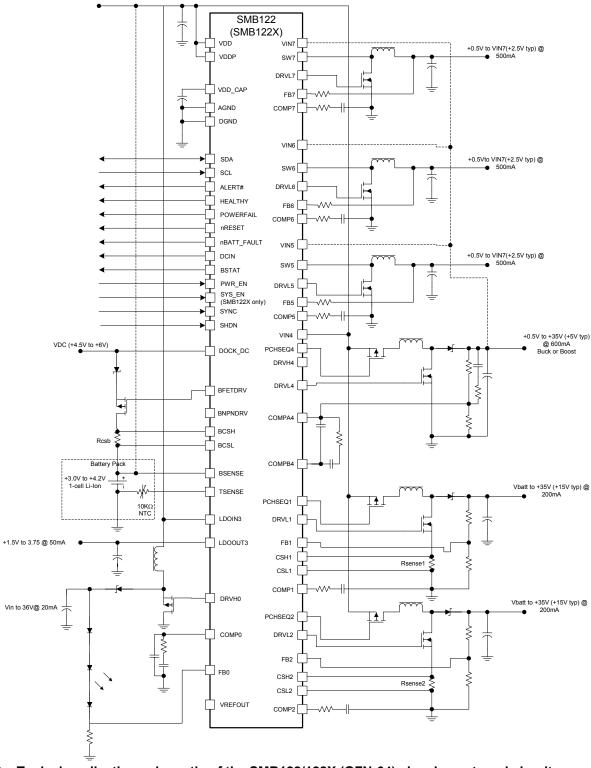

# TYPICAL APPLICATION

+2.7 to +6.0V

Figure 3 – Typical application schematic of the SMB122/122X (QFN-64) showing external circuitry necessary to configure the output channels as: step-up, LDO, step-down, LED driver and battery charger.

| PIN DESC      | RIPTIONS      |              |                                                                                                                                                                                                                                                                                                                         |

|---------------|---------------|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>Number | Pin Name      | Pin Type     | Pin Description                                                                                                                                                                                                                                                                                                         |

| 1             | DGND          | Ground       | Digital Ground. Connect to isolated PCB ground                                                                                                                                                                                                                                                                          |

| 2             | AGND          | Ground       | Analog Ground. Connect to isolated PCB ground                                                                                                                                                                                                                                                                           |

| 3             | PWR_EN        | Input        | Enable input. PWR_EN is programmable to activate one or more channels. This pin can be programmed to latch and act as a debounced, manual push button input. Active high when level triggered, active low when used as a push- button input. A Software power-off command overrides this pin.                           |

| 4             | VREF_OUT      | Output       | Inverting Buck-Boost level-shifting reference                                                                                                                                                                                                                                                                           |

| 5             | COMP0         | Input        | Inverting Buck-Boost Compensation. Connect to R/C compensation network                                                                                                                                                                                                                                                  |

| 6             | FB0           | Input        | Inverting Buck-Boost Feedback. Connect to output resistor divider                                                                                                                                                                                                                                                       |

| 7             | DRVH0         | Output       | Inverting Buck-Boost High-side FET drive. Connect to PFET gate                                                                                                                                                                                                                                                          |

| 8             | DRVL4         | Output       | Buck or Boost converter low-side drive. Connect to NFET gate                                                                                                                                                                                                                                                            |

| 9             | DRVH4         | Output       | Buck converter high-side drive. Connect to PFET gate (for Buck only)                                                                                                                                                                                                                                                    |

| 10            | VIN4          | Power        | Channel 4 power. Connect to +2.7V to +6.0V to supply internal FET drivers                                                                                                                                                                                                                                               |

| 11            | COMPA4        | Input        | Channel 4 Buck or Boost outputs error amplifier input. Connect this node to the type three R/C compensation network                                                                                                                                                                                                     |

| 12, 32, 46    | PCHSEQ[4,1,2] | Output       | P-Channel MOSFET sequencing pin. Connect to PFET gate for Boost channel on/off and sequencing. Internally connected to a 100uA current sink to pull PFET gate resistor from VDD to ground to enable sequencing. Must be tied to ground when unused.                                                                     |

| 13            | COMPB4        | Input        | Channel 4 Buck or Boost outputs error amplifier output. Connect this node to the type three R/C compensation network.                                                                                                                                                                                                   |

| 14            | HEALTHY       | Output       | Output Monitor. Open drain active-high output asserts when all output channels are within UV/OV limits (ignoring disabled outputs)                                                                                                                                                                                      |

| 15            | POWER_FAIL    | Output       | Battery/Input Monitor. Detects low input voltage. Latched open-drain active high output. Associated threshold must be set higher than nBATT_FAULT threshold.                                                                                                                                                            |

| 26, 16, 59    | COMP[7:5]     | Input        | Buck converter compensation pin. Connect to type 2 R/C compensation network                                                                                                                                                                                                                                             |

| 25, 17, 58    | FB[7:5]       | Input        | Buck converter feedback pin. Connect directly to output                                                                                                                                                                                                                                                                 |

| 24, 18, 53    | SW[7:5]       | Input/Output | Buck converter switch pin. Connect to drains of NFET                                                                                                                                                                                                                                                                    |

| 23, 19, 54    | VIN[7:5]      | Power        | Buck Converter Power. Connect to +2.7V to +6.0V to supply internal PFET                                                                                                                                                                                                                                                 |

| 22, 20, 55    | DRVL[7:5]     | Output       | Buck converter low-side drive. Connect to NFET gate                                                                                                                                                                                                                                                                     |

|               | NC            | NC           | SMB122: Not connected                                                                                                                                                                                                                                                                                                   |

| 21            | SYS_EN        | Input        | SMB122X: Enable input. The SYS_EN pin is an active high programmable input used to enable (disable) selected supplies. When unused this pin should be tied to a solid logic level.                                                                                                                                      |

| 27            | DCIN          | Output       | DC Input Valid. Active high open drain indicates presence of DC input voltage (docking) with programmable threshold                                                                                                                                                                                                     |

| 28            | BSTAT         | Output       | Battery Charger Status Output – Open Drain output asserts low when battery is charging and releases when charging is terminated/interrupted. Can be configured to blink while charging. When configured to blink, it will blink once every second while precharging and twice per second while fast and taper charging. |

|               | RIPTIONS (Co | ntinued)     |                                                                                                                                                                                                                                                                                                                                                                          |

|---------------|--------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin<br>Number | Pin Name     | Pin Type     | Pin Description                                                                                                                                                                                                                                                                                                                                                          |

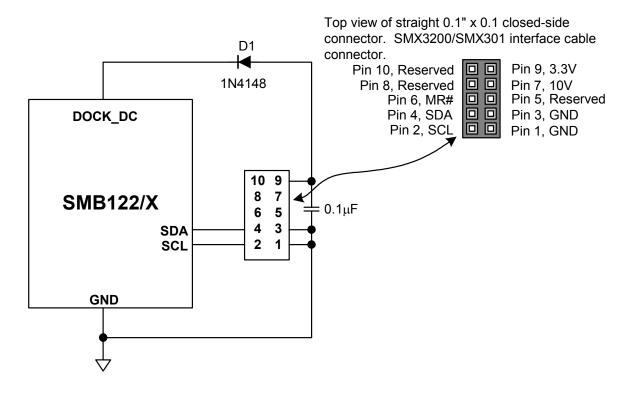

| 29            | DOCK_DC      | Power        | Docking Connector Detector. DOCK_DC detects presence of external DC input and asserts DCIN pin. Provides power to the chip when greater than VBATT. Voltage on this pin must be greater than DOCK_DC trip point (programmable) for battery charging to be initiated. When voltage is present on DOCK_DC pin the SHDN pin is bypassed.                                    |

| 30            | nBATT_FAULT  | Output       | Battery/Input Monitor. nBATT_FAULT detects low input voltage. Open-drain active low output. Associated threshold must be set lower than POWER_FAIL threshold.                                                                                                                                                                                                            |

| 31            | nRESET       | Output       | Reset Output. Releases with programmable delay after all selected outputs are valid (see UV/OV trip points). Open-drain active low output                                                                                                                                                                                                                                |

| 33            | VDD_CAP      | Power        | VDD Bypass. Connect to VDD bypass capacitor with 10uF capacitor.                                                                                                                                                                                                                                                                                                         |

| 34            | VDDP         | Power        | Power Input for the Boost and Buck-Boost Converters. Connect to +2.7V to +6.0V voltage source. Must be at same voltage as source of PFET for the Boost converters.                                                                                                                                                                                                       |

| 35            | VBATT        | Power        | Power Input for Controller. Connect to +2.7V to +6.0V voltage source . Bypass with a 0.1uF ceramic capacitor close to the pin.                                                                                                                                                                                                                                           |

| 36, 45        | COMP[1:2]    | Input        | Boost converter compensation pin. Connect to R/C compensation network                                                                                                                                                                                                                                                                                                    |

| 37, 43        | CSH[1:2]     | Input        | Boost converter current sense high. Connect to high side of sense resistor                                                                                                                                                                                                                                                                                               |

| 38, 44        | CSL[1:2]     | Input        | Boost converter current sense low. Connect to low side of sense resistor                                                                                                                                                                                                                                                                                                 |

| 39, 42        | FB[1:2]      | Input        | Boost converter feedback pin. Connect to external resistor divider                                                                                                                                                                                                                                                                                                       |

| 40, 41        | DRVL[1:2]    | Output       | Boost converter low-side drive. Connect to NFET gate                                                                                                                                                                                                                                                                                                                     |

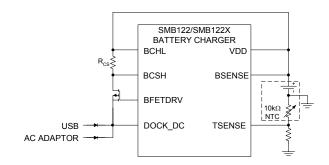

| 47            | BFETDRV      | Output       | Battery Charger FET Drive. Connects to gate of a PFET to control battery charging current                                                                                                                                                                                                                                                                                |

| 48            | BSENSE       | Input        | Battery Voltage Sense. Connect directly to positive terminal of battery                                                                                                                                                                                                                                                                                                  |

| 49            | TSENSE       | Input        | Battery Temperature Sense – Connect to "Temp" terminal of battery pack. This pin injects a programmable current into the NTC thermistor internal to the battery pack and measures the resulting current to detect temperatures. Place a 24.9K resistor, for 10K NTC, from this node to ground. Temperature levels are designed for a NTC thermistor with a Beta of 4400. |

| 50            | BCSH         | Input        | Charge Current Sense. Connect to high-side of charge current sense resistor                                                                                                                                                                                                                                                                                              |

| 51            | LDOIN3       | Power        | LDO Power Input. Connect to +2.7V to +6.0V to supply internal LDO                                                                                                                                                                                                                                                                                                        |

| 52            | LDOOUT3      | Input/Output | LDO Output/Feedback                                                                                                                                                                                                                                                                                                                                                      |

| 56            | BNPNDRV      | Output       | Leave floating.                                                                                                                                                                                                                                                                                                                                                          |

| 57            | BCSL         | Input        | Charge Current Sense resistor. Connect to low side of charge current sense resistor. Do not attach to battery node at any other point.                                                                                                                                                                                                                                   |

| 60            | SHDN         | Input        | Shutdown. Active high, disables all functions of the SMB122 for low power operation. When low the SMB122 is in low current mode. When voltage is present on the DOCK_DC input the part will exit shutdown state.                                                                                                                                                         |

# **SMB122/SMB122X**

| <b>PIN DESC</b> | PIN DESCRIPTIONS (Continued) |              |                                                                                                                                                                |  |  |  |  |

|-----------------|------------------------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 61              | SDA                          | Input/Output | I <sup>2</sup> C Data                                                                                                                                          |  |  |  |  |

| 62              | SCL                          | Input        | I <sup>2</sup> C Clock                                                                                                                                         |  |  |  |  |

| 63              | nALERT                       | Output       | Fault Interrupt. Latched, open drain active low output. Flag for all fault conditions (multiplexed)                                                            |  |  |  |  |

| 64              | SYNC                         | Input        | Oscillator Synchronization. Used for synchronization with external clock (range: 500kHz to 1MHz). Please contact Summit Microelectronics for more information. |  |  |  |  |

| PAD             | DRVGND                       | Ground       | Power Ground. Internally connect to under package pad. Connect to isolated PCB ground plane/flood                                                              |  |  |  |  |

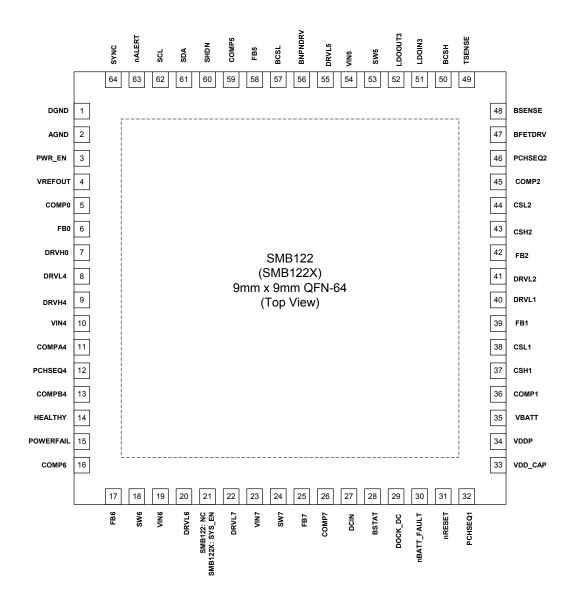

### **PACKAGE AND PIN DESCRIPTION**

### SMB122 64-pin QFN Top view

### **ABSOLUTE MAXIMUM RATINGS**

| Temperature Under Bias         | 55°C to 125°C |

|--------------------------------|---------------|

| Storage Temperature            | 65°C to 150°C |

| Terminal Voltage with Respect  | to GND:       |

| VBATT                          | 0.3V to +6.5V |

| VIN[7:5], LDOIN3               | 0.3V to +6.5V |

| All Others                     | 0.3V to +6.5V |

| Output Short Circuit Current   |               |

| Lead Solder Temperature (10 s) | 300°C         |

| Junction Temperature           | 150°C         |

| ESD Rating per JEDEC           | 2000V         |

| Latch-Up testing per JEDEC     | ±100mA        |

|                                |               |

| RECOMMENDED OPERATING CO             | ONDITIONS         |

|--------------------------------------|-------------------|

| Commercial Temperature Range         | 0°C to +70°C      |

| Industrial Temperature Range         | 40°C to +85°C     |

| VBATT                                | +2.7V to +6.0V    |

| VIN[7:5], LDOIN3                     | +2.7V to +6.0V    |

| DOCK_DC                              | +4.5V to +6.0V    |

| 64-lead 9x9 QFN Package Thermal F    |                   |

| Die paddle not attached to PCB       | 41.9°C/W          |

| Die paddle attached to PCB           | 27.4°C/W          |

| Moisture Classification Level 3 (MSL | 3) per J-STD- 020 |

| RELIABILITY CHARACTERISTICS          |                   |

| Data Retention                       | 100 Years         |

| Endurance                            | 100,000 Cycles    |

Note - The device is not guaranteed to function outside its operating rating. Stresses listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions outside those listed in the operational sections of the specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability. Devices are ESD sensitive. Handling precautions are recommended.

|                          | DC OPERATING CHARACTERISTICS (Over commercial operating conditions, unless otherwise noted. All voltages are relative to GND.) |                                                                         |            |      |      |       |  |  |

|--------------------------|--------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------|------------|------|------|-------|--|--|

| Symbol                   | Parameter                                                                                                                      | Notes                                                                   | es are rei | Typ  | Max  | Unit  |  |  |

| General                  |                                                                                                                                |                                                                         |            |      |      | ı     |  |  |

| $V_{BATT}$               | Input supply voltage                                                                                                           |                                                                         | +2.7       |      | +6.0 | V     |  |  |

| VIN[7:5],<br>LDOIN3      | Regulator power supply voltage                                                                                                 |                                                                         | +2.7       |      | +6.0 | V     |  |  |

| $V_{UVLO}$               | Under-voltage lockout                                                                                                          | V <sub>BATT</sub> rising                                                |            | 2.3  | 2.4  | V     |  |  |

| <b>V</b> UVLO            | voltage                                                                                                                        | V <sub>BATT</sub> falling                                               |            | 2.1  |      | V     |  |  |

| I <sub>DD-ACTIVE</sub>   | Active supply current                                                                                                          | All regulators and monitors enabled – no load, V <sub>BATT</sub> = 4.2V |            | 3.7  | 4.5  | mA    |  |  |

| I <sub>DD-STANDBY</sub>  | Standby supply current                                                                                                         | All regulators disabled, monitors active, $V_{BATT} = 4.2V$             |            | 135  | 300  | μА    |  |  |

| I <sub>DD-SHUTDOWN</sub> | Shutdown supply current                                                                                                        | All regulators and monitors disabled, Note 4                            |            | 0.6  | 5    | μА    |  |  |

| T <sub>SHDN</sub>        | Thermal shutdown temp                                                                                                          |                                                                         |            | 160  |      | °C    |  |  |

| T <sub>HYST</sub>        | Thermal shutdown temp hysteresis                                                                                               |                                                                         |            | 20   |      | °C    |  |  |

| VDD_CAP                  | Voltage on VDD_CAP pin                                                                                                         | All logic derived from this voltage, no load                            | 2.4        | 2.5  | 2.6  | V     |  |  |

| f <sub>OSC</sub>         | Oscillator frequency                                                                                                           | T = 0°C to +70°C                                                        | 900        | 1000 | 1100 | kHz   |  |  |

| OSC                      | (Note 1)                                                                                                                       | T = -40°C to +85°C                                                      | 850        | 1000 | 1150 | NI IZ |  |  |

| Symbol                | Parameter                                          | Notes                                          | Min    | Тур      | Max   | Unit        |

|-----------------------|----------------------------------------------------|------------------------------------------------|--------|----------|-------|-------------|

| <u> </u>              |                                                    | Notes                                          | 141111 | тур      | IVIAA | Offic       |

|                       | Inverting BUCK-BOOST                               |                                                |        | τ        |       | <del></del> |

| $V_{OUT}$             | Voltage (nominal set point)                        | V <sub>BATT</sub> =4.2V, I <sub>LOAD</sub> =0A | -35    |          | -0.5  | V           |

| $V_{FB0}$             | Feedback Voltage Reference                         | V <sub>BATT</sub> =4.2V                        | 0.97   | 1        | 1.03  | V           |

| V <sub>REFOUT</sub>   | Level Shift Voltage Reference                      | Programmable in 8mV steps                      | 1      |          | 2     | V           |

| $\Delta V_{REFOUT}$   | Level Shift Voltage Reference<br>Accuracy (Note 2) | V <sub>REFOUT</sub> =1.832V                    | -2     |          | +2    | %           |

| I <sub>VREFOUT</sub>  | Level Shift Current                                | Note 4                                         | 850    | 890      |       | μΑ          |

| g <sub>m</sub>        | Error amp transconductance                         |                                                |        | 146      |       | umho        |

| I <sub>EA</sub>       | Error amp output drive                             |                                                |        | ±20      |       | μА          |

| D                     | LIC Cate drive immedes                             | Output High                                    |        | 13       |       | Ω           |

| $R_{DRVH}$            | HS Gate drive impedance                            | Output Low                                     |        | 2.5      |       | Ω           |

| D.O.                  | Duty Cycle                                         | Maximum                                        | 85     | 90       | 98    | %           |

| D.C.                  |                                                    | Minimum, PWM mode                              |        | 14       | 25    | %           |

| Channel [2:           | 1] – Step-up BOOST                                 |                                                |        | <u> </u> | 1     | _ I         |

| V <sub>OUT</sub>      | Voltage (nominal set point)                        | $V_{BATT} = 4.2V$ , $I_{LOAD} = 0A$            | VIN    |          | +35   | V           |

| $V_{FB}$              | Feedback Voltage Reference                         | Programmable in 4mV steps                      | 0      |          | 1     | V           |

| $\Delta V_FB$         | Feedback Voltage Accuracy at FB[2:1] Pin (Note 2)  | V <sub>FB</sub> =0.836V                        | -3     | ±1       | +3    | %           |

| <b>g</b> <sub>m</sub> | Error amp transconductance                         |                                                |        | 145      |       | umho        |

| I <sub>EA</sub>       | Error amp output drive                             |                                                |        | ±20      |       | μΑ          |

|                       | 00 15 1                                            | $R_{SENSE} = 0.1\Omega$ , $I_{LOAD} = 350$ mA  |        | 0.8      |       |             |

| R <sub>CS</sub>       | CS amplifier transresistance                       |                                                |        | 1.6      |       | Ω           |

| I <sub>OL-SEQ</sub>   | PCHSEQ pull down current                           | V <sub>OL-SEQ</sub> = 1V                       | 60     | 100      |       | μА          |

|                       |                                                    | Output High                                    |        | 6.0      |       | Ω           |

| $R_{DRVL}$            | LS Gate drive impedance                            | Output Low                                     |        | 2.5      |       | Ω           |

| V <sub>cl</sub>       | Clamp threshold voltage                            | Programmable 1.0, 1.1, 1.2, 1.5V               | 1.0    |          | 1.5   | V           |

| V <sub>cl_acc</sub>   | Clamp threshold voltage<br>Accuracy                | Clamp threshold 1.0 and 1.5V                   |        | ±5       |       | %           |

| D.C.                  | Duty Cycle                                         | Maximum (clamp on)                             | 85     | 90       | 98    | %           |

| D.C.                  | Duty Cycle                                         | Minimum, PWM mode                              |        | 16       | 30    | %           |

| DC OPE              | RATING CHARACTERISTICS              | (CONTINUED)                                            |            |            |      |      |

|---------------------|-------------------------------------|--------------------------------------------------------|------------|------------|------|------|

| (Over com           | mercial operating conditions, unl   | ess otherwise noted. All voltage                       | es are rel | ative to G | ND.) |      |

| Channel             | [7:5] – Step-down BUCK              |                                                        |            |            |      |      |

| V <sub>OUT</sub>    | Voltage (nominal set point)         | VIN[7:5]=4.2V, I <sub>LOAD</sub> =0A                   | +0.5       |            | VIN  | V    |

|                     | Voltage accuracy                    | Note 2, V <sub>OUT</sub> = 2.5V,<br>T = -40°C to +85°C | -2         | ±1         | +2   | %    |

| $\Delta V_{OUT}$    | voltage accuracy                    | Note 2, V <sub>OUT</sub> = 1.2V,<br>T = 0°C to +70°C   | -2         | ±1         | +2   | %    |

| V <sub>FB</sub>     | Feedback Voltage Reference range    | Programmable in 4mV steps                              | 0          |            | 1    | V    |

| g <sub>m</sub>      | Error amp transconductance          |                                                        |            | 160        |      | umho |

| I <sub>EA</sub>     | Error amp output drive              |                                                        |            | ±20        |      | μΑ   |

| R <sub>CS</sub>     | CS amplifier transresistance        | I <sub>LOAD</sub> = 500mA                              |            | 1.2        |      | Ω    |

| R <sub>HS</sub>     | HS Switch Resistance                | I <sub>LOAD</sub> = 500mA                              |            | 320        |      | mΩ   |

| R <sub>DRVL</sub>   | LS Gate drive impedance             | Output High                                            |            | 5.5        |      | Ω    |

| NDRVL               | L3 Gate drive impedance             | Output Low                                             |            | 2.7        |      | Ω    |

| V <sub>cl</sub>     | Clamp threshold voltage             | Programmable 1.0, 1.1, 1.2, 1.5V                       | 1.0        |            | 1.5  | V    |

| V <sub>cl_acc</sub> | Clamp threshold voltage<br>Accuracy | Clamp threshold 1.0 and 1.5V                           |            | ±5         |      | %    |

|                     |                                     | Maximum, V <sub>BATT</sub> = 4.2V                      |            | 100        |      | %    |

| D.C.                | Duty Cycle                          | Minimum, PWM mode,<br>V <sub>BATT</sub> = 4.2V         |            | 15         | 30   | %    |

| <u> </u>         | <u> </u>                            | ess otherwise noted. All voltag                | es are rel | ative to G | ND.) |    |

|------------------|-------------------------------------|------------------------------------------------|------------|------------|------|----|

| Channel 4 –      | Step-down BUCK or Step-u            | •                                              |            | 1          | I    | ı  |

| $V_{\text{OUT}}$ | Voltage (nominal set point, Buck)   | V <sub>BATT</sub> =4.2V, I <sub>LOAD</sub> =0A | +0.5       |            | +VIN | V  |

| V <sub>OUT</sub> | Voltage (nominal set point, Boost)  | V <sub>BATT</sub> =4.2V, I <sub>LOAD</sub> =0A | +VIN       |            | +35  | V  |

| V <sub>FB</sub>  | Feedback Voltage<br>Reference range | Programmable in 4mV steps                      | 0          |            | 1    | V  |

| $\Delta V_{FB}$  | Feedback Voltage<br>Reference       | FB[4] Pin, V <sub>FB</sub> = 0.660V,<br>Note 2 | -2         |            | +2   | %  |

| A <sub>VOL</sub> | Error amp open loop gain            |                                                |            | 60         |      | dB |

| I <sub>EA</sub>  | Error amp output drive              |                                                |            | ±20        |      | μΑ |

| D                | HS Gate drive impedance             | Output High                                    |            | 15         |      | Ω  |

| $R_{DRVH}$       | (Buck only)                         | Output Low                                     |            | 15         |      | Ω  |

| D                | LS Gate drive impedance             | Output High                                    |            | 15         | +2   | Ω  |

| $R_{DRVL}$       | L3 Gate drive impedance             | Output Low                                     |            | 15         |      | Ω  |

|                  |                                     | Maximum, V <sub>BATT</sub> = 4.2V              | 85         | 93         | 98   | %  |

| D.C. (Boost)     | Duty Cycle                          | Minimum, PWM mode,<br>V <sub>BATT</sub> = 4.2V |            | 11         | 16   | %  |

|                  |                                     | Maximum, V <sub>BATT</sub> = 4.2V              |            | 100        |      | %  |

| D.C. (Buck)      | Duty Cycle                          | Minimum, PWM mode,<br>V <sub>BATT</sub> = 4.2V |            | 7          | 11   | %  |

|                          | nercial operating conditions, unl             |                                                                            |       |       |       |           |

|--------------------------|-----------------------------------------------|----------------------------------------------------------------------------|-------|-------|-------|-----------|

| Symbol                   | Parameter                                     | Notes                                                                      | Min   | Тур   | Max   | Unit      |

| Channel 3                |                                               |                                                                            |       |       |       |           |

| $V_{OUT}$                | Voltage (nominal set point)                   | LDOIN3=4.2V, I <sub>LOAD</sub> =0A                                         | +1.5  |       | +3.75 | V         |

| $\Delta V_{OUT}$         | Voltage accuracy                              | LDOIN3=4.2V, I <sub>LOAD</sub> =0A,<br>V <sub>OUT</sub> =2.5V              | -2.5  | ±0.5  | +2.5  | %         |

| $\Delta V_{\text{LINE}}$ | Line regulation                               | LDOIN3=4.2V, I <sub>LOAD</sub> =0A,                                        |       | 1     |       | mV/V      |

| $\Delta V_{LOAD}$        | Load regulation                               | Vo=2.5, Vin = 4.2V                                                         |       | 1     |       | mV/<br>mA |

| $\Delta V_{TRANS}$       | Load Transient Regulation                     | Step Load: 5mA to 50mA<br>C <sub>OUT</sub> = 10uF                          |       | 50    |       | mV        |

| PSRR                     | Input Ripple Rejection                        | LDOIN2=3.8V, $V_{OUT}$ =3.3V $I_{LOAD}$ =50mA, $V_{P-P}$ =200mV, $F$ =1kHz |       | 45    |       | dB        |

| I <sub>OUTMAX</sub>      | Maximum output Current                        | LDOIN3=3.2V, V <sub>OUT</sub> =2.5V                                        | 50    | 75    |       | mA        |

| $V_{DO}$                 | Dropout voltage                               | I <sub>LOAD</sub> =50mA                                                    |       | 150   |       | mV        |

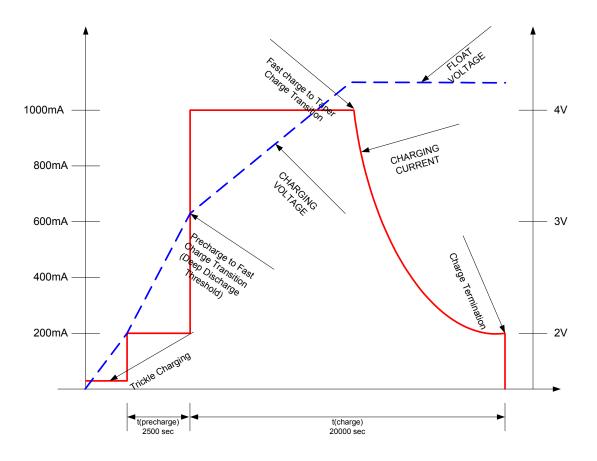

| Battery Ch               | arger (Note 3), DOCK_DC=5V                    |                                                                            |       | l .   | l .   | <u>.L</u> |

| V <sub>Dockdc</sub>      | Input Voltage                                 | VBATT=3.6V                                                                 |       | 5.0   |       | V         |

| V <sub>PRECHG</sub>      | Precharge voltage threshold range             | Programmable in 100mV steps                                                | 2.500 |       | 3.200 | V         |

| V <sub>PRECHG_ACC</sub>  | Precharge voltage threshold accuracy          | VBATT rising, V <sub>PRECHG</sub> = 2.5V and 3.2V                          |       | ±20   |       | mV        |

| I <sub>PRECHG</sub>      | Nominal precharge current range               | $R_{CSB}$ =0.1 $\Omega$ , 15mA steps                                       | 25    |       | 250   | mA        |

| $\Delta I_{PRECHG}$      | Precharge current tolerance                   | I <sub>PRECHG</sub> = 100mA                                                | 70    | 100   | 130   | mA        |

| I <sub>CHG</sub>         | Nominal Fast charge current                   | R <sub>CSB</sub> =0.1Ω, 60mA steps                                         | 100   |       | 1000  | mA        |

| $\Delta I_{CHG}$         | Fast charge current tolerance                 | I <sub>CHG</sub> = 520mA                                                   | 485   | 520   | 565   | mA        |

| $V_{FLT}$                | Float voltage range                           | 20mV steps                                                                 | 4.000 |       | 4.620 | V         |

| $\Delta V_{FLT}$         | Float voltage tolerance                       | V <sub>FLT</sub> = 4.2V                                                    | -1.2  | ±0.5  | +1.2  | %         |

| V <sub>FLT_HYST</sub>    | Float voltage hysteresis (recharge threshold) | VBATT falling, V <sub>FLT</sub> - V <sub>FLT_HYST</sub>                    |       | 100   |       | mV        |

| I <sub>TERM</sub>        | Charge termination current range              | R <sub>CSB</sub> =0.1Ω, 15mA steps                                         | 100   |       | 145   | mA        |

| $\Delta I_{TERM}$        | Termination current tolerance                 | I <sub>TERM</sub> = 100mA                                                  | 50    | 100   | 170   | mA        |

| T <sub>HI</sub>          | Charge cutoff temp (high)                     | 5°C steps                                                                  | +30   |       | +65   | °C        |

| $T_LO$                   | Charge cutoff temp (low)                      | 5°C steps                                                                  | -20   |       | +15   | °C        |

| T <sub>TSENSE</sub>      | THERM bias current                            |                                                                            | 80    | 100   | 130   | μА        |

| T <sub>precharge</sub>   | Precharge timer duration                      | Adjustable (3 setpoints)                                                   |       | 2621  |       | S         |

| T <sub>charge</sub>      | Charge timer duration                         | Adjustable (3 setpoints)                                                   |       | 20972 |       | S         |

| V <sub>PDDCTH</sub>      | Programmable DOCK_DC threshold range          | Programmable in 0.2V steps                                                 | 3.4   |       | 4.8   | V         |

| V <sub>PDDCTHACC</sub>   | DOCK_DC threshold accuracy                    | V <sub>PDDCTH</sub> =4.6V                                                  | -4    |       | +4    | %         |

| Symbol             | Parameter                                | Notes                                         | Min  | Тур              | Max  | Unit |

|--------------------|------------------------------------------|-----------------------------------------------|------|------------------|------|------|

| $V_{IH}$           | Input high voltage                       |                                               |      | 0.7 x<br>VDD_CAP |      | V    |

| V <sub>IL</sub>    | Input low voltage                        |                                               |      | 0.3 x<br>VDD_CAP |      | V    |

| $V_{PBFTH}$        | Programmable nBATT_FAULT threshold range | Programmable in 150 mV increments             | 2.55 |                  | 3.60 | V    |

| $\Delta V_{PBFTH}$ | nBATT_FAULT accuracy                     | V <sub>PBFTH</sub> =3.15V                     | -3   |                  | +4   | %    |

| $V_{PPFTH}$        | Programmable POWER_FAIL threshold range  | Programmable in 150 mV increments             | 2.55 |                  | 3.60 | V    |

| $\Delta V_{PPFTH}$ | POWER_FAIL accuracy                      | V <sub>PPFTH</sub> =3.3V                      | -3   |                  | +4   | %    |

|                    |                                          |                                               |      | -5               |      | . %  |

| $P_{UVTH}$         | Programmable under voltage               | Relative to nominal operating voltage. CH1 to |      | -10              |      |      |

| LUVTH              | threshold                                | CH7. Note 3.                                  |      | -15              |      |      |

|                    |                                          |                                               | -15  | -20              | -25  |      |

|                    |                                          |                                               |      | 5                |      |      |

| <b>D</b>           | Programmable over voltage                | Relative to nominal operating voltage. CH1 to |      | 10               |      | %    |

| P <sub>OVTH</sub>  | threshold                                | CH7. Note 4.                                  |      | 15               |      | /0   |

|                    |                                          |                                               | 15   | 20               | 25   | 1    |

Note 1: Contact Summit factory for other frequency settings.

Note 2: Voltage, current and frequency accuracies are only guaranteed for factory-programmed settings. Changing any of these parameters from the values reflected in the customer specific CSIR code will result in inaccuracies exceeding those specified above.

Note 3: The SMB122 and SMB122X devices are not intended to function as a battery pack protector. Battery packs used in conjunction with this device need to provide adequate internal protection and to comply with the corresponding battery pack specifications.

Note 4: Guaranteed by Design and Characterization – not 100% tested in Production.

OFF

50

100

200

0

25

100

400

3

3

3

ms

ms

ms

ms

$\mu$ S

#### (Over commercial operating conditions, unless otherwise noted. All voltages are relative to GND.) **Symbol Parameter Notes** Min Тур Max Unit 1.5 12.5 Programmable power-On Programmable sequence power-On ms t<sub>PPTO</sub> sequence timeout period. position to sequence position delay. 25 50 1.5 12.5 Programmable power-off Programmable power-off sequence ms $t_{\mathsf{DPOFF}}$ sequence timeout period. position to sequence position delay. 25 50 25 Programmable time following assertion of 50 Programmable reset last supply before nRESET pin is released ms t<sub>PRTO</sub> time-out delay high. 100 200

Time between active enable in which corresponding outputs must exceed there

programmed under voltage threshold. If

exceeded, a force shutdown will be

When PWR\_EN is programmed as power

Timeout begins after latch is cleared.

Timeout begins after fault conditions

15

Period for which fault must persist before

fault triggered actions are taken. Present

on all Buck, Boost, and inverting supplies.

initiated.

on pin.

cleared.

**AC OPERATING CHARACTERISTICS (CONTINUED)**

Programmable sequence

termination period

PWR\_EN de-bounce

POWER\_FAIL timeout

nBATT FAULT timeout

Programmable glitch filter

period

period

period

$t_{PST}$

$t_{PDB}$

t<sub>PFTO</sub>

**t**BFTO

$t_{\mathsf{PGF}}$

| AC OPERATING CHARACTERISTICS (CONTINUED)  (Over commercial operating conditions, unless otherwise noted. All voltages are relative to GND.) |                                             |                             |     |      |     |      |  |  |

|---------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------|-----------------------------|-----|------|-----|------|--|--|

| Symbol                                                                                                                                      | Parameter                                   | Notes                       | Min | Тур  | Max | Unit |  |  |

|                                                                                                                                             |                                             |                             |     | 400  |     |      |  |  |

|                                                                                                                                             |                                             |                             |     | 200  |     |      |  |  |

|                                                                                                                                             |                                             |                             |     | 100  |     |      |  |  |

| CD.                                                                                                                                         | Programmable slew rate                      | Adjustable slew rate factor |     | 66.7 |     | \//o |  |  |

| SK <sub>REF</sub>                                                                                                                           | reference Proportional to output slew rate. | 50                          |     | V/s  |     |      |  |  |

|                                                                                                                                             |                                             |                             |     | 33.3 |     |      |  |  |

|                                                                                                                                             |                                             |                             |     | 25   |     |      |  |  |

|                                                                                                                                             |                                             |                             |     | 20   |     |      |  |  |

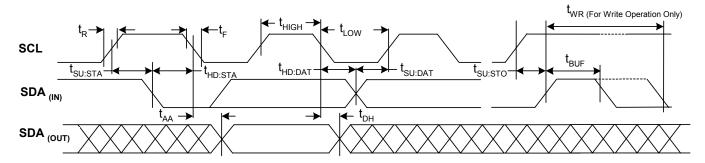

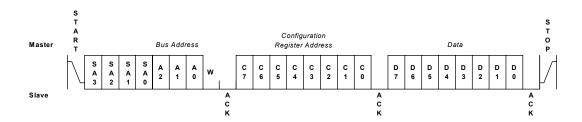

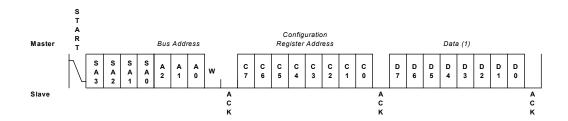

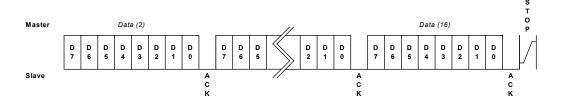

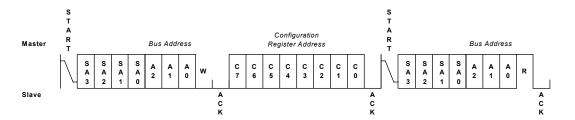

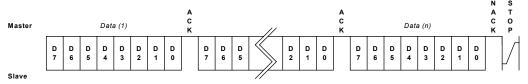

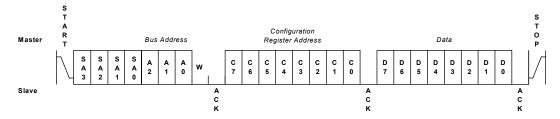

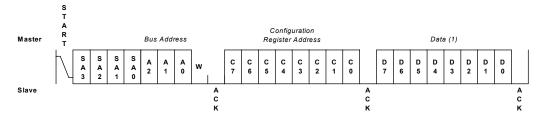

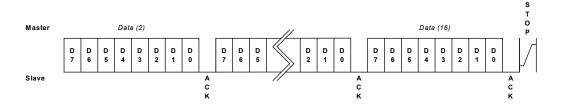

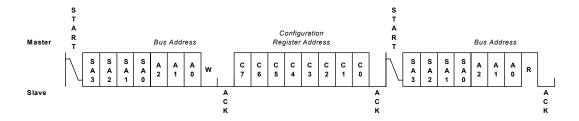

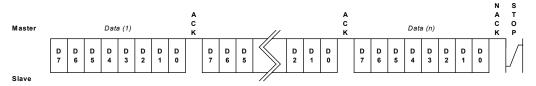

#### 1<sup>2</sup>C-2 WIRE SERIAL INTERFACE AC OPERATING CHARACTERISTICS -100 kHz (Over commercial operating conditions, unless otherwise noted. All voltages are relative to GND.) Conditions 100kHz **Symbol Description** Min Тур Max Units 0 100 KHz $f_{SCL}$ SCL clock frequency $T_{LOW}$ Clock low period 4.7 μS T<sub>HIGH</sub> Clock high period 4.0 μS Before new transmission - Note Bus free time 4.7 t<sub>BUF</sub> μS Start condition setup time 4.7 t<sub>SU:STA</sub> μS Start condition hold time 4.0 $t_{\text{HD:STA}}$ μS 4.7 Stop condition setup time t<sub>SU:STO</sub> μS Clock edge to data valid 0.2 3.5 $t_{AA}$ SCL low to valid SDA (cycle n) μS SCL low (cycle n+1) to SDA Data output hold time 0.2 $t_{DH}$ μS change SCL and SDA rise time Note 5 1000 $t_R$ ns 300 SCL and SDA fall time Note 5 t⊧ ns Data in setup time 250 t<sub>SU:DAT</sub> ns Data in hold time 0 t<sub>HD'DAT</sub> ns ΤI Noise filter SCL and SDA 100 Noise suppression ns Write cycle time config Configuration registers 10 ms twr config 5 Write cycle time EE ms twr ee Memory array

Note 5: Guaranteed by Design

### I<sup>2</sup>C TIMING DIAGRAMS

Figure 4: I<sup>2</sup>C timing diagram

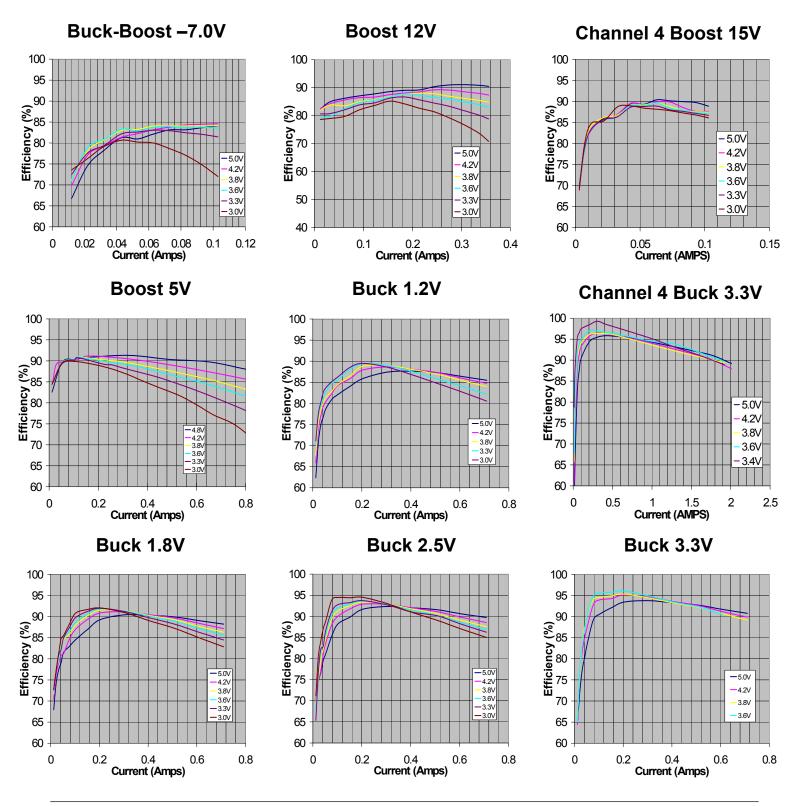

### **EFFICIENCY GRAPHS**

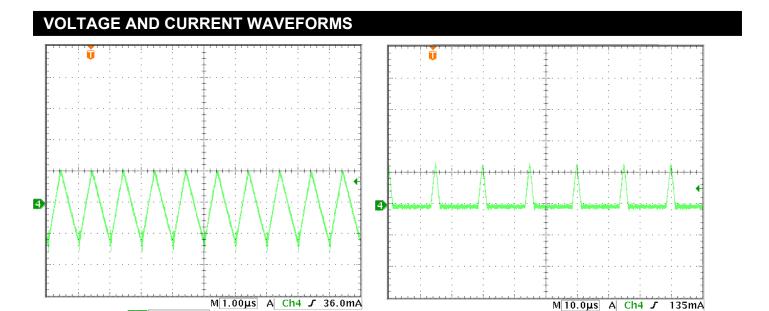

Figure 5: Light load inductor current in constant frequency mode (PWM).

Time/Horizontal division =  $1\mu$ s Ch 4 (50mA/Div) = 1.5V (Ch 7) converter output (Green trace)

Ch4 50.0mAΩ

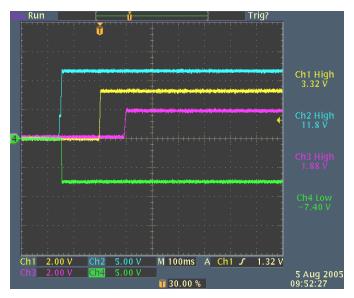

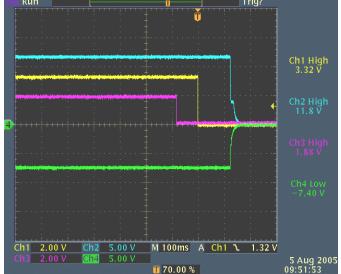

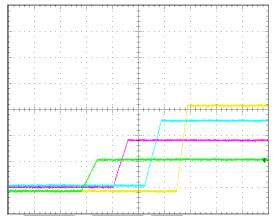

Figure 7: SMB122/SMB122X Sequence-On Waveforms

Time/Horizontal division = 100mS

Ch 1(2V/Div) = 3.3V (Ch 4) converter output (Yellow trace)

Ch 2 (5V/Div) = 12V (Ch 2) converter output (Blue trace)

Ch 3 (2V/Div) = 1.8V (Ch 6) converter output (Purple trace)

Ch 4 (5V/Div) = -7.5V (Ch 0) converter output (Green trace)

Figure 6: Light load inductor current in asynchronous mode.

Time/Horizontal division =  $10\mu$ s Ch 4 (50mA/Div) = 1.5V (Ch 7) converter output (Green trace)

250mAΩ

Figure 8: SMB122/SMB122X Sequence-Off Waveforms

Time/Horizontal division = 100mS

Ch 1(2V/Div) = 3.3V (Ch 4) converter output (Yellow trace)

Ch 2 (5V/Div) = 12V (Ch 2) converter output (Blue trace)

Ch 3 (2V/Div) = 1.8V (Ch 6) converter output (Purple trace)

Ch 4 (5V/Div) = -7.5V (Ch 0) converter output (Green trace)

## **VOLTAGE AND CURRENT WAVEFORMS (CONTINUED)**

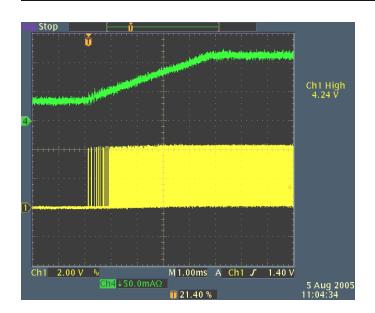

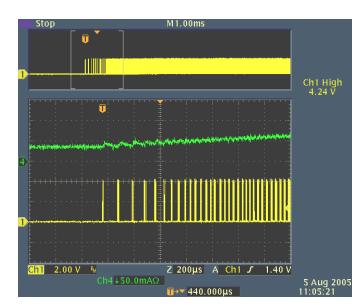

Figure 9: Pulse skipping on LSDRV pin while in PFM mode of operation. Switching frequency is proportional to load.

Time/Horizontal division = 1ms

Ch 1(2V/Div) = LSDRV output (Yellow trace)

Ch 4 (50mA/Div) = 150mA load step (Green trace)

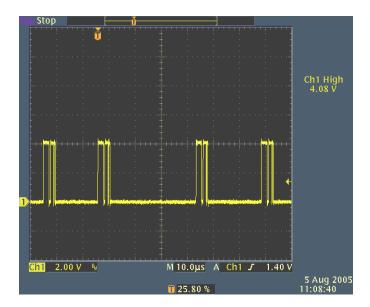

Figure 11: Pulse skipping on LSDRV for light load PFM operation

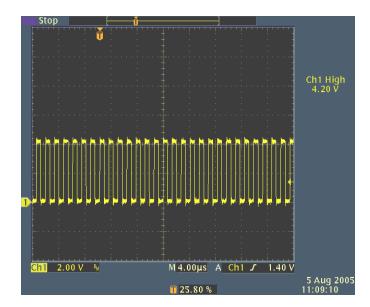

Time/Horizontal division =  $4\mu$ s Ch 1(2V/Div) = LSDRV output (Yellow trace)

Figure 10: Pulse skipping on LSDRV pin while in PFM mode of operation. Switching frequency is proportional to load.

$Time/Horizontal\ division = 200 \mu s$   $Ch\ 1(2V/Div) = LSDRV\ output\ (Yellow\ trace)$   $Ch\ 4\ (50mA/Div) = 150mA\ load\ step\ (Green\ trace)$

Figure 12: Forced PWM operation.

Time/Horizontal division = 4μs Ch 1(2V/Div) = LSDRV output (Yellow trace)

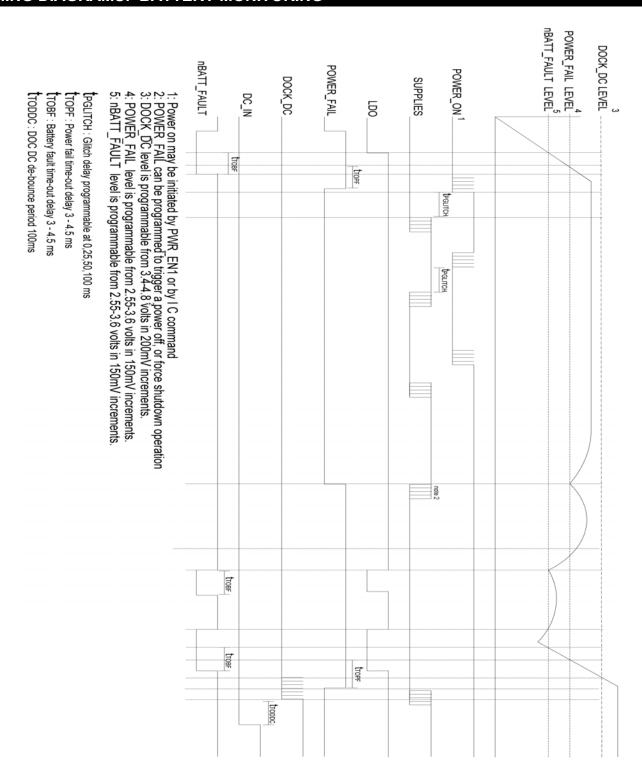

# TIMING DIAGRAMS: BATTERY MONITORING

Figure 13 - Battery monitoring timing diagram.

### **APPLICATIONS INFORMATION**

# DEVICE OPERATION POWER SUPPLY

The SMB122 and SMB122X can be powered from an input voltage between +2.7 and +6.0 volts applied between the VBATT pin and ground. The SMB122 and SMB122X are optimized for use with a rechargeable single cell Lithium ion battery, but may also be powered from a rectified AC adaptor or three AA batteries. The input voltage applied to the VBATT pin is filtered by an external filter capacitor attached between the VDD\_CAP pin and ground; this filtered voltage is then used as an internal VDD supply. The VDD\_CAP node is monitored by an UnderVoltage Lockout (UVLO) circuit, which prevents the device from turning on when the voltage at this node is less than the UVLO threshold.

When the voltage on the DOCK\_DC input exceeds that on the VBATT input the VBATT pin goes into a high impedance state and no longer powers the SMB122 or SMB122X, and the DOCK\_DC pin becomes the new power input.

#### **SHUTDOWN**

A shutdown pin is provided, that disconnects power from the SMB122 and SMB122X and reduces the current consumption to  $0.1\mu A$  when asserted. In this mode all channels are shut off. When asserted the SMB122 will not respond to  $I^2C$  commands.

Once the voltage on the VBATT input supply pin exceeds the UVLO threshold a 10 to 20ms delay must pass before supplies can be enabled. During this period the non-volatile registers are initialized with the default values from the nonvolatile memory.

If voltage is present on the DOCK\_DC input the SHDN pin will be bypassed and the output will be powered on.

#### POWER-ON/OFF CONTROL

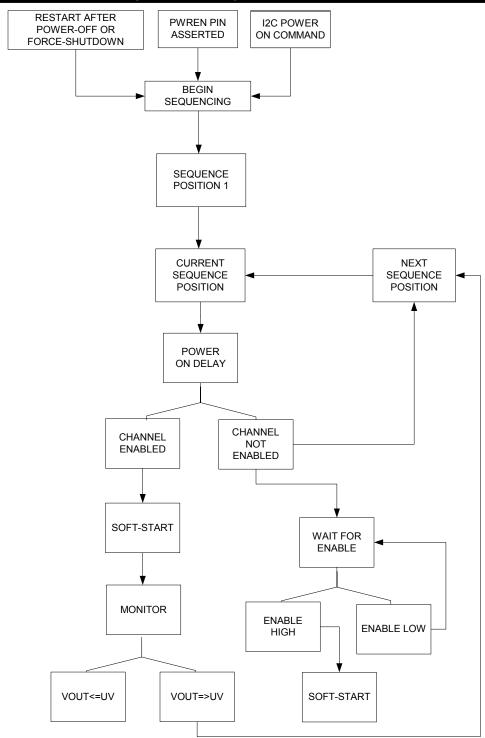

Sequencing can be initiated: automatically, by a volatile  $I^2C$  **Power on** command, or by asserting the PWREN pin. When the PWREN pin is programmed to initiate sequencing, it can be level or edge triggered. The PWREN input has a programmable de-bounce time of 100, 50, or 25ms. The de-bounce time can also be disabled.

When configured as a push-button enable, PWREN must be asserted longer than the de-bounce time before sequencing can commence, and pulled low for the same period to disable the channels.

### INDEPENDENT CHANNEL ENABLE CONTROL

Each output can be enabled and disable by an enable signal. The enable signal is can be provided from either

the Enable pins or by the contents of the enable register.

When enabling a channel from the enable register, the register contents default state must be set so that the output will be enabled or disabled following a POR (power on reset).

When *Default On* is selected, the channel will turn on after its sequence position is reached or power is applied—depending on the sequencing type. When *Default Off* is selected, the channel will not turn on until

### **SEQUENCING**

Each channel on the SMB122 and SMB122X may be placed in any one of 8 unique sequence positions, as assigned by the configurable non-volatile register contents. The SMB122 and SMB122X navigate between each sequence position using a feedbackbased cascade-sequencing circuit. Cascade sequencing is the process in which each channel is continually compared against a programmable reference voltage until the voltage on the monitored channel exceeds the reference voltage, at which point an internal sequence position counter is incremented and the next sequence position is entered. In the event that a channels enable input is not asserted when the channel is to be sequenced on, that sequence position will be skipped and the channel in the next sequence position will be enabled.

Figure 14 – Power on sequencing waveforms.

Time = 4ms/devision. Scale = 1V/devision

Ch 1 = 3.3V output (Yellow trace)

Ch 2 = 2.5V output (Blue trace)

Ch 3 = 1.8V output (Purple trace)

Ch 4 = 1.2V output (Green trace)

#### POWER ON/OFF DELAY

There is a programmable delay between when channels in subsequent sequence positions are enabled. The delay is programmable at 50, 25, 12.5 and 1.5ms intervals. This delay is programmable for each of the eight sequence positions.

### **MANUAL MODE**

The SMB122 and SMB122X provide a manual poweron mode in which each channel may be enabled individually irrespective of the state of other channels. In this mode, the enable signal has complete control over the channel, and all sequencing is ignored. In Manual mode, channels will not be disabled in the event of a UV/OV fault on any output or the VBATT pin.

### **FORCE-SHUTDOWN**

When a battery fault occurs, a UV/OV is detected on any output, or an I<sup>2</sup>C force-shutdown command is issued, all channels will be immediately disabled, ignoring sequence positions or power off delay times.

### **SEQUENCE TERMINATION TIMER**

At the beginning of each sequence position, an internal programmable timer will begin to time out. When this timer has expired, the SMB122 and SMB122X will automatically perform a force-shutdown operation. This timer is user programmable with a programmable sequence termination period (t<sub>PST</sub>) of 50, 100, 200 ms; this function can also be disabled.

### **POWER OFF SEQUENCING**

The SMB122 and SMB122X have a power-off sequencing operation. During a power off operation, the supplies will be powered off in the reverse order they where powered on in.

When a power-off command is issued the SMB122 and SMB122X will set the sequence position counter to the last sequence position and disable that channel without soft-start control; once off, the power off delay for the channel(s) in the next to last sequence position will begin to timeout, after which that channel(s) will be disabled. This process will continue until all channels have been disabled and are off. The programmable

If a channel fails to turn off within the sequence termination period, the sequence termination timer will initiate a force shutdown, if enabled.

#### INPUT AND OUTPUT MONITORING

Both products monitor all outputs for under-voltage (UV) and over-voltage (OV) faults. The monitored levels are user programmable, and may be set at 5, 10, 15, and 20 percent of the nominal output voltage.

The VBATT pin is monitored for two user programmable UV settings. The VBATT UV settings are programmable from 2.55V to 3.45V in 150mV increments. Once the UV/OV voltage set points have been violated, the SMB122 and SMB122X can be programmed to respond in one of three ways, perform: a power-off operation, a force-shutdown operation andor it can trigger the nRESET/HEALTHY pin.

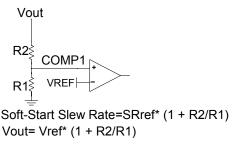

### **SOFT START**

The SMB122 and SMB122X provide a programmable soft-start function for all PWM outputs. The soft-start control limits the slew rate that each output is allowed to ramp up without the need for an external capacitor. The soft start slew rate is proportional to the product of the output voltage and a slew rate reference. This global reference is programmable and may be set to 400, 200, 100, 67, 50, 33, 25, and 20 Volts per second. The slew rate control can also be disabled on any channel not requiring the feature.

Figure 15 – The output voltage is set by the voltage divider. The VREF voltage is programmable from 0 to 1.0 volt in 4mV increments via the I<sup>2</sup>C interface

Figure 14 – Power-on sequencing flow chart.

#### **BATTERY MONITORING**

The battery voltage is monitored for two user programmable UV settings via the VBATT pin. In addition, the battery charging input, DOCK\_DC, is provided to monitor for the presence of a battery charging docking station, or AC wall adaptor.

Monitoring is accomplished by a comparator-based approach, in which a programmable voltage reference is compared against the monitored signal. Each channel possesses a dedicated reference voltage generated by a programmable level shifting digital to analog converter.

The SMB122 and SMB122X contain three user programmable voltage-monitoring levels, each of which triggers a corresponding status pin when exceeded. Battery voltage, like all monitored voltages, is compared against a user programmable voltage set internally by a digital to analog converter.

The DOCK\_DC pin is a power input pin that can be used to power the SMB122 or SMB122X and also indicate the presence, and level, of a supplemental input like that supplied by a docking station or AC wall adaptor. It has a user programmable threshold from 3.4-4.8 volts at 200mV increments. When the user programmable voltage level for this pin is exceeded, continuously, for a de-bounced period in excess of 100 ms the DC IN pin will be asserted.

When asserted, the POWER\_FAIL pin is latched and will not be released as long as the voltage on the battery is below the POWER\_FAIL level. Once the voltage on the battery has risen above the POWER\_FAIL level one of three conditions may clear the latch and allow the POWER\_FAIL pin to be released: if the nBATT\_FAULT output pin is asserted and released, if the DC\_IN output pin is asserted, and finally if an I<sup>2</sup>C POWER FAIL CLEAR command is issued. Once one of these conditions has been met, the POWER\_FAIL pin will be released after a power-fail timeout period (t<sub>PFTO</sub>) of 3.0-4.5ms. The POWER\_FAIL level is user programmable from 2.55-3.6.0V at 150 mV increments.

When the voltage at the VBATT pin falls below the second user programmable level, the active low nBATT\_FAULT pin will be asserted. This pin is not latched and is used to indicate the impending loss of power to the SMB122 and SMB122X. After the nBATT\_FAULT pin has been asserted, a battery fault timeout period (t<sub>BFTO</sub>) of 3.0-4.5ms must pass in which the battery voltage exceeds the nBATT\_FAULT threshold before it will be released. The nBATT\_FAULT

threshold is user programmable from 2.55-3.6.0V at 150 mV increments.

Normally Dock DC, Power fail, and no battery fault thresholds are set in descending order respectively.

Upon assertion of either the nBATT\_FAULT or POWER\_FAIL pin the SMB122 and SMB122X can be programmed to respond in one of three ways, it may perform: a power-off operation, a force-shutdown operation, or take no action. When programmed to perform a power-off or force-shutdown operation the SMB122 can optionally be programmed to latch the outputs off until the power on pin is toggled or an I<sup>2</sup>C power-on command is issued.

### LDO STANDBY VOLTAGE

The LDO has a programmable output voltage from 1.5V to 3.75V. It is capable of supplying up to 80 mA and has UV and OV monitoring levels with corresponding fault responses. The channel 3 LDO can be sequenced on in any of the eight sequence positions, and can be enabled and disabled at any time.

#### **SOFT START**

The SMB122 and SMB122X provide a programmable soft-start function for all PWM outputs. The soft-start control limits the slew rate that each output is allowed to ramp up without the need for an external capacitor. The soft start slew rate is proportional to the product of the output voltage and a slew rate reference; see Figure 6. This global reference is programmable and may be set to 400, 200, 100, 67, 50, 33, 25, and 20 volts per second. The slew rate control can also be disabled on any channel not requiring the feature.

### **OUTPUT VOLTAGE**

The PWM output voltages are set by a resistive voltage divider from the output to the COMP1 node. For the Buck channels (Ch[7:5]), the voltage divider is internal to the part and programmable. The resistive divider may be set by adjusting a 100 k $\Omega$  resistor string with 8 taps from R1 = 20-90 k $\Omega$ . For the Boost outputs (Ch[2:1]), the resistive divider is external and any appropriate value of R1 an R2 can be chosen. The reference voltage that sets the output is user programmable, and may be set anywhere from 0-1.000 volt at 4 mV increments.

#### PROGRAMMABLE SWITCHING FREQUENCY

The SMB122 and SMB122X have a 1000kHz switching frequency. If a different frequency is desirable, please contact the Summit factory.

#### DYNAMIC VOLTAGE MANAGEMENT

The SMB122 and SMB122XX have three voltage settings, nominal, margin high, and margin low. The nominal setting is the voltage that the converter regulates at by default, while the margin high and margin low voltages are transitioned to by means of a volatile I<sup>2</sup>C write command. A status register is provided to indicate the current margin state of each channel.

A seven level margining option is available for channels 4 and 5 of the SMB122X device. When enabled, seven level margining allows channels 4 and 5 to be dynamically modified to one of seven pre-determined voltage levels. When seven level margining is enabled channels 0, 3, 6 and 7 loose the margin high and margin low settings.

While a channel is dynamically changing its voltage the UV/OV flags can be disabled temporarily, allowing the channels time to reached the new voltage settings.

Note: Configuration writes or reads of registers should not be performed while dynamic voltage management.

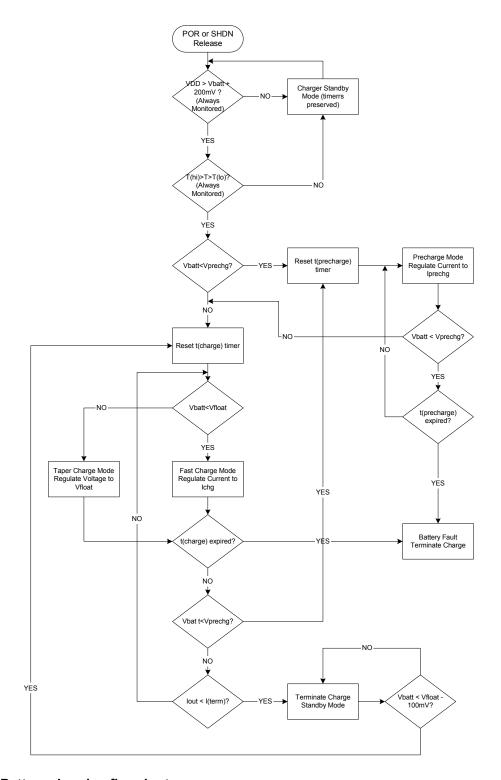

### **BATTERY CHARGER**

The SMB122 and SMB122X are equipped with a fully programmable lithium ion battery charger. The programmable feature set includes fast and pre-charge option, each with a programmable charge current level, a charge termination timeout period, an over and under temperature limit, multiple allowable recharge events, fault logging that can be accessed via the l<sup>2</sup>C interface and a general purpose output used to indicate the current status of the battery.

Battery charging is initiated by the detection a DC voltage on the DOCK\_DC input. When the voltage on DOCK\_DC exceeds the programmed minimum threshold voltage, the DC\_IN pin will be asserted indicating the successful connection of a charging input.

Once the charging voltage exceeds the DOCK\_DC threshold voltage, the SMB122 will be powered from the DOCK\_DC pin. Once the voltage on DOCK\_DC is above the programmed setting, battery charging will automatically commence. However, a programmable option allows the user to prevent battery charging until an I<sup>2</sup>C command has been issued. The SHDN pin is bypassed once voltage is sensed on the DOCK\_DC pin.

#### TRICKLE CHARGE

Once all pre-qualification conditions are met, the device checks the BSENSE voltage to decide if trickle charging is required. If the battery voltage is below approximately 2.0V, a charging current of 2mA (typical) is applied on the battery cell. This allows the SMB122 and SMB122X to reset the protection circuit in the battery pack and bring the battery voltage to a higher level without compromising safety.

### **PRE-CHARGE MODE**