### GS1503B HD Embedded Audio CODEC

GS1503B Data Sheet

#### **Features**

- complies with SMPTE 292M and SMPTE 299M

- · single chip HD embedded audio solution

- operates as an embedded audio multiplexer or demultiplexer

- full support for 48kHz synchronous 24-bit audio

- support for 8 channels of audio per device

- cascadable architecture supports up to 16 audio channels

- integrated scrambler/descrambler and word alignment

- CRC error detection and insertion

- audio control packet insertion and extraction

- arbitrary data packet insertion and extraction

- 3.3V power supply with 5V tolerant I/O

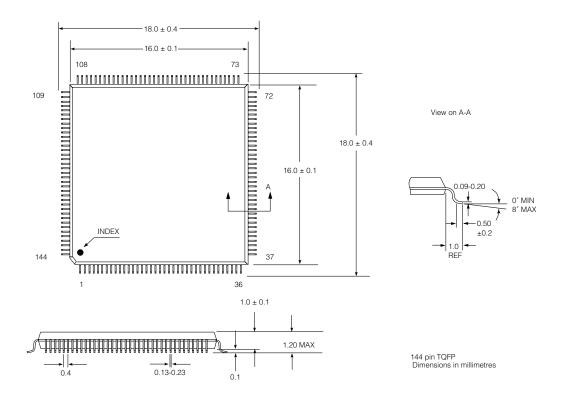

- 144 pin TQFP package

#### **Applications**

HD SDI Embedded Audio

#### **Description**

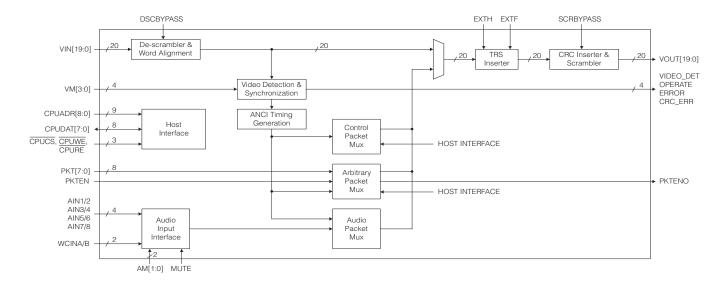

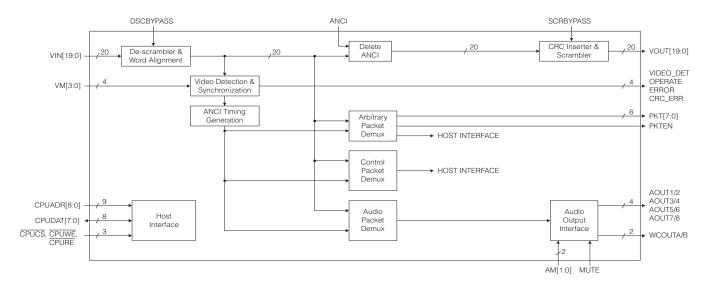

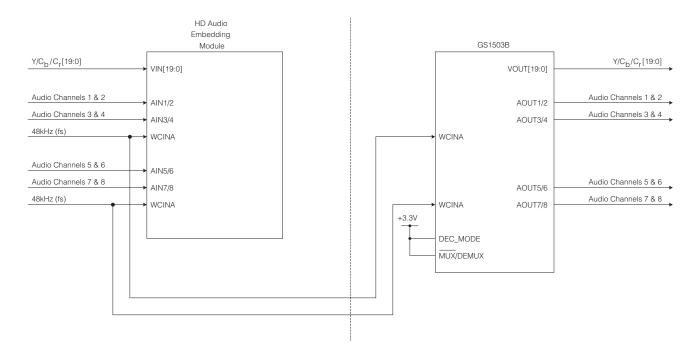

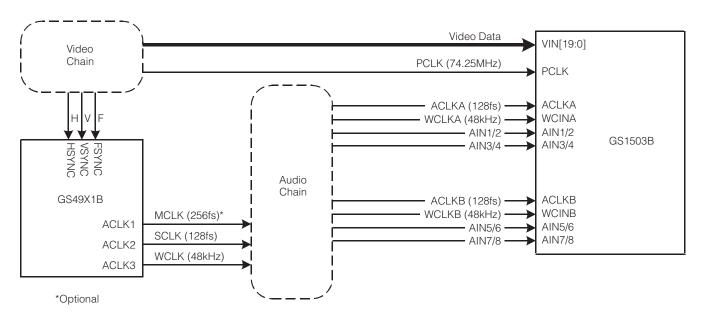

The GS1503B is a highly integrated, single chip solution for embedding/extracting digital audio streams into and out of high definition digital video signals. The GS1503B supports insertion/extraction of 24-bit synchronous audio data with a 48kHz sample rate. Audio signals with different sample rates may be converted to 48kHz by using audio sample rate converters before or after the GS1503B.

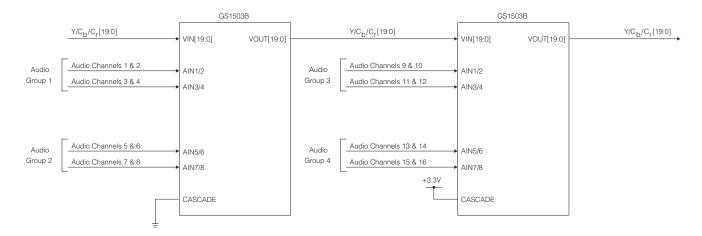

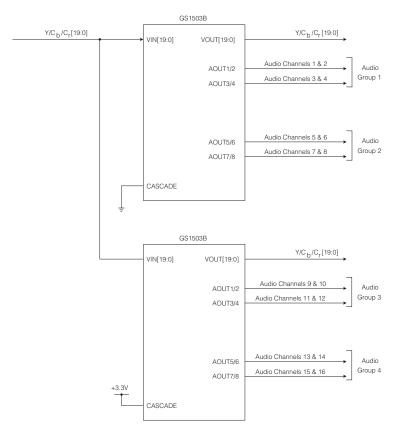

Each GS1503B supports all processing required for embedding/extracting up to eight digital audio channels in the horizontal ancillary data space of the video chroma channel. Two GS1503B's can be cascaded for insertion/extraction of up to 16 audio channels with no external glue logic.

The GS1503B supports embedding/extracting of audio control and arbitrary data packets in the horizontal ancillary data space of the video luma channel. It also supports line CRC detection and insertion.

The GS1503B supports HD video standards at 74.25MHz and 74.25/1.001MHz rates. It has an on chip SMPTE compliant scrambler/de-scrambler, and integrated word alignment. Use the GS1503B with Gennum's GS1545 or GS1522 for two chip HD SDI receive or transmit solutions.

The GS1503B operates from a single 3.3V power supply with 5V tolerant I/O and is packaged in a 144 pin TQFP package.

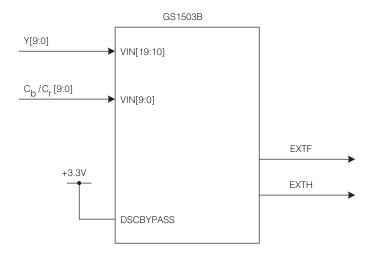

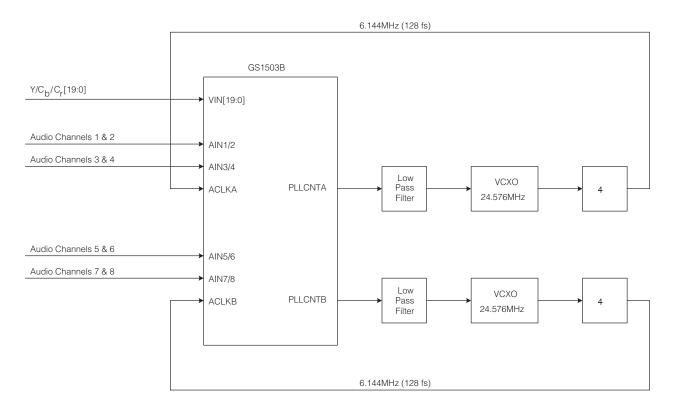

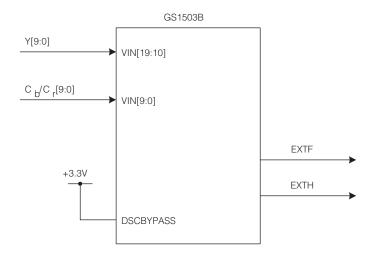

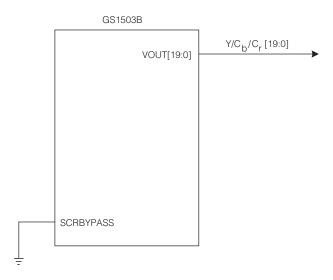

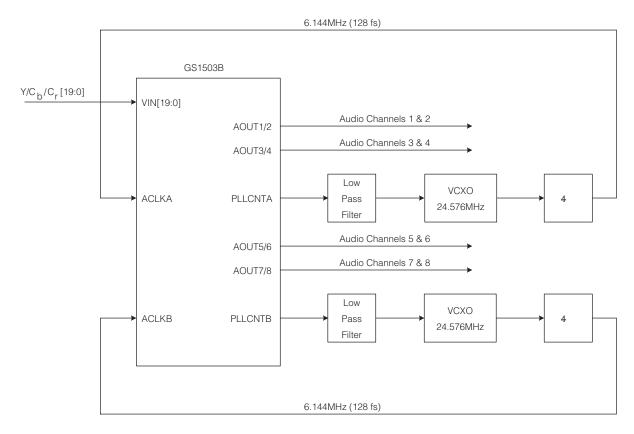

#### **Multiplex Mode Block Diagram**

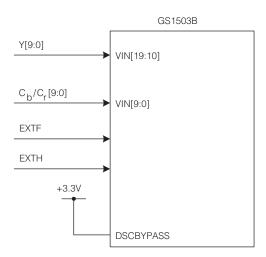

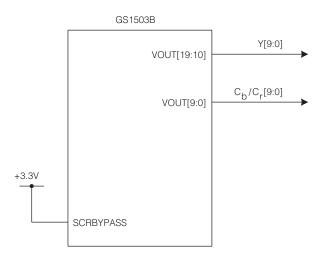

**Demultiplex Mode Block Diagram**

## **Contents**

| Features                                                             | 1  |

|----------------------------------------------------------------------|----|

| Applications                                                         | 1  |

| Description                                                          | 1  |

| 1. Pin Connections                                                   | 6  |

| 1.1 Pin Descriptions                                                 | 7  |

| 2. Electrical Characteristics                                        | 11 |

| 2.1 Absolute Maximum Ratings                                         | 11 |

| 2.2 DC Electrical Characteristics                                    | 11 |

| 2.3 AC Electrical Characteristics                                    | 12 |

| 2.4 Solder Reflow Profiles                                           |    |

| 3. Host Interface                                                    | 15 |

| 4. Detailed Description                                              | 18 |

| 4.1 Multiplex Mode                                                   | 18 |

| 4.1.1 Functional Overview                                            | 18 |

| 4.2 Video Standard                                                   | 19 |

| 4.3 Video Input Format                                               | 20 |

| 4.3.1 10-bit Y and Cb/Cr Input Video with TRS and Line Numbers       | 20 |

| 4.3.2 8-bit Y and Cb/Cr Input Video With TRS and Line Numbers        | 21 |

| 4.3.3 10-bit or 8-bit Y and Cb/Cr Input Without TRS and Line Numbers |    |

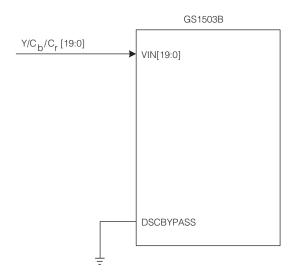

| 4.3.4 20-bit Scrambled Input                                         | 23 |

| 4.4 Video Output Format                                              | 24 |

| 4.4.1 20-bit Scrambled Output                                        | 24 |

| 4.4.2 10-bit Y and Cb/Cr Output                                      | 24 |

| 4.5 Video Data Processing                                            | 25 |

| 4.5.1 Video Signal Input Detection                                   | 25 |

| 4.5.2 Video Input CRC Error Detection                                | 25 |

| 4.5.3 Video Output CRC Insertion                                     | 26 |

| 4.5.4 Illegal Code Re-mapping                                        | 26 |

| 4.5.5 Input Blanking                                                 | 26 |

| 4.5.6 Line Number Insertion                                          | 27 |

| 4.5.7 TRS Word Insertion                                             | 27 |

| 4.6 Audio Data Processing                                            |    |

| 4.6.1 Digital Audio Input Format                                     | 28 |

| 4.6.2 Digital Audio Input Timing                                     | 29 |

| 4.6.3 Audio Clock Phase Locked Loop                                  | 31 |

| 4.6.4 Audio Signal Input Detection                                   | 31 |

| 4.6.5 Audio Channel Status CRC Error Detection                       | 32 |

| 4.6.6 Audio Input Parity Error Detection                             | 32 |

| 4.6.7 Audio Channel Status CRC Insert Function                       | 33 |

| 4.7 Audio Data Packets                                               | 33 |

|      | 4.7.1 Audio Data Packet Structure                          | 33 |

|------|------------------------------------------------------------|----|

|      | 4.7.2 Audio Data Packet DID Setting                        | 34 |

|      | 4.7.3 Audio Channel Multiplex Enable                       | 35 |

|      | 4.8 Video Switching Line Setting                           | 36 |

|      | 4.9 Multiplex Cascade Mode                                 | 37 |

|      | 4.10 Audio Control Packets                                 | 39 |

|      | 4.10.1 Audio Control Packet Structure                      | 39 |

|      | 4.10.2 Audio Control Packet DID Setting                    | 40 |

|      | 4.11 Arbitrary Data Packets                                | 42 |

|      | 4.11.1 Arbitrary Data Multiplexing In External Pin Mode    | 43 |

|      | 4.11.2 Arbitrary Data Multiplexing in Host Interface Mode  | 44 |

| 5. C | Demultiplex Mode                                           | 52 |

|      | 5.1 Functional Overview                                    | 52 |

|      | 5.2 Video Standard                                         | 53 |

|      | 5.3 Video Input Format                                     | 54 |

|      | 5.3.1 20-bit Scrambled Input                               | 54 |

|      | 5.3.2 10-bit Y and Cb/Cr Input with TRS and Line Numbers   | 55 |

|      | 5.4 Video Output Format                                    | 56 |

|      | 5.4.1 10-bit Y and Cb/Cr Output                            | 56 |

|      | 5.4.2 20-bit Scrambled Output                              | 56 |

|      | 5.5 Video Data Processing                                  | 57 |

|      | 5.5.1 Video Signal Input Detection                         | 57 |

|      | 5.5.2 Video Input CRC Error Detection                      | 57 |

|      | 5.5.3 Video Output CRC Insertion                           | 58 |

|      | 5.5.4 Input Blanking                                       | 58 |

|      | 5.5.5 Line Number Insertion                                | 58 |

|      | 5.5.6 TRS Word Insertion                                   | 59 |

|      | 5.6 Audio Data Processing                                  | 59 |

|      | 5.6.1 Digital Audio Output Format                          | 59 |

|      | 5.6.2 Digital Audio Output Timing                          | 60 |

|      | 5.6.3 Audio Clock Phase Locked Loop                        | 63 |

|      | 5.6.4 Audio Data Packet Detection                          | 64 |

|      | 5.6.5 ECC Error Detection & Correction                     | 64 |

|      | 5.6.6 Audio Data Packet Error Detection                    | 65 |

|      | 5.6.7 Audio Data Packet DID Setting                        | 66 |

|      | 5.7 Demultiplex Cascade Mode                               | 67 |

|      | 5.8 Audio Control Packets                                  | 68 |

|      | 5.8.1 Audio Control Packet Detection                       | 68 |

|      | 5.8.2 Audio Control Packet DID Setting                     |    |

|      | 5.9 Arbitrary Data Packets                                 | 70 |

|      | 5.9.1 Arbitrary Data Demultiplexing in External Pin Mode   | 71 |

|      | 5.9.2 Arbitrary Data Demultiplexing in Host Interface Mode | 71 |

|      | 5.10 Ancillary Data Deletion                               |    |

|      | 5.10.1 Entire Ancillary Data Deletion                      | 72 |

|      | 5.10.2 Audio Group Designation Ancillary Data Deletion     | 72 |

| 5.11 Demultiplex Mode With Word Clock Input      | 73 |

|--------------------------------------------------|----|

| 6. Using the GS1503B with the GS4911B or GS4910B | 85 |

| 7. References & Bibliography                     | 86 |

| 8. Packaging & Ordering Information              | 87 |

| 8.1 Package Dimensons                            | 87 |

| 8.2 Packaging Data                               | 87 |

| 8.3 Ordering Information                         | 87 |

| 9. Revision History                              | 88 |

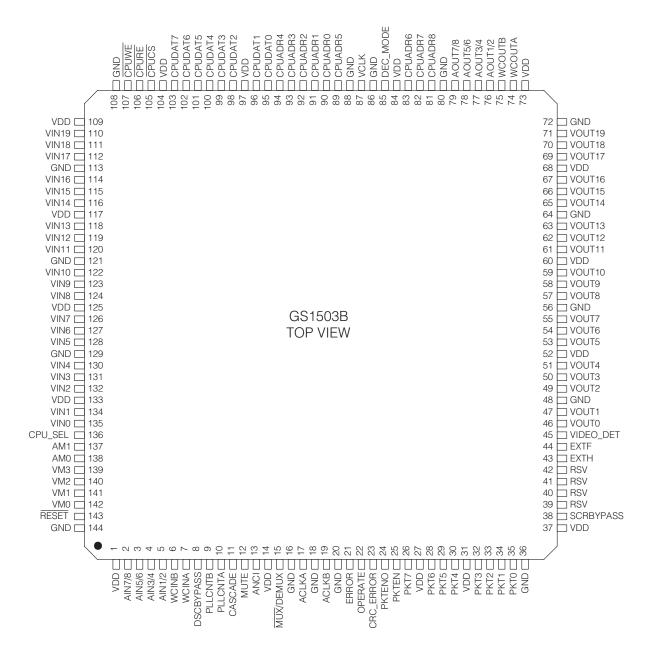

### 1. Pin Connections

# 1.1 Pin Descriptions

**Table 1-1: Pin Descriptions**

| Number                                                                            | Symbol    | Туре | Description                                                                                                                                                                                                                                                                                                                                                                               |

|-----------------------------------------------------------------------------------|-----------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 14, 27,<br>31, 37, 52,<br>60, 68, 73,<br>84, 97, 104,<br>109, 117,<br>125, 133 | VDD       | -    | +3.3V power supply pins.                                                                                                                                                                                                                                                                                                                                                                  |

| 2                                                                                 | AIN7/8    | 1    | Audio signal input for channels 7 and 8. AES/EBU digital audio data is bi-phase mark encoded. For all non-AES/EBU input modes, bi-phase mark encoding is not required.                                                                                                                                                                                                                    |

| 3                                                                                 | AIN5/6    | I    | Audio signal input for channels 5 and 6. AES/EBU digital audio data is bi-phase mark encoded. For all non-AES/EBU input modes, bi-phase mark encoding is not required.                                                                                                                                                                                                                    |

| 4                                                                                 | AIN3/4    | I    | Audio signal input for channels 3 and 4. AES/EBU digital audio data is bi-phase mark encoded. For all non-AES/EBU input modes, bi-phase mark encoding is not required.                                                                                                                                                                                                                    |

| 5                                                                                 | AIN1/2    | I    | Audio signal input for channels 1 and 2. AES/EBU digital audio data is bi-phase mark encoded. For all non-AES/EBU input modes, bi-phase mark encoding is not required.                                                                                                                                                                                                                    |

| 6                                                                                 | WCINB     | I    | 48kHz word clock for channels 5 to 8. Used only when operating in Multiplex Mode and when the audio source is not an AES/EBU data stream. This pin should be grounded when inputting AES/EBU digital audio data or when operating in Demultiplex Mode (DEC_MODE set LOW).                                                                                                                 |

| 7                                                                                 | WCINA     | I    | 48kHz word clock for channels 1 to 4. Used only when operating in Multiplex Mode and when the audio source is not an AES/EBU data stream. This pin should be grounded when inputting AES/EBU digital audio data or when operating in Demultiplex Mode (DEC_MODE set LOW).                                                                                                                 |

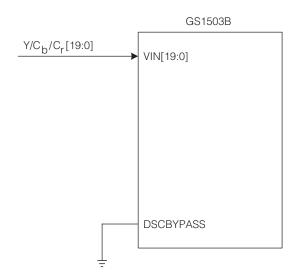

| 8                                                                                 | DSCBYPASS | I    | Descrambler bypass. When set LOW, the internal SMPTE 292M descrambler is enabled. When set HIGH, the internal SMPTE 292M descrambler is bypassed. The video input to the device must be word aligned.                                                                                                                                                                                     |

| 9                                                                                 | PLLCNTB   | 0    | Audio clock PLL control signal for channels 5 to 8.                                                                                                                                                                                                                                                                                                                                       |

| 10                                                                                | PLLCNTA   | 0    | Audio clock PLL control signal for channels 1 to 4.                                                                                                                                                                                                                                                                                                                                       |

| 11                                                                                | CASCADE   | I    | Cascade mode select. When set HIGH, the GS1503B will default to audio groups 3 and 4. Two GS1503B devices can then be cascaded in series to allow up to 16 channels of audio to be multiplexed or demultiplexed (only one device requires CASCADE to be set HIGH). When set LOW, the GS1503B will default to audio groups 1 and 2.                                                        |

| 12                                                                                | MUTE      | I    | Audio mute. In Multiplex Mode, when set HIGH, the embedded audio packets are forced to '0'. In Demultiplex Mode, when set HIGH, the audio output data is forced to "0".                                                                                                                                                                                                                   |

| 13                                                                                | ANCI      | I    | Ancillary data delete select. Valid in Demultiplex Mode only. When set HIGH, all ancillary data packets are removed from both the Luma and Chroma channels of the input video signal. The data contained in the packets are output at the corresponding pins. When set LOW, all ancillary data packets remain in the video signal. See Demultiplex Mode With Word Clock Input on page 73. |

| 15                                                                                | MUX/DEMUX | i    | Mode of operation. When set LOW, the GS1503B operates in Multiplex Mode.                                                                                                                                                                                                                                                                                                                  |

Table 1-1: Pin Descriptions (Continued)

| Number                                                                             | Symbol    | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|------------------------------------------------------------------------------------|-----------|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16, 18, 20,<br>36, 48, 56,<br>64, 72, 80,<br>86, 88, 108,<br>113, 121,<br>129, 144 | GND       | -    | Device ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

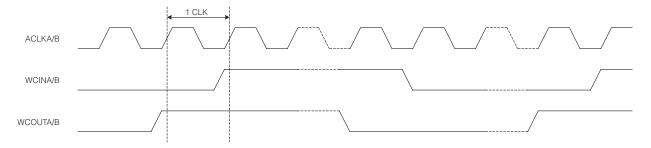

| 17                                                                                 | ACLKA     | I    | Input audio signal clock at 6.144 MHz (128 fs) for channels 1 to 4.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 19                                                                                 | ACLKB     | I    | Input audio signal clock at 6.144 MHz (128 fs) for channels 5 to 8.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 21                                                                                 | ERROR     | 0    | Format error indicator. When HIGH, the incoming video data stream contains TRS errors or there are errors within the incoming ancillary data packets.                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 22                                                                                 | OPERATE   | 0    | Audio processing indicator. When HIGH, audio data is being multiplexed or demultiplexed.                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 23                                                                                 | CRC_ERROR | 0    | CRC error indicator. Will be set HIGH when a CRC error is detected in the incoming video data stream.                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

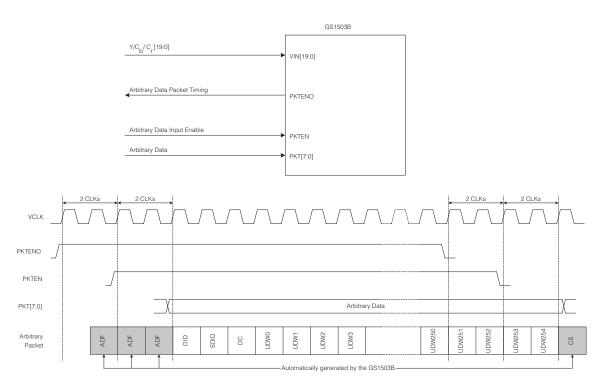

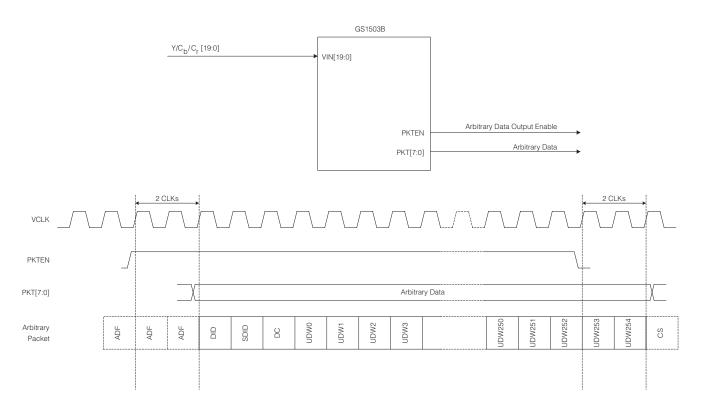

| 24                                                                                 | PKTENO    | 0    | Arbitrary data packet timing signal. Valid in Multiplex Mode only. Will be HIGH when arbitrary data packets can be input to the device. This signal is only valid when multiplexing arbitrary data packets via the PKT[7:0] bus. See Figure 4-22 for timing.                                                                                                                                                                                                                                                                                                           |

| 25                                                                                 | PKTEN     | I/O  | Arbitrary data packet enable. In Multiplex Mode, PKTEN is an input and must be set HIGH two VCLK cycles after the PKTENO signal goes HIGH. Arbitrary packet data is input to the device two VCLK cycles after PKTEN is set HIGH. In Demultiplex Mode, PKTEN is an output and is set HIGH two VCLK cycles before the device outputs arbitrary packet data. See Figure 4-22 and Figure 5-12.                                                                                                                                                                             |

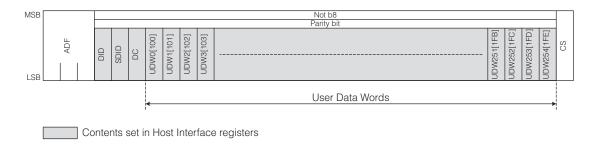

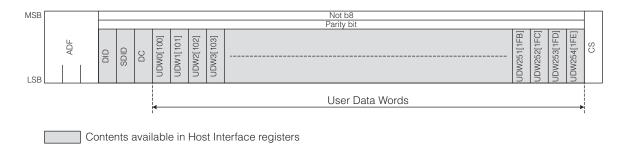

| 26, 28, 29,<br>30, 32, 33,<br>34, 35                                               | PKT[7:0]  | I/O  | Arbitrary data I/O bus. PKT[7] is the MSB and PKT[0] is the LSB. In Multiplex Mode, the user must input the arbitrary data packet words starting from the data identification (DID) to the last user data word (UDW) according to SMPTE 291M. The GS1503B internally converts the data to 10 bits by generating the parity bit (bit 8) and inversion bit (bit 9). The checksum (CS) word is also generated internally. In Demultiplex Mode, the GS9023 outputs the arbitrary data packet words starting from the DID to the last UDW. See Figure 4-22 and Figure 5-12. |

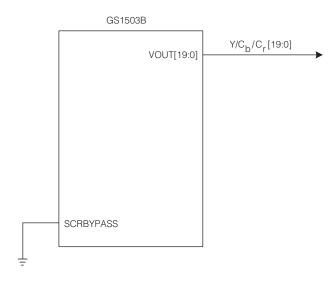

| 38                                                                                 | SCRBYPASS | I    | Scrambler bypass. When set LOW, the output video stream is scrambled according to SMPTE 292M and NRZ(I) encoded. When set HIGH, the scrambler and NRZ(I) encoder are bypassed.                                                                                                                                                                                                                                                                                                                                                                                         |

| 39, 40, 41,<br>42                                                                  | RSV       | -    | Connect to ground.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

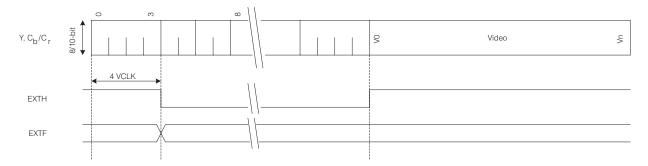

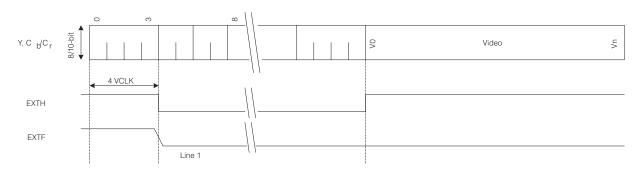

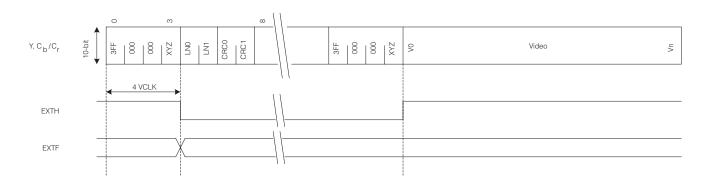

| 43                                                                                 | EXTH      | I/O  | Horizontal sync signal. The GS1503B outputs a horizontal sync signal derived from the incoming TRS. In Multiplex Mode, with EXT_SEL set HIGH in the Host Interface, a horizontal sync signal can be input to the device for TRS and line number insertion.                                                                                                                                                                                                                                                                                                             |

| 44                                                                                 | EXTF      | I/O  | Field sync signal. The GS1503B outputs a field sync signal derived from the incoming TRS. In Multiplex Mode, with EXT_SEL set HIGH in the Host Interface, a field sync signal can be input to the device for TRS and line number insertion. For progressive formats, a signal with a high to low transition at the position of line one must be provided. See Figure 4-6 and Figure 4-7.                                                                                                                                                                               |

| 45                                                                                 | VIDEO_DET | 0    | Video input signal detection. Indicates that the device has detected a valid video input stream.  NOTE: When EXT_SEL is set HIGH in the Host Interface, VIDEO_DET will indicate when valid EXTH and EXTF signals have been detected.                                                                                                                                                                                                                                                                                                                                   |

Table 1-1: Pin Descriptions (Continued)

| Number                                                                                                                        | Symbol      | Туре | Description                                                                                                                                                                                                                                                                                                                                                                   |

|-------------------------------------------------------------------------------------------------------------------------------|-------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 71, 70, 69,<br>67, 66, 65,<br>63, 62, 61,<br>59, 58, 57,<br>55, 54, 53,<br>51, 50, 49,<br>47, 46                              | VOUT[19:0]  | 0    | Parallel digital video signal output. VOUT[19] is the MSB and VOUT[0] is the LSB.                                                                                                                                                                                                                                                                                             |

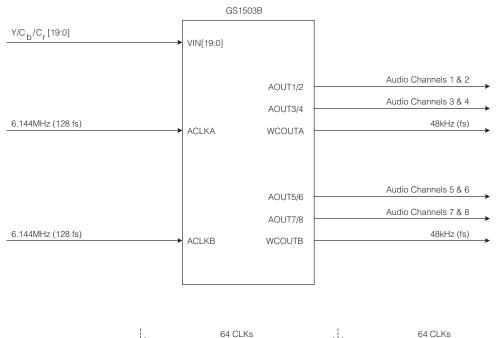

| 74                                                                                                                            | WCOUTA      | 0    | 48kHz word clock for channels 1 to 4. Valid only when operating in Demultiplex Mode.                                                                                                                                                                                                                                                                                          |

| 75                                                                                                                            | WCOUTB      | 0    | 48kHz word clock for channels 5 to 8. Valid only when operating in Demultiplex Mode.                                                                                                                                                                                                                                                                                          |

| 76                                                                                                                            | AOUT1/2     | 0    | Audio signal output for channels 1 and 2. The AES/EBU digital audio output is bi-phase mark encoded. In both non-AES/EBU modes, the output is not bi-phase mark encoded.                                                                                                                                                                                                      |

| 77                                                                                                                            | AOUT3/4     | 0    | Audio signal output for channels 3 and 4. The AES/EBU digital audio output is bi-phase mark encoded. In both non-AES/EBU modes, the output is not bi-phase mark encoded.                                                                                                                                                                                                      |

| 78                                                                                                                            | AOUT5/6     | 0    | Audio signal output for channels 5 and 6. The AES/EBU digital audio output is bi-phase mark encoded. In both non-AES/EBU modes, the output is not bi-phase mark encoded.                                                                                                                                                                                                      |

| 79                                                                                                                            | AOUT7/8     | 0    | Audio signal output for channels 7 and 8. The AES/EBU digital audio output is bi-phase mark encoded. In both non-AES/EBU modes, the output is not bi-phase mark encoded.                                                                                                                                                                                                      |

| 85                                                                                                                            | DEC_MODE    | I    | Demultiplex Mode select. Valid in Demultiplex Mode only. When set HIGH, the GS1503B requires a 48kHz word clock input at WCINA and WCINB. This word clock must be synchronous to the word clock used to embed the audio data. The embedded audio clock phase information in the ancillary data packet will be ignored. See Demultiplex Mode With Word Clock Input on page 73. |

| 87                                                                                                                            | VCLK        | I    | Video clock signal input.                                                                                                                                                                                                                                                                                                                                                     |

| 81, 82, 83,<br>89, 94, 93,<br>92, 91, 90                                                                                      | CPUADR[8:0] | I    | Host Interface address bus. CPUADR[8] is the MSB and CPUADR[0] is the LSB. In Host Interface Mode B (CPU_SEL set LOW), CPUADR[1:0] are used as the Host Interface control bus. See Table 3-4.                                                                                                                                                                                 |

| 103, 102,<br>101, 100,<br>99, 98, 96,<br>95                                                                                   | CPUDAT[7:0] | I/O  | Host Interface data bus. CPUDAT[7] is the MSB and CPUDAT[0] is the LSB.  Host Interface Mode B (CPU_SEL set LOW), CPUDAT[7:0] are used as the Host Interface address and data bus.                                                                                                                                                                                            |

| 105                                                                                                                           | CPUCS       | I    | Chip select for Host Interface. Active LOW.                                                                                                                                                                                                                                                                                                                                   |

| 106                                                                                                                           | CPURE       | I    | Read enable for Host Interface. Active LOW. In Host Interface Mode B (CPU_SEL set LOW), this input is not used.                                                                                                                                                                                                                                                               |

| 107                                                                                                                           | CPUWE       | I    | Write enable for Host Interface. Active LOW. In Host Interface Mode B (CPU_SEL set LOW), this input is used as the Host Interface control enable.                                                                                                                                                                                                                             |

| 110, 111,<br>112, 114,<br>115, 116,<br>118, 119,<br>120, 122,<br>123, 124,<br>126, 127,<br>128, 130,<br>131, 132,<br>134, 135 | VIN[19:0]   | I    | Parallel digital video signal input. VIN[19] is the MSB and VIN[0] is the LSB.                                                                                                                                                                                                                                                                                                |

#### Table 1-1: Pin Descriptions (Continued)

| Number                | Symbol  | Туре | Description                                                                                                                                                                                                                       |

|-----------------------|---------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 136                   | CPU_SEL | I    | Host Interface mode select. When set HIGH, the GS1503B is configured for Host Interface Mode A. When set LOW, the GS1503B is configured for Host Interface Mode B.                                                                |

| 137, 138              | AM[1:0] | I    | Audio format select. In Multiplex Mode, AM[1:0] indicates the input audio data format. In Demultiplex Mode, AM[1:0] indicates the output audio data format. AM[1] is the MSB and AM[0] is the LSB. See Table 4-16 and Table 5-13. |

| 139, 140,<br>141, 142 | VM[3:0] | I    | Video standard select. VM[3] is the MSB and VM[0] is the LSB. See Table 4-1 or Table 5-1.                                                                                                                                         |

| 143                   | RESET   | 1    | Device reset. Active LOW.                                                                                                                                                                                                         |

GS1503B Data Sheet

# 2. Electrical Characteristics

# 2.1 Absolute Maximum Ratings

| Parameter                             | Value          |

|---------------------------------------|----------------|

| Supply Voltage                        | -0.3V to 4.0V  |

| Input Voltage (any input)             | -0.3 to 5.5V   |

| Operating Temperature                 | 0°C to 70°C    |

| Storage temperature                   | -65°C to 150°C |

| Lead Temperature (soldering, 10 sec.) | 260°C          |

## 2.2 DC Electrical Characteristics

#### **Table 2-1: DC Electrical Characteristics**

$T_A = 0$ °C to 70°C unless otherwise shown.

| Parameter                   | Symbol          | Conditions                     | Min                  | Тур | Max | Units |

|-----------------------------|-----------------|--------------------------------|----------------------|-----|-----|-------|

| Supply Voltage              | $V_{DD}$        | 3.3V operating range           | 3.0                  | 3.3 | 3.6 | V     |

| Supply Current              | I <sub>DD</sub> | V <sub>DD</sub> = 3.3V         |                      | 270 |     | mA    |

| Input Current               | I <sub>IN</sub> | _                              | -1                   | -   | 1   | μА    |

| Hi-Z Output Leakage Current | l <sub>OZ</sub> | _                              | -1                   | -   | 1   | μΑ    |

| Output Voltage, Logic High  | V <sub>OH</sub> | I <sub>OH</sub> = -12mA        | V <sub>DD</sub> -0.4 | -   | -   | V     |

| Output Voltage, Logic Low   | V <sub>OL</sub> | I <sub>OL</sub> = 12mA         | _                    | -   | 0.4 | V     |

| Input Voltage, Logic High   | V <sub>IH</sub> | TTL Level                      | 2.0                  | -   | _   | V     |

| Input Voltage, Logic Low    | V <sub>IL</sub> | TTL Level                      | _                    | -   | 0.8 | V     |

| Input Capacitance           | C <sub>I</sub>  | f = 1MHz, V <sub>DD</sub> = 0V | _                    | -   | 10  | pF    |

| Output Capacitance          | C <sub>O</sub>  | f = 1MHz, V <sub>DD</sub> = 0V | _                    | -   | 10  | pF    |

| I/O Capacitance             | C <sub>IO</sub> | f = 1MHz, V <sub>DD</sub> = 0V | _                    | _   | 10  | pF    |

GS1503B Data Sheet

### 2.3 AC Electrical Characteristics

**Table 2-2: AC Electrical Characteristics**

$\rm V_{DD}$  = 3.3V ± 5%,  $\rm T_A$  = 0°C to 70°C unless otherwise shown.

| Parameter                    | Symbol             | Conditions         | Min  | Тур   | Max  | Units |

|------------------------------|--------------------|--------------------|------|-------|------|-------|

| Video Clock Frequency        |                    | -                  | _    | 74.25 | 80   | MHz   |

| Video Clock Pulse Width Low  | t <sub>VPWL</sub>  | -                  | 5.0  | _     | _    | ns    |

| Video Clock Pulse Width High | t <sub>VPWH</sub>  | _                  | 5.0  | _     | _    | ns    |

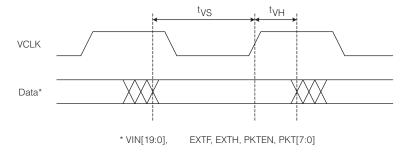

| Video Input Data Setup Time  | t <sub>VS</sub>    | -                  | 3.5  | -     | -    | ns    |

| Video Input Data Hold Time   | t <sub>VH</sub>    | -                  | 1.0  | -     | -    | ns    |

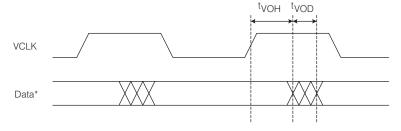

| Video Output Data Delay Time | $t_{VOD}$          | With 10pF loading  | -    | -     | 8.5  | ns    |

| Video Output Data Hold Time  | $t_{VOH}$          | With 10pF loading  | 1.0  | -     | -    | ns    |

| Audio Clock Frequency        |                    | _                  | -    | 6.144 | _    | MHz   |

| Audio Clock Pulse Width Low  | t <sub>APWL</sub>  | -                  | 60   | -     | _    | ns    |

| Audio Clock Pulse Width High | t <sub>APWH</sub>  | -                  | 60   | -     | _    | ns    |

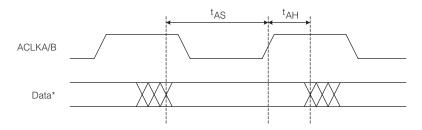

| Audio Input Data Setup Time  | t <sub>AS</sub>    | -                  | 10.5 | -     | _    | ns    |

| Audio Input Data Hold Time   | t <sub>AH</sub>    | -                  | 1.0  | -     | _    | ns    |

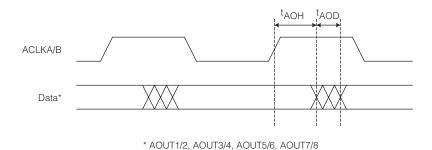

| Audio Output Data Delay Time | t <sub>AOD</sub>   | With 10pF loading  | _    | _     | 20.0 | ns    |

| Audio Output Data Hold Time  | t <sub>AOH</sub>   | With 10pF loading  | 1.0  | _     | -    | ns    |

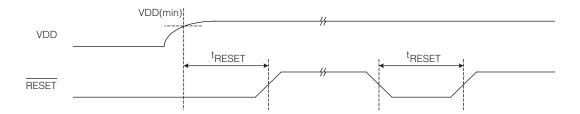

| Reset Pulse Width            | t <sub>RESET</sub> | -                  | 1    | _     | -    | ms    |

| Device Latency               | _                  | Multiplexer Mode   | 53   | 53    | 53   | PCLKs |

|                              |                    | Demultiplexer Mode | 53   | 53    | 53   |       |

Figure 2-1: Video Data Input Setup & Hold Time

\* VOUT[19:0], EXTF, EXTH, PKTEN, PKT[7:0]

Figure 2-2: Video Data Output Delay & Hold Time

\* WCINA, AIN1/2, AIN3/4, WCINB, AIN5/6, AIN7/8

Figure 2-3: Audio Data Input Setup & Hold Time

Figure 2-4: Audio Data Output Delay & Hold Time

Figure 2-5: Reset Timing

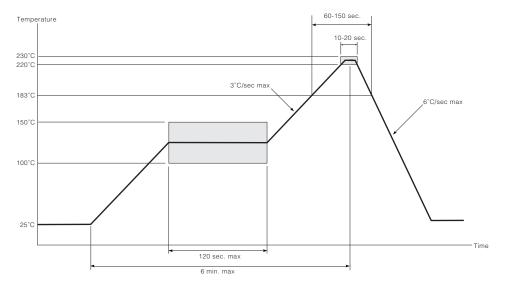

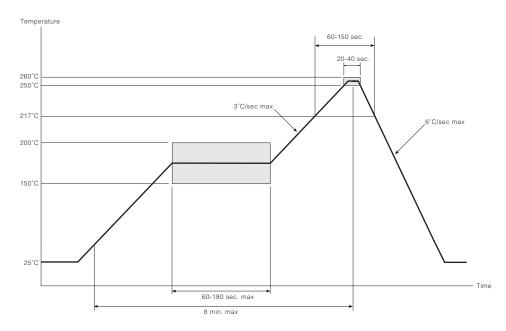

### 2.4 Solder Reflow Profiles

Figure 2-6: Maximum Pb-Free Solder Reflow Profile (Preferred)

Figure 2-7: Standard Eutectic Solder Reflow Profile

# 3. Host Interface

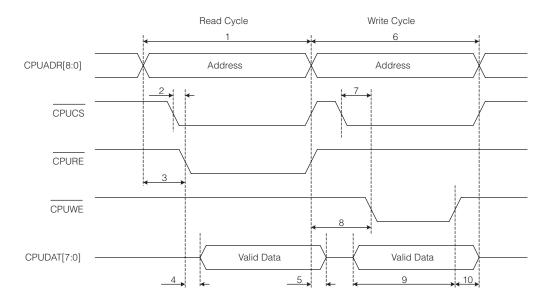

Table 3-1: Mode A (CPU\_SEL set HIGH)

| Parameter                    | Number | Min | Тур | Max | Units |

|------------------------------|--------|-----|-----|-----|-------|

| Read Cycle Time              | 1      | 50  | -   | _   | ns    |

| Read Chip Select Setup Time  | 2      | 0   | -   | _   | ns    |

| Read Address Setup Time      | 3      | 15  | -   | _   | ns    |

| Read Data Output Delay Time  | 4      | _   | -   | 15  | ns    |

| Read Data Hold Time          | 5      | 0   | -   | _   | ns    |

| Write Cycle Time             | 6      | 50  | -   | _   | ns    |

| Write Chip Select Setup Time | 7      | 10  | -   | _   | ns    |

| Write Address Setup Time     | 8      | 10  | -   | _   | ns    |

| Write Data Setup Time        | 9      | 10  | -   | _   | ns    |

| Write Data Hold Time         | 10     | 0   | -   | _   | ns    |

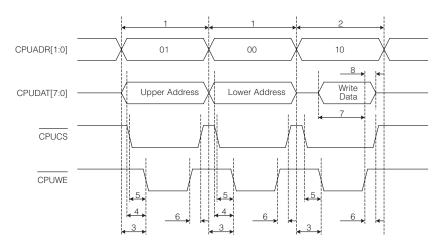

Figure 3-1: Host Interface Mode A Timing (CPU\_SEL set HIGH)

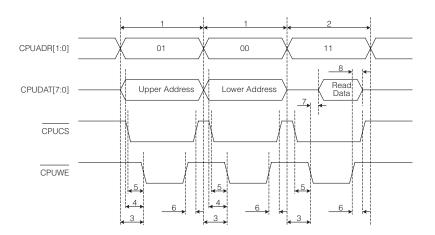

Table 3-2: Mode B Read Cycle (CPU\_SEL set LOW)

| Parameter                   | Number | Min | Тур | Max | Units |

|-----------------------------|--------|-----|-----|-----|-------|

| Read Address Cycle Time     | 1      | 80  | -   | _   | ns    |

| Read Cycle Time             | 2      | 80  | -   | -   | ns    |

| Read Enable Setup Time      | 3      | 20  | -   | -   | ns    |

| Read Address Setup Time     | 4      | 20  | -   | _   | ns    |

| Read Chip Select Setup Time | 5      | 10  | -   | _   | ns    |

| Read Chip Select Hold Time  | 6      | 0   | -   | _   | ns    |

| Read Data Output Delay Time | 7      | -   | -   | 10  | ns    |

| Read Data Hold Time         | 8      | 0   | _   | _   | ns    |

Figure 3-2: Host Interface Mode B Read Cycle Timing (CPU\_SEL set LOW)

Table 3-3: Mode B Write Cycle (CPU\_SEL set LOW)

| Parameter                    | Number | Min | Тур | Max | Units |

|------------------------------|--------|-----|-----|-----|-------|

| Write Address Cycle Time     | 1      | 80  | -   | _   | ns    |

| Write Cycle Time             | 2      | 80  | -   | _   | ns    |

| Write Enable Setup Time      | 3      | 20  | -   | _   | ns    |

| Write Address Setup Time     | 4      | 20  | -   | _   | ns    |

| Write Chip Select Setup Time | 5      | 10  | -   | -   | ns    |

| Write Chip Select Hold Time  | 6      | 0   | -   | -   | ns    |

| Write Data Setup Time        | 7      | 30  | -   | -   | ns    |

| Write Data Hold Time         | 8      | 0   | -   | _   | ns    |

Figure 3-3: Host Interface Mode B Write Cycle Timing (CPU\_SEL set LOW)

Table 3-4: Host Interface Mode B Control Codes

| CPUADR[1:0] | Data Bus Operation |

|-------------|--------------------|

| 01          | Upper Address      |

| 00          | Lower Address      |

| 11          | Read Data          |

| 10          | Write Data         |

# 4. Detailed Description

### 4.1 Multiplex Mode

#### 4.1.1 Functional Overview

The GS1503B HD Embedded Audio CODEC fully supports the multiplexing of Audio Data Packets, Audio Control Packets and Arbitrary Data Packets as per SMPTE 291M and 299M. The device can be configured to operate with all video standards defined in SMPTE 292M, levels A through M. The GS1503B also supports the 1080/24PsF, 25PsF and 30PsF video formats as described in SMPTE RP211.

The video input format can be one of the following configurations:

- 10-bit Y and C<sub>b</sub>/C<sub>r</sub> input with TRS and Line Numbers

- 8-bit Y and C<sub>h</sub>/C<sub>r</sub> input with TRS and Line Numbers

10-bit or 8-bit Y and  $C_b/C_r$  input without TRS and Line Numbers (GS1503B will insert TRS and Line Numbers based on EXTF and EXTH inputs)

· 20-bit scrambled input

The video output format can be one of the following configurations:

- · 20-bit scrambled output

- 10-bit Y and C<sub>b</sub>/C<sub>r</sub> output

Up to a maximum of 8 channels of 48kHz digital audio can be multiplexed per device. The audio input format can be selected as either AES/EBU, or one of two serial audio data input modes. A maximum of 16 channels of audio can be multiplexed by serially cascading two devices.

Audio control packets, as defined in SMPTE 299M, can also be multiplexed to provide information to receivers about the nature of the embedded audio data. The contents of the audio control packet can be programmed via the Host Interface.

The GS1503B will also multiplex arbitrary data packets as defined in SMPTE 291M. The arbitrary data packets can serve as an auxiliary data signal for proprietary applications. The GS1503B can be configured to multiplex arbitrary data packets, input via the Host Interface or using dedicated external pins. Up to a maximum of 255 8-bit words can be multiplexed (excluding Ancillary Data Flags and Checksum).

To use the GS1503B in Multiplex Mode, set the MUX/DEMUX external pin LOW.

GS1503B Data Sheet

#### 4.2 Video Standard

The video standard is selected from the VM[3:0] external pins or VM[3:0] bits 3-0 in Host Interface register 000h. To configure the video standard via the Host Interface, VM\_SEL bit 7 in Host Interface register 000h must be set HIGH. The GS1503B will default to the VM[3:0] external pin setting. The supported video standards are listed in Table 4-1.

Table 4-1: Supported Video Standards

| VM [3:0]               | Input Format                    | Reference SMPTE Document | SMPTE 292M Level |

|------------------------|---------------------------------|--------------------------|------------------|

| 1110b                  | 1035i (30 & 30/1.001 Hz)        | 260M                     | A, B             |

| 1100b                  | 1080i (25 Hz)                   | 295M                     | С                |

| 1000b                  | 1080i/1080sF (30 & 30/1.001 Hz) | 274M, RP211              | D, E             |

| 1010b                  | 1080i/1080sF (25 Hz)            | 274M, RP211              | F                |

| 1111b                  | 1080sF (24 & 24/1.001 Hz)       | RP211                    |                  |

| 0010b                  | 1080p (30 & 30/1.001 Hz)        | 274M                     | G, H             |

| 0100b                  | 1080p (25 Hz)                   | 274M                     | I                |

| 0110b                  | 1080p (24 & 24/1.001 Hz)        | 274M                     | J, K             |

| 0000b                  | 720p (60 & 60/1.001 Hz)         | 296M                     | L, M             |

| 0001b                  | 720p (30 & 30/1.001 Hz)         | 296M                     |                  |

| 0011b                  | 720p (50 Hz)                    | 296M                     |                  |

| 0101b                  | 720p (25 Hz)                    | 296M                     |                  |

| 0111b                  | 720p (24 & 24/1.001 Hz)         | 296M                     |                  |

| All other settings are | reserved                        |                          |                  |

Table 4-2: Register Settings

| Name    | Description                                  | Address | Bit | Setting          | Default |

|---------|----------------------------------------------|---------|-----|------------------|---------|

| VM_SEL  | 0: External pin select<br>1: Register select | 000     | 7   | 1                | 0       |

| VM[3:0] | Video formal selection (VM[3] is MSB)        | 000     | 3-0 | See<br>Table 4-1 | 0       |

# 4.3 Video Input Format

### 4.3.1 10-bit Y and $C_b/C_r$ Input Video with TRS and Line Numbers

Figure 4-1: Configuration for 10-bit Y and  $\mathrm{C_b}/\mathrm{C_r}$  Input Video with TRS and Line Numbers

Figure 4-2: Video Input Format 10-bit with TRS and Line Numbers

**Table 4-3: Register Settings**

| Name      | Description                                          | Address | Bit | Setting | Default |

|-----------|------------------------------------------------------|---------|-----|---------|---------|

| EXT_SEL   | 0: EXTH/EXTF output select 1: EXTH/EXTF input select | 001     | 3   | 0       | 0       |

| 8BIT_SEL  | 0: 10-bit mode select<br>1: 8-bit mode select        | 001     | 1   | 0       | 0       |

| DSCBYPASS | Descrambling enabled     Bypass descrambling         | 001     | 0   | 1       | 0       |

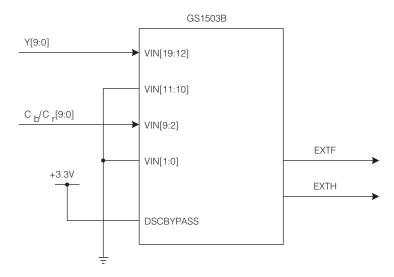

## 4.3.2 8-bit Y and $C_b/C_r$ Input Video With TRS and Line Numbers

Figure 4-3: Configuration for 8-bit Y and  $C_b/C_r$  Input Video with TRS and Line Numbers

Figure 4-4: Video Input Format 8-bit with TRS and Line Numbers

Table 4-4: Register Settings

| Name      | Description                                          | Address | Bit | Setting | Default |

|-----------|------------------------------------------------------|---------|-----|---------|---------|

| EXT_SEL   | 0: EXTH/EXTF output select 1: EXTH/EXTF input select | 001     | 3   | 0       | 0       |

| 8BIT_SEL  | 0: 10-bit mode select<br>1: 8-bit mode select        | 001     | 1   | 1       | 0       |

| DSCBYPASS | 0: Descrambling enabled 1: Bypass descrambling       | 001     | 0   | 1       | 0       |

### 4.3.3 10-bit or 8-bit Y and $C_b/C_r$ Input Without TRS and Line Numbers

The GS1503B will insert TRS and Line Numbers based on EXTF and EXTH inputs. See Figure 4-6 for timing. In progressive format video standards, a high-to-low edge signal must be input at the EXTF external pin on every frame to indicate the position of line 1. See Figure 4-7.

Figure 4-5: Configuration for 10-bit or 8-bit Y and  $\rm C_b/\rm C_r$  Input Video without TRS and Line Numbers

Figure 4-6: Video Input Format (8/10-bit without TRS and Line Numbers)

Figure 4-7: 15 Video Input Format (Progressive)

Proprietary and Confidential 37953 - 0 August 2006

Table 4-5: Register Settings

| Name      | Description                                          | Address | Bit | Setting | Default |

|-----------|------------------------------------------------------|---------|-----|---------|---------|

| EXT_SEL   | 0: EXTH/EXTF output select 1: EXTH/EXTF input select | 001     | 3   | 1       | 0       |

| 8BIT_SEL  | 0: 10-bit mode select<br>1: 8-bit mode select        | 001     | 1   | 0 or 1  | 0       |

| DSCBYPASS | Descrambling enabled     Bypass descrambling         | 001     | 0   | 1       | 0       |

## 4.3.4 20-bit Scrambled Input

Figure 4-8: Configuration for 20-bit Scrambled Input

Table 4-6: Register Settings (Default Mode)

| Name      | Description                                          | Address | Bit | Setting | Default |

|-----------|------------------------------------------------------|---------|-----|---------|---------|

| EXT_SEL   | 0: EXTH/EXTF output select 1: EXTH/EXTF input select | 001     | 3   | 0       | 0       |

| 8BIT_SEL  | 0: 10-bit mode select<br>1: 8-bit mode select        | 001     | 1   | 0       | 0       |

| DSCBYPASS | 0: Descrambling enabled 1: Bypass descrambling       | 001     | 0   | 0       | 0       |

# 4.4 Video Output Format

### 4.4.1 20-bit Scrambled Output

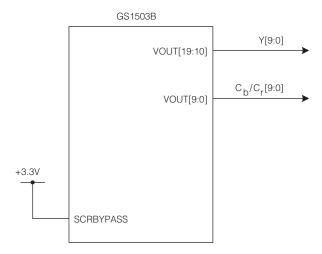

Figure 4-9: Configuration for 20-bit Scrambled Output

Table 4-7: Register Settings (Default Mode)

| Name      | Description                      | Address | Bit | Setting | Default |

|-----------|----------------------------------|---------|-----|---------|---------|

| SCRBYPASS | 0: SMPTE 292M scrambling enabled | 001     | 2   | 0       | 0       |

|           | 1: Bypass SMPTE 292M scrambling  |         |     |         |         |

## 4.4.2 10-bit Y and $C_b/C_r$ Output

Figure 4-10: Configuration for 10-bit Y and  $C_b/C_r$  Output

Proprietary and Confidential 37953 - 0 August 2006

**Table 4-8: Register Settings**

| Name      | Description                                                      | Address | Bit | Setting | Default |

|-----------|------------------------------------------------------------------|---------|-----|---------|---------|

| SCRBYPASS | 0: SMPTE 292M scrambling enabled 1: Bypass SMPTE 292M scrambling | 001     | 2   | 1       | 0       |

# 4.5 Video Data Processing

### 4.5.1 Video Signal Input Detection

The GS1503B will set the VIDEO\_DET external pin HIGH when three consecutive TRS are detected in the input video signal. Also, the VIDEO\_DET bit of Host Interface register 000h is set HIGH.

Table 4-9: Register Settings

| Name      | Description                                 | Address | Bit | Setting | Default |

|-----------|---------------------------------------------|---------|-----|---------|---------|

| VIDEO_DET | Video input signal detection (1: Detection) | 000     | 6   | -       | 0       |

### 4.5.2 Video Input CRC Error Detection

The GS1503B will set the CRC\_ERR external pin HIGH when a CRC error is detected in the input video signal. Also, the CRC\_ERR bit 5 of Host Interface register 000h is set HIGH. The number of CRC errors accumulated in one video frame can be read form CRC\_CNT[11:0] in Host Interface registers 006h and 007h.

Table 4-10: Register Settings

| Name          | Description                                                | Address    | Bit        | Setting | Default |

|---------------|------------------------------------------------------------|------------|------------|---------|---------|

| CRC_ERR       | Video input signal CRC error detection (1: Detection)      | 000        | 5          | -       | 0       |

| CRC_CNT[11:0] | Video input signal CRC error accumulation in 1 video frame | 006<br>007 | 3-0<br>7-0 | -       | 0       |

### 4.5.3 Video Output CRC Insertion

When the CRC\_INS bit 4 of Host Interface register 000h is set HIGH, the GS1503B will re-calculate the video line CRC words. The re-calculated CRC words are inserted in the video output signal. When CRC\_INS is set LOW, the line CRC words are not updated and existing CRC words at the input of the device will be output unchanged.

Table 4-11: Register Settings

| Name    | Description                             | Address | Bit | Setting | Default |

|---------|-----------------------------------------|---------|-----|---------|---------|

| CRC_INS | Video line CRC insertion (1: Insertion) | 000     | 4   | 1       | 1       |

#### 4.5.4 Illegal Code Re-mapping

When LIMIT\_ON bit 4 of Host Interface register 008h is set HIGH, input video words between 000-003 are re-mapped to 004, and values between 3FC-3FF are re-mapped to 3FB. Valid only when the EXT\_SEL bit 3 of Host Interface register 000h is set HIGH.

**Table 4-12: Register Settings**

| Name     | Description                                          | Address | Bit | Setting | Default |

|----------|------------------------------------------------------|---------|-----|---------|---------|

| EXT_SEL  | 0: EXTH/EXTF output select 1: EXTH/EXTF input select | 001     | 3   | 1       | 0       |

| LIMIT_ON | Illegal code re-mapping (1: Enabled)                 | 008     | 4   | 1       | 0       |

# 4.5.5 Input Blanking

When VBLK\_INS bit 3 of Host Interface register 008h is set HIGH, the input video vertical blanking will be set to 040h for the Luma channel and 200h for the Chroma channel.

When HBLK\_INS bit 2 of Host Interface register 008h is set HIGH, the input video horizontal blanking will be set to 040h for the Luma channel and 200h for the Chroma channel. The TRS, line number and CRC words will also be set to blanking values.

The blanking function is performed at the output of the GS1503B video data stream. If the HBLK\_INS bit is set HIGH, any multiplexed audio will be replaced with blanking codes.

Table 4-13: Register Settings

| Name     | Description                            | Address | Bit | Setting | Default |

|----------|----------------------------------------|---------|-----|---------|---------|

| VBLK_INS | Input vertical blanking (1: Enabled)   | 800     | 3   | 1       | 0       |

| HBLK_INS | Input horizontal blanking (1: Enabled) | 800     | 2   | 1       | 0       |

#### 4.5.6 Line Number Insertion

When LN\_INS bit 1 of Host Interface register 008h is set HIGH, the GS1503B will insert line numbers into the video data stream. When set LOW, existing line numbers will remain in the output video stream.

When EXT\_SEL bit 3 of Host Interface register 001h is set HIGH, line numbers will be inserted based on the timing of EXTH and EXTF input signals.

**Table 4-14: Register Settings**

| Name   | Description                        | Address | Bit | Setting | Default |

|--------|------------------------------------|---------|-----|---------|---------|

| LN_INS | Line number insertion (1: Enabled) | 800     | 1   | 1       | 1       |

#### 4.5.7 TRS Word Insertion

When TRS\_INS bit 0 of Host Interface register 008h is set HIGH, the GS1503B will insert TRS codes into the video data stream. When set LOW, existing TRS codes will remain in the output video stream.

When EXT\_SEL bit 3 of Host Interface register 001h is set HIGH, TRS codes will be inserted based on the timing of EXTH and EXTF input signals.

**Table 4-15: Register Settings**

| Name    | Description                     | Address | Bit | Setting | Default |

|---------|---------------------------------|---------|-----|---------|---------|

| TRS_INS | TRS word insertion (1: Enabled) | 008     | 0   | 1       | 1       |

# 4.6 Audio Data Processing

#### 4.6.1 Digital Audio Input Format

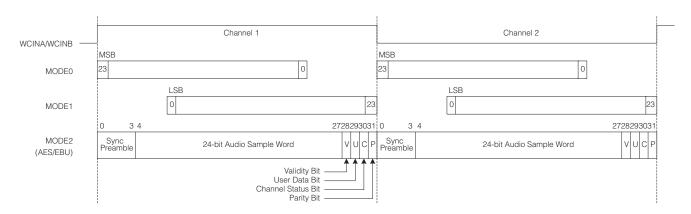

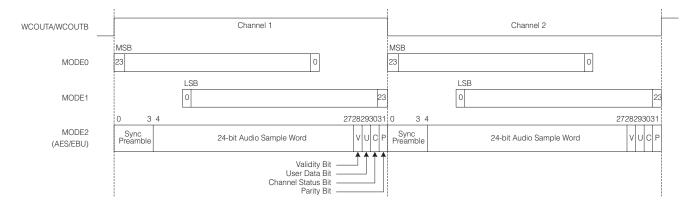

The GS1503B will accept two audio input formats, AES/EBU digital audio input and serial input, as listed in Table 4-16. Serial input can be formatted in the following two modes. See Figure 4-11.

- · 24-bit Left Justified; MSB first

- 24-bit Right Justified; MSB last

The audio input format is configured using the AM[1:0] external pins or via AM[1:0] bits 1-0 in Host Interface register 010h. To configure the audio input format via the Host Interface, AM\_SEL bit 7 in Host Interface register 010h must be set HIGH. The GS1503B will default to the AM[1:0] external pin setting.

Table 4-16: Audio Input Formats

| AM[1:0] | Audio Input Format                                   |

|---------|------------------------------------------------------|

| 0       | Serial audio input: 24-bit Left Justified; MSB first |

| 1       | Serial audio input: 24-bit Right Justified; MSB last |

| 2       | AES/EBU audio input                                  |

Table 4-17: Register Settings

| Name    | Description                                 | Address | Bit | Setting           | Default |

|---------|---------------------------------------------|---------|-----|-------------------|---------|

| AM_SEL  | External pin setting     Register setting   | 010     | 7   | 1                 | 0       |

| AM[1:0] | Audio input format selection (AM[1] is MSB) | 010     | 1-0 | See<br>Table 4-11 | 0       |

Figure 4-11: Audio Input Formats

#### 4.6.2 Digital Audio Input Timing

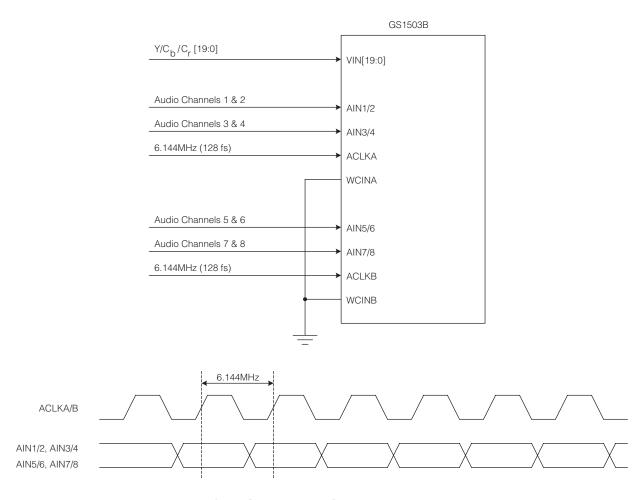

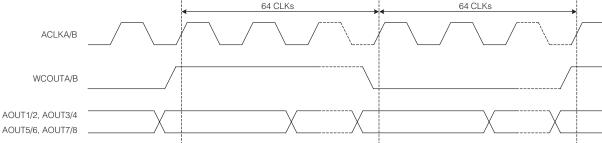

#### 4.6.2.1 AES/EBU Format Input

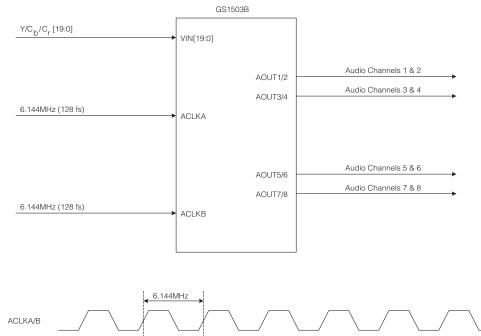

A 6.144MHz (128fs) audio clock must be supplied to the ACLKA and ACLKB inputs. ACLKA is used to clock the AES/EBU digital audio signal for channels 1 to 4 (AIN1/2 and AIN3/4) into the device. ACLKB is used to clock the AES/EBU digital audio signal for channels 5 to 8 (AIN5/6 and AIN7/8) into the device. In AES/EBU input mode, the WCINB and WCINB external pins should be grounded. See Figure 4-12 for timing.

Figure 4-12: AES/EBU Input Configuration and Timing

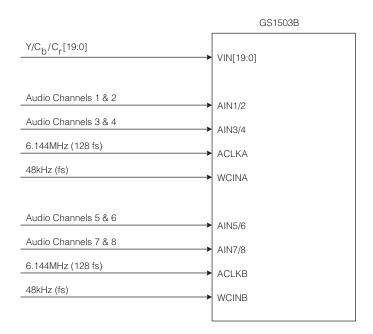

#### 4.6.2.2 Serial Audio Input Modes

A 6.144MHz (128fs) audio clock must be supplied to the ACLKA and ACLKB inputs. The GS1503B divides this clock by 2 to clock the 3.072MHz audio data. An audio word clock at 48kHz (fs) must also be supplied to the WCINA and WCINB inputs, as shown in Figure 4-13. The AUDIO\_CS[183:0] bits in Host Interface registers 058h to 06Eh can be used to enter the 23 8-bit bytes of the Audio Channel Status Block, as defined in AES3-1992. NOTE: The CRC byte is generated internally by the GS1503B. The GS1503B will default to Professional audio mode with 24-bit word length and emphasis off. See Table 4-34.

Figure 4-13: Serial Audio Input Configuration and Timing

Proprietary and Confidential 37953 - 0 August 2006

### 4.6.3 Audio Clock Phase Locked Loop

Figure 4-14 shows the configuration for deriving the 6.144MHz audio clock in AES/EBU audio input mode. The GS1503B will internally synchronize the AES/EBU audio input to the corresponding ACLK, using the clock extracted from the AES/EBU bi-phase mark encoding. This configuration is not required for serial audio input modes.

Figure 4-14: Block Diagram of GS1503B Audio Clock PLL

#### 4.6.4 Audio Signal Input Detection

The audio input signal detect registers will be set HIGH in AES/EBU audio mode when the preamble of the audio input data is detected 3 times consecutively. In serial audio input mode, the GS1503B will set the audio input signal detect registers HIGH when a 48kHz word clock is detected at the corresponding inputs. Audio channels 1 to 4 will be set when WCINA is validated, and audio channels 5 to 8 when WCINB is validated. Host Interface register 010h, bits 6-3, report the individual audio channels pairs detected.

Table 4-18: Register Settings

| Name       | Description                                      | Address | Bit | Setting | Default |

|------------|--------------------------------------------------|---------|-----|---------|---------|

| AUD7/8_DET | Ch7/8 Audio input signal detection (1:Detection) | 010     | 6   | -       | 0       |

| AUD5/6_DET | Ch5/6 Audio input signal detection (1:Detection) | 010     | 5   | _       | 0       |

| AUD3/4_DET | Ch3/4 Audio input signal detection (1:Detection) | 010     | 4   | -       | 0       |

| AUD1/2_DET | Ch1/2 Audio input signal detection (1:Detection) | 010     | 3   | -       | 0       |

#### 4.6.5 Audio Channel Status CRC Error Detection

In AES/EBU audio mode, the GS1503B will check the Channel Status CRC for errors. If any Channel Status CRC errors are detected in an AES/EBU audio input channel pair, the corresponding bit in Host Interface register 011h will be set HIGH. In serial audio input mode, the CRC error flags are always set LOW.

Table 4-19: Register Settings

| Name        | Description                                                   | Address | Bit | Setting | Default |

|-------------|---------------------------------------------------------------|---------|-----|---------|---------|

| ACRC7/8_ERR | Ch7/8 Audio Channel Status CRC error detection (1: Detection) | 011     | 3   | -       | 0       |

| ACRC5/6_ERR | Ch5/6 Audio Channel Status CRC error detection (1: Detection) | 011     | 2   | -       | 0       |

| ACRC3/4_ERR | Ch3/4 Audio Channel Status CRC error detection (1: Detection) | 011     | 1   | -       | 0       |

| ACRC1/2_ERR | Ch1/2 Audio Channel Status CRC error detection (1: Detection) | 011     | 0   | -       | 0       |

#### 4.6.6 Audio Input Parity Error Detection

In AES/EBU audio mode, the GS1503B will check for Audio Parity errors. If any Audio Parity errors are detected in an AES/EBU audio input channel pair, the corresponding bit in Host Interface register 012h will be set HIGH. In serial audio input mode, the Audio Parity error flags are always set LOW.

Table 4-20: Register Settings

| Name      | Description                                       | Address | Bit | Setting | Default |

|-----------|---------------------------------------------------|---------|-----|---------|---------|

| AP7/8_ERR | Ch7/8 Audio parity error detection (1: Detection) | 012     | 3   | _       | 0       |

| AP5/6_ERR | Ch5/6 Audio parity error detection (1: Detection) | 012     | 2   | _       | 0       |

| AP3/4_ERR | Ch3/4 Audio parity error detection (1: Detection) | 012     | 1   | _       | 0       |

| AP1/2_ERR | Ch1/2 Audio parity error detection (1: Detection) | 012     | 0   | _       | 0       |

Proprietary and Confidential 37953 - 0 August 2006

**GENNUM**

#### 4.6.7 Audio Channel Status CRC Insert Function

When bits 7-4 of Host Interface register 011h are set HIGH, the GS1503B will re-calculate the Channel Status CRC word for the corresponding audio input channel pair. The re-calculated Channel Status CRC word is multiplexed into the audio data packet as per SMPTE 299M. When bits 3-0 of Host Interface register 011h are set LOW, the Channel Status CRC word is not updated and the existing Channel Status CRC word will be multiplexed. In serial audio input mode, these registers should be set LOW.

Table 4-21: Register Settings

| Name        | Description                                             | Address | Bit | Setting | Default |

|-------------|---------------------------------------------------------|---------|-----|---------|---------|

| ACRC7/8_INS | Ch7/8 Audio Channel Status CRC insertion (1: Insertion) | 011     | 7   | 1       | 0       |

| ACRC5/6_INS | Ch5/6 Audio Channel Status CRC insertion (1: Insertion) | 011     | 6   | 1       | 0       |

| ACRC3/4_INS | Ch3/4 Audio Channel Status CRC insertion (1: Insertion) | 011     | 5   | 1       | 0       |

| ACRC1/2_INS | Ch1/2 Audio Channel Status CRC insertion (1: Insertion) | 011     | 4   | 1       | 0       |

#### 4.7 Audio Data Packets

#### 4.7.1 Audio Data Packet Structure

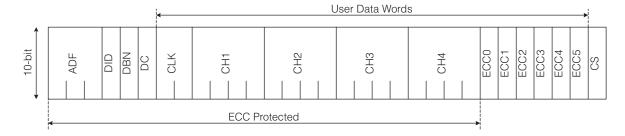

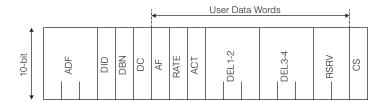

Figure 4-15 shows the structure of the audio data packets as defined in SMPTE 299M. The audio data packets are multiplexed into the Chroma channel of the video data stream. Table 4-22 lists the description of the individual audio data packet words. Note that the GS1503B will automatically generate certain audio data packet words.

Figure 4-15: Audio Data Packet Structure

Table 4-22: Audio Data Packet Word Descriptions

| Name   | No of<br>Words | Description                                                       | Data         | Auto-Generation   |

|--------|----------------|-------------------------------------------------------------------|--------------|-------------------|

| ADF    | 3              | Ancillary Data Flag                                               | 000h         | Yes               |

|        |                |                                                                   | 3FFh         |                   |

|        |                |                                                                   | 3FFh         |                   |

| DID    | 1              | Audio Group Data ID                                               | 2E7h         | See Table 4-23 in |

|        |                |                                                                   | 1E6h         | Section 4.7.2     |

|        |                |                                                                   | 1E5h         |                   |

|        |                |                                                                   | 2E4h         |                   |

| DBN    | 1              | Data Block Number                                                 | Repeat 1-255 | Yes               |

| DC     | 1              | Data Count                                                        | 218h         | Yes               |

| CLK    | 2              | Audio Clock Phase Data                                            | _            | Yes               |

| CH1    | 4              | Channel 1 audio data                                              | _            |                   |

| CH2    | 4              | Channel 2 audio data                                              | _            |                   |

| СНЗ    | 4              | Channel 3 audio data                                              | _            |                   |

| CH4    | 4              | Channel 4 audio data                                              | _            |                   |

| ECC0-5 | 6              | Error correction code for lower 8 bits of first 24 words          | _            | Yes               |

| CS     | 1              | Checksum. Calculates the sum of lower 9 bits of 22 words from DID | -            | Yes               |

### 4.7.2 Audio Data Packet DID Setting

The audio group DID for audio input channels 1 to 4 (AIN1/2 and AIN3/4) is set in DATAIDA[1:0] bits 1-0 of Host Interface register 014h. The audio group DID for audio input channels 5 to 8 (AIN5/6 and AIN7/8) is set in DATAIDB[1:0] bits 3-2 of Host Interface register 014h. Table 4-23 shows the 2-bit Host Interface setting for the corresponding audio group DID.

When CASCADE is set LOW (external pin or register), the GS1503B will default to audio groups 1 and 2, where AIN1/2 and AIN3/4 will be multiplexed with audio group 1 DID, and AIN5/6 and AIN7/8 with audio group 2 DID.

Table 4-23: Audio Data Packet Group DID Host Interface Setting

| Audio Group | 10-bit Data | Host Interface Register Setting (2-bit) |  |  |  |

|-------------|-------------|-----------------------------------------|--|--|--|

| 1           | 2E7h        | 11b                                     |  |  |  |

| 2           | 1E6h        | 10b                                     |  |  |  |

| 3           | 1E5h        | 01b                                     |  |  |  |

| 4           | 2E4h        | 00b                                     |  |  |  |

Proprietary and Confidential 37953 - 0 August 2006

Table 4-24: Register Settings (CASCADE set LOW)

| Name          | Description                         | Address | Bit | Setting    | Default |

|---------------|-------------------------------------|---------|-----|------------|---------|

| DATAIDA [1-0] | Ch1-4 Audio data packet DID setting | 014     | 1-0 | See        | 11b     |

| DATAIDB [1-0] | Ch5-8 Audio data packet DID setting | 014     | 3-2 | Table 4-23 | 10b     |

When CASCADE is set HIGH (external pin or register), the GS1503B will default to audio groups 3 and 4, where AIN1/2 and AIN3/4 will be multiplexed with audio group 3 DID, and AIN5/6 and AIN7/8 with audio group 4 DID.

Table 4-25: Register Settings (CASCADE set HIGH)

| Name          | Description                         | Address | Bit | Setting    | Default |

|---------------|-------------------------------------|---------|-----|------------|---------|

| DATAIDA [1-0] | Ch1-4 Audio data packet DID setting | 014     | 1-0 | See        | 01b     |

| DATAIDB [1-0] | Ch5-8 Audio data packet DID setting | 014     | 3-2 | Table 4-23 | 00b     |

#### 4.7.3 Audio Channel Multiplex Enable

Multiplexing of individual audio channels is enabled using the CHACT[7:0] bits 7-0 of Host Interface register 013h. When set HIGH, the corresponding audio channel is multiplexed into the audio data packet in the Chroma video data stream. CHACT7 corresponds to audio input channel 8 and CHACT0 corresponds to audio input channel 1. When all bits are set LOW, no audio data packets will be multiplexed and the GS1503B will be in bypass mode.

Table 4-26: Register Settings

| Name   | Description                       | Address | Bit | Setting | Default |

|--------|-----------------------------------|---------|-----|---------|---------|

| CHACT7 | Ch8 multiplex enable (1: Enabled) | 013     | 7   | _       | 1       |

| CHACT6 | Ch7 multiplex enable (1: Enabled) | 013     | 6   | _       | 1       |

| CHACT5 | Ch6 multiplex enable (1: Enabled) | 013     | 5   | _       | 1       |

| CHACT4 | Ch5 multiplex enable (1: Enabled) | 013     | 4   | _       | 1       |

| СНАСТЗ | Ch4 multiplex enable (1: Enabled) | 013     | 3   | _       | 1       |

| CHACT2 | Ch3 multiplex enable (1: Enabled) | 013     | 2   | -       | 1       |

| CHACT1 | Ch2 multiplex enable (1: Enabled) | 013     | 1   | -       | 1       |

| CHACT0 | Ch1 multiplex enable (1: Enabled) | 013     | 0   | _       | 1       |

# 4.8 Video Switching Line Setting

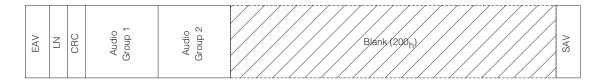

The video switching point for field 1 and field 2 can be configured via the GS1503B Host Interface. The SW\_LNA[12:0] register is used to configure the video switching line for field 1, and SW\_LNB[12:0] to set video switching line for field 2. In progressive format video standards, only the SW\_LNA[12:0] register is used. The default settings are line 7 for field 1 and line 569 for field 2 as defined in SMPTE 299M.

The GS1503B will not multiplex any audio data packets in the line immediately after the video switching point. For example, with the default setting of line 7 field 1, there will be no audio data packets in line 8. The next packets will appear on line 9. Audio control packets will be multiplexed once per field, two lines after the video switching point (on line 9, using the previous example). Arbitrary data packets will not be multiplexed in the two lines following the video switching point.

NOTE: The SMPTE 299M standard defines the video switching point as lines 7 and 569. If the SW\_LNA[12:0] and SW\_LNB[12:0] registers are programmed with values other than lines 7 and 569, the output of the GS1503B is not guaranteed to be compatible with all HD audio demultiplex systems. With non-SMPTE 299M compliant switch line settings, the user should avoid inputting a video data stream to the GS1503B, which already contains embedded audio data and control packets.

For reliable operation, non-SMPTE 299M compliant video data streams with embedded audio should not be used in conjunction with the GS1503B in Multiplex Mode.

Table 4-27: Register Settings

| Name         | Description                           | Address | Bit | Setting | Default |

|--------------|---------------------------------------|---------|-----|---------|---------|

| SW_LNA[12:0] | Video Field 1 switching point setting | 004     | 4-0 | _       | 7d      |

|              |                                       | 005     | 7-0 |         |         |

| SW_LNB[12:0] | Video Field 2 switching point setting | 002     | 4-0 | _       | 569d    |

|              |                                       | 003     | 7-0 |         |         |

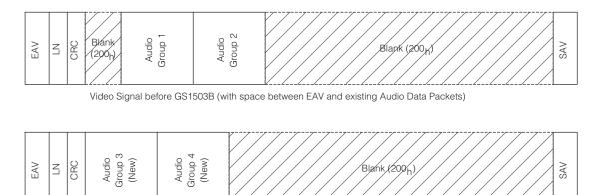

# 4.9 Multiplex Cascade Mode