# **Sitronix**

## ST7533

33 x 96 Dot Matrix LCD Controller/Driver

### FEATURES

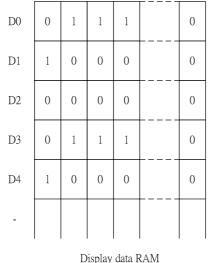

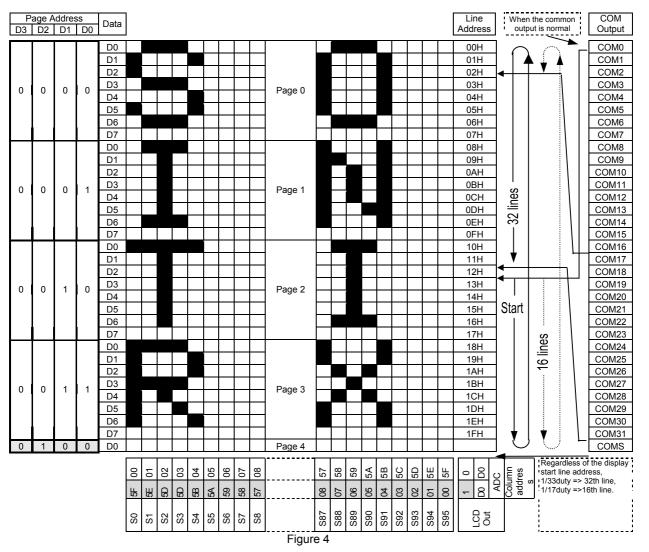

- Direct display of RAM data through the display data RAM.

- RAM capacity : 33 x 96 = 3168 bits

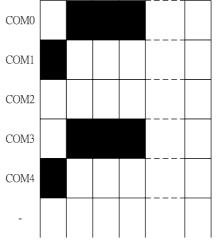

- Display duty selectable by select pin 1/33 duty : 33 common x 96 segment 1/17 duty : 17 common x 96 segment

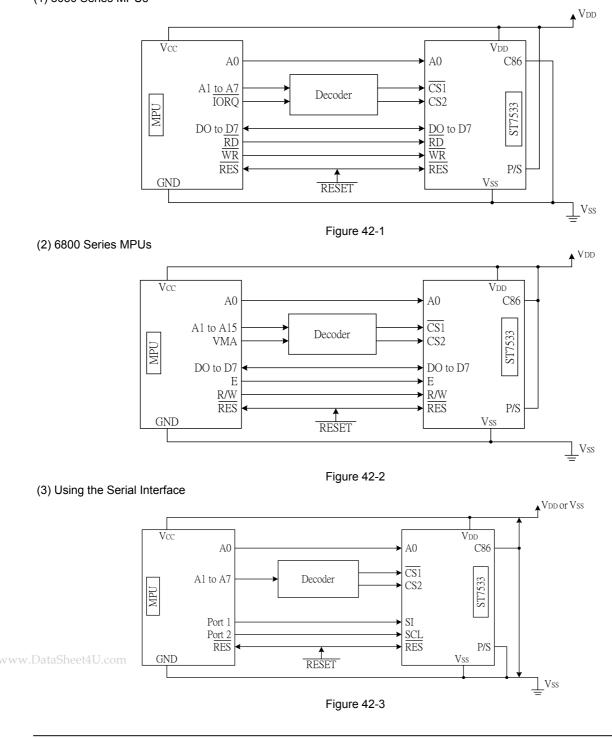

- High-speed 8-bit MPU interface (The chip can be connected directly to the both the 80x86 series MPUs and the 68000 series MPUs) /Serial interfaces are supported.

- Abundant command functions

Display data Read/Write, display ON/OFF, Normal/ Reverse display mode, page address set, display start line set, column address set, status read, display all points ON/OFF, LCD bias set, electronic volume, read/modify/write, segment driver direction select, power saver, static indicator, common output status select, V5 voltage regulation internal resistor ratio set.

- Static drive circuit equipped internally for indicators. (1 system, with variable flashing speed.)

- Low-power liquid crystal display power supply circuit equipped internally.

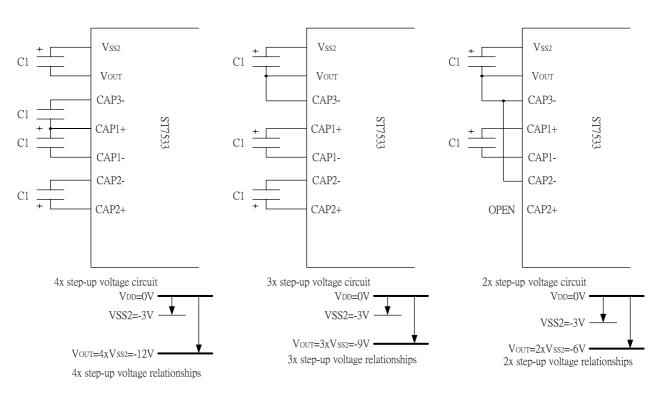

Booster circuit (with Boost ratios of 2X/3X/4X , where the step-up voltage reference power supply can be input externally). High-accuracy voltage adjustment circuit (Thermal

**GENERAL DESCRIPTION**

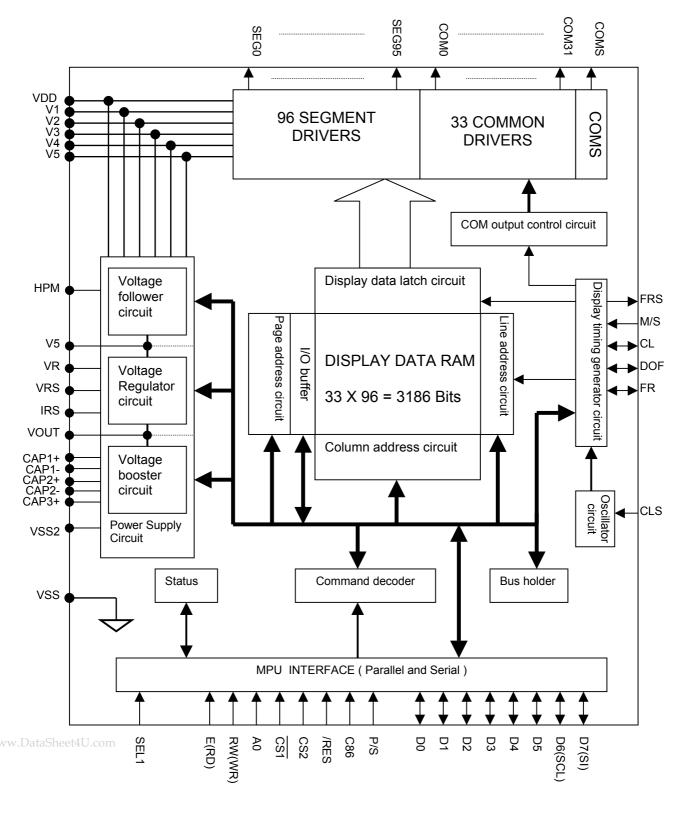

The ST7533 is a single-chip dot matrix LCD drivers that can be connected directly to a microprocessor bus. 8-bit parallel or serial display data sent from the microprocessor is stored in the internal display data RAM and the chip generates a LCD drive signal independent of the microprocessor. Because the chips in the ST7533 contain 33x96 bits of display data RAM and there is a 1-to-1 correspondence between the LCD panel pixels and the internal RAM bits, these chips enable displays with a high degree of freedom.

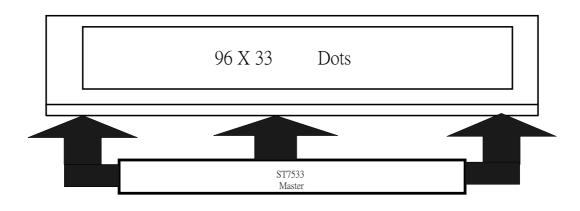

The ST7533 chips contain 33 common output circuits and 96 segment output circuits, so that a single chip can drive a 33x96 dot display (capable of displaying 8 columnsx4 rows of DataSheetd L com

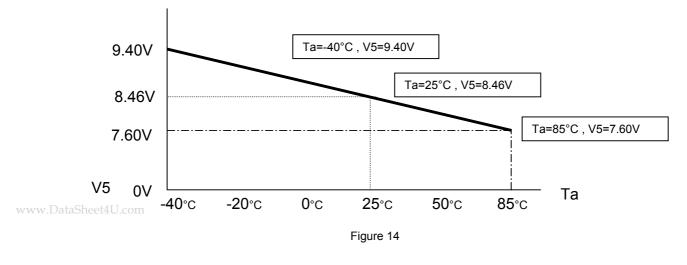

gradient –0.15%/°C ) V5 voltage regulator resistors equipped internally, V1 to V4 voltage divider resistors equipped internally, electronic volume function equipped internally, voltage follower.

• CR oscillator circuit equipped internally (external clock can also be input)

Extremely low power consumption Operating power when the built-in power supply is used (an example) 70uA (VDD – VSS = VDD – VSS2 = 3.0 V, Quad voltage, V5 – VDD = – 11.0 V).

Conditions: When displays pattern OFF and the normal mode is selected.

- Power supply operate on the low 1.8 voltage Logic power supply

VDD – VSS = 1.8V to 3.3V (+10% Range)

Boost reference voltage: VDD – VSS2 = 1.8V to 3.3V

Booster maximum voltage limited

VOUT= -13V (+10% Range)

Liquid crystal drive power supply:

VDD – V5 = 4.0V to 13.0 V

- Wide range of operating temperatures: -40 to 85°C

- CMOS process

- These chips not designed for resistance to light or resistance to radiation.

a 16x16 dot kanji font).

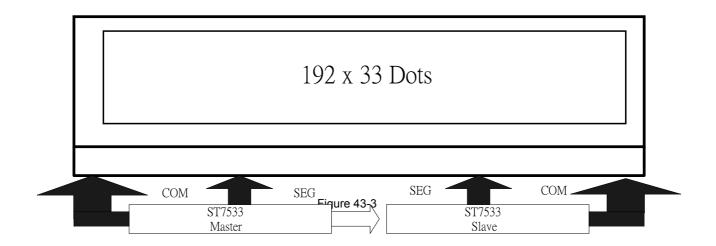

Moreover, the capacity of the display can be extended through the use of master/slave structures between chips. The chips are able to minimize power consumption because no external operating clock is necessary for the display data RAM read/write operation. Furthermore, because each chip is equipped internally with a low-power LCD driver power supply, resistors for LCD driver power voltage adjustment and a display clock CR oscillator circuit, the ST7533 can be used to create the lowest power display system with the fewest components for high-performance portable devices.

| ſ | PART NO. | VRS temperature gradient | VRS range    |

|---|----------|--------------------------|--------------|

|   | ST7533   | -0.15%/°C                | -2.1V ±0.03V |

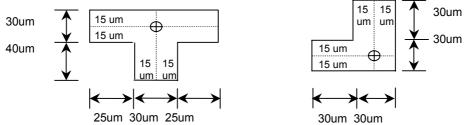

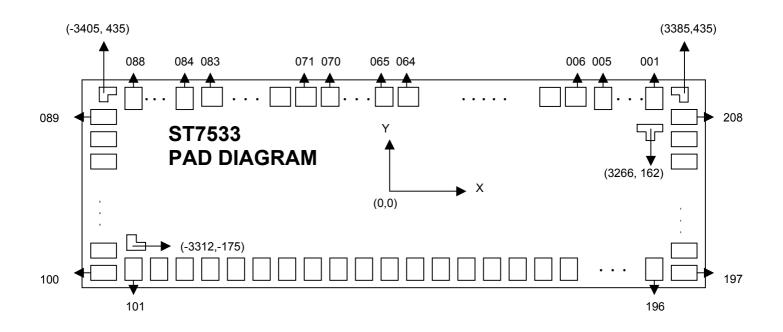

### ST7533 Pad Arrangement

| Chip Size:        | 7240 $\mu$ m x 1,000 $\mu$ m |                             |  |

|-------------------|------------------------------|-----------------------------|--|

| Origin: Chip Cent | ter                          |                             |  |

| Bump Pitch:       | 69.1 μ m(Min.)               |                             |  |

| Bump Size:        | PAD No. 001~005              | 49.1 $\mu$ m x 70.5 $\mu$ m |  |

|                   | PAD No. 006~064              | 56 $\mu$ m x 60 $\mu$ m     |  |

|                   | PAD No. 065~070              | 51 $\mu$ m x 60 $\mu$ m     |  |

|                   | PAD No. 071~083              | 56 $\mu$ m x 60 $\mu$ m     |  |

|                   | PAD No. 084~088              | 49.1 $\mu$ m x 70.5 $\mu$ m |  |

|                   | PAD No. 089~100              | 70.5 $\mu$ m x 49.1 $\mu$ m |  |

|                   | PAD No. 101~196              | 49.1 $\mu$ m x 70.5 $\mu$ m |  |

|                   | PAD No. 197~208              | 70.5 $\mu$ m x 49.1 $\mu$ m |  |

| Bump Height:      | 18 μ m(Typ)                  |                             |  |

| Chip Thickness:   | 660 μ m                      |                             |  |

| -                 |                              |                             |  |

|                   |                              |                             |  |

# ST7533 Pad Center Coordinates (1/33 Duty)

|                  | Center         | - |              | iales (1 |

|------------------|----------------|---|--------------|----------|

| PAD<br>No.       | PIN Name       |   | х            | Y        |

| 1                | COM[28]        |   | 3290         | 409      |

| 2                | COM[29]        |   | 3221         | 409      |

| 3                | COM[30]        |   | 3152         | 409      |

| 4                | COM[31]        |   | 3083         | 409      |

| 5                | COMS1          |   | 3014         | 409      |

| 6                | FRS            |   | 2919         | 414      |

| 7                | FR             |   | 2843         | 414      |

| 8                | CL             |   | 2767         | 414      |

| 9                | /DOF           |   | 2691         | 414      |

| 10               | VSS            |   | 2614         | 414      |

| 11               | /CS1           |   | 2538         | 414      |

| 12               | CS2            |   | 2462         | 414      |

| 13               | VDD            |   | 2386         | 414      |

| 14               | /RES           |   | 2310         | 414      |

| 15               | A0             |   | 2234         | 414      |

| 16               | VSS            |   | 2157         | 414      |

| 17               | /WR(R/W)       |   | 2081         | 414      |

| 18               | /RD(E)         |   | 2005         | 414      |

| 19               | VDD            |   | 1929         | 414      |

| 20               | D0             |   | 1853         | 414      |

| 20               | D1             |   | 1777         | 414      |

| 22               | D1<br>D2       |   | 1701         | 414      |

| 23               | D2             |   | 1624         | 414      |

| 23               | D3<br>D4       |   | 1548         | 414      |

| 24               | D4<br>D5       |   | 1472         | 414      |

| 25               | D5             |   | 1396         | 414      |

| 20               | D0             |   | 1390         | 414      |

| 28               | VDD            |   | 1244         | 414      |

| 20               | VDD            |   | 1244         | 414      |

| 30               | VDD            |   | 1091         | 414      |

| 30               | VDD            |   | 1091         | 414      |

| 32               | VSS            |   | 939          | 414      |

| 33               | VSS2           |   | 863          | 414      |

| 33               | VSS2           |   | 787          | 414      |

| 35               | VOUT           |   | 707          | 414      |

| 36               | VOUT           |   | 634          | 414      |

| 30               | CAP3-          |   | 558          | 414      |

| 38               | CAP3-          |   | 482          | 414      |

|                  | CAP3-          |   |              | 414      |

| 39<br>40         | CAP1+<br>CAP1+ |   | 406<br>330   | 414      |

| 40               | CAP1+<br>CAP1- |   | 254          | 414      |

|                  |                |   |              | 414      |

| 42               | CAP1-<br>CAP2- |   | 178          | 414      |

| 43<br>44         | CAP2-<br>CAP2- |   | 101<br>25    | 414      |

|                  | CAP2-<br>CAP2+ |   |              | 414      |

| 45<br>46         | CAP2+<br>CAP2+ |   | -51<br>-127  | 414      |

| 40               | VSS            |   | -127<br>-203 | 414      |

|                  |                |   |              | 414      |

| 48               | VSS            |   | -279         |          |

| 49               | VRS            |   | -355         | 414      |

| Da <b>50</b> 5he | et4U.VDD       |   | -432         | 414      |

| 51               | VDD            |   | -508         | 414      |

| 52               | V1             |   | -584         | 414      |

| PAD<br>No. | PIN Name | x     | Y    |

|------------|----------|-------|------|

| 53         | V1       | -660  | 414  |

| 54         | V2       | -736  | 414  |

| 55         | V2       | -812  | 414  |

| 56         | V3       | -889  | 414  |

| 57         | V3       | -965  | 414  |

| 58         | V4       | -1041 | 414  |

| 59         | V4       | -1117 | 414  |

| 60         | V5       | -1193 | 414  |

| 61         | V5       | -1269 | 414  |

| 62         | VR       | -1345 | 414  |

| 63         | VDD      | -1422 | 414  |

| 64         | VDD      | -1498 | 414  |

| 65         | TEST0    | -1571 | 414  |

| 66         | TEST1    | -1642 | 414  |

| 67         | TEST2    | -1713 | 414  |

| 68         | TEST3    | -1784 | 414  |

| 69         | TEST4    | -1855 | 414  |

| 70         | TEST5    | -1926 | 414  |

| 71         | VDD      | -2000 | 414  |

| 72         | M/S      | -2076 | 414  |

| 73         | CLS      | -2152 | 414  |

| 74         | VSS      | -2228 | 414  |

| 75         | C86      | -2305 | 414  |

| 76         | P/S      | -2381 | 414  |

| 77         | VDD      | -2457 | 414  |

| 78         | /HPM     | -2533 | 414  |

| 79         | VSS      | -2609 | 414  |

| 80         | IRS      | -2685 | 414  |

| 81         | VDD      | -2762 | 414  |

| 82         | SEL1     | -2838 | 414  |

| 83         | VSS      | -2914 | 414  |

| 84         | COM[15]  | -3011 | 409  |

| 85         | COM[14]  | -3080 | 409  |

| 86         | COM[13]  | -3150 | 409  |

| 87         | COM[12]  | -3219 | 409  |

| 88         | COM[11]  | -3288 | 409  |

| 89         | COM[10]  | -3529 | 351  |

| 90         | COM[9]   | -3529 | 282  |

| 91         | COM[8]   | -3529 | 213  |

| 92         | COM[7]   | -3529 | 144  |

| 93         | COM[6]   | -3529 | 75   |

| 94         | COM[5]   | -3529 | 6    |

| 95         | COM[4]   | -3529 | -64  |

| 96         | COM[3]   | -3529 | -133 |

| 97         | COM[2]   | -3529 | -202 |

| 98         | COM[1]   | -3529 | -271 |

| 99         | COM[0]   | -3529 | -340 |

| 100        | COMS2    | -3529 | -409 |

| 101        | SEG[0]   | -3280 | -409 |

| 102        | SEG[1]   | -3211 | -409 |

| 103        | SEG[2]   | -3142 | -409 |

| 104        | SEG[3]   | -3073 | -409 |

### **ST7533**

| PAD<br>No.  | PIN Name                 | x     | Y    |

|-------------|--------------------------|-------|------|

| 105         | SEG[4]                   | -3004 | -409 |

| 106         | SEG[5]                   | -2935 | -409 |

| 107         | SEG[6]                   | -2866 | -409 |

| 108         | SEG[7]                   | -2797 | -409 |

| 109         | SEG[8]                   | -2728 | -409 |

| 110         | SEG[9]                   | -2658 | -409 |

| 111         | SEG[10]                  | -2589 | -409 |

| 112         | SEG[11]                  | -2520 | -409 |

| 113         | SEG[12]                  | -2451 | -409 |

| 114         | SEG[13]                  | -2382 | -409 |

| 115         | SEG[14]                  | -2313 | -409 |

| 116         | SEG[15]                  | -2244 | -409 |

| 117         | SEG[16]                  | -2175 | -409 |

| 118         | SEG[17]                  | -2106 | -409 |

| 119         | SEG[18]                  | -2037 | -409 |

| 120         | SEG[19]                  | -1967 | -409 |

| 121         | SEG[20]                  | -1898 | -409 |

| 122         | SEG[21]                  | -1829 | -409 |

| 123         | SEG[22]                  | -1760 | -409 |

| 124         | SEG[23]                  | -1691 | -409 |

| 125         | SEG[24]                  | -1622 | -409 |

| 126         | SEG[25]                  | -1553 | -409 |

| 127         | SEG[26]                  | -1484 | -409 |

| 128         | SEG[27]                  | -1415 | -409 |

| 129         | SEG[28]                  | -1346 | -409 |

| 130         | SEG[29]                  | -1276 | -409 |

| 131         | SEG[30]                  | -1207 | -409 |

| 132         | SEG[31]                  | -1138 | -409 |

| 133         | SEG[32]                  | -1069 | -409 |

| 134         | SEG[33]                  | -1000 | -409 |

| 135         | SEG[34]                  | -931  | -409 |

| 136         | SEG[35]                  | -862  | -409 |

| 137         | SEG[36]                  | -793  | -409 |

| 138         | SEG[37]                  | -724  | -409 |

| 139         | SEG[38]                  | -655  | -409 |

| 140         | SEG[39]                  | -585  | -409 |

| 141         | SEG[40]                  | -516  | -409 |

| 142         | SEG[41]                  | -447  | -409 |

| 143         | SEG[42]                  | -378  | -409 |

| 144         | SEG[43]                  | -309  | -409 |

| 145         | SEG[44]                  | -240  | -409 |

| 146         | SEG[45]                  | -171  | -409 |

| 147         | SEG[46]                  | -102  | -409 |

| 148         | SEG[47]                  | -33   | -409 |

| 149         | SEG[48]                  | 36    | -409 |

| 150         | SEG[49]                  | 106   | -409 |

| 151         | SEG[50]                  | 175   | -409 |

| 152         | SEG[51]                  | 244   | -409 |

| 153         | SEG[52]                  | 313   | -409 |

| 154         | SEG[53]                  | 382   | -409 |

| - · · · · · | et4 <sup>1</sup> SEG[54] | 451   | -409 |

| 156         | SEG[55]                  | 520   | -409 |

| PAD | PIN Name           | x    | Y    |

|-----|--------------------|------|------|

| No. |                    |      |      |

| 157 | SEG[56]            | 589  | -409 |

| 158 | SEG[57]            | 658  | -409 |

| 159 | SEG[58]            | 727  | -409 |

| 160 | SEG[59]            | 797  | -409 |

| 161 | SEG[60]            | 866  | -409 |

| 162 | SEG[61]            | 935  | -409 |

| 163 | SEG[62]            | 1004 | -409 |

| 164 | SEG[63]            | 1073 | -409 |

| 165 | SEG[64]            | 1142 | -409 |

| 166 | SEG[65]            | 1211 | -409 |

| 167 | SEG[66]            | 1280 | -409 |

| 168 | SEG[67]            | 1349 | -409 |

| 169 | SEG[68]            | 1418 | -409 |

| 170 | SEG[69]            | 1488 | -409 |

| 171 | SEG[70]            | 1557 | -409 |

| 172 | SEG[71]            | 1626 | -409 |

| 173 | SEG[72]            | 1695 | -409 |

| 174 | SEG[73]            | 1764 | -409 |

| 175 | SEG[74]            | 1833 | -409 |

| 176 | SEG[75]            | 1902 | -409 |

| 177 | SEG[76]            | 1971 | -409 |

| 178 | SEG[77]            | 2040 | -409 |

| 179 | SEG[78]            | 2109 | -409 |

| 180 | SEG[79]            | 2179 | -409 |

| 181 | SEG[80]            | 2248 | -409 |

| 182 | SEG[81]            | 2317 | -409 |

| 183 | SEG[82]            | 2386 | -409 |

| 184 | SEG[83]            | 2455 | -409 |

| 185 | SEG[84]            | 2524 | -409 |

| 186 | SEG[85]            | 2593 | -409 |

| 187 | SEG[86]            | 2662 | -409 |

| 188 | SEG[87]            | 2731 | -409 |

| 189 | SEG[88]            | 2800 | -409 |

| 190 | SEG[89]            | 2870 | -409 |

| 191 | SEG[90]            | 2939 | -409 |

| 192 | SEG[91]            | 3008 | -409 |

| 193 | SEG[92]            | 3077 | -409 |

| 194 | SEG[93]            | 3146 | -409 |

| 195 | SEG[94]            | 3215 | -409 |

| 196 | SEG[95]            | 3284 | -409 |

| 197 | COM[16]            | 3529 | -409 |

| 198 | COM[17]            | 3529 | -340 |

| 199 | COM[17]            | 3529 | -271 |

| 200 | COM[19]            | 3529 | -202 |

| 200 | COM[20]            | 3529 | -133 |

| 201 | COM[21]            | 3529 | -64  |

| 202 | COM[22]            | 3529 | 6    |

| 200 | COM[23]            | 3529 | 75   |

| 204 | COM[23]            | 3529 | 144  |

| 205 | COM[24]            | 3529 | 213  |

| 200 | COM[25]            | 3529 | 213  |

| 207 | COM[20]<br>COM[27] | 3529 | 351  |

| 200 |                    | 5529 | 551  |

## ST7533 Pad Center Coordinates (1/17 Duty)

| <u>i uu</u>      | Center             | - |      |     |

|------------------|--------------------|---|------|-----|

| PAD<br>No.       | PIN Name           |   | х    | Y   |

| 1                | COM[12]            |   | 3290 | 409 |

| 2                | COM[13]            |   | 3221 | 409 |

| 3                | COM[14]            |   | 3152 | 409 |

| 4                | COM[15]            |   | 3083 | 409 |

| 5                | COMS1              |   | 3014 | 409 |

| 6                | FRS                |   | 2919 | 414 |

| 7                | FR                 |   | 2843 | 414 |

| 8                | CL                 |   | 2767 | 414 |

| 9                | /DOF               |   | 2691 | 414 |

| 10               | VSS                |   | 2614 | 414 |

| 11               | /CS1               |   | 2538 | 414 |

| 12               | CS2                |   | 2462 | 414 |

| 13               | VDD                |   | 2386 | 414 |

| 14               | /RES               |   | 2310 | 414 |

| 15               | A0                 |   | 2234 | 414 |

| 16               | VSS                |   | 2157 | 414 |

| 17               | /WR(R/W)           |   | 2081 | 414 |

| 18               | /WR(R/W)<br>/RD(E) |   | 2001 | 414 |

| 19               | VDD                |   | 1929 | 414 |

| 20               | D0                 |   | 1853 | 414 |

| 20               | D0                 |   | 1777 | 414 |

|                  | D1<br>D2           |   | 1701 | 414 |

| 22               | D2<br>D3           |   | 1624 | 414 |

| 23               |                    |   |      | 414 |

| 24               | D4                 |   | 1548 |     |

| 25               | D5                 |   | 1472 | 414 |

| 26               | D6                 |   | 1396 | 414 |

| 27               | D7                 |   | 1320 | 414 |

| 28               | VDD                |   | 1244 | 414 |

| 29               | VDD                |   | 1168 | 414 |

| 30               | VDD                |   | 1091 | 414 |

| 31               | VSS                |   | 1015 | 414 |

| 32               | VSS                |   | 939  | 414 |

| 33               | VSS2               |   | 863  | 414 |

| 34               | VSS2               |   | 787  | 414 |

| 35               | VOUT               |   | 711  | 414 |

| 36               | VOUT               |   | 634  | 414 |

| 37               | CAP3-              |   | 558  | 414 |

| 38               | CAP3-              |   | 482  | 414 |

| 39               | CAP1+              |   | 406  | 414 |

| 40               | CAP1+              |   | 330  | 414 |

| 41               | CAP1-              |   | 254  | 414 |

| 42               | CAP1-              |   | 178  | 414 |

| 43               | CAP2-              |   | 101  | 414 |

| 44               | CAP2-              |   | 25   | 414 |

| 45               | CAP2+              |   | -51  | 414 |

| 46               | CAP2+              |   | -127 | 414 |

| 47               | VSS                |   | -203 | 414 |

| 48               | VSS                |   | -279 | 414 |

| 49               | VRS                |   | -355 | 414 |

| Da <b>50</b> 5he | et4U.VDD           |   | -432 | 414 |

| 51               | VDD                |   | -508 | 414 |

| 52               | V1                 |   | -584 | 414 |

| PAD<br>No. | PIN Name | x     | Y    |

|------------|----------|-------|------|

| 53         | V1       | -660  | 414  |

| 54         | V2       | -736  | 414  |

| 55         | V2       | -812  | 414  |

| 56         | V3       | -889  | 414  |

| 57         | V3       | -965  | 414  |

| 58         | V4       | -1041 | 414  |

| 59         | V4       | -1117 | 414  |

| 60         | V5       | -1193 | 414  |

| 61         | V5       | -1269 | 414  |

| 62         | VR       | -1345 | 414  |

| 63         | VDD      | -1422 | 414  |

| 64         | VDD      | -1498 | 414  |

| 65         | TEST0    | -1571 | 414  |

| 66         | TEST1    | -1642 | 414  |

| 67         | TEST2    | -1713 | 414  |

| 68         | TEST3    | -1784 | 414  |

| 69         | TEST4    | -1855 | 414  |

| 70         | TEST5    | -1926 | 414  |

| 71         | VDD      | -2000 | 414  |

| 72         | M/S      | -2076 | 414  |

| 73         | CLS      | -2152 | 414  |

| 74         | VSS      | -2228 | 414  |

| 75         | C86      | -2305 | 414  |

| 76         | P/S      | -2381 | 414  |

| 77         | VDD      | -2457 | 414  |

| 78         | /HPM     | -2533 | 414  |

| 79         | VSS      | -2609 | 414  |

| 80         | IRS      | -2685 | 414  |

| 81         | VDD      | -2762 | 414  |

| 82         | SEL1     | -2838 | 414  |

| 83         | VSS      | -2914 | 414  |

| 84         | Reserve  | -3011 | 409  |

| 85         | Reserve  | -3080 | 409  |

| 86         | Reserve  | -3150 | 409  |

| 87         | Reserve  | -3219 | 409  |

| 88         | Reserve  | -3288 | 409  |

| 89         | Reserve  | -3529 | 351  |

| 90         | Reserve  | -3529 | 282  |

| 91         | Reserve  | -3529 | 213  |

| 92         | COM[7]   | -3529 | 144  |

| 93         | COM[6]   | -3529 | 75   |

| 94         | COM[5]   | -3529 | 6    |

| 95         | COM[4]   | -3529 | -64  |

| 96         | COM[3]   | -3529 | -133 |

| 97         | COM[2]   | -3529 | -202 |

| 98         | COM[1]   | -3529 | -271 |

| 99         | COM[0]   | -3529 | -340 |

| 100        | COMS2    | -3529 | -409 |

| 101        | SEG[0]   | -3280 | -409 |

| 102        | SEG[1]   | -3211 | -409 |

| 103        | SEG[2]   | -3142 | -409 |

| 104        | SEG[3]   | -3073 | -409 |

### **ST7533**

| PAD<br>No. | PIN Name    | x     | Y    |

|------------|-------------|-------|------|

| 105        | SEG[4]      | -3004 | -409 |

| 106        | SEG[5]      | -2935 | -409 |

| 107        | SEG[6]      | -2866 | -409 |

| 108        | SEG[7]      | -2797 | -409 |

| 109        | SEG[8]      | -2728 | -409 |

| 110        | SEG[9]      | -2658 | -409 |

| 111        | SEG[10]     | -2589 | -409 |

| 112        | SEG[11]     | -2520 | -409 |

| 113        | SEG[12]     | -2451 | -409 |

| 114        | SEG[13]     | -2382 | -409 |

| 115        | SEG[14]     | -2313 | -409 |

| 116        | SEG[15]     | -2244 | -409 |

| 117        | SEG[16]     | -2175 | -409 |

| 118        | SEG[17]     | -2106 | -409 |

| 119        | SEG[18]     | -2037 | -409 |

| 120        | SEG[19]     | -1967 | -409 |

| 121        | SEG[20]     | -1898 | -409 |

| 122        | SEG[21]     | -1829 | -409 |

| 123        | SEG[22]     | -1760 | -409 |

| 124        | SEG[23]     | -1691 | -409 |

| 125        | SEG[24]     | -1622 | -409 |

| 126        | SEG[25]     | -1553 | -409 |

| 127        | SEG[26]     | -1484 | -409 |

| 128        | SEG[27]     | -1415 | -409 |

| 129        | SEG[28]     | -1346 | -409 |

| 130        | SEG[29]     | -1276 | -409 |

| 131        | SEG[30]     | -1207 | -409 |

| 132        | SEG[31]     | -1138 | -409 |

| 133        | SEG[32]     | -1069 | -409 |

| 134        | SEG[33]     | -1000 | -409 |

| 135        | SEG[34]     | -931  | -409 |

| 136        | SEG[35]     | -862  | -409 |

| 137        | SEG[36]     | -793  | -409 |

| 138        | SEG[37]     | -724  | -409 |

| 139        | SEG[38]     | -655  | -409 |

| 140        | SEG[39]     | -585  | -409 |

| 141        | SEG[40]     | -516  | -409 |

| 142        | SEG[41]     | -447  | -409 |

| 143        | SEG[42]     | -378  | -409 |

| 144        | SEG[43]     | -309  | -409 |

| 145        | SEG[44]     | -240  | -409 |

| 146        | SEG[45]     | -171  | -409 |

| 147        | SEG[46]     | -102  | -409 |

| 148        | SEG[47]     | -33   | -409 |

| 149        | SEG[48]     | 36    | -409 |

| 150        | SEG[49]     | 106   | -409 |

| 151        | SEG[50]     | 175   | -409 |

| 152        | SEG[51]     | 244   | -409 |

| 152        | SEG[52]     | 313   | -409 |

| 155        | SEG[53]     | 382   | -409 |

| Dat55he    | et4 SEG[54] | 451   | -409 |

|            | 0=0[0:]     | 520   |      |

| 156        | SEG[55]     | 520   | -409 |

| PAD | PIN Name | x            | Y            |

|-----|----------|--------------|--------------|

| No. |          | 500          | 400          |

| 157 | SEG[56]  | 589<br>658   | -409<br>-409 |

| 158 | SEG[57]  | 727          | -409         |

| 159 | SEG[58]  | 727          | -409         |

| 160 | SEG[59]  |              |              |

| 161 | SEG[60]  | 866          | -409         |

| 162 | SEG[61]  | 935          | -409         |

| 163 | SEG[62]  | 1004         | -409         |

| 164 | SEG[63]  | 1073         | -409         |

| 165 | SEG[64]  | 1142<br>1211 | -409         |

| 166 | SEG[65]  |              | -409         |

| 167 | SEG[66]  | 1280         | -409         |

| 168 | SEG[67]  | 1349         | -409         |

| 169 | SEG[68]  | 1418         | -409         |

| 170 | SEG[69]  | 1488         | -409         |

| 171 | SEG[70]  | 1557         | -409         |

| 172 | SEG[71]  | 1626         | -409         |

| 173 | SEG[72]  | 1695         | -409         |

| 174 | SEG[73]  | 1764         | -409         |

| 175 | SEG[74]  | 1833         | -409         |

| 176 | SEG[75]  | 1902         | -409         |

| 177 | SEG[76]  | 1971         | -409         |

| 178 | SEG[77]  | 2040         | -409         |

| 179 | SEG[78]  | 2109         | -409         |

| 180 | SEG[79]  | 2179         | -409         |

| 181 | SEG[80]  | 2248         | -409         |

| 182 | SEG[81]  | 2317         | -409         |

| 183 | SEG[82]  | 2386         | -409         |

| 184 | SEG[83]  | 2455         | -409         |

| 185 | SEG[84]  | 2524         | -409         |

| 186 | SEG[85]  | 2593         | -409         |

| 187 | SEG[86]  | 2662         | -409         |

| 188 | SEG[87]  | 2731         | -409         |

| 189 | SEG[88]  | 2800         | -409         |

| 190 | SEG[89]  | 2870         | -409         |

| 191 | SEG[90]  | 2939         | -409         |

| 192 | SEG[91]  | 3008         | -409         |

| 193 | SEG[92]  | 3077         | -409         |

| 194 | SEG[93]  | 3146         | -409         |

| 195 | SEG[94]  | 3215         | -409         |

| 196 | SEG[95]  | 3284         | -409         |

| 197 | Reserve  | 3529         | -409         |

| 198 | Reserve  | 3529         | -340         |

| 199 | Reserve  | 3529         | -271         |

| 200 | Reserve  | 3529         | -202         |

| 201 | Reserve  | 3529         | -133         |

| 202 | Reserve  | 3529         | -64          |

| 203 | Reserve  | 3529         | 6            |

| 204 | Reserve  | 3529         | 75           |

| 205 | COM[8]   | 3529         | 144          |

| 206 | COM[9]   | 3529         | 213          |

| 207 | COM[10]  | 3529         | 282          |

| 208 | COM[11]  | 3529         | 351          |

Ver 1.0

6/60

### **BLOCK DIAGRAM**

### ST7533 PIN DESCRIPTIONS

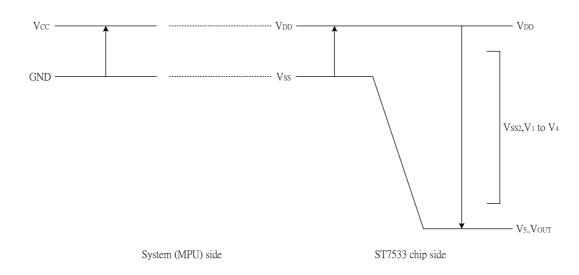

### **Power Supply Pins**

| Pin Name                 | I/O             | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | No. of Pins |

|--------------------------|-----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| VDD                      | Power<br>Supply | Shared with the MPU power supply terminal Vcc.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 12          |

| VSS                      | Power<br>Supply | This is a 0V terminal connected to the system GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 9           |

| VSS2                     | Power<br>Supply | This is the reference power supply for the step-up voltage circuit for the liquid crystal drive.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            | 2           |

| VRS                      | Power<br>Supply | This is the internal-output VREG power supply for the LCD power supply voltage regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 1           |

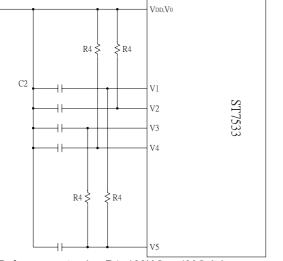

| V1, V2,<br>V3, V4,<br>V5 | Power<br>Supply | This is a multi-level power supply for the liquid crystal drive. The voltage Supply applied is determined by the liquid crystal cell, and is changed through the use of a resistive voltage divided or through changing the impedance using an op. amp. Voltage levels are determined based on VDD, and must maintain the relative magnitudes shown below.<br>VDD (= V0) $\geq$ V1 $\geq$ V2 $\geq$ V3 $\geq$ V4 $\geq$ V5<br>When the power supply turns ON, the internal power supply circuits produce the V1 to V4 voltages shown below. The voltage settings are selected using the LCD bias set command.<br>$\frac{1/33 \text{ DUTY}}{\text{V1 1/6*V5,1/5*V5}} \frac{1/17 \text{ DUTY}}{1/17 \text{ DUTY}}$ $\frac{1/34 \text{ CUY}}{1/16 \text{ CV},2/5 \text{ CV}} \frac{1}{1/6 \text{ CV},2/5 \text{ CV}} \frac{1}{1/6 \text{ CV},2/5 \text{ CV}}}{1/6 \text{ CV},2/5 \text{ CV}} \frac{1}{1/6 \text{ CV},2/5 \text{ CV}}}{1/6 \text{ CV},2/5 \text{ CV}} \frac{1}{1/6 \text{ CV},2/5 \text{ CV}}}{1/6 \text{ CV},2/5 \text{ CV}}}$ | 10          |

### LCD Power Supply Pins

| Pin Name | I/O | Function                                                                                                                                                                                                                                                        | No. of Pins |

|----------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|

| CAP1+    | 0   | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1- terminal.                                                                                                                                                                      | 2           |

| CAP1-    | 0   | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.                                                                                                                                                                      | 2           |

| CAP2+    | 0   | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2- terminal.                                                                                                                                                                      | 2           |

| CAP2-    | 0   | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP2+ terminal.                                                                                                                                                                      | 2           |

| CAP3–    | 0   | DC/DC voltage converter. Connect a capacitor between this terminal and the CAP1+ terminal.                                                                                                                                                                      | 2           |

| VOUT     | 0   | DC/DC voltage converter. Connect a capacitor between this terminal and VSS.                                                                                                                                                                                     | 2           |

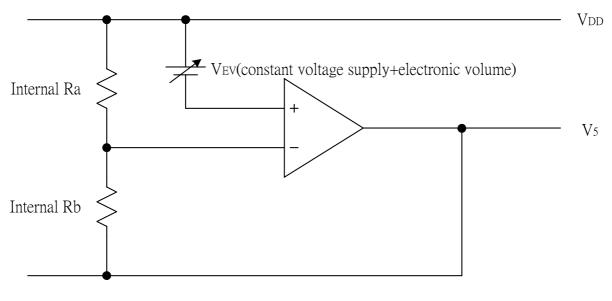

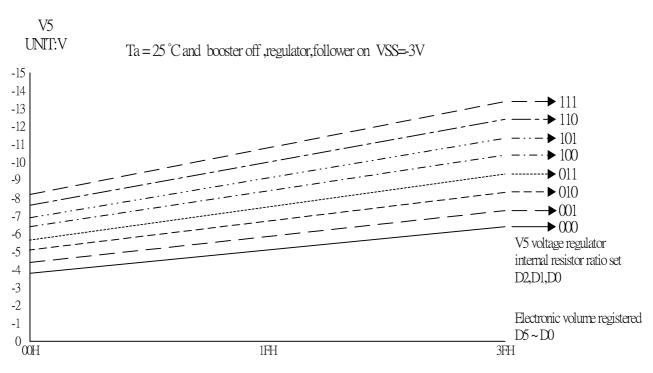

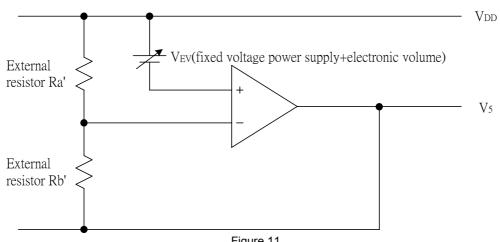

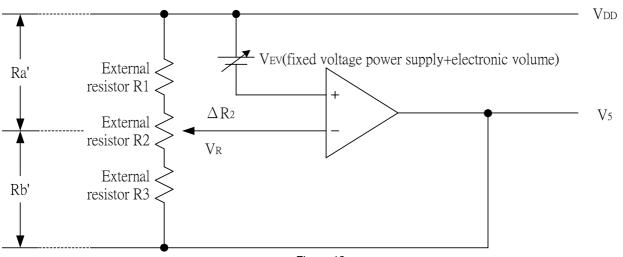

| VR       | I   | Output voltage regulator terminal. Provides the voltage between VDD and V5 through a resistive voltage divider.<br>IRS = "L" : the V5 voltage regulator internal resistors are not used .<br>IRS = "H" : the V5 voltage regulator internal resistors are used . | 2           |

#### System Bus Connection Pins

| Pin Name                        | I/O |                                   |                                                                                                                                                                                                                                                                                                                                                                                              |                                                                    | Function       |            |              | No. of Pins |  |  |

|---------------------------------|-----|-----------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------|----------------|------------|--------------|-------------|--|--|

| D5 to D0<br>D6 (SCL)<br>D7 (SI) | I/O | star<br>Whe<br>D7<br>D0<br>Whe    | ndard MP<br>en the se<br>: serial da<br>to D5 are<br>en the ch                                                                                                                                                                                                                                                                                                                               | n impedance.                                                       | 8              |            |              |             |  |  |

| A0                              | I   | and<br>A0 :                       | s is conne<br>it determ<br>= "H": Ind<br>= "L": Indi                                                                                                                                                                                                                                                                                                                                         | 1                                                                  |                |            |              |             |  |  |

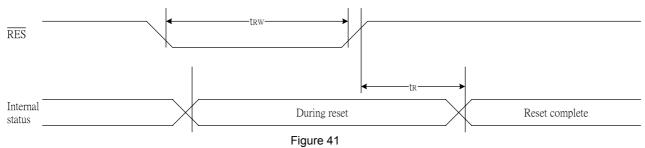

| /RES                            | Ι   |                                   | en /RES i<br>reset op                                                                                                                                                                                                                                                                                                                                                                        | 1                                                                  |                |            |              |             |  |  |

| /CS1<br>CS2                     | I   |                                   |                                                                                                                                                                                                                                                                                                                                                                                              | nip select signal. W<br>ecomes active, and                         |                |            |              | 2           |  |  |

| /RD<br>(E)                      | I   | (E)<br>ST7<br>• W                 | hen conn<br>This pin i<br>7533 serie<br>hen conn<br>s is the 68                                                                                                                                                                                                                                                                                                                              | 1                                                                  |                |            |              |             |  |  |

| /WR<br>(R/W)                    | I   | (R/V<br>the<br>• W<br>This<br>Whe | <ul> <li>When connected to an 8080 MPU, this is active LOW.</li> <li>(R/W) This terminal connects to the 8080 MPU/WR signal. The signals on the data bus are latched at the rising edge of the /WR signal.</li> <li>When connected to a 6800 Series MPU:<br/>This is the read/write control signal input terminal.</li> <li>When R/W = "H": Read.</li> <li>When R/W = "L": Write.</li> </ul> |                                                                    |                |            |              |             |  |  |

| C86                             | I   | C86                               | 6 = "H": 68                                                                                                                                                                                                                                                                                                                                                                                  | PU interface switch<br>800 Series MPU in<br>980 MPU interface.     | terface.       |            |              | 1           |  |  |

|                                 |     | P/S<br>P/S                        | This is the parallel data input/serial data input switch terminal.<br>P/S = "H": Parallel data input.<br>P/S = "L": Serial data input.<br>The following applies depending on the P/S status:                                                                                                                                                                                                 |                                                                    |                |            |              |             |  |  |

|                                 |     |                                   | P/S                                                                                                                                                                                                                                                                                                                                                                                          | Data/Command                                                       | Data           | Read/Write | Serial Clock |             |  |  |

| P/S                             | Ι   |                                   | "H"                                                                                                                                                                                                                                                                                                                                                                                          | 1                                                                  |                |            |              |             |  |  |

|                                 |     |                                   | "L"                                                                                                                                                                                                                                                                                                                                                                                          |                                                                    |                |            |              |             |  |  |

|                                 |     | /RD                               | (E) and                                                                                                                                                                                                                                                                                                                                                                                      | "L", D0 to D5 fixed<br>/WR (R/W) are fixe<br>ata input, It_is impo | d to either "⊦ | l" or "L". | 1.           |             |  |  |

| Pin Name    | I/O |                                                          | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                  |                              |                  |                            |                  |         |

|-------------|-----|----------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|------------------------------|------------------|----------------------------|------------------|---------|

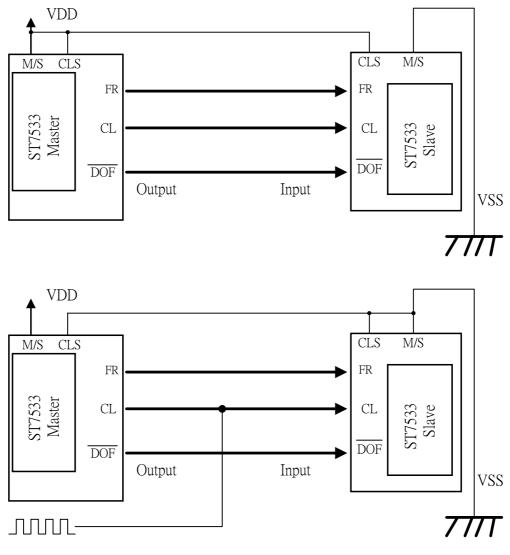

| CLS         | I   | oscillator c<br>CLS = "H"<br>CLS = "L"<br>When CLS       | Terminal to select whether or enable or disable the display clock internal<br>oscillator circuit.<br>CLS = "H" : used Internal oscillator circuit .<br>CLS = "L" : used external clock input .(internal oscillator is disable)<br>When CLS = "L", input the display clock through the CL terminal.<br>This terminal selects the master/slave operation for the ST7533 Series chips.<br>Master operation outputs the timing signals that are required for the LCD display, while |                                                  |                              |                  |                            |                  |         |

|             |     | Master oper<br>slave operat<br>Synchroniz<br>M/S = "H" M |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | ne timing sigr<br>ming signals<br>crystal displa | nals that are<br>required fo | e required f     | or the LCD                 | display, whi     | le      |

| M/S         | I   | M/S C                                                    | LS Oscillator<br>Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                        | Power<br>Supply<br>Circuit                       | CL                           | FR               | FRS                        | DOF              | 1       |

|             |     |                                                          | H" Enabled<br>L" Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                  | Output<br>Input              | Output<br>Output | Output<br>Output           | Output<br>Output |         |

|             |     | """                                                      | H" Disabled                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Disabled                                         | Input<br>Input               | Input<br>Input   | Output<br>Output<br>Output | Input<br>Input   |         |

|             |     |                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Disableu                                         | mput                         | input            | Output                     | input            |         |

|             |     | The followi                                              | display clock<br>ng is true dep                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                  |                              | ind CLS s        | tatus.                     |                  |         |

|             | 1/0 |                                                          | CLS CL                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | .+                                               |                              |                  |                            |                  | 1       |

| CL          | I/O |                                                          | "H" Outpu<br>"L" Input                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                  |                              |                  |                            |                  | 1       |

|             |     |                                                          | "H" Input<br>"L" Input                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                  |                              |                  |                            |                  |         |

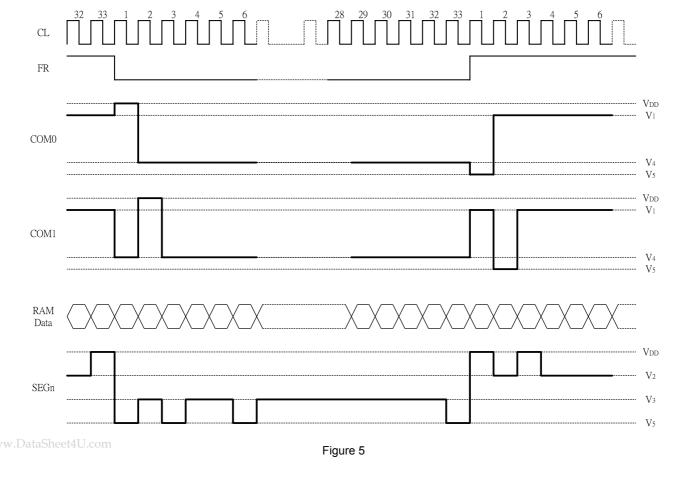

| FR          | 0   | This is the                                              | This is the liquid crystal alternating current signal terminal.                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                  |                              |                  |                            |                  | 1       |

| /DOF        | 0   | This is the                                              | LCD blanking                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | g control ter                                    | minal.                       |                  |                            |                  | 1       |

| FRS         | 0   | This termin                                              | output termin<br>nal is only ena<br>d in conjunctio                                                                                                                                                                                                                                                                                                                                                                                                                             | abled when                                       | the static                   | indicator        | display is                 | ON               | 1       |

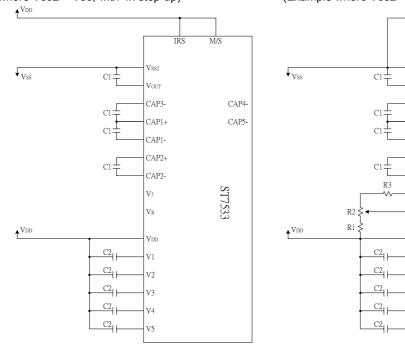

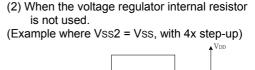

| IRS         | I   | IRS = "H":<br>IRS = "L":                                 | nal selects the<br>Use the inter<br>Do not use th<br>by an external                                                                                                                                                                                                                                                                                                                                                                                                             | nal resistor:<br>e internal re                   | s<br>esistors. 1             | The V5 vo        | tage level                 | lis              | 1<br>al |

| /HPM        | I   | This is the<br>drive.<br>/HPM = "H<br>/HPM = "L'         | regulated by an external resistive voltage divider attached to the VR terminal<br>This is the power control terminal for the power supply circuit for liquid crystal<br>drive.<br>/HPM = "H": Normal mode<br>/HPM = "L": High power mode                                                                                                                                                                                                                                        |                                                  |                              |                  |                            |                  |         |

|             |     |                                                          | are DUTY s                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                                                  |                              |                  |                            |                  |         |

|             |     |                                                          | T                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                                                  | 1                            |                  |                            |                  |         |

| SEL1        | I   | SE                                                       |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | DUTY                                             |                              | AS               |                            |                  | 1       |

|             | ·   |                                                          | 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1/33                                             |                              | or 1/6           |                            |                  |         |

|             |     |                                                          | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 1/17                                             | 1/5 0                        | or 1/6           |                            |                  |         |

| DataSheet4U | com | These are                                                | torminals for                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | IC testing                                       |                              |                  |                            |                  |         |

| TEST0 ~ 5   | I   | TEST0 (PA                                                | terminals for<br>AD No.65) mu<br>must floating                                                                                                                                                                                                                                                                                                                                                                                                                                  | ist connect                                      | to VDD                       |                  |                            |                  | 6       |

#### LCD Driver Pins

| Pin Name   | I/O |                                                                                                                                     | Function                                                                                                                                                                       |                  |            |       |  |    |  |  |  |

|------------|-----|-------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|------------|-------|--|----|--|--|--|

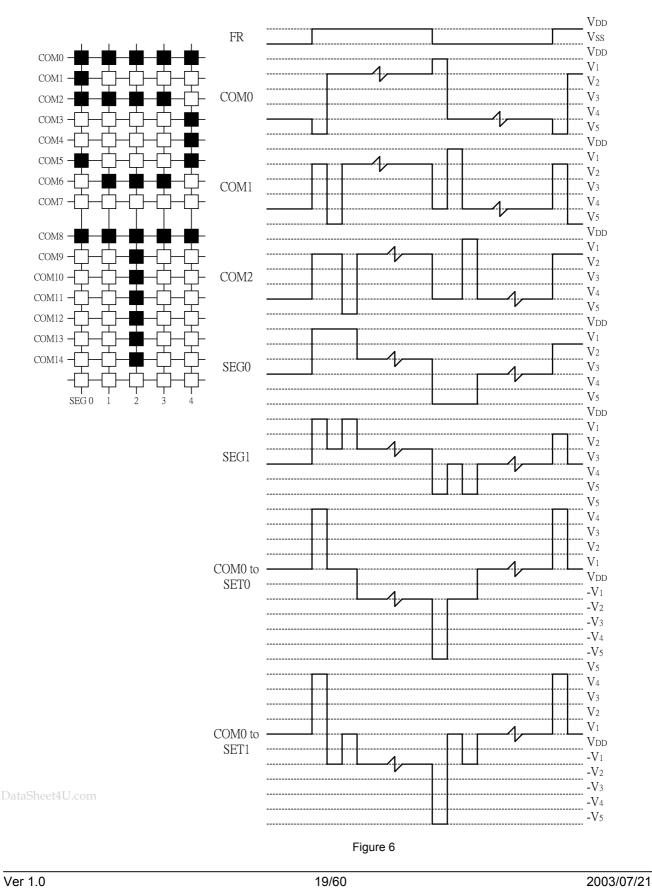

|            |     | contents of the o                                                                                                                   | These are the LCD segment drive outputs. Through a combination of the contents of the display RAM and with the FR signal, a single level is selected from VDD, V2, V3, and V5. |                  |            |       |  |    |  |  |  |

|            |     |                                                                                                                                     | Output Voltage                                                                                                                                                                 |                  |            |       |  |    |  |  |  |

| SEG0<br>to |     | RAM DATA                                                                                                                            | FR                                                                                                                                                                             | Normal Displ     |            |       |  |    |  |  |  |

|            | 0   | Н                                                                                                                                   | Н                                                                                                                                                                              | VDD              |            | V2    |  | 96 |  |  |  |

| SEG95      |     | Н                                                                                                                                   | L                                                                                                                                                                              | V5               |            | V3    |  |    |  |  |  |

|            |     | L                                                                                                                                   | Н                                                                                                                                                                              | V2               |            | Vdd   |  |    |  |  |  |

|            |     | L                                                                                                                                   | L                                                                                                                                                                              | V3               |            | V5    |  |    |  |  |  |

|            |     | Power save                                                                                                                          |                                                                                                                                                                                |                  | Vdd        | Vdd   |  |    |  |  |  |

|            |     | These are the L                                                                                                                     | CD con                                                                                                                                                                         | nmon drive outpu | ts.        |       |  |    |  |  |  |

|            |     |                                                                                                                                     | Part No.                                                                                                                                                                       |                  | СОМ        | TOTAL |  |    |  |  |  |

|            |     |                                                                                                                                     | 33 DUTY                                                                                                                                                                        | CO               | M0 ~ COM31 | 32    |  |    |  |  |  |

|            |     | 17 DUTY                                                                                                                             | CO                                                                                                                                                                             | M0 ~ COM15       | 16         |       |  |    |  |  |  |

| СОМО       |     | Through a combination of the contents of the scan data and with the FR signal, a single level is selected from VDD, V1, V4, and V5. |                                                                                                                                                                                |                  |            |       |  |    |  |  |  |

| to<br>COMn | 0   | Scan Data                                                                                                                           | FR                                                                                                                                                                             | Output Voltage   | e          |       |  |    |  |  |  |

|            |     | Н                                                                                                                                   | Н                                                                                                                                                                              | V5               |            |       |  |    |  |  |  |

|            |     | Н                                                                                                                                   | L                                                                                                                                                                              | Vdd              |            |       |  |    |  |  |  |

|            |     | L                                                                                                                                   | Н                                                                                                                                                                              | V1               |            |       |  |    |  |  |  |

|            |     | L                                                                                                                                   | L                                                                                                                                                                              | V4               |            |       |  |    |  |  |  |

|            |     | Power save                                                                                                                          |                                                                                                                                                                                | VDD              |            |       |  |    |  |  |  |

| COMS       | 0   | the same signal                                                                                                                     | These are the COM output terminals for the indicator. Both terminals output the same signal.<br>Leave these open if they are not used.                                         |                  |            |       |  |    |  |  |  |

### **DESCRIPTION OF FUNCTIONS**

#### The MPU Interface

#### Selecting the Interface Type

With the ST7533 chips, data transfers are done through an 8-bit parallel data bus (D7 to D0) or through a serial data input (SI). Through selecting the P/S terminal polarity to the

"H" or "L" it is possible to select either parallel data input or serial data input as shown in Table 1.

|                   |                 |              |         | Table 1 |     |     |    |     | <u> </u> |

|-------------------|-----------------|--------------|---------|---------|-----|-----|----|-----|----------|

| P/S               | /CS1            | CS2          | A0      | /RD     | /WR | C86 | D7 | D6  | D5~D0    |

| H: Parallel Input | /CS1            | CS2          | A0      | /RD     | /WR | C86 | D7 | D6  | D5~D0    |

| L: Serial Input   | /CS1            | CS2          | A0      |         | —   | —   | SI | SCL | (HZ)     |

| " "indianta       | - five of to al | thar "II" or | La #1 " |         |     |     |    |     |          |

—" indicates fixed to either "H" or to "L"

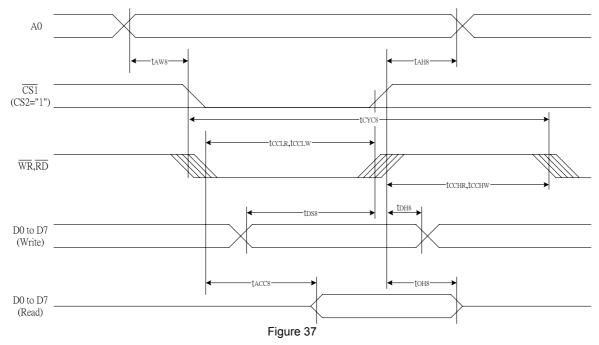

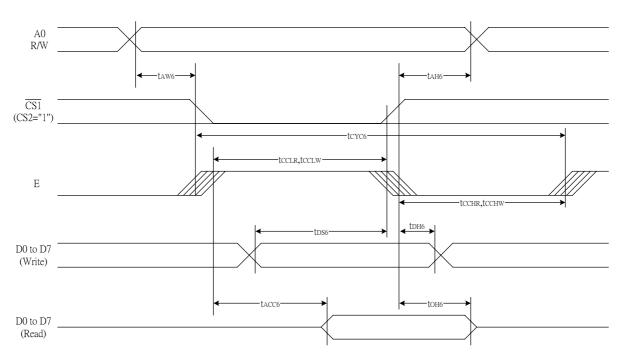

#### The Parallel Interface

When the parallel interface has been selected (P/S ="H"), then it is possible to connect directly to either an

8080-system MPU or a 6800 Series MPU (shown in Table 2) by selecting the C86 terminal to either "H" or to "L".

Table 2

| C86 (P/S=H)    | /CS1 | CS2 | A0 | /RD | /WR | D7~D0 |

|----------------|------|-----|----|-----|-----|-------|

| H: 6800 Series | /CS1 | CS2 | A0 | Е   | R/W | D7~D0 |

| L: 8080 Series | /CS1 | CS2 | A0 | /RD | /WR | D7~D0 |

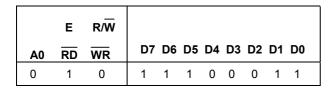

Moreover, data bus signals are recognized by a combination of A0, /RD (E), /WR (R/W) signals, as shown in Table 3.

|        |             | Та   | ble 3  |                              |  |

|--------|-------------|------|--------|------------------------------|--|

| Shared | 6800 Series | 8080 | Series | Function                     |  |

| A0     | R/W         | /RD  | /WR    | - Function                   |  |

| 1      | 1           | 0    | 1      | Reads the display data       |  |

| 1      | 0           | 1    | 0      | Writes the display data      |  |

| 0      | 1           | 0    | 1      | Status read                  |  |

| 0      | 0           | 1    | 0      | Write control data (command) |  |

### ST7533

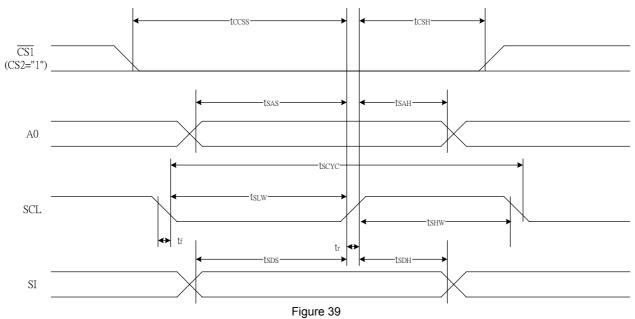

#### The Serial Interface

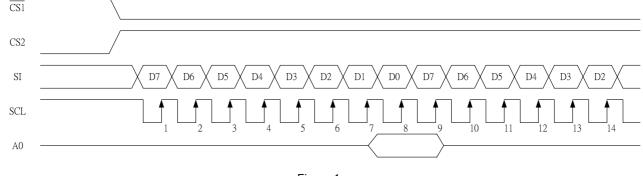

When the serial interface has been selected (P/S = "L") then when the chip is in active state (/CS1 = "L" and CS2 = "H") the serial data input (SI) and the serial clock input (SCL) can be received. The serial data is read from the serial data input pin in the rising edge of the serial clocks D7, D6 through D0, in this order. This data is converted to 8 bits parallel data in the rising edge of the eighth serial clock for the processing. The A0 input is used to determine whether or the serial data input is display data or command data; when A0 = "H", the data is display data, and when A0 = "L" then the data is command data. The A0 input is read and used for detection every 8th rising edge of the serial clock after the chip becomes active. Figure 1 is a serial interface signal chart.

#### Figure 1

\* When the chip is not active, the shift registers and the counter are reset to their initial states.

\* Reading is not possible while in serial interface mode.

\* Caution is required on the SCL signal when it comes to line-end reflections and external noise. We recommend that operation be rechecked on the actual equipment.

#### **The Chip Select**

The ST7533 have two chip select terminals: /CS1 and CS2. The MPU interface or the serial interface is enabled only when /CS1 = "L" and CS2 = "H".

When the chip select is inactive, D0 to D7 enter a high impedance state, and the A0, /RD, and /WR inputs are inactive. When the serial interface is selected, the shift register and the counter are reset.

#### The Accessing the Display Data RAM and the Internal Registers

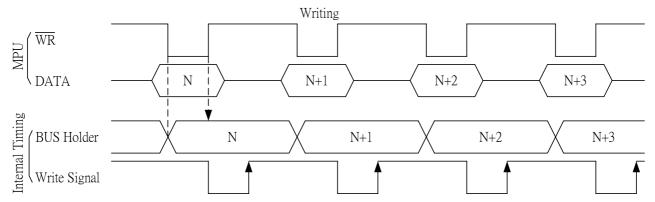

Data transfer at a higher speed is ensured since the MPU is required to satisfy the cycle time (tcYc) requirement alone in accessing the ST7533. Wait time may not be considered. And, in the ST7533, each time data is sent from the MPU, a type of pipeline process between LSIs is performed through the bus holder attached to the internal data bus. Internal data bus.

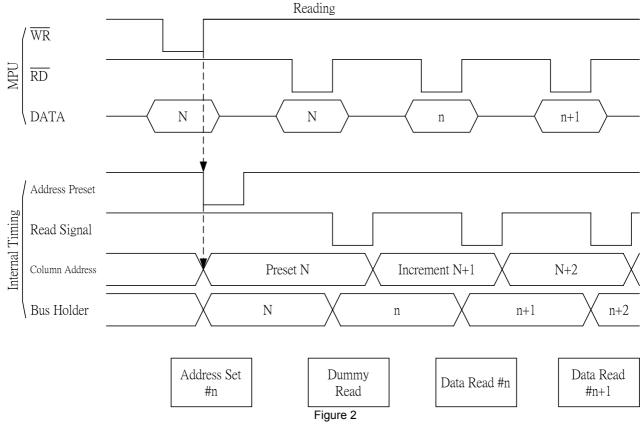

For example, when the MPU writes data to the display data RAM, once the data is stored in the bus holder, then it is written to the display data RAM before the next data write cycle. Moreover, when the MPU reads the display data RAM,

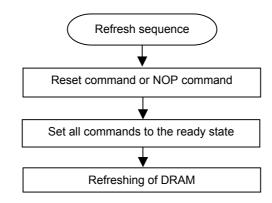

the first data read cycle (dummy) stores the read data in the bus holder, and then the data is read from the bus holder to the system bus at the next data read cycle.