# MOS INTEGRATED CIRCUIT $\mu$ PD6124A, 6600A

# 4-BIT SINGLE-CHIP MICROCONTROLLER FOR REMOTE CONTROL TRANSMISSION

#### **DESCRIPTION**

★ The  $\mu$ PD6124A and 6600A are 4-bit single-chip microcontrollers for infrared remote controllers for TVs, VCRs, stereos, cassette decks, air conditions, etc.

www.DataSheet4U.conThese microcontrollers consist of ROM, RAM, a 4-bit parallel-processing ALU, a programmable timer, key input/output ports, and transmit output ports. Functioning is controlled by a program.

A one-time PROM, model  $\mu$ PD61P24, to which a program can be written only once is also available. This one-time PROM is ideal for evaluation of programs running in a  $\mu$ PD6124A or 6600A, and for small-scale production of such systems.

#### **FEATURES**

- Transmitter for programmable infrared remote controller

- 19 types of instructions

- Instruction execution time: 17.6 μs (with 455-kHz ceramic resonator)

- Program memory (ROM) capacity

- $\mu$ PD6124A: 1002 × 10 bits

- $\mu$ PD6600A: 512 × 10 bits

- Data memory (RAM) capacity: 32 × 5 bits

- 9-bit programmable timer: 1 channel

- I/O pins (K<sub>I</sub>/o): 8 pinsInput pins (K<sub>I</sub>): 4 pins

- Serial input pins (S-IN): 1 pin

- Transmission-in-progress indication pin (S-OUT): 1 pin

- Transmit carrier frequency (REM) fosc/12, fosc/8

- Standby operation (HALT/STOP mode)

- Low power consumption

- Current consumption in STOP mode (T<sub>A</sub> = 25°C)

- Low-voltage operation

$\mu$ PD6124A: V<sub>DD</sub> = 2.2 to 5.5 V  $\mu$ PD6600A: V<sub>DD</sub> = 2.2 to 3.6 V

Caution To use the NEC transmission format, ask NEC to supply the custom code.

b Do not use R₀ when using a register as an operand of the branch instruction.

#### ORDERING INFORMATION

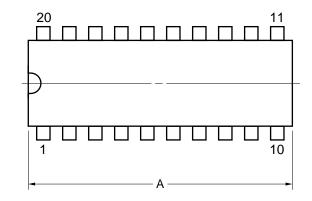

| Part Number         | Package                             |

|---------------------|-------------------------------------|

| $\mu$ PD6124ACS-XXX | 20-pin plastic shrink DIP (300 mil) |

| $\mu$ PD6124AGS-XXX | 20-pin plastic SOP (300 mil)        |

|                     |                                     |

| $\mu$ PD6600ACS-XXX | 20-pin plastic shrink DIP (300 mil) |

| $\mu$ PD6600AGS-XXX | 20-pin plastic SOP (300 mil)        |

|                     |                                     |

Remark XXX indicates ROM code suffix.

vw.DataSheet4U.com

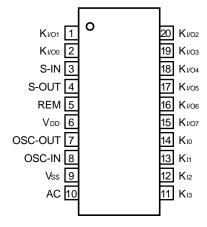

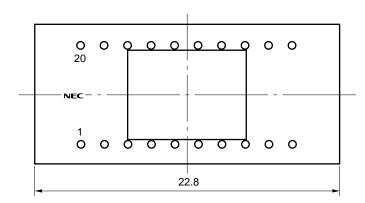

# PIN CONFIGURATION (TOP VIEW)

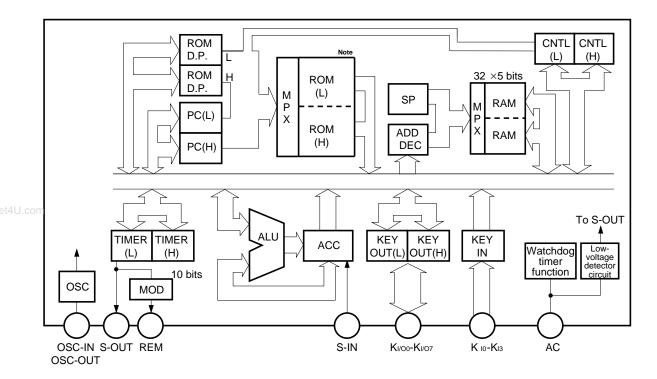

#### **BLOCK DIAGRAM**

Note ROM capacity depends on the products.

#### **DIFFERENCES AMONG PRODUCTS**

| Item Product Name          | μPD6124A                            | μPD6600A                       |  |  |  |  |

|----------------------------|-------------------------------------|--------------------------------|--|--|--|--|

| ROM Capacity               | 1002 × 10 bits (Mark ROM)           | 512 × 10 bits (Mask ROM)       |  |  |  |  |

| RAM Capacity               | 32 × 5 bits                         |                                |  |  |  |  |

| I/O Pins                   | 8 (KI/O0-KI/O7)                     |                                |  |  |  |  |

| S-IN Pins                  | Provided                            |                                |  |  |  |  |

| Current Consumption        | 2 μΑ                                |                                |  |  |  |  |

| (fosc = STOP) (MAX.)       |                                     |                                |  |  |  |  |

| S-IN High Level Input      | 30 μΑ                               |                                |  |  |  |  |

| Current (MAX.)             |                                     |                                |  |  |  |  |

| Transmit Carrier Frequency | fosc/12, fosc/8                     |                                |  |  |  |  |

| Low-voltage Detector       | Provided                            |                                |  |  |  |  |

| (Reset) Circuit            |                                     |                                |  |  |  |  |

| Supply Current             | V <sub>DD</sub> = 2.2 to 5.5 V      | V <sub>DD</sub> = 2.2 to 3.6 V |  |  |  |  |

| Package                    | 20-pin plastic SOP (300 mil)        |                                |  |  |  |  |

|                            | 20-pin plastic shrink DIP (300 mil) |                                |  |  |  |  |

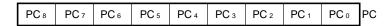

# 1. PROGRAM COUNTER (PC) ....... 9 BITS : $\mu$ PD6600A 10 BITS : $\mu$ PD6124A

The program counter (PC) is a binary counter, which holds the address information for the program memory.

Figure 1-1. Program Counter Organization

(a)  $\mu$  PD6600A

**(b)**  $\mu$ **PD6124A**

PC 9 PC 8 PC 7 PC 6 PC 5 PC 4 PC 3 PC 2 PC 1 PC 0 PC

ww.DataSneet4U.com

Normally, the program counter contents are automatically incremented each time an instruction is executed, according to the number of instruction bytes.

When executing a jump instruction (JMP0, JC, JF), the program counter indicates the jump destination.

Immediate data or the data memory contents are loaded to all or some bits of the PC.

When executing the call instruction (CALL0), the PC contents are incremented (+1) and saved into the stack memory. Then, a value needed for each jump instruction will be loaded.

When executing the return instruction (RET), the stack memory contents are double incremented (+2) and loaded into the PC.

When "all clear" is input or on reset, the PC contents are cleared to "000H".

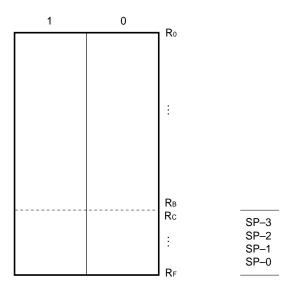

#### 2. STACK POINTER (SP) ...... 2 BITS

This 2-bit register holds the start address information for the stack area. The stack area is shared with the data memory.

The SP contents are incremented, when the call instruction (CALL0) is executed. They are decremented, when the return instruction (RET) is executed.

The stack pointer is cleared to "00B" after reset or "all clear" is input, and indicates the highest address FH for the data memory as the stack area.

The figure below shows the relationship for the stack pointer and the data memory area.

| Data n | nemory | (SP)                 |

|--------|--------|----------------------|

|        |        | Rc — 11B             |

|        |        | R <sub>D</sub> — 10B |

|        |        | RE - 01B             |

|        |        | R <sub>F</sub> — 00B |

If the stack pointer overflows or underflows, it is determined that the CPU overflows, and the PC internal reset signal will be generated.

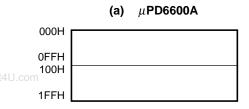

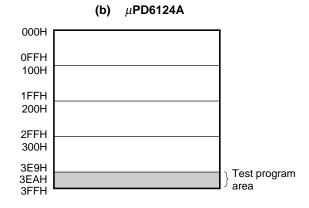

3. PROGRAM MEMORY (ROM) ....... 512 STEPS imes 10 BITS :  $\mu$ PD6600A 1002 STEPS imes 10 BITS :  $\mu$ PD6124A

The program memory (ROM) is configured in 10 bits steps. It is addressed by the program counter. Program and table data are stored in the program memory.

Figure 3-1. Program Memory Map

4. DATA MEMORY (RAM) ....... 32 WORDS  $\times$  5 BITS

The data memory is a RAM of 32 words  $\times$  5 bits. The data memory stores processing data. In some cases, the data memory is processed in 8-bit units. R<sub>0</sub> may be used as the data pointer for the ROM.

After power application, the RAM will be undefined. The RAM retains the previous data on reset.

Figure 4-1. Data Memory Organization

Caution Avoid using the RAM areas RD, RE, and RF in a CALL routine as much as possible because these areas are also used as stack memory areas (to prevent program hang-up in case the value of the SP is destroyed due to some reason such as noise).

When using these RAM areas as general-purpose RAM areas, be sure to include stack pointer checking in the main routine.

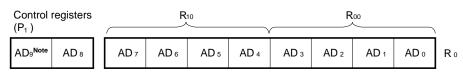

#### 5. DATA POINTER (Ro)

Ro (R10, R00) for the data memory can serve as the data pointer for the ROM.

Ro specifies the low-order 8 bits in the ROM address. The high-order 2 bits in the ROM address are specified by the control register.

Table referencing for ROM data can be easily executed by calling the ROM contents by setting the ROM address to the data pointer.

On reset or "all clear" is input, it becomes undefined.

Figure 5-1. Data Pointer Organization

w.DataSneet40.com

**Note**  $\mu PD6600A: AD_9 = 0$

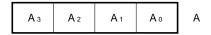

#### 6. ACCUMULATOR (A) ...... 4 BITS

The accumulator (A) is a 4-bit register. The accumulator plays a major role in each operation. On reset or "all clear" is input, it becomes undefined.

Figure 6-1. Accumulator Organization

#### 7. ARITHMETIC LOGIC UNIT (ALU) ....... 4 BITS

The arithmetic logic unit (ALU) is a 4-bit operation circuit, and executes simple operations, such as arithmetic operations.

#### 8. FLAGS

#### (1) Status flag

When the status for each pin is checked by the STTS instruction, if the condition coincides with the condition specified by the STTS instruction, the status flag (F) is set (to 1).

On reset or "all clear" is input, it becomes undefined.

#### (2) Carry flag

When the INC (increment) instruction or the RL (rotate left) instruction is executed, if a carry is generated from the MSB for the accumulator, the carry flag (C) is set (to 1).

The carry flag (C) is also set (to 1), if the contents for the accumulator are "FH", when the SCAF instruction is executed.

On reset or "all clear" is input, it becomes undefined.

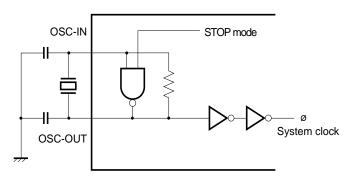

#### SYSTEM CLOCK GENERATOR

The system clock generator consists of a resonator, which uses a ceramic resonator (400kHz to 500kHz).

Figure 9-1. System Clock Generator

In the STOP mode (oscillation stop HALT instruction), the oscillator in the system clock generator stops its operation, and the system clock  $\emptyset$  is stopped.

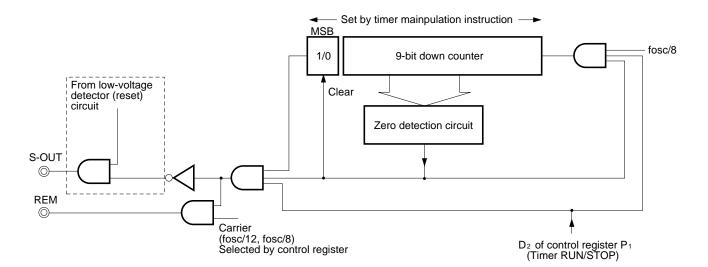

#### 10. TIMER

The timer block determines the transmission output pattern. The timer consists of 10 bits, of which 9 bits serve as the 9-bit down counter and the remaining 1 bit serves as the 1-bit latch, which determines the carrier output validity.

The 9-bit down counter is decremented (–1) every 8/fosc(s) in synchronization with the machine cycle, after starting down count operation. Down counting stops after all of the 9 bits become 0. When down counting is stopped, the signal indicating that the timer operation has stopped, is output. If the CPU is at standby (HALT TIMER) for the timer operation completion, the standby (HALT) condition is released and the next instruction will be executed. If the next instruction again sets the value of the down counter, down counting continues without any error (the carrier output of the REM pin is not affected).

Set the down count time according to the following calculation; (set value (HEX) + 1)  $\times$  8/fosc. Setting the value to the timer is done by the timer manipulation instruction.

When the down counter is operating, the remote control transmission carrier can be output to the REM pin. Whether or not to output the carrier can be selected by the MSB for the timer register block. Set "1", when outputting the carrier, or "0", when not outputting the carrier.

If all the down counter bits become "0", when outputting the carrier, the carrier output will be stopped. When not outputting the carrier, the REM pin output will become low level.

A signal in synchronization with the REM output is output to the S-OUT pin. However, the waveform for the S-OUT pin is low, when the carrier is being output to the REM pin, or it is high, when the carrier is not being output to the REM pin.

If the HALT instruction, which initiates the oscillation stop mode, is executed when the down counter is operating, the oscillation stop mode is initiated after down counting is stopped (after 0).

Timer operation STOP/RUN is controlled by the control register (P<sub>1</sub>). (Refer to **13. CONTROL REGISTER (P<sub>1</sub>).**) At reset (all clear) time, the REM pin goes low and S-OUT pin goes high. All 10 bits of the timer are cleared to 000H.

- Cautions 1. Because the timer clock is not synchronized with the carrier output, the pulse width may be shortened at the beginning and end of the carrier output.

- 2. Reset caused by the low-voltage detector circuit causes the S-OUT pin to output low level.

Figure 10-1. Timer Block Organization

#### 11. PIN FUNCTIONS

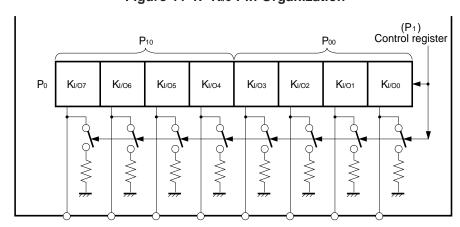

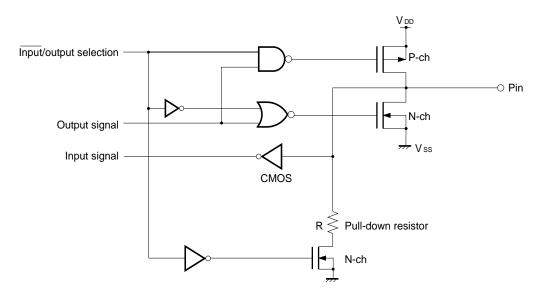

#### 11.1 K<sub>I/O</sub> PIN (P<sub>0</sub>)

This is the 8-bit I/O pin for key-scan output. When the control register (P<sub>1</sub>) is set for the input port, the port can be used as an 8-bit input pin. When the port is set for the input mode, all of these pins are pulled down to the Vss level inside the LSI.

★ At reset (all cleared), the value of I/O mode and output latch becomes undefined.

Figure 11-1. K<sub>VO</sub> Pin Organization

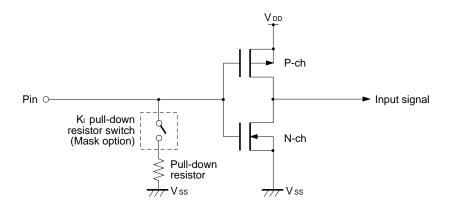

#### 11.2 KI/O PULL-DOWN RESISTOR CONFIGURATION

When  $K_{I\!I\!O}$  is set to the input mode, pull-down resistor R is turned on.

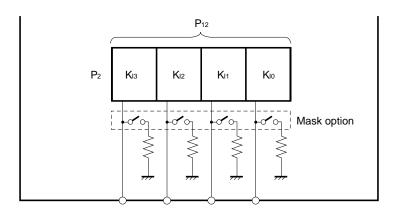

#### 11.3 K<sub>I</sub> PIN (P<sub>12</sub>)

This is the 4-bit pin for key input. All of these pins can be pulled down to the Vss level by mask option.

Figure 11-2. Kı Pin Organization

ww.DataSheet4U.com

#### 11.4 KI PULL-DOWN RESISTOR CONFIGURATION

When the pull-down resistor switch is turned on (set 1) by the mask option, pull-down resistor R is turned on.

Caution When using the pin as the key switch, turn on the pull-down resistor switch by the mask option.

#### 11.5 S-OUT PIN

By going low whenever the carrier frequency is output from the REM pin, the S-OUT pin indicates that communication is in progress.

★ The S-OUT pin is CMOS output.

The S-OUT pin goes high on reset.

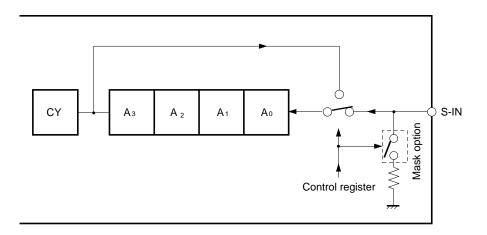

#### 11.6 S-IN PIN (Do BIT OF P1)

To input serial data, use the S-IN pin. When control register (P<sub>1</sub>) is set to serial input mode, the S-IN pin is connected as an input to the LSB of the accumulator; the S-IN pin can be pulled down to the Vss level by a mask option from within the LSI. In this state, if the rotate-left accumulator instruction (RL A) is executed, the data on the S-IN pin is copied to the LSB of the accumulator.

If the control register is released from serial input mode, the S-IN pin goes into a high-impedance state, but no through www.DataSheet4Ucurrent flows internally.

When the RL A instruction is executed, the MSB is copied to the LSB.

★ At reset (all cleared), the S-IN pin goes into a high-impedance state.

Caution The  $\mu$ PD6123 is not provided with an S-IN pin.

Figure 11-3. Configuration of the S-IN Pin

# 12. PORT REGISTER ( $P_{\times}$ )

$K_{I/O},\,K_{I},$  and the control register are handled as port registers.

The table below shows the relations between the port registers and pins.

Table 12-1. Relations between Port Registers and Pins

| Pin  | Input                | Mode                | Output                                 | Mode         | On Decet                             |

|------|----------------------|---------------------|----------------------------------------|--------------|--------------------------------------|

| Name | Read Write           |                     | Read                                   | Write        | On Reset                             |

| Kı/o | Pin status           | Output latch        | Pin status                             | Output latch | Undefined [input mode, output latch] |

| Kı   | Pin status           | _                   | _                                      | _            | Input mode                           |

| S-IN | Pin status is read I | by RL A instruction | High impedance (Do of P1 register = 0) |              |                                      |

www.DataSheet4U.com

| P <sub>1</sub> × (H) | P <sub>0</sub> × (L) |    |

|----------------------|----------------------|----|

| K <sub>1/07-4</sub>  | K1/03-0              | Po |

| Control register (H) | Control register (L) | P₁ |

| K <sub>13-0</sub>    | P <sub>02</sub>      | Pa |

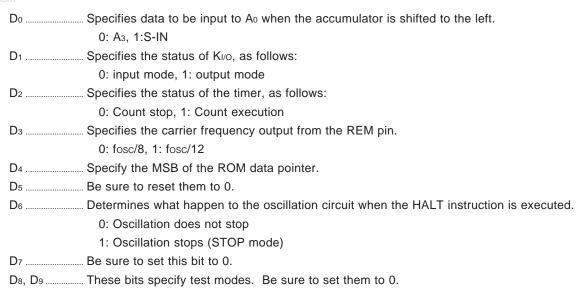

#### 13. CONTROL REGISTER (P1)

The control register contains of 10 bits. The controllable items are shown in Table 13-1.

#### Table 13-1. Control Register (P<sub>1</sub>) (1/2)

#### (a) $\mu$ PD6124A

| ı           | Bit | D 9               | D 8 | D7 | D 6         | <b>D</b> 5              | D 4                     | Dз      | D 2   | D <sub>1</sub> | D٥             |

|-------------|-----|-------------------|-----|----|-------------|-------------------------|-------------------------|---------|-------|----------------|----------------|

| Na          | ame | Test mode         |     | _  | HALT        | D.P.<br>AD <sub>9</sub> | D.P.<br>AD <sub>8</sub> | MOD     | Timer | <b>K</b> 1/0   | RL Acc<br>A₀ ← |

| .com<br>Set | 0   | Be sure to set 0. |     |    | NOP         | AD9=0                   | AD8=0                   | fosc/8  | STOP  | IN             | Аз             |

| Valu        | 1 1 |                   |     |    | OSC<br>STOP | AD9=1                   | AD8=1                   | fosc/12 | RUN   | OUT            | S-IN           |

0: A<sub>3</sub>, 1:S-IN

D<sub>1</sub> ...... Specifies the status of K<sub>1</sub>/O, as follows:

0: input mode, 1: output mode

D<sub>2</sub> ...... Specifies the status of the timer, as follows:

0: Count stop, 1: Count execution

D<sub>3</sub> ...... Specifies the carrier frequency output from the REM pin.

0: fosc/8, 1: fosc/12

D<sub>4</sub>, D<sub>5</sub> ...... Specify the high-order 2 bits of the ROM data pointer.

D6 ....... Determines what happen to the oscillation circuit when the HALT instruction is executed.

0: Oscillation does not stop

1: Oscillation stops (STOP mode)

D<sub>7</sub> ...... Be sure to set this bit to 0.

$D_8,\ D_9$  ...... These bits specify test modes. Be sure to set them to 0.

**Remark**  $D_0 = D_8 = D_9 = 0$  on reset, and the other bits are undefined.

#### Table 13-1. Control Register (P<sub>1</sub>) (2/2)

#### (b) $\mu$ PD6600A

| Bit   |   | D 9               | D 8 | D 7 | D 6         | D 5                     | D 4                     | Dз      | D 2   | D <sub>1</sub> | Dο                         |

|-------|---|-------------------|-----|-----|-------------|-------------------------|-------------------------|---------|-------|----------------|----------------------------|

| Nam   | e | Test mode         |     | _   | HALT        | D.P.<br>AD <sub>9</sub> | D.P.<br>AD <sub>8</sub> | MOD     | Timer | <b>K</b> 1/0   | RL Acc<br>A <sub>0</sub> ← |

| Set   | 0 | Be sure to set 0. |     |     | NOP         | Be sure to              | AD8=0                   | fosc/8  | STOP  | IN             | Аз                         |

| Value | 1 |                   |     |     | OSC<br>STOP | set 0.                  | AD <sub>8</sub> =1      | fosc/12 | RUN   | OUT            | S-IN                       |

www.DataSheet4LL.com

**Remark**  $D_0 = D_8 = D_9 = 0$  on reset, and the other bits are undefined.

#### 14. STANDBY FUNCTION (HALT INSTRUCTION)

The  $\mu$ PD6600A is provided with the standby mode (HALT instruction), in order to reduce the power consumption, when not executing the program. Clock oscillation can be stopped in the standby mode (STOP mode).

In the standby mode, the program execution stops. However, the contents of the internal registers and the data memory are all retained.

#### 14.1 STOP MODE (OSCILLATION STOP HALT INSTRUCTION)

In the STOP mode, the operation of the system clock generator (ceramic resonator oscillation circuit) stops. Therefore, operations requiring the system clock will stop.

If the HALT instruction is executed during timer operation, the program counter stops. The oscillation stop mode will be initiated, after the timer count down operation is completed.

#### HALT MODE (OSCILLATION CONTINUE HALT INSTRUCTION)

The CPU stops its operation, until the HALT release condition is satisfied.

The system clock operation continues in this mode.

#### 14.3 STANDBY RELEASE CONDITIONS

- (1) S-IN input

- (2) Ki/o input

- Kı input (3)

- (4) Timer count down operation completion

Remark Either high level or low level can be specified for setting a release condition by input.

Table 14-1. Standby Mode Releasing Condition

| Dз  | D <sub>2</sub> | D <sub>1</sub> | Do | Releasing<br>Condition | Remarks                                                        |  |  |  |

|-----|----------------|----------------|----|------------------------|----------------------------------------------------------------|--|--|--|

|     | 0              | 0 0 0 S-IN     |    | S-IN                   | When RL ←A ₃ is selected, the standby mode is always released. |  |  |  |

| 0/1 | 0              | 0 0 1 K vo     |    | <b>K</b> 1/0           | Valid only in the IN mode.                                     |  |  |  |

|     | 0              | 1              | 0  | Κı                     |                                                                |  |  |  |

| 0   | 0              | 1              | 1  | Timer                  | Released when 0.                                               |  |  |  |

"1"...High level detection

Releasing condition: "0"...Low level detection

#### 15. AC PIN (ALL CLEAR PIN)

Internal part of the CPU including the program counter can be reset by setting the AC pin to the low level.

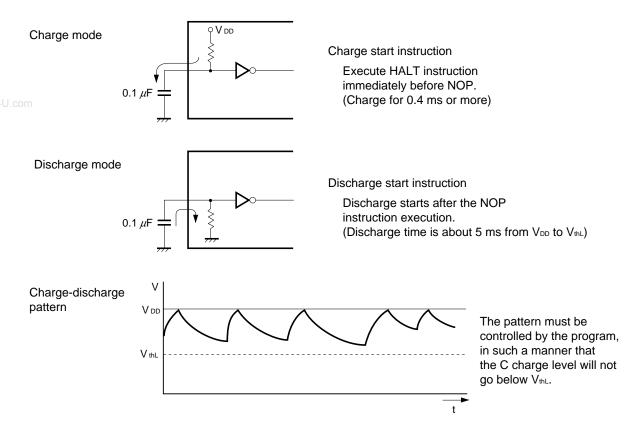

#### WATCHDOG TIMER FUNCTION

A power-on reset function and a CR watchdog timer function, that can be controlled by program, can be realized by connecting a 0.1  $\mu$ F capacitor across the AC pin and the Vss.

Caution When the watchdog timer function is not used, switch to charging mode by executing a NOP instruction immediately before a HALT instruction at the beginning of the program. (Be sure to connect the capacitor.)

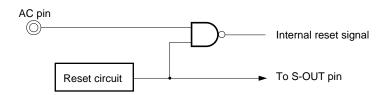

#### 16. LOW-VOLTAGE DETECTOR (RESET) CIRCUIT

The  $\mu$ PD6124A and 6600A are internally provided with the low-voltage detector (reset) circuit, in order to prevent program hang-up.

When V<sub>DD</sub> goes down to 1 V or below, an internal reset signal is generated. In the reset condition, a low level is output to the S-OUT pin.

w.DataSheet4U.com

Caution The low-voltage detector circuit starts operating at a voltage ranging from 1 to 2.2 V. Hence, if the supply voltage is 2 V or lower, the program counter may hang up before the low-voltage detector circuit operates.

#### 17. MASK OPTIONS (PLA DATA)

The following items can be selected by mask option selection:

- Provide/not provide K<sub>I</sub>, S-IN pin pull-down resistor

- Carrier duty selection (1/2, 1/3) at fosc/12

- · Hang-up detection specification

Mask option data should be registered at the object code end.

#### BIT ASSIGNMENT BY SWITCH SELECTION

| ω,      |                               | MSB         | MSB          |                          |                   |   |   |                               |   |

|---------|-------------------------------|-------------|--------------|--------------------------|-------------------|---|---|-------------------------------|---|

| Address | Corresponding<br>Portion      |             |              |                          |                   |   |   |                               |   |

| _       |                               | 7           | 6            | 5                        | 4                 | 3 | 2 | 1                             | 0 |

| 0       | Kı<br>pull-down resistor Note | Кіз         | <b>K</b> 12  | K <sub>I1</sub>          | Кю                | 0 |   |                               |   |

| 1       | Duty<br>S-IN                  | 0           | 0            | 0                        | Duty<br>selection | 0 | 0 | S-IN<br>pull-down<br>resistor | 0 |

| 2       | Hang-up detection             | Kı/o<br>ALL | HALT<br>S-IN | HALT<br>K <sub>I/O</sub> | HALT<br>Kı        |   |   | 0                             |   |

**Note** The setting (bit) positions differ from the  $\mu$ PD6125A and 6126A.

#### SWITCH FOR DATA

(1) Pull-down resistor

When 0 ... Not provided (OFF)

When 1 ··· Provided (ON)

(2) Modulation duty (at fosc/12)

When 0 ··· 1/2 duty When 1 ··· 1/3 duty

Hang-up detection (3)

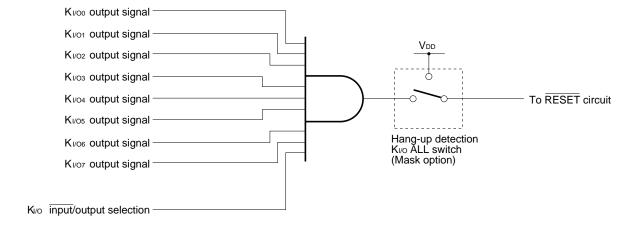

<1> KI/O ALL

If the switch for hang-up detection K<sub>1</sub>/O ALL is set to ON (1) by mask option, the system is reset if, in oscillation HALT (STOP) mode, the Ki/o pin is in input mode, or if at least one of the Ki/o pins is low (AC pin discharge mode).

When 0 ··· No reset function (OFF)

When 1 ··· Reset function (ON)

To use a pin as a key source of a key matrix, be sure to set the switch to ON by mask option.

Figure 17-1. Hang-up Detection K<sub>VO</sub> ALL Configuration Diagram

<2> HALT releasing condition specification (S-IN, K<sub>1</sub>/o, K<sub>1</sub>)

If the condition specified by mask option to be unused is satisfied in the HALT mode, the system is reset.

When 0 ··· Used

When 1 ··· Unused

Caution Be sure to specify the HALT mode of the unused releasing condition to be unused (set).

#### 18. PROGRAM DEVELOPMENT TOOLS

To develop programs for the  $\mu$ PD6124A and 6600A, an assembler and an emulator for the  $\mu$ PD612X series are available from I.C. Corp. For details, contact IC Corp.

IC Corporation

6th Barnet Gotanda Bldg.

1-9-5 Higashi-Gotanda, Shinagawa-ku

Tel. 03-3447-3793

Fax. 03-3440-5606

#### ★ Caution

To develop the programs for the  $\mu$ PD6124A and 6600A, use the  $\mu$ PD6124 because the  $\mu$ PD6124A and 6600A are not available as the target devices for assembly and emulation.

The upper limit of ROM addresses is different in the  $\mu$ PD6124A/6600A and  $\mu$ PD6124. Make sure that the program does not exceed 512 steps by checking the end address of the assembly listing after assembling the program.

The mask option of the  $\mu$ PD6124A/6600A is the same as that of the  $\mu$ PD6124.

#### 19. ORDERING ROM CODE

<1> To generate the data required for ordering a mask ROM, after assembling the program, convert the HEX file to a ROM file by using the PROM utility program "UPDPROM".

Caution When using "UPDPROM" select "27256" for PROM TYPE.

<2> Confirm that the instruction ROM code data is stored in addresses 0 through 7D3H (3FFH in  $\mu$ PD6600A) of the PROM.

Also confirm that the mask option ROM code data are stored in addresses 7FF0H through 7FF2H.

#### 20. INSTRUCTION SET

#### ACCUMULATOR MANIPULATION INSTRUCTIONS

|            | Rr       | I   | R <sub>10</sub> | R <sub>11</sub> | R <sub>12</sub> | R <sub>1F</sub> | R <sub>00</sub> | R <sub>01</sub> | RoF |

|------------|----------|-----|-----------------|-----------------|-----------------|-----------------|-----------------|-----------------|-----|

| ANL        | A, Rr    |     | D00             | D01             | D02             | D0F             | D20             | D21             | D2F |

| ANL        | A, @R₀H  | D10 |                 |                 |                 |                 |                 |                 |     |

| ANL        | A, @R₀L  | D30 |                 |                 |                 |                 |                 |                 |     |

| ANL        | A, #data | D31 |                 |                 |                 |                 |                 |                 |     |

| ORL        | A, Rr    |     | E00             | E01             | E02             | E0F             | E20             | E21             | E2F |

| ORL        | A, @R₀H  | E10 |                 |                 |                 |                 |                 |                 |     |

| ORL        | A, @R₀L  | E30 |                 |                 |                 |                 |                 |                 |     |

| ORL        | A, #data | E31 |                 |                 |                 |                 |                 |                 |     |

| J. com XRL | A, Rr    |     | A00             | A01             | A02             | A0F             | A20             | A21             | A2F |

| XRL        | A, @R₀H  | A10 |                 |                 |                 |                 |                 |                 |     |

| XRL        | A, @R₀L  | A30 |                 |                 |                 |                 |                 |                 |     |

| XRL        | A, #data | A31 |                 |                 |                 |                 |                 |                 |     |

| INC        | Α        | A13 |                 |                 |                 |                 |                 |                 |     |

| RL         | Α        | F13 |                 |                 |                 |                 |                 |                 |     |

www DataSheet4LL

#### INPUT/OUTPUT INSTRUCTIONS

|                      | P <sub>P</sub> P <sub>10</sub> | P <sub>11</sub> | P <sub>12</sub> | P <sub>00</sub> | P <sub>01</sub> | P <sub>02</sub> |

|----------------------|--------------------------------|-----------------|-----------------|-----------------|-----------------|-----------------|

| IN A, P <sub>P</sub> | F18                            | F19             | F1A             | F38             | F39             | F3A             |

| OUT Pp, A            | 218                            | 219             | 21A             | 238             | 239             | 23A             |

| ANL A, P             | D18                            | D19             | D1A             | D38             | D39             | D3A             |

| ORL A, P             | E18                            | E19             | E1A             | E38             | E39             | E3A             |

| XRL A, P             | A18                            | A19             | A1Z             | A38             | A39             | A3A             |

|     | PP       | P₀  | P <sub>1</sub> | $P_2$ |

|-----|----------|-----|----------------|-------|

| OUT | P⊳ #data | 318 | 319            | 31A   |

P<sub>1P</sub> and P<sub>0P</sub> operate in pair format

#### DATA TRANSFER INSTRUCTIONS

| Rr                                                      |                   | R <sub>10</sub> | R <sub>11</sub> | R <sub>12</sub> | R <sub>1F</sub> | R00 | R <sub>01</sub> | Rof |

|---------------------------------------------------------|-------------------|-----------------|-----------------|-----------------|-----------------|-----|-----------------|-----|

| MOV A, Rr<br>MOV A, @R₀H<br>MOV A, @R₀H<br>MOV A, #data | F10<br>F30<br>F31 | F00             | F01             | F02             | F0F             | F20 | F21             | F2F |

| MOV Rr, A                                               |                   | 200             | 201             | 202             | 20F             | 220 | 221             | 22F |

| Rr                         | R₀  | R <sub>1</sub> | R <sub>2</sub> | RF  |

|----------------------------|-----|----------------|----------------|-----|

| MOV R <sub>r</sub> , #data | 300 | 301            | 302            | 30F |

| MOV Rr, @Ro                | 320 | 321            | 322            | 32F |

R<sub>1r</sub> and R<sub>0r</sub> operate in pair format

#### **BRANCH INSTRUCTIONS**

$R_{\text{r}}$  $R_0$  $R_1$  $R_2$  $\mathsf{R}_\mathsf{F}$ JMP0 411 addr JMP0  $Rr^{\text{Note}}$ 401 402 40F JC 611  $Rr^{\text{Note}}$ JC 601 602 60F **JNC** addr 631 622 JNC Rr<sup>Note</sup> 621 62F \_ JF addr 711  $Rr^{\text{Note}}$ JF 701 702 70F JNF addr 731 JNF  $Rr^{\text{Note}}$ 721 722 72F

←Pair register

DataSHEE14U.COH

$\star$

Note r = 1 through F

r = 0 canot be used.

#### SUBROUTINE INSTRUCTIONS

| CALL0 addr | 312 | 411 |

|------------|-----|-----|

| RET        | 412 |     |

#### TIMER/COUNTER MANIPULATION INSTRUCTIONS

| Tt                     | T <sub>0-1</sub> | T <sub>1</sub> | Τo  |

|------------------------|------------------|----------------|-----|

| MOV A, T <sub>t</sub>  | 1                | F1F            | F3F |

| MOV T <sub>t</sub> , A |                  | 21F            | 23F |

| MOV T, #data           | 31F              |                |     |

| MOV T, @R <sub>0</sub> | 33F              |                |     |

#### **OTHER INSTRUCTIONS**

|                      |     | R <sub>00</sub> | R <sub>01</sub> | R <sub>02</sub> | Rof |

|----------------------|-----|-----------------|-----------------|-----------------|-----|

| HALT #data           | 111 |                 |                 |                 |     |

| STTS R <sub>0r</sub> |     | 120             | 121             | 122             | 12F |

| STTS #data           | 131 |                 |                 |                 |     |

| SCAF                 | D13 |                 |                 |                 |     |

| NOP                  | 000 |                 |                 |                 |     |

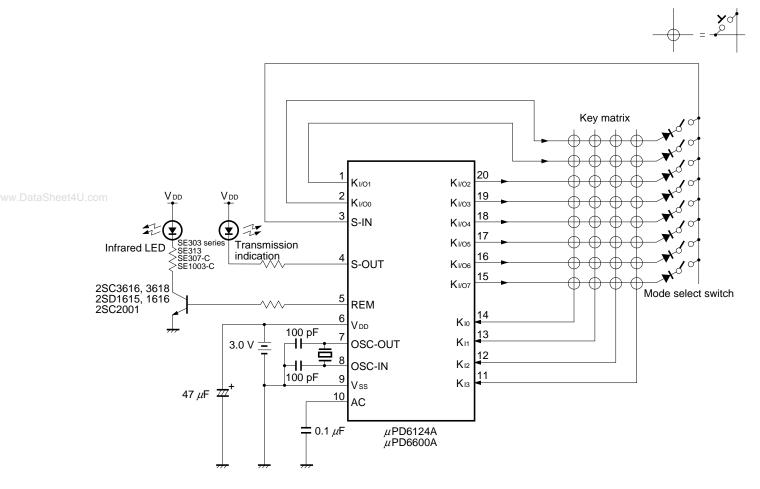

#### 21. APPLICATION CIRCUIT EXAMPLE

Caution The ceramic resonator start up capacitor value must be determined, by taking the voltage level and the oscillation start up characteristics for the ceramic resonator into consideration.

#### 22. ELECTRICAL SPECIFICATIONS

#### (1) $\mu$ PD6124A Electrical Specifications

#### ABSOLUTE MAXIMUM RATINGS ( $T_A = 25$ °C)

| Parameter                     | Symbol | Ratings           | Unit |

|-------------------------------|--------|-------------------|------|

| Supply Voltage                | Vdd    | -0.3 to +7.0      | V    |

| Input Voltage                 | Vin    | -0.3 to VDD + 0.3 | V    |

| Operating Ambient Temperature | ТА     | -20 to +75        | °C   |

| Storage Temperature           | Tstg   | -40 to +125       | °C   |

Even if one of the parameters exceeds its absolute maximum rating even momentarily, the quality of the product may be degraded. The absolute maximum rating therefore specifies the upper or lower limit of the value at which the product can be used without physical damages. Be sure to use the product(s) within the ratings.

#### RECOMMENDED OPERATING RANGE ( $T_A = -20$ to +75 °C)

| Parameter             | Symbol | MIN. | TYP. | MAX. | Unit |

|-----------------------|--------|------|------|------|------|

| Supply Voltage        | Vdd    | 2.2  |      | 5.5  | V    |

| Oscillation Frequency | fosc   | 400  |      | 500  | kHz  |

#### DC CHARACTERISTICS (V<sub>DD</sub> = 3.0 V, fosc = 455 kHz, T<sub>A</sub> = 25 $^{\circ}$ C)

| Parameter                       | Symbol         | Conditions                             | MIN. | TYP. | MAX. | Unit |

|---------------------------------|----------------|----------------------------------------|------|------|------|------|

| Supply Voltage                  | VDD            |                                        | 2.2  |      | 5.5  | V    |

| Current Consumption 1           | IDD1           | fosc = 455 kHz                         |      | 0.3  | 1.0  | mA   |

| Current Consumption 2           | IDD2           | fosc = STOP                            |      |      | 2.0  | μΑ   |

| REM High Level Output Current   | Іон1           | Vo = 1.0 V                             | -5   | -8   |      | mA   |

| REM Low Level Output Current    | IOL1           | Vo = 0.3 V                             | 0.5  | 1.5  | 2.5  | mA   |

| S-OUT High Level Output Current | Іон2           | Vo = 2.7 V                             | -0.3 | -1.0 | -2.0 | mA   |

| S-OUT Low Level Output Current  | IOL2           | Vo = 0.3 V                             | 1    | 1.5  |      | mA   |

| Kı High Level Input Current     | IIH1           | VI = 3.0 V                             | 10   |      | 30   | μΑ   |

| Kı High Level Input Current     | IIH1'          | VI = 3.0 V, without pull-down resistor |      |      | 0.2  | μΑ   |

| Ki Low Level Input Current      | IIL1           | VI = 0 V                               |      |      | -0.2 | μΑ   |

| Ki/o High Level Input Current   | IIH2           | VI = 3.0 V                             | 10   |      | 30   | μΑ   |

| Ki/o High Level Input Current   | IIH2'          | VI = 3.0 V, without pull-down resistor |      |      | 0.2  | μΑ   |

| KI/O Low Level Input Current    | lIL2           | VI = 0 V                               |      |      | -0.2 | μΑ   |

| Ki/o High Level Output Current  | Іонз           | Vo = 2.5 V                             | -1.5 | -2.0 | -4.0 | mA   |

| KI/O Low Level Output Current   | IOL3           | Vo = 2.1 V                             | 25   | 50   | 100  | μΑ   |

| S-IN High Level Input Current   | Іінз           | VI = 3.0 V                             | 6    |      | 30   | μΑ   |

| S-IN High Level Input Current   | IIH3'          | VI = 3.0 V, without pull-down resistor |      |      | 0.2  | μΑ   |

| S-IN Low Level Input Current    | IIL3           | VI = 0 V                               |      |      | -0.2 | μΑ   |

| Kı High Level Input Voltage     | VIH1           |                                        | 2.1  |      | 3.0  | V    |

| Kı Low Level Input Voltage      | VIL1           | VI = 3.0 V                             | 0    |      | 0.9  | V    |

| Ki/o High Level Input Voltage   | VIH2           |                                        | 1.3  |      | 3.0  | V    |

| Ki/o Low Level Input Voltage    | VIL2           |                                        | 0    |      | 0.4  | V    |

| S-IN High Level Input Voltage   | Іінз           |                                        | 1.1  |      | 3.0  | V    |

| S-IN Low Level Input Voltage    | lıl3           |                                        | 0    |      | 0.4  | V    |

| AC Pull-Up Resistor             | R1             | VI = 0 V                               | 0.3  |      | 3.0  | kΩ   |

| AC Pull-Down Resistor           | R <sub>2</sub> | VI = 2.7 V                             | 150  |      | 1500 | kΩ   |

| AC High Level Input Voltage     | VIH4           |                                        | 1.8  |      | 3.0  | V    |

| AC Low Level Input Voltage      | VIL4           |                                        | 0    |      | 1.2  | V    |

www.DataSheet4U

#### (2) $\mu$ PD6600A Electrical Specifications

#### ABSOLUTE MAXIMUM RATINGS (T<sub>A</sub> = 25 $^{\circ}$ C)

| Parameter                     | Symbol | Ratings           | Unit |

|-------------------------------|--------|-------------------|------|

| Supply Voltage                | Vdd    | -0.3 to +7.0      | V    |

| Input Voltage                 | Vin    | -0.3 to VDD + 0.3 | V    |

| Operating Ambient Temperature | TA     | -20 to +75        | °C   |

| Storage Temperature           | Tstg   | -40 to +125       | °C   |

Caution Even if one of the parameters exceeds its absolute maximum rating even momentarily, the quality of the product may be degraded. The absolute maximum rating therefore specifies the upper or lower limit of the value at which the product can be used without physical damages. Be sure to use the product(s) within the ratings.

#### RECOMMENDED OPERATING RANGE (TA = -20 to +75 °C)

| Parameter             | Symbol | MIN. | TYP. | MAX. | Unit |

|-----------------------|--------|------|------|------|------|

| Supply Voltage        | Vdd    | 2.2  |      | 3.6  | V    |

| Oscillation Frequency | fosc   | 400  |      | 500  | kHz  |

#### DC CHARACTERISTICS (V<sub>DD</sub> = 3.0 V, fosc = 455 kHz, T<sub>A</sub> = 25 $^{\circ}$ C)

| Parameter                       | Symbol | Conditions                             | MIN. | TYP. | MAX. | Unit |

|---------------------------------|--------|----------------------------------------|------|------|------|------|

| Supply Voltage                  | VDD    |                                        | 2.2  |      | 3.6  | V    |

| Current Consumption 1           | IDD1   | fosc = 455 kHz                         |      | 0.3  | 1.0  | mA   |

| Current Consumption 2           | IDD2   | fosc = STOP                            |      |      | 2.0  | μΑ   |

| REM High Level Output Current   | Іон1   | Vo = 1.0 V                             | -5   | -8   |      | mA   |

| REM Low Level Output Current    | lOL1   | Vo = 0.3 V                             | 0.5  | 1.5  | 2.5  | mA   |

| S-OUT High Level Output Current | Іон2   | Vo = 2.7 V                             | -0.3 | -1.0 | -2.0 | mA   |

| S-OUT Low Level Output Current  | lOL2   | Vo = 0.3 V                             | 1    | 1.5  |      | mA   |

| Kı High Level Input Current     | liH1   | VI = 3.0 V                             | 10   |      | 30   | μΑ   |

| Kı High Level Input Current     | lih1'  | VI = 3.0 V, without pull-down resistor |      |      | 0.2  | μΑ   |

| KI Low Level Input Current      | IIL1   | VI = 0 V                               |      |      | -0.2 | μΑ   |

| Kı/o High Level Input Current   | IIH2   | VI = 3.0 V                             | 10   |      | 30   | μΑ   |

| Kı/o High Level Input Current   | IIH2'  | VI = 3.0 V, without pull-down resistor |      |      | 0.2  | μΑ   |

| Ki/o Low Level Input Current    | IIL2   | VI = 0 V                               |      |      | -0.2 | μΑ   |

| Ki/o High Level Output Current  | Іонз   | Vo = 2.5 V                             | -1.5 | -2.0 | -4.0 | mA   |

| Ki/o Low Level Output Current   | IOL3   | Vo = 2.1 V                             | 25   | 50   | 100  | μΑ   |

| S-IN High Level Input Current   | Іінз   | VI = 3.0 V                             | 6    |      | 30   | μΑ   |

| S-IN High Level Input Current   | Іінз'  | VI = 3.0 V, without pull-down resistor |      |      | 0.2  | μΑ   |

| S-IN Low Level Input Current    | IIL3   | VI = 0 V                               |      |      | -0.2 | μΑ   |

| Kı High Level Input Voltage     | VIH1   |                                        | 2.1  |      | 3.0  | V    |

| Kı Low Level Input Voltage      | VIL1   | VI = 3.0 V                             | 0    |      | 0.9  | V    |

| Kı/o High Level Input Voltage   | VIH2   |                                        | 1.3  |      | 3.0  | V    |

| Ki/o Low Level Input Voltage    | VIL2   |                                        | 0    |      | 0.4  | V    |

| S-IN High Level Input Voltage   | Іінз   |                                        | 1.1  |      | 3.0  | V    |

| S-IN Low Level Input Voltage    | IIL3   |                                        | 0    |      | 0.4  | V    |

| AC Pull-Up Resistor             | R1     | VI = 0 V                               | 0.3  |      | 3.0  | kΩ   |

| AC Pull-Down Resistor           | R2     | VI = 2.7 V                             | 150  | 400  | 1500 | kΩ   |

| AC High Level Input Voltage     | VIH4   |                                        | 1.8  |      | 3.0  | V    |

| AC Low Level Input Voltage      | VIL4   |                                        | 0    |      | 1.2  | V    |

#### RECOMMENDED CERAMIC RESONATOR

(Common in  $\mu$ PD6124A and 6600A)

| Manufactura            | Duaduat | External Cap | acitance (pF) | Oscillation Volt | Pomorko |         |

|------------------------|---------|--------------|---------------|------------------|---------|---------|

| Manufacturer           | Product | C1           | C2            | MIN.             | MAX.    | Remarks |

| Murata Mfg. Co., Ltd.  | CSB375P | 220          | 220           | 2.0              | 3.3     |         |

|                        | CSB400P | 220          | 220           | 2.0              | 5.0     |         |

|                        | CSB455E | 100          | 100           | 2.0              | 5.0     |         |

|                        | CSB480E | 100          | 100           | 2.0              | 5.0     |         |

|                        | CSB500E | 100          | 100           | 2.0              | 3.3     |         |

| Toko Ceramic Co., Ltd. | CRK400  | 100          | 100           | 2.0              | 6.0     |         |

|                        | CRK455  | 100          | 100           | 2.0              | 6.0     |         |

|                        | CRK500  | 100          | 100           | 2.0              | 6.0     |         |

www.DataSheet4U.com

# NEC

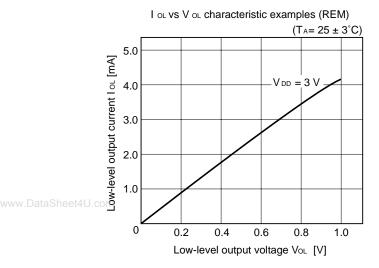

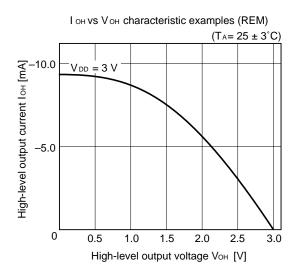

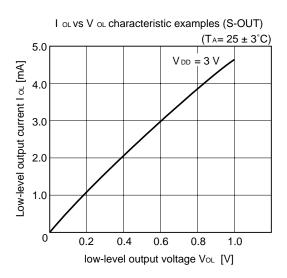

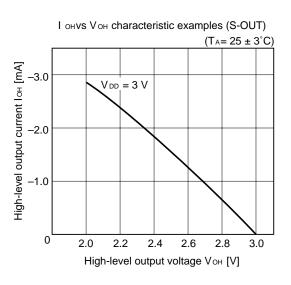

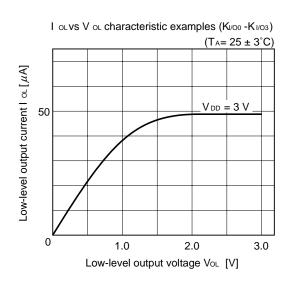

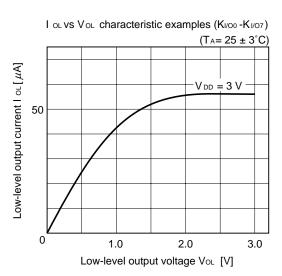

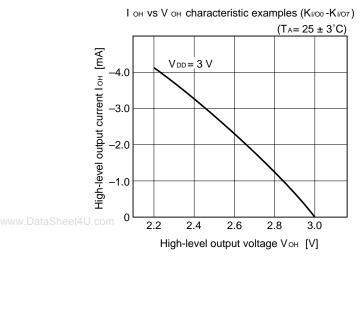

#### 23. CHARACTERISTICS CURVE (REFERENCE VALUE) (Common in $\mu$ PD6124A and 6600A)

High-level output voltage Vон [V]

www.DataSheet4U.com

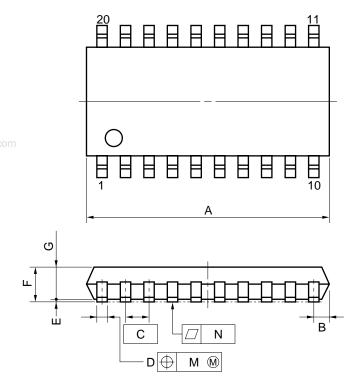

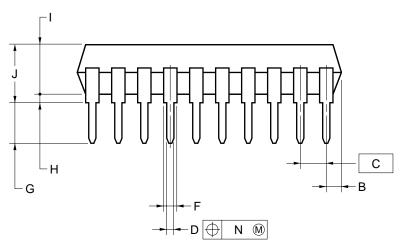

#### 24. PACKAGE DRAWINGS

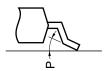

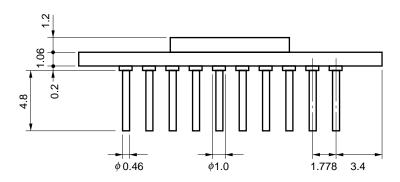

# 20 PIN PLASTIC SOP (300 mil)

detail of lead end

#### NOTE

Each lead centerline is located within 0.12 mm (0.005 inch) of its true position (T.P.) at maximum material condition.

| ITEM | MILLIMETERS            | INCHES                    |

|------|------------------------|---------------------------|

| A    | 13.00 MAX.             | 0.512 MAX.                |

| В    | 0.78 MAX.              | 0.031 MAX.                |

| С    | 1.27 (T.P.)            | 0.050 (T.P.)              |

| D    | $0.40^{+0.10}_{-0.05}$ | $0.016^{+0.004}_{-0.003}$ |

| Е    | 0.1±0.1                | 0.004±0.004               |

| F    | 1.8 MAX.               | 0.071 MAX.                |

| G    | 1.55                   | 0.061                     |

| Н    | 7.7±0.3                | 0.303±0.012               |

| I    | 5.6                    | 0.220                     |

| J    | 1.1                    | 0.043                     |

| K    | $0.20^{+0.10}_{-0.05}$ | $0.008^{+0.004}_{-0.002}$ |

| L    | 0.6±0.2                | $0.024^{+0.008}_{-0.009}$ |

| М    | 0.12                   | 0.005                     |

| N    | 0.10                   | 0.004                     |

| Р    | 3°+7°<br>-3°           | 3°+7°<br>-3°              |

P20GM-50-300B, C-4

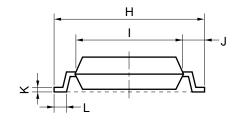

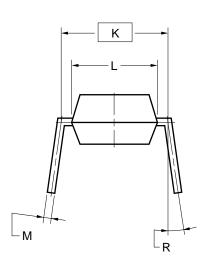

# 20PIN PLASTIC SHRINK DIP (300 mil)

w.DataSheet4U.com

#### NOTES

- 1) Each lead centerline is located within 0.17 mm (0.007 inch) of its true position (T.P.) at maximum material condition.

- 2) Item "K" to center of leads when formed parallel.

| ITEM | MILLIMETERS                    | INCHES                    |

|------|--------------------------------|---------------------------|

| A    | 19.57 MAX.                     | 0.771 MAX.                |

| В    | 1.78 MAX.                      | 0.070 MAX.                |

| С    | 1.778 (T.P.)                   | 0.070 (T.P.)              |

| D    | 0.50±0.10                      | $0.020^{+0.004}_{-0.005}$ |

| F    | 0.85 MIN.                      | 0.033 MIN.                |

| G    | 3.2±0.3                        | 0.126±0.012               |

| Н    | 0.51 MIN.                      | 0.020 MIN.                |

| ı    | 4.31 MAX.                      | 0.170 MAX.                |

| J    | 5.08 MAX.                      | 0.200 MAX.                |

| K    | 7.62 (T.P.)                    | 0.300 (T.P.)              |

| L    | 6.5                            | 0.256                     |

| М    | 0.25 <sup>+0.10</sup><br>-0.05 | 0.010+0.004               |

| N    | 0.17                           | 0.007                     |

| R    | 0~15°                          | 0~15°                     |

|      |                                |                           |

P20C-70-300B-1

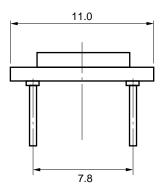

# 20-PIN SHRINK DIP FOR ES (REFERENCE) (UNITS IN mm)

#### 25. RECOMMENDED SOLDERING CONDITIONS

It is recommended that  $\mu$ PD6124A and 6600A be soldered under the following conditions.

For details on the recommended soldering conditions, refer to Information Document "Semiconductor Device Mounting Technology Manual" (C10535E).

For other soldering methods and conditions, consult NEC.

Table 25-1. Soldering Conditions of Surface-Mount Type

★  $\mu$ PD6124AGS-XXX: 20-pin plastic SOP (300 mil)  $\mu$ PD6600AGS-XXX: 20-pin plastic SOP (300 mil)

| ConSoldering Method | Soldering Conditions                                                                                                                                                 | Symbol for<br>Recommended Condition |

|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|

| Infrared Reflow     | Package peak temperature: 230°C, time: 30 seconds max. (210°C min.), number of times: 1                                                                              | IR30-00-1                           |

| VPS                 | Package peak temperature: 215°C, time: 40 seconds max. (200°C min.), number of times: 1                                                                              | VP15-00-1                           |

| Wave Soldering      | Vave Soldering  Soldering bath temperature: 260°C max., time: 10 seconds max., number of times: 1  Pre-heating temperature: 120°C max. (package surface temperature) |                                     |

| Partial Heating     | Pin temperature: 300°C max., time: 3 seconds max. (per side)                                                                                                         | _                                   |

Caution Do not use two or more soldering methods in combination (except the partial heating method).

#### \*

#### Table 25-2. Soldering Conditions of Through-Hole Type

$\mu$ PD6124ACS-XXX: 20-pin plastic shrink DIP (300 mil)  $\mu$ PD6600ACS-XXX: 20-pin plastic shrink DIP (300 mil)

| Soldering Method                   | Soldering Conditions                                          |  |  |

|------------------------------------|---------------------------------------------------------------|--|--|

| Wave Soldering (Only for pin part) | Soldering bath temperature: 260°C max., time: 10 seconds max. |  |  |

| Partial Heating                    | Pin temperature: 300°C max., time: 30 seconds max.            |  |  |

Caution The wave soldering must be performed at the pin part only. Note that the solder must not be directly contacted to the package body.

# APPENDIX $\mu$ PD612× SERIES PRODUCT LIST

| Part Number Item                         | μPD6124A                                 | μPD6600A                                 | μPD61P24                                 | μPD6125A                                                                                                  | μPD6126A                          |  |

|------------------------------------------|------------------------------------------|------------------------------------------|------------------------------------------|-----------------------------------------------------------------------------------------------------------|-----------------------------------|--|

| ROM capacity                             | 1002 × 10 bits<br>(mask ROM)             | 512 × 10 bits<br>(mask ROM)              | 1002 × 10 bits<br>(one-time PROM)        | 1002 × 10 bits<br>(mask ROM)                                                                              |                                   |  |

| RAM capacity                             | 32 × 5 bits                              |                                          |                                          |                                                                                                           |                                   |  |

| I/O pin                                  | 8 pins (K <sub>1/00-7</sub> )            |                                          |                                          | 12 pins 16 pins (Kuoo-<br>(Kuoo-7, I/Ooo-03) I/Ooo-03, I/O10-                                             |                                   |  |

| S-IN pin                                 | Provided                                 |                                          |                                          |                                                                                                           |                                   |  |

| Current consumption (fosc = STOP) (MAX.) | 2 μΑ                                     |                                          | 1 μΑ                                     |                                                                                                           |                                   |  |

| S-IN high-level input current (MAX.)     | 30 μΑ                                    |                                          | 15 μΑ                                    |                                                                                                           |                                   |  |

| Transmission carrier frequency           | fosc/12, fosc/8                          |                                          |                                          |                                                                                                           |                                   |  |

| Low-voltage detection (reset) function   | Provided                                 |                                          | None                                     |                                                                                                           |                                   |  |

| Mask option                              | Provided                                 |                                          | None (fixed)                             | Provided                                                                                                  |                                   |  |

| Supply voltage                           | V <sub>DD</sub> = 2.0 to 5.5 V           | $V_{DD} = 2.2 \text{ to } 3.6 \text{ V}$ | $V_{DD} = 2.2 \text{ to } 5.5 \text{ V}$ | V <sub>DD</sub> = 2.0 to 6.0 V                                                                            |                                   |  |

| Package                                  | 20-pin plastic SO     20-pin plastic shr | ,                                        |                                          | <ul> <li>24-pin plastic<br/>SOP (300 mil)</li> <li>24-pin plastic<br/>shrink DIP<br/>(300 mil)</li> </ul> | • 28-pin plastic<br>SOP (375 mil) |  |

#### **NOTES FOR CMOS DEVICES -**

## 1 PRECAUTION AGAINST ESD FOR SEMICONDUCTORS

Note: Strong electric field, when exposed to a MOS device, can cause destruction of the gate oxide and ultimately degrade the device operation. Steps must be taken to stop generation of static electricity as much as possible, and quickly dissipate it once, when it has occurred. Environmental control must be adequate. When it is dry, humidifier should be used. It is recommended to avoid using insulators that easily build static electricity. Semiconductor devices must be stored and transported in an anti-static container, static shielding bag or conductive material. All test and measurement tools including work bench and floor should be grounded. The operator should be grounded using wrist strap. Semiconductor devices must not be touched with bare hands. Similar precautions need to be taken for PW boards with semiconductor devices on it.

## (2) HANDLING OF UNUSED INPUT PINS FOR CMOS

Note: No connection for CMOS device inputs can be cause of malfunction. If no connection is provided to the input pins, it is possible that an internal input level may be generated due to noise, etc., hence causing malfunction. CMOS device behave differently than Bipolar or NMOS devices. Input levels of CMOS devices must be fixed high or low by using a pull-up or pull-down circuitry. Each unused pin should be connected to VDD or GND with a resistor, if it is considered to have a possibility of being an output pin. All handling related to the unused pins must be judged device by device and related specifications governing the devices.

# **③** STATUS BEFORE INITIALIZATION OF MOS DEVICES

Note: Power-on does not necessarily define initial status of MOS device. Production process of MOS does not define the initial operation status of the device. Immediately after the power source is turned ON, the devices with reset function have not yet been initialized. Hence, power-on does not guarantee out-pin levels, I/O settings or contents of registers. Device is not initialized until the reset signal is received. Reset operation must be executed immediately after power-on for devices having reset function.

# **Regional Information**

Some information contained in this document may vary from country to country. Before using any NEC product in your application, please contact the NEC office in your country to obtain a list of authorized representatives and distributors. They will verify:

- Device availability

- · Ordering information

- Product release schedule

- Availability of related technical literature

- Development environment specifications (for example, specifications for third-party tools and components, host computers, power plugs, AC supply voltages, and so forth)

- · Network requirements

In addition, trademarks, registered trademarks, export restrictions, and other legal issues may also vary from country to country.

#### **NEC Electronics Inc. (U.S.)**

Santa Clara, California Tel: 800-366-9782 Fax: 800-729-9288

#### **NEC Electronics (Germany) GmbH**

Duesseldorf, Germany Tel: 0211-65 03 02 Fax: 0211-65 03 490

#### **NEC Electronics (UK) Ltd.**

Milton Keynes, UK Tel: 01908-691-133 Fax: 01908-670-290

#### NEC Electronics Italiana s.r.1.

Milano, Italy Tel: 02-66 75 41 Fax: 02-66 75 42 99

#### **NEC Electronics (Germany) GmbH**

Benelux Office Eindhoven, The Netherlands Tel: 040-2445845 Fax: 040-2444580

#### **NEC Electronics (France) S.A.**

Velizy-Villacoublay, France Tel: 01-30-67 58 00 Fax: 01-30-67 58 99

#### **NEC Electronics (France) S.A.**

Spain Office Madrid, Spain Tel: 01-504-2787 Fax: 01-504-2860

#### **NEC Electronics (Germany) GmbH**

Scandinavia Office Taeby, Sweden Tel: 08-63 80 820 Fax: 08-63 80 388

#### **NEC Electronics Hong Kong Ltd.**

Hong Kong Tel: 2886-9318 Fax: 2886-9022/9044

#### **NEC Electronics Hong Kong Ltd.**

Seoul Branch Seoul, Korea Tel: 02-528-0303 Fax: 02-528-4411

#### **NEC Electronics Singapore Pte. Ltd.**

United Square, Singapore 1130

Tel: 253-8311 Fax: 250-3583

#### **NEC Electronics Taiwan Ltd.**

Taipei, Taiwan Tel: 02-719-2377 Fax: 02-719-5951

#### **NEC do Brasil S.A.**

Sao Paulo-SP, Brasil Tel: 011-889-1680 Fax: 011-889-1689

J96. 8

#### [MEMO]

The export of this product from Japan is regulated by the Japanese government. To export this product may be prohibited without governmental license, the need for which must be judged by the customer. The export or re-export of this product from a country other than Japan may also be prohibited without a license from that country. Please call an NEC sales representative.

www.DataSheet4UThe application circuits and their parameters are for reference only and are not intended for use in actual design-ins.

No part of this document may be copied or reproduced in any form or by any means without the prior written consent of NEC Corporation. NEC Corporation assumes no responsibility for any errors which may appear in this document

NEC Corporation does not assume any liability for infringement of patents, copyrights or other intellectual property rights of third parties by or arising from use of a device described herein or any other liability arising from use of such device. No license, either express, implied or otherwise, is granted under any patents, copyrights or other intellectual property rights of NEC Corporation or others.

While NEC Corporation has been making continuous effort to enhance the reliability of its semiconductor devices, the possibility of defects cannot be eliminated entirely. To minimize risks of damage or injury to persons or property arising from a defect in an NEC semiconductor device, customers must incorporate sufficient safety measures in its design, such as redundancy, fire-containment, and anti-failure features.

NEC devices are classified into the following three quality grades:

"Standard", "Special", and "Specific". The Specific quality grade applies only to devices developed based on a customer designated "quality assurance program" for a specific application. The recommended applications of a device depend on its quality grade, as indicated below. Customers must check the quality grade of each device before using it in a particular application.

Standard: Computers, office equipment, communications equipment, test and measurement equipment, audio and visual equipment, home electronic appliances, machine tools, personal electronic equipment and industrial robots

Special: Transportation equipment (automobiles, trains, ships, etc.), traffic control systems, anti-disaster systems, anti-crime systems, safety equipment and medical equipment (not specifically designed for life support)

Specific: Aircrafts, aerospace equipment, submersible repeaters, nuclear reactor control systems, life support systems or medical equipment for life support, etc.

The quality grade of NEC devices is "Standard" unless otherwise specified in NEC's Data Sheets or Data Books. If customers intend to use NEC devices for applications other than those specified for Standard quality grade, they should contact an NEC sales representative in advance.

Anti-radioactive design is not implemented in this product.

M4 96.5