# MEMORY Mobile FCRAM<sup>TM</sup> cmos

# **16 Mbit (1 M word** × **16 bit)**Mobile Phone Application Specific Memory

# MB82D01181E-60L

#### ■ DESCRIPTION

MB82D01181E is a Fast Cycle Random Access Memory (FCRAM) with asynchronous Static Random Access Memory (SRAM) interface containing 16,777,216 storages accessible in a 16-bit format. MB82D01181E is suited for mobile applications such as Cellular Handset and PDA.

Note: FCRAM is a trademark of Fujitsu Limited, Japan.

#### **■ FEATURES**

· Asynchronous SRAM Interface

• 1 M word × 16 bit Organization

• Low-voltage Operating Conditions :  $V_{DD} = 2.3 \text{ V}$  to 3.5 V• Wide Operating Temperature :  $T_A = 0 \text{ °C}$  to + 70 °C• Read/Write Cycle Time :  $t_{RC} = t_{WC} = 70 \text{ ns Min}$ • Fast Random Access Time :  $t_{AA} = t_{CE} = 60 \text{ ns Max}$ • Active current :  $t_{DDA1} = 20 \text{ mA Max}$

• Standby current :  $I_{DDs1} = 100 \mu A \text{ Max} (V_{DD} \le 3.1 \text{ V})$

• Power down current : IDDP = 10 μA Max

• Byte Control

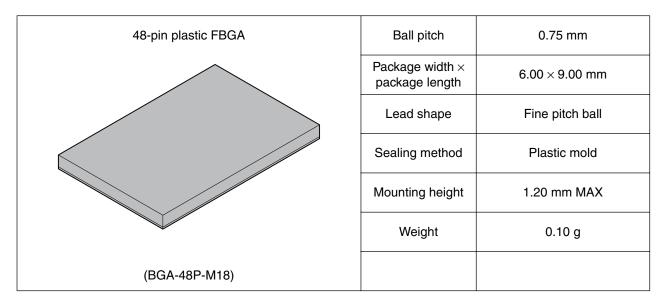

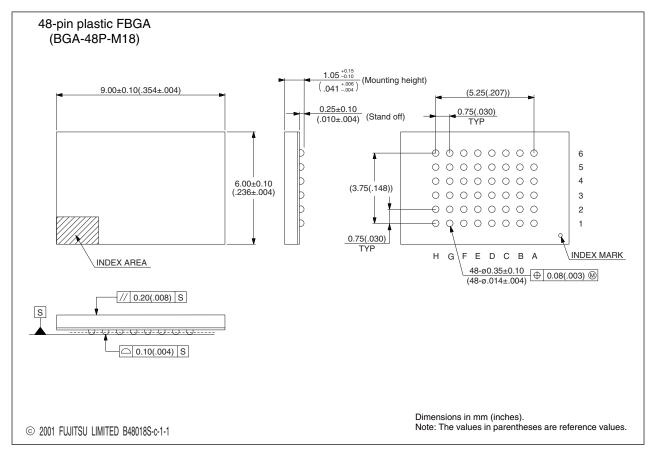

• Shipping Form : Wafer/Chip, 48-pin plastic FBGA

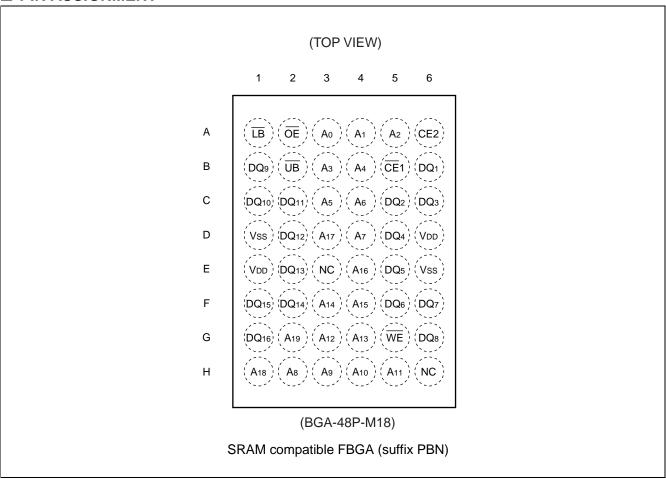

## **■ PIN ASSIGNMENT**

## **■ PIN DESCRIPTION**

| Pin Name                            | Description                     |

|-------------------------------------|---------------------------------|

| A <sub>19</sub> to A <sub>0</sub>   | Address Input                   |

| CE1                                 | Chip Enable (Low Active)        |

| CE2                                 | Chip Enable (High Active)       |

| WE                                  | Write Enable (Low Active)       |

| ŌĒ                                  | Output Enable (Low Active)      |

| LB                                  | Lower Byte Control (Low Active) |

| ŪB                                  | Upper Byte Control (Low Active) |

| DQ <sub>8</sub> to DQ <sub>1</sub>  | Lower Byte Data Input/Output    |

| DQ <sub>16</sub> to DQ <sub>9</sub> | Upper Byte Data Input/Output    |

| V <sub>DD</sub>                     | Power Supply                    |

| Vss                                 | Ground                          |

| NC                                  | No Connection                   |

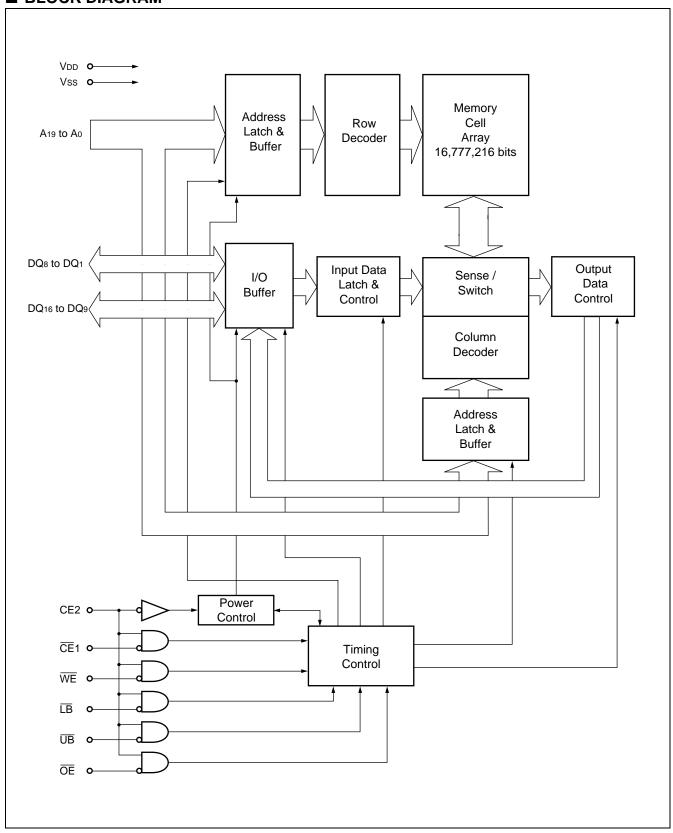

## **■ BLOCK DIAGRAM**

## **■ FUNCTION TRUTH TABLE**

| Mode               | CE2 | CE <sub>1</sub> | WE | ŌĒ | LB | UB | A19 to A0 | DQ <sub>8</sub> to DQ <sub>1</sub> | DQ <sub>16</sub> to DQ <sub>9</sub> | IDD  | Data<br>Retention |

|--------------------|-----|-----------------|----|----|----|----|-----------|------------------------------------|-------------------------------------|------|-------------------|

| Standby (Deselect) |     | Н               | Х  | Х  | Х  | Х  | Х         | High-Z                             | High-Z                              | IDDS |                   |

| Output Disable*1   |     |                 | Н  | Н  | Х  | Х  | *3        | High-Z                             | High-Z                              |      |                   |

| No Read            |     |                 |    |    | Н  | Н  | Valid     | High-Z                             | High-Z                              |      |                   |

| Read (Upper Byte)  |     |                 |    |    | Н  | L  | Valid     | High-Z                             | Output<br>Valid                     | •    |                   |

| Read (Lower Byte)  |     |                 | Н  | L  | L  | Н  | Valid     | Output<br>Valid                    | High-Z                              | •    |                   |

| Read (Word)        | Н   | L               |    |    | L  | L  | Valid     | Output<br>Valid                    | Output<br>Valid                     | IDDA | Yes               |

| No Write           |     |                 |    |    | Н  | Н  | Valid     | Invalid                            | Invalid                             |      |                   |

| Write (Upper Byte) |     |                 |    |    | Н  | L  | Valid     | Invalid                            | Input<br>Valid                      | •    |                   |

| Write (Lower Byte) |     |                 | L  | Н  | L  | Н  | Valid     | Input<br>Valid                     | Invalid                             | •    |                   |

| Write (Word)       |     |                 |    |    | L  | L  | Valid     | Input<br>Valid                     | Input<br>Valid                      | •    |                   |

| Power Down *2      | L   | Х               | Х  | Х  | Х  | Х  | Х         | High-Z                             | High-Z                              | IDDP | No                |

Note : L =  $V_{IL}$ , H =  $V_{IH}$ , X = either  $V_{IL}$  or  $V_{IH}$ , High-Z = High impedance

<sup>\*1 :</sup> Output disable mode should not be kept longer than 1  $\mu s$ .

<sup>\*2 :</sup> Power down mode can be entered from standby state and all DQ pins are in High-Z state.

<sup>\*3 :</sup> Can be either  $V_{\text{IL}}$  or  $V_{\text{IH}}$  but must be valid before read or write.

#### ■ ABSOLUTE MAXIMUM RATINGS

| Parameter                    | Symbol          | Rat         | Unit |       |

|------------------------------|-----------------|-------------|------|-------|

| Farameter                    | Symbol          | Min         | Max  | Offic |

| Supply Voltage *             | V <sub>DD</sub> | -0.5        | +3.6 | V     |

| Input Voltage *              | Vin             | -0.5        | +3.6 | V     |

| Output voltage *             | Vоит            | -0.5        | +3.6 | V     |

| Short Circuit Output Current | Іоит            | -50         | +50  | mA    |

| Storage Temperature          | Тѕтс            | <b>-</b> 55 | +125 | °C    |

<sup>\*:</sup> All voltages are referenced to Vss.

WARNING: Semiconductor devices can be permanently damaged by application of stress (voltage, current, temperature, etc.) in excess of absolute maximum ratings. Do not exceed these ratings.

#### ■ RECOMMENDED OPERATING CONDITIONS

| Parameter                           | Symbol               | Va                    | lue                                   | Unit  |

|-------------------------------------|----------------------|-----------------------|---------------------------------------|-------|

| raiametei                           | Symbol               | Min                   | Max                                   | Oilit |

|                                     | V <sub>DD</sub> (31) | 3.1                   | 3.5                                   | V     |

| Supply Voltage *1. *2               | V <sub>DD</sub> (27) | 2.7                   | 3.1                                   | V     |

| Supply Voltage *1, *2               | V <sub>DD</sub> (23) | 2.3                   | 2.7                                   | V     |

|                                     | Vss                  | 0                     | 0                                     | V     |

| High Level Input Voltage *1, *2, *3 | VIH (31)             | V <sub>DD</sub> × 0.8 | V <sub>DD</sub> + 0.2<br>and<br>≤ 3.5 | V     |

|                                     | VIH (23, 27)         | $V_{DD} \times 0.8$   | V <sub>DD</sub> + 0.2                 | V     |

| Low Level Input Voltage *1, *4      | VıL                  | -0.3                  | $V_{DD} \times 0.2$                   | V     |

| Ambient Temperature                 | TA                   | 0                     | +70                                   | °C    |

<sup>\*1 :</sup> All voltages are referenced to Vss.

WARNING: The recommended operating conditions are required in order to ensure the normal operation of the semiconductor device. All of the device's electrical characteristics are warranted when the device is operated within these ranges.

Always use semiconductor devices within their recommended operating condition ranges. Operation outside these ranges may adversely affect reliability and could result in device failure.

No warranty is made with respect to uses, operating conditions, or combinations not represented on the data sheet. Users considering application outside the listed conditions are advised to contact their FUJITSU representatives beforehand.

<sup>\*2 :</sup> This device supports three voltage ranges, V<sub>DD</sub> (31), V<sub>DD</sub> (27), and V<sub>DD</sub> (23) on identical device. V<sub>DD</sub> range is divided into three ranges on the table due to V<sub>IH</sub> varied according to V<sub>DD</sub> supply voltage.

<sup>\*3 :</sup> Overshoot spec. (ViH (Max) = VDD + 1.0 V, pulse width  $\leq 5.0 ns$ )

<sup>\*4 :</sup> Undershoot spec. ( $V_{IL (Min)} = -1.0 \text{ V}$ , pulse width  $\leq 5.0 \text{ ns}$ )

## **■ PIN CAPACITANCE**

$(f = 1.0 \text{ MHz}, T_A = +25 \text{ }^{\circ}\text{C})$

| Parameter                     | Symbol            | Conditions            |     | Value |     | Unit  |

|-------------------------------|-------------------|-----------------------|-----|-------|-----|-------|

| raiailletei                   | Symbol Conditions |                       | Min | Тур   | Max | Offic |

| Address Input Capacitance     | C <sub>IN1</sub>  | V <sub>IN</sub> = 0 V | _   | _     | 5   | pF    |

| Control Input Capacitance     | C <sub>IN2</sub>  | V <sub>IN</sub> = 0 V | _   | _     | 5   | pF    |

| Data Input/Output Capacitance | Сю                | Vio = 0 V             | _   | _     | 8   | pF    |

## **■ DC CHARACTERISTICS**

| Parameter                          | Symbol              | Conditions -                                                                                                                                                                                                                                                  |                                                                                                | Val  | lue  | Unit |

|------------------------------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------|------|------|------|

| Parameter                          | Symbol              |                                                                                                                                                                                                                                                               |                                                                                                | Min  | Max  | Unit |

| Input Leakage Current              | lu                  | $V_{SS} \leq V_{IN} \leq V_{DD}$                                                                                                                                                                                                                              |                                                                                                | -1.0 | +1.0 | μΑ   |

| Output Leakage Current             | ILO                 | Vss ≤ Vouт ≤ Vdd, Output Di                                                                                                                                                                                                                                   | sable                                                                                          | -1.0 | +1.0 | μΑ   |

|                                    | V <sub>OH(31)</sub> | $V_{DD} = V_{DD(31)}$ Min, $I_{OH} = -0.5$                                                                                                                                                                                                                    | mA                                                                                             | 2.5  | _    | V    |

| Output High Voltage Level          | V <sub>OH(27)</sub> | $V_{DD} = V_{DD(27)}$ Min, $I_{OH} = -0.5$                                                                                                                                                                                                                    | mA                                                                                             | 2.2  | _    | V    |

|                                    | V <sub>OH(23)</sub> | $V_{DD} = V_{DD(23)}$ Min, $I_{OH} = -0.5$                                                                                                                                                                                                                    | mA                                                                                             | 1.8  | _    | V    |

| Output Low Voltage Level           | Vol                 | IoL = 1 mA                                                                                                                                                                                                                                                    |                                                                                                | _    | 0.4  | V    |

| V <sub>DD</sub> Power Down Current | IDDP                | $V_{DD} = V_{DD}$ Max, $V_{IN} = V_{IH}$ or $V_{IL}$ , $CE2 \le 0.2$ $V$                                                                                                                                                                                      |                                                                                                | _    | 10   | μΑ   |

|                                    | 1                   | $V_{DD} = V_{DD(31)}$ Max, $V_{IN} = V_{IH}$ or $V_{IL}$ , $\overline{CE1} = CE2 = V_{IH}$                                                                                                                                                                    |                                                                                                | _    | 2.0  | A    |

|                                    | Idds                | $V_{DD} = V_{DD(27, 23)} \text{ Max, } V_{IN} = V_{IN}$<br>$\overline{CE}1 = CE2 = V_{IH}$                                                                                                                                                                    | $V_{DD} = V_{DD(27, 23)}$ Max, $V_{IN} = V_{IH}$ or $V_{IL}$ , $\overline{CE1} = CE2 = V_{IH}$ |      | 1.0  | · mA |

| V <sub>DD</sub> Standby Current    | lana.               | $\begin{aligned} &V_{DD} = V_{DD(31)} \text{ Max,} \\ &V_{IN} \leq 0.2 \text{ V or } V_{IN} \geq V_{DD} - 0. \\ &\overline{CE}1 = CE2 \geq V_{DD} - 0.2 \text{ V} \end{aligned}$                                                                              | $V_{IN} \le 0.2 \text{ V or } V_{IN} \ge V_{DD} - 0.2 \text{ V},$                              |      | 150  |      |

|                                    | IDDS1               | $\begin{split} & V_{\text{DD}} = V_{\text{DD}(27,\ 23)} \ \text{Max}, \\ & V_{\text{IN}} \leq 0.2 \ \text{V or} \ V_{\text{IN}} \geq V_{\text{DD}} - 0.2 \ \text{V}, \\ & \overline{\text{CE}1} = \text{CE}2 \geq V_{\text{DD}} - 0.2 \ \text{V} \end{split}$ |                                                                                                | _    | 100  | μΑ   |

| V <sub>DD</sub> Active Current     | DDA1                | V <sub>DD</sub> = V <sub>DD</sub> Max,<br>V <sub>IN</sub> = V <sub>IH</sub> or V <sub>IL</sub> ,                                                                                                                                                              | trc / twc = Min                                                                                | _    | 20   | mA   |

| Active Current                     | IDDA1               | $\overline{\text{CE}}1 = \text{V}_{\text{IL}} \text{ and CE2} = \text{V}_{\text{IH}},$ $\text{Iout} = 0 \text{ mA}$                                                                                                                                           | $t_{RC} / t_{WC} = 1 \mu s$                                                                    | —    | 3.0  | IIIA |

Notes: • All voltages are referenced to Vss.

- DC Characteristics are measured after following POWER-UP timing.

- lout depends on the output load conditions.

#### **■ AC CHARACTERISTICS**

## (1) Read Operation

| Parameter                       | Comple of     | Value |      | l lm:4 | Notes  |

|---------------------------------|---------------|-------|------|--------|--------|

| Parameter                       | Symbol        | Min   | Max  | Unit   | Notes  |

| Read Cycle Time                 | <b>t</b> RC   | 70    | 1000 | ns     | *1, *2 |

| CE1 Access Time                 | <b>t</b> ce   | _     | 60   | ns     | *3     |

| OE Access Time                  | toe           | _     | 40   | ns     | *3     |

| Address Access Time             | <b>t</b> AA   | _     | 60   | ns     | *3, *5 |

| LB, UB Access Time              | <b>t</b> BA   | _     | 30   | ns     | *3     |

| Output Data Hold Time           | tон           | 5     | _    | ns     | *3     |

| CE1 Low to Output Low-Z         | tclz          | 5     | _    | ns     | *4     |

| OE Low to Output Low-Z          | tolz          | 0     | _    | ns     | *4     |

| LB, UB Low to Output Low-Z      | <b>t</b> BLZ  | 0     | _    | ns     | *4     |

| CE1 High to Output High-Z       | tснz          | _     | 20   | ns     | *3     |

| OE High to Output High-Z        | tонz          | _     | 20   | ns     | *3     |

| LB, UB High to Output Low-Z     | tвнz          | _     | 20   | ns     | *3     |

| Address Setup Time to CE1 Low   | tasc          | -5    | _    | ns     |        |

| Address Setup Time to OE Low    | taso          | 10    | _    | ns     |        |

| Address Invalid Time            | tax           | _     | 10   | ns     | *5     |

| Address Hold Time from CE1 High | <b>t</b> chah | -5    | _    | ns     | *6     |

| Address Hold Time from OE High  | tонан         | -5    | _    | ns     |        |

| WE High to OE Low Time for Read | <b>t</b> whoL | 10    | 1000 | ns     | *7     |

| CE1 High Pulse Width            | <b>t</b> cp   | 10    | _    | ns     |        |

<sup>\*1 :</sup> Maximum value is applicable if  $\overline{CE}1$  is kept at Low without any address change.

<sup>\*2 :</sup> Address should not be changed within minimum tRC.

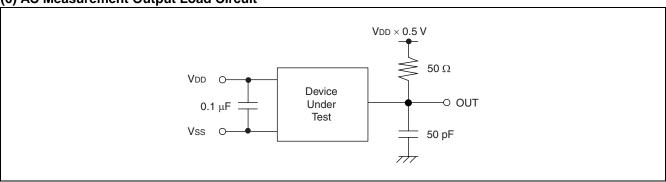

<sup>\*3 :</sup> The output load 50 pF with 50  $\Omega$  termination to V<sub>DD</sub>  $\times$  0.5 V.

<sup>\*4 :</sup> The output load 5 pF without any other load.

<sup>\*5 :</sup> Applicable when  $\overline{CE}1$  is kept at Low.

<sup>\*6 :</sup> trc (Min) must be satisfied.

<sup>\*7:</sup> If the actual value of twhoL is shorter than specified minimum value, the actual tAA of following Read may become longer by the amount of subtracting actual value from specified minimum value.

#### (2) Write Operation

| Doromotor                               | Symbol                 | Va  | alue | l lni4 | Notes  |

|-----------------------------------------|------------------------|-----|------|--------|--------|

| Parameter                               | Symbol                 | Min | Max  | Unit   | Notes  |

| Write Cycle Time                        | twc                    | 70  | 1000 | ns     | *1, *2 |

| Address Setup Time                      | tas                    | 0   | _    | ns     | *2     |

| CE1 Write Pulse Width                   | tcw                    | 45  | _    | ns     | *3     |

| WE Write Pulse Width                    | <b>t</b> wp            | 45  | _    | ns     | *3     |

| LB, UB Write Pulse Width                | <b>t</b> <sub>BW</sub> | 45  | _    | ns     | *3     |

| LB, UB Byte Mask Setup Time             | tss                    | -5  | _    | ns     | *4     |

| LB, UB Byte Mask Hold Time              | tвн                    | -5  | _    | ns     | *5     |

| Write Recovery Time                     | <b>t</b> wr            | 0   | _    | ns     | *6     |

| CE1 High Pulse Width                    | tcp                    | 10  | _    | ns     |        |

| WE High Pulse Width                     | twhp                   | 10  | 1000 | ns     |        |

| LB, UB High Pulse Width                 | <b>t</b> внр           | 10  | 1000 | ns     |        |

| Data Setup Time                         | tos                    | 15  | _    | ns     |        |

| Data Hold Time                          | tон                    | 0   | _    | ns     |        |

| OE High to Address Setup Time for Write | toes                   | 0   | _    | ns     | *8     |

| OE High to CE1 Low Setup Time for Write | <b>t</b> oncl          | -5  | _    | ns     | *7     |

| LB and UB Write Pulse Overlap           | <b>t</b> bwo           | 30  |      | ns     |        |

- \*1 : Maximum value is applicable if  $\overline{CE}1$  is kept at Low without any address change.

- \*2 : Minimum value must be equal or greater than the sum of write pulse width (tcw, twp or tbw) and write recovery time (twr) .

- \*3 : Write pulse width is defined from High to Low transition of  $\overline{CE}1$ ,  $\overline{WE}$ ,  $\overline{LB}$  or  $\overline{UB}$ , whichever occurs last.

- \*4 : Applicable for byte mask only. Byte mask setup time is defined to the High to Low transition of  $\overline{\text{CE}}1$  or  $\overline{\text{WE}}$  whichever occurs last.

- \*5 : Applicable for byte mask only. Byte mask hold time is defined from the Low to High transition of  $\overline{\text{CE}}1$  or  $\overline{\text{WE}}$  whichever occurs first.

- \*6 : Write recovery time is defined from Low to High transition of CE1, WE, LB or UB, whichever occurs first.

- \*7 : If  $\overline{OE}$  is Low after minimum toHCL, read cycle is initiated. In other words,  $\overline{OE}$  must be brought to High within 5 ns after  $\overline{CE}1$  is brought to Low.

- \*8 : If  $\overline{OE}$  is Low after new address input, read cycle is initiated. In other words,  $\overline{OE}$  must be brought to High at the same time or before new address valid.

Note: AC Characteristics are measured after following POWER-UP timing.

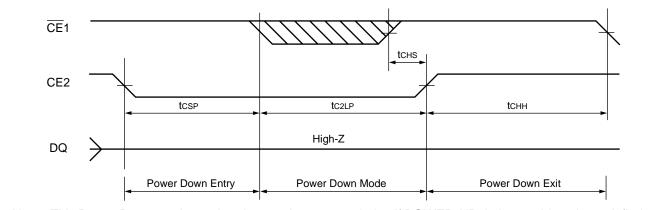

#### (3) Power Down Parameters

| Parameter                                                    | Symbol        | Va  | lue | Unit | Note |

|--------------------------------------------------------------|---------------|-----|-----|------|------|

| Farameter                                                    | Symbol        | Min | Max | Onit | Note |

| CE2 Low Setup Time for Power Down Entry                      | tcsp          | 10  | _   | ns   |      |

| CE2 Low Hold Time after Power Down Entry                     | <b>t</b> C2LP | 80  | _   | ns   |      |

| CE1 High Hold Time following CE2 High after Power Down Exit  | tснн          | 300 | _   | μs   | *    |

| CE1 High Setup Time following CE2 High after Power Down Exit | tснs          | 0   | _   | ns   |      |

<sup>\*:</sup> Applicable also to power-up.

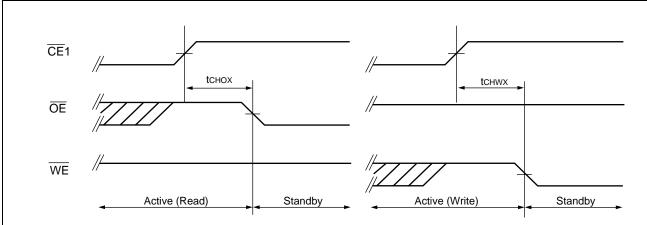

#### (4) Other Timing Parameters

| Parameter                                            | Cumbal        | Va  | Unit | Note |      |

|------------------------------------------------------|---------------|-----|------|------|------|

| Parameter                                            | Symbol        | Min | Max  | Unit | Note |

| CE1 High to OE Invalid Time for Standby Entry        | <b>t</b> chox | 10  | _    | ns   |      |

| CE1 High to WE Invalid Time for Standby Entry        | <b>t</b> chwx | 10  | _    | ns   | *1   |

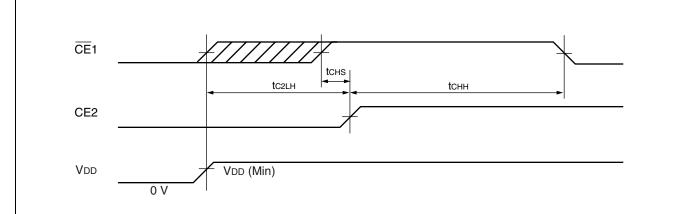

| CE2 Low Hold Time after Power-up                     | tc2LH         | 50  | _    | μs   |      |

| CE1 High Hold Time following CE2 High after Power-up | tснн          | 300 | _    | μs   |      |

| Input Transition Time                                | t⊤            | 1   | 25   | ns   | *2   |

<sup>\*1:</sup> Some data might be written into any address location if tchwx (Min) is not satisfied.

## (5) AC Test Conditions

| Parameter                      | Symbol           | Conditions                                    | Measured Value      | Unit | Note |

|--------------------------------|------------------|-----------------------------------------------|---------------------|------|------|

| Input High Level               | VIH              | _                                             | $V_{DD} \times 0.8$ | V    |      |

| Input Low level                | VIL              | _                                             | $V_{DD} \times 0.2$ | V    |      |

| Input Timing Measurement Level | V <sub>REF</sub> | _                                             | $V_{DD} \times 0.5$ | V    |      |

| Input Transition Time          | t⊤               | Between V <sub>I</sub> L and V <sub>I</sub> H | 5                   | ns   |      |

#### (6) AC Measurement Output Load Circuit

<sup>\*2:</sup> The Input Transition Time (t₁) at AC testing is 5 ns as shown in below. If actual t₁ is longer than 5 ns, it may violate AC specifications of some timing parameters.

## **■ TIMING DIAGRAM**

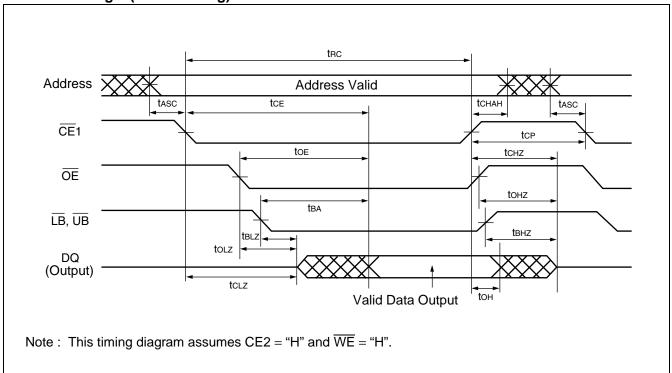

## 1. READ Timing 1 (Basic Timing)

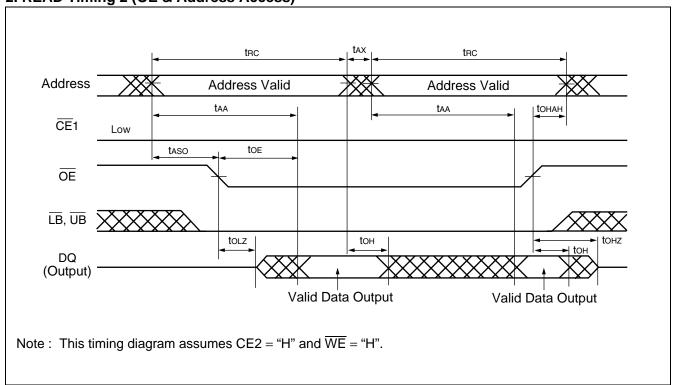

# 2. READ Timing 2 (OE & Address Access)

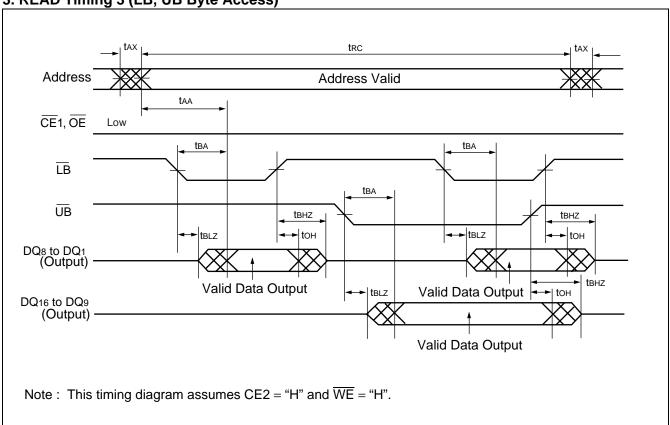

# 3. READ Timing 3 (LB, UB Byte Access)

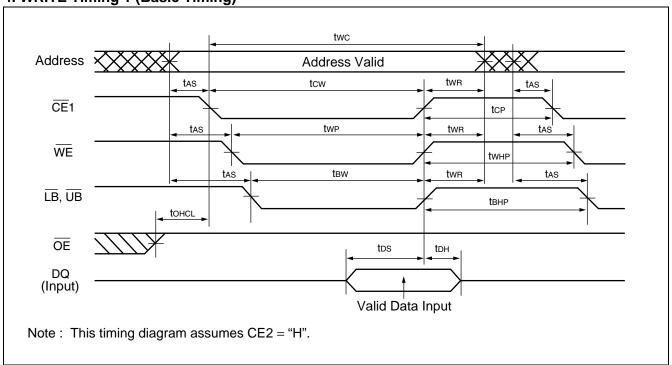

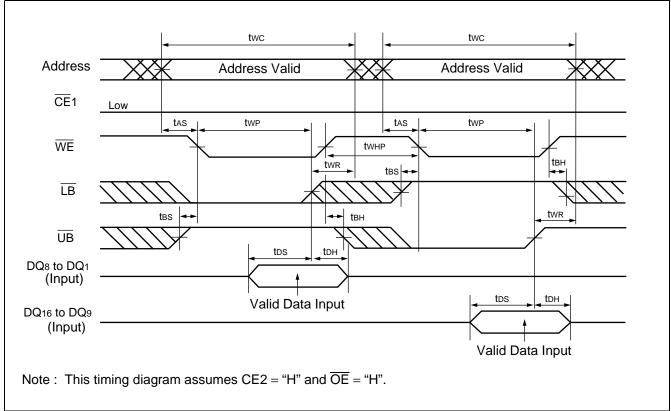

## 4. WRITE Timing 1 (Basic Timing)

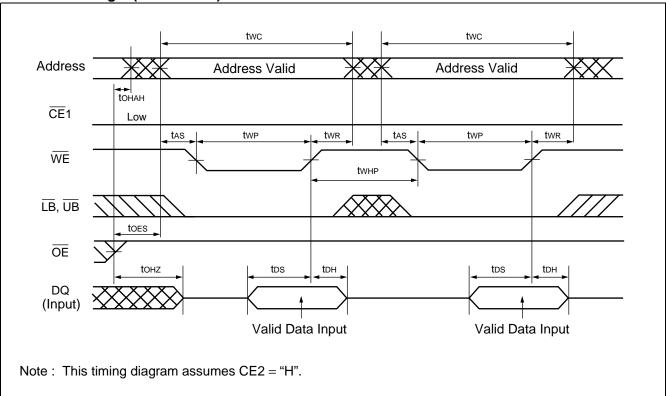

# 5. WRITE Timing 2 (WE Control)

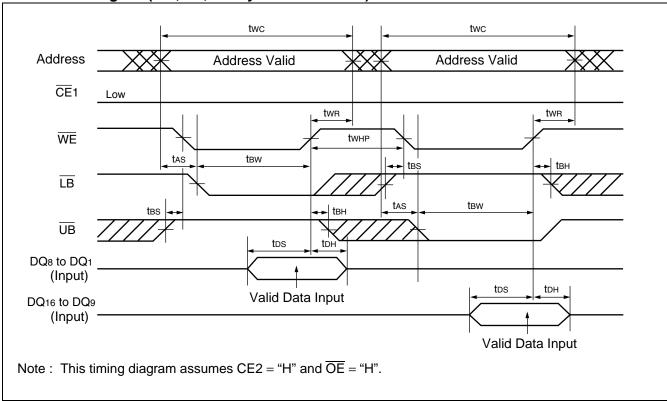

## 6. WRITE Timing 3-1 (WE, LB, UB Byte Write Control)

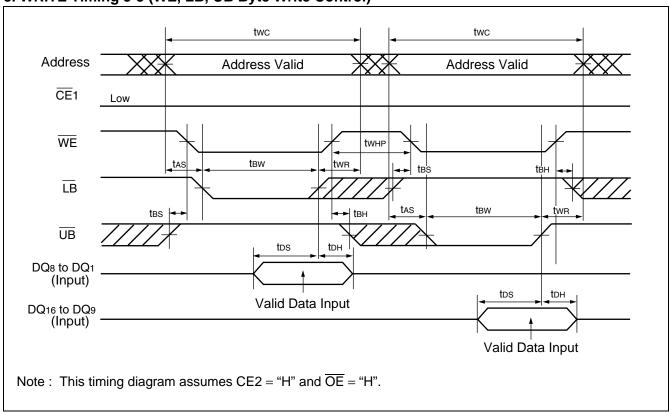

# 7. WRITE Timing 3-2 (WE, LB, UB Byte Write Control)

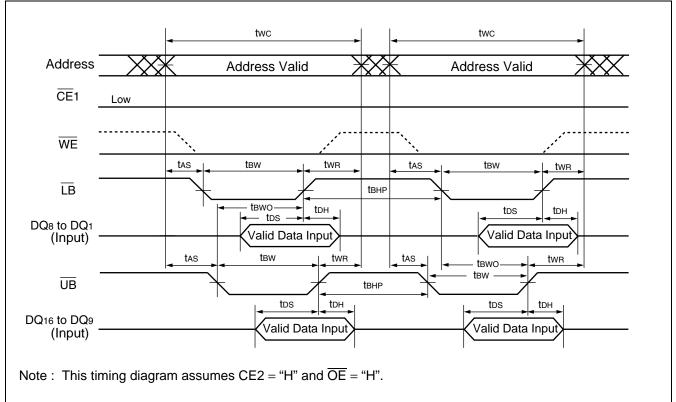

## 8. WRITE Timing 3-3 (WE, LB, UB Byte Write Control)

# 9. WRITE Timing 3-4 (WE, LB, UB Byte Write Control)

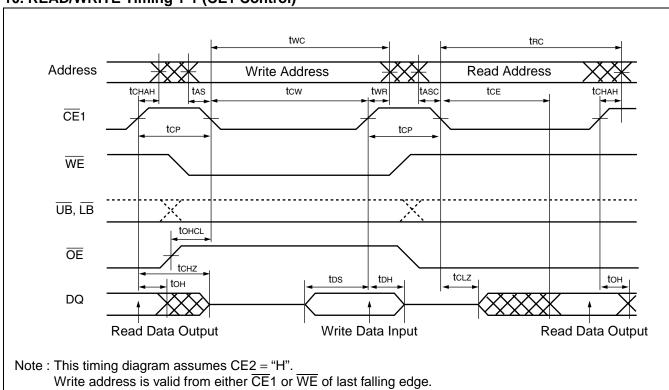

## 10. READ/WRITE Timing 1-1 (CE1 Control)

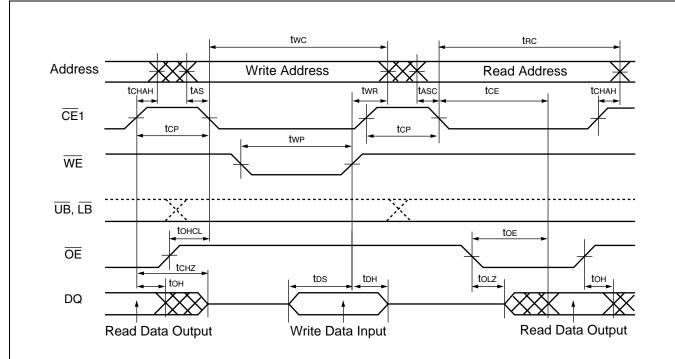

# 11. READ/WRITE Timing 1-2 (CE1, WE, OE Control)

Note: This timing diagram assumes CE2 = "H".

OE can be fixed Low during write operation if it is CE1 controlled write at Read-Write-Read sequence.

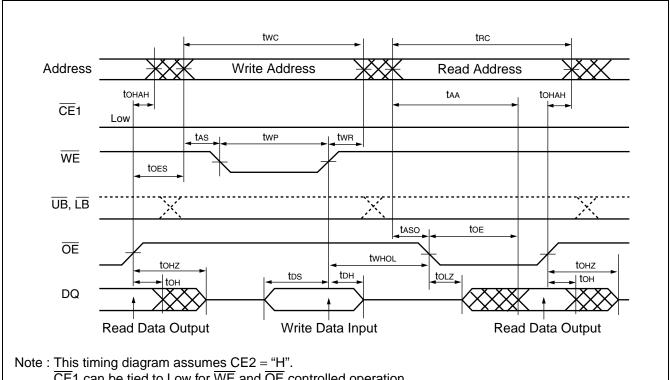

# 12. READ/WRITE Timing 2 (OE, WE Control)

CE1 can be tied to Low for WE and OE controlled operation.

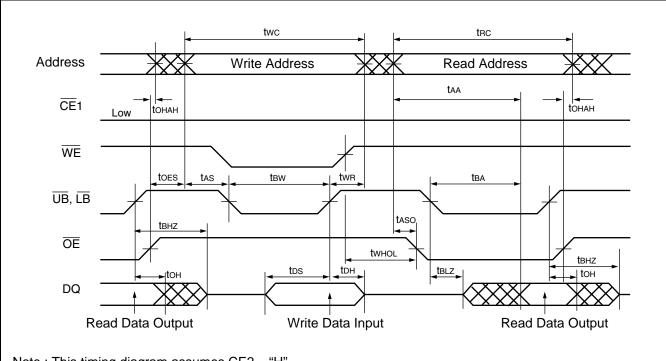

# 13. READ/WRITE Timing 3 (OE, WE, LB, UB Control)

Note: This timing diagram assumes CE2 = "H".

$\overline{\text{CE}}$ 1 can be tied to Low for  $\overline{\text{WE}}$  and  $\overline{\text{OE}}$  controlled operation.

## 14. POWER-UP Timing 1

Note: tc2LH specifies after VDD reaches specified minimum level.

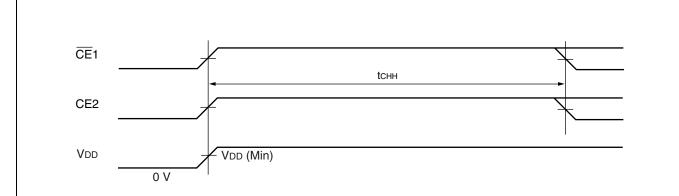

## 15. POWER-UP Timing 2

Note: tchh specifies after VDD reaches specified minimum level and applicable to both  $\overline{\text{CE}}1$  and CE2. If transition time of VDD (from 0 V to VDD Min) is longer than 100 ms, POWER-UP Timing#1 must be applied.

## 16. POWER DOWN Entry and Exit Timing

Note: This Power Down mode can be also used as a reset timing if POWER-UP timing could not be satisfied.

## 17. Standby Entry Timing after Read or Write

Note: Both tchox and tchwx define the earliest entry timing for Standby mode.

If either of timing is not satisfied, it takes trc (Min) period for Standby mode from  $\overline{CE}1$  Low to High transition.

## **■ BONDING PAD INFORMATION**

Please contact local FUJITSU representative for pad layout and pad coordinate information.

## **■** ORDERING INFORMATION

| Part No.           | Shipping Form/Package | Remarks                                      |

|--------------------|-----------------------|----------------------------------------------|

| MB82D01181E-60LWT  | Wafer                 |                                              |

| MB82D01181E-60LPBN |                       | SRAM compatible FBGA package tce = 60 ns Max |

#### **■ PACKAGE DIMENSION**

# **FUJITSU LIMITED**

All Rights Reserved.

The contents of this document are subject to change without notice. Customers are advised to consult with FUJITSU sales representatives before ordering.

The information, such as descriptions of function and application circuit examples, in this document are presented solely for the purpose of reference to show examples of operations and uses of Fujitsu semiconductor device; Fujitsu does not warrant proper operation of the device with respect to use based on such information. When you develop equipment incorporating the device based on such information, you must assume any responsibility arising out of such use of the information. Fujitsu assumes no liability for any damages whatsoever arising out of the use of the information.

Any information in this document, including descriptions of function and schematic diagrams, shall not be construed as license of the use or exercise of any intellectual property right, such as patent right or copyright, or any other right of Fujitsu or any third party or does Fujitsu warrant non-infringement of any third-party's intellectual property right or other right by using such information. Fujitsu assumes no liability for any infringement of the intellectual property rights or other rights of third parties which would result from the use of information contained herein.

The products described in this document are designed, developed and manufactured as contemplated for general use, including without limitation, ordinary industrial use, general office use, personal use, and household use, but are not designed, developed and manufactured as contemplated (1) for use accompanying fatal risks or dangers that, unless extremely high safety is secured, could have a serious effect to the public, and could lead directly to death, personal injury, severe physical damage or other loss (i.e., nuclear reaction control in nuclear facility, aircraft flight control, air traffic control, mass transport control, medical life support system, missile launch control in weapon system), or (2) for use requiring extremely high reliability (i.e., submersible repeater and artificial satellite).

Please note that Fujitsu will not be liable against you and/or any third party for any claims or damages arising in connection with above-mentioned uses of the products.

Any semiconductor devices have an inherent chance of failure. You must protect against injury, damage or loss from such failures by incorporating safety design measures into your facility and equipment such as redundancy, fire protection, and prevention of over-current levels and other abnormal operating conditions.

If any products described in this document represent goods or technologies subject to certain restrictions on export under the Foreign Exchange and Foreign Trade Law of Japan, the prior authorization by Japanese government will be required for export of those products from Japan.

Edited Business Promotion Dept.