## ANALOG DEVICES

# Dual BiFET Op Amp

**Precision, Low Cost**

AD642

### **FEATURES**

Matched Offset Voltage Matched Offset Voltage Over Temperature Matched Bias Current Crosstalk: -124 dB @ 1 kHz Low Bias Current: 35 pA max Warmed Up Low Offset Voltage: 500  $\mu$ V max Low Input Voltage Noise: 2  $\mu$ V p-p High Open Loop Gain Low Quiescent Current: 2.8 mA max Low Total Harmonic Distortion Standard Dual Amplifier Pin Out Available in Hermetic Metal Can Package and Chip Form MIL-STD-883B Processing Available Single Version Available: AD542

#### AMPLIFIER NO. 1 OUTPUT OUTPUT INVERTING INVERTING OUTPUT TOP VIEW ONNINVERTING OUTPUT OUTPUT

PIN CONFIGURATION

### **PRODUCT DESCRIPTION**

The AD642 is a pair of matched high speed monolithic BiFET operational amplifier fabricated with the most advanced bipolar, JFET and laser trimming technologies. The AD642 offers matched bias currents that are significantly lower than currently available monolithic dual FET input operational amplifiers: 35 pA max matched to 25 pA for the AD642K and L; 75 pA max, matched to 35 pA for the AD642J and S. In addition, the offset voltage is laser trimmed to less than 0.5 mV and matched to 0.25 mV for the AD642L, 1.0 mV and matched to 0.5 mV for the AD642K, utilizing Analog's laser-wafer trimming (LWT) process.

The tight matching and temperature tracking between the operational amplifiers is achieved by ion-implanted JFETs and laser-wafer trimming. Ion-implantation permits the fabrication of precision, matched JFETs on a monolithic bipolar chip. The optimizes the process to product matched bias currents which have lower initial bias currents than other popular BiFET op amps. Laser-wafer trimming each amplifier's input offset voltage assures tight initial match and combined with superior IC processing guarantees offset voltage tracking over the temperature range.

The AD642 is recommended for applications in which excellent ac and dc performance is required. The matched amplifiers provide a low-cost solution for true instrumentation amplifiers, log ratio amplifiers, and output amplifiers for four quadrant multiplying D/A converters such as the AD7541. The AD642 is available in four versions: the "J", "K" and "L," all specified over the 0°C to +70°C temperature range and one version, "S," over the -55°C to +125°C extended operating temperature range. All devices are packaged in the hermetically-sealed, TO-99 metal can or available in chip form.

### **PRODUCT HIGHLIGHTS**

- 1. The AD642 has tight matching specifications to ensure high performance, eliminating the need to match individual devices.

- 2. Analog Devices, unlike some manufacturers, specifies each device for the maximum bias current at either input in the warmed-up condition, thus assuring the user that the AD642 will meet its published specifications in actual use.

- Laser-wafer-trimming reduces offset voltage to as low as 0.5 mV max and matched side to side to 0.25 mV (AD642L), thus eliminating the need for external nulling.

- 4. Low voltage noise (2  $\mu$ V, p-p), and high open loop gain enhance the AD642's performance as a precision op amp.

- 5. The standard dual amplifier pin out allows the AD642 to replace lower performance duals without redesign.

- 6. The AD642 is available in chip form.

#### REV.0

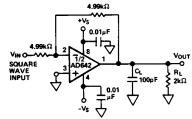

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 Fax: 617/326-8703

## **AD642—SPECIFICATIONS** (@ + 25°C, and $V_s = \pm 15 V dc$ )

| Model                                                                                                                                                                                                                                                                         | Min                       | AD642J<br>Typ                         | Max               | Min                | AD642I<br>Typ                         | K<br>Max          | Min              | AD642<br>Typ                          | L<br>Max          | Min                | AD6429<br>Typ                         | S<br>Max          | Unit                                                                                                                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|---------------------------------------|-------------------|--------------------|---------------------------------------|-------------------|------------------|---------------------------------------|-------------------|--------------------|---------------------------------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------|

| $\begin{array}{l} \text{OPEN LOOP GAIN} \\ V_o = \pm 10 \text{ V},  R_L \geq 2  k\Omega \\ T_{\text{MIN}} \text{ to } T_{\text{MAX}},  R_L = 2  k\Omega \end{array}$                                                                                                          | <b>100,000</b><br>100,000 |                                       |                   | 250,000<br>250,000 |                                       |                   | 250,00<br>250,00 |                                       |                   | 250,000<br>100,000 |                                       |                   | V/V<br>V/V                                                                                                                          |

| $\begin{array}{l} \textbf{OUTPUT CHARACTERISTICS}\\ \textbf{Voltage (@, R_L = 2 k\Omega, T_{MIN} to T_{MAX} \\ \textbf{Voltage (@, R_L = 10 k\Omega, T_{MIN} to T_{MAX} \\ \textbf{Short Circuit Current} \end{array}$                                                        | ±10<br>±12                | ±12<br>±13<br>25                      |                   | ±10<br>±12         | ±12<br>±13<br>25                      |                   | ±10<br>±12       | ±12<br>±13<br>25                      |                   | ±10<br>±12         | ±12<br>±13<br>25                      |                   | V<br>V<br>mA                                                                                                                        |

| FREQUENCY RESPONSE<br>Unity Gain Small Signal<br>Full Power Response<br>Slew Rate, Unity Gain                                                                                                                                                                                 | 2.0                       | 1.0<br>50<br>3.0                      |                   | 2.0                | 1.0<br>50<br>3.0                      |                   | 2.0              | 1.0<br>50<br>3.0                      |                   | 2.0                | 1.0<br>50<br>3.0                      |                   | MHz<br>kHz<br>V/µs                                                                                                                  |

| $\label{eq:constraint} \begin{array}{l} \text{INPUT OFFSET VOLTAGE}^1 \\ \text{Initial Offset} \\ \text{Input Offset Voltage } T_{\text{MIN}} \text{ to } T_{\text{MAX}} \\ \text{Input Offset Voltage vs. Supply,} \\ T_{\text{MIN}} \text{ to } T_{\text{MAX}} \end{array}$ |                           |                                       | 2.0<br>3.5<br>200 |                    |                                       | 1.0<br>2.0<br>100 |                  |                                       | 0.5<br>1.0<br>100 |                    |                                       | 1.0<br>3.5<br>100 | mV<br>mV<br>μV/V                                                                                                                    |

| INPUT BIAS CURRENT <sup>2</sup><br>Either Input<br>Offset Current                                                                                                                                                                                                             |                           | 10<br>5                               | 75                |                    | 10<br>2                               | 35                |                  | 10<br>2                               | 35                |                    | 10<br>2                               | 35                | pА                                                                                                                                  |

| MATCHING CHARACTERISTICS <sup>3</sup><br>Input Offset Voltage<br>Input Offset Voltage $T_{MIN}$ to $T_{MAX}$<br>Input Bias Current<br>Crosstalk                                                                                                                               |                           | -124                                  | 1.0<br>3.5<br>35  |                    | -124                                  | 0.5<br>2.0<br>25  |                  | -124                                  | 0.25<br>1.0<br>25 |                    | -124                                  | 0.5<br>3.5<br>35  | mV<br>mV<br>pA<br>dB                                                                                                                |

| INPUT IMPEDANCE<br>Differential<br>Common Mode                                                                                                                                                                                                                                |                           | $\frac{10^{12}}{10^{12}} \frac{6}{6}$ |                   |                    | $\frac{10^{12}}{10^{12}} \frac{6}{6}$ |                   |                  | $\frac{10^{12}}{10^{12}} \frac{6}{6}$ |                   |                    | $\frac{10^{12}}{10^{12}} \frac{6}{6}$ |                   | MΩ  pF<br>MΩ  pF                                                                                                                    |

| INPUT VOLTAGE RANGE<br>Differential <sup>4</sup><br>Common Mode<br>Common-Mode Rejection                                                                                                                                                                                      | ±10<br>76                 | ±20<br>±12                            |                   | ±10<br>80          | ±20<br>±12                            |                   | ±10<br>80        | ±20<br>±12                            |                   | ±10<br>80          | ±20<br>±12                            |                   | V<br>V<br>dB                                                                                                                        |

| INPUT NOISE<br>Voltage 0.1 Hz to 10 Hz<br>f = 10 Hz<br>f = 100 Hz<br>f = 1 kHz<br>f = 10 kHz                                                                                                                                                                                  |                           | 2<br>70<br>45<br>30<br>25             |                   |                    | 2<br>70<br>45<br>30<br>25             |                   |                  | 2<br>70<br>45<br>30<br>25             |                   |                    | 2<br>70<br>45<br>30<br>25             |                   | $ \begin{array}{c} \mu V \ p\text{-}p \\ nV/\sqrt{Hz} \\ nV/\sqrt{Hz} \\ nV/\sqrt{Hz} \\ nV/\sqrt{Hz} \\ nV/\sqrt{Hz} \end{array} $ |

| POWER SUPPLY<br>Rated Performance<br>Operating<br>Quiescent Current                                                                                                                                                                                                           | ±5                        | ±15                                   | ±18<br>2.8        | ±5                 | ±15                                   | ±15<br>2.8        | ±5               | ±15                                   | ±15<br>2.8        | ±5                 | ±15                                   | ±15<br>2.8        | V<br>V<br>mA                                                                                                                        |

| TRANSISTOR COUNT                                                                                                                                                                                                                                                              |                           | 58                                    |                   |                    | 58                                    |                   |                  | 58                                    |                   |                    | 58                                    |                   |                                                                                                                                     |

| PACKAGE OPTION<br>TO-99 Style (H-08B)                                                                                                                                                                                                                                         |                           | AD642JI                               | Н                 |                    | AD6421                                | KH                |                  | AD642                                 | LH                |                    | AD6423                                | SH                |                                                                                                                                     |

NOTES

<sup>1</sup>Input Offset Voltage specifications are guaranteed after 5 minutes of operation at  $T_A = +25^{\circ}C$ .

<sup>2</sup>Bias Current specifications are guaranteed at maximum at either input after 5 minutes of operation at  $T_A = +25^{\circ}$ C. For higher temperatures, the current doublers every 10°C.

<sup>3</sup>Matching is defined as ther difference between parameters of the two amplifiers.

<sup>4</sup>Defined as the maximum safe voltage between inputs, such that neither exceeds  $\pm 10$  V from ground.

Specifications subject to change without notice.

Specifications shown in **boldface** are tested on all production units at final electrical test. Results from those tests are used to calculate outgoing quality levels. All min and max specifications are guaranteed, although only those shown in boldface are tested on all production units.

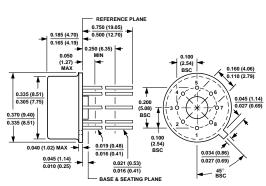

### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

**TO-99**

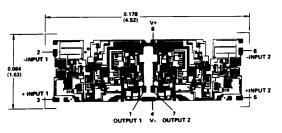

### METALIZATION PHOTOGRAPHIC

Contact factory for latest dimensions. Dimensions shown in inches and (mm).

Downloaded from Elcodis.com electronic components distributor

### AD642

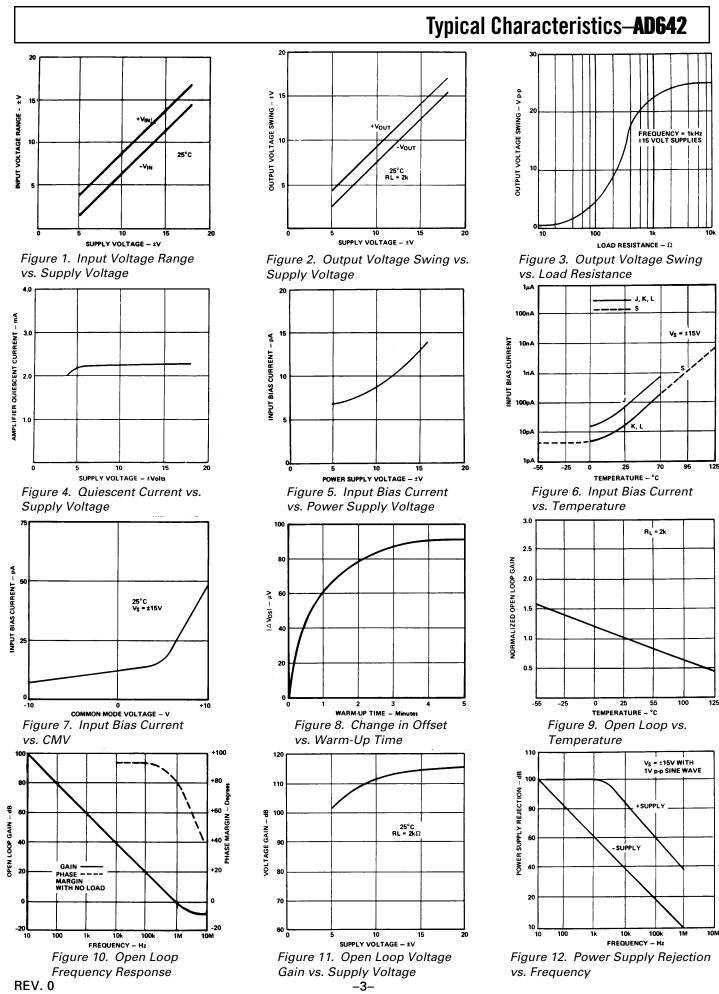

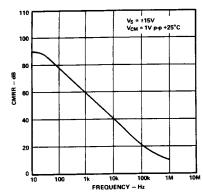

Figure 13. Common-Mode Rejection Ratio vs. Frequency

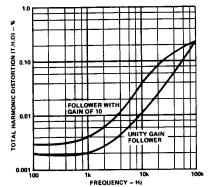

Figure 16. Total Harmonic Distortion vs. Frequency

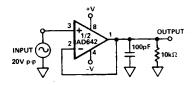

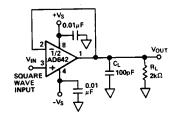

a. Unity Gain Follower

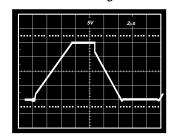

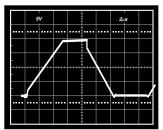

Figure 21a. Unity Gain Follower Pulse Response (Large Signal)

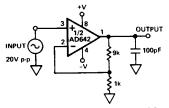

Figure 22a. Unity Gain Inverter

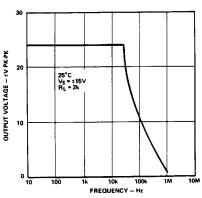

Figure 14. Large Signal Frequency Response

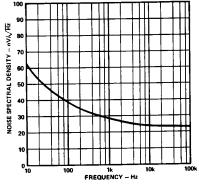

Figure 17. Input Noise Voltage Spectral Density

Follower b. Follower with Gain = 10 Figure 19. T. H. D. Test Circuits

Figure 21b. Unity Gain Follower Pulse Response (Small Signal)

Figure 22b. Unity Gain Inverter Pulse Response (Large Signal)

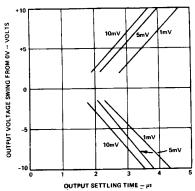

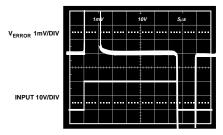

Figure 15. Output Swing and Error vs. Output Settling Time (Circuit of Figure 23)

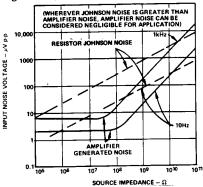

Figure 18. Total Noise vs. Source Impedance

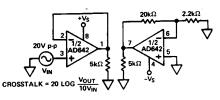

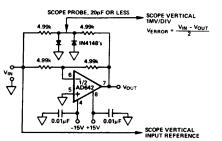

Figure 20. Crosstalk Test Circuit

Figure 21c. Unity Gain Follower

Figure 22c. Unity Gain Inverter Pulse Response (Small Signal)

### AD642

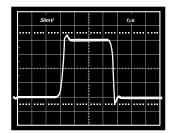

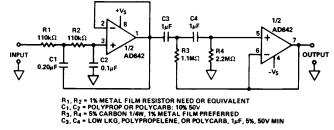

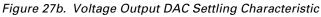

Figure 23. Settling Time Test Circuit

Fast settling time (8  $\mu$ s to 0.01% for 20 V p-p step), low power and low offset voltage make the AD642 an excellent choice for use as an output amplifier for current output D/A converters such as the AD7541.

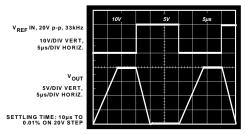

Figure 24. Settling Characteristic Detail

The upper trace of the oscilloscope photograph of Figure 24 shows the settling characteristic of the AD642. The lower trace represents the input to Figure 23. The AD642 has been designed for fast settling to 0.01%, however, feedback components, circuit layout and circuit design must be carefully considered to obtain optimum settling time.

Figure 25. 0.1 Hz to 10 Hz 2nd Order Bandpass Filter, Maximally Flat

The low frequency (1/f) noise has a power spectrum that is inversely proportional to frequency. Typically this noise is not important above 10 Hz, but it can be important for low frequency-high gain applications.

The low noise characteristic of the AD642 make it ideal for 1/f noise testing circuits. The circuit of Figure 25 is a 0.1 Hz to 10 Hz bandpass filter with second order filter characteristics.

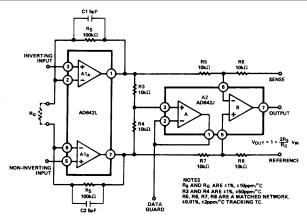

The circuit illustrated in Figure 26 uses two AD642s to construct an instrumentation amplifier with low input current (35 pA max), high linearity and low offset voltage and offset voltage drift. The AD644 may be substituted for increased speed, but the higher open-loop gain of the AD642 maintains better linearity over the gain range of 1 to 1000. Amplifier A1 is an AD642L for low input offset voltage (250  $\mu$ V max) and low input offset voltage drift at high gains because matching and tracking are very important for the balanced input stage. Amplifier A2 serves two nonrelated functions, output amplifier and active data-guard drive, and does not require close matching between sections; thus it may be an AD642J.

Figure 26. Precision FET Input Instrumentation Amplifier

The output impedance of a CMOS DAC varies with the digital word thus changing the noise of the amplifier circuit. This effect will cause a nonlinearity whose magnitude is dependent on the offset voltage of the amplifier. The AD642K with trimmed offset will minimize the effect. The Schottky protection diodes recommended for use with many older CMOS DACs are not required when using the AD642.

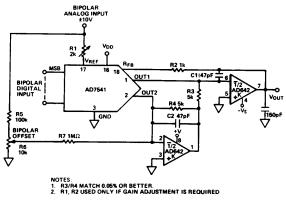

Figure 27a. AD642 Used as DAC Output Amplifier

Figure 27a illustrates the AD7541 12-bit digital-to-analog converter, connected for bipolar operation. Since the digital input can accept bipolar numbers and  $V_{REF}$  can accept a bipolar analog input, the circuit can perform a 4-quadrant multiplication.

The photo above shows the output of the circuit Figure 27a. The upper trace represents the reference input, and the bottom trace shows the output voltage for a digital input of all ones on the DAC. The 47 pF capacitor across the feedback resistor compensates for the DAC output capacitance, and the 150 pF load capacitor serves to minimize output glitches.

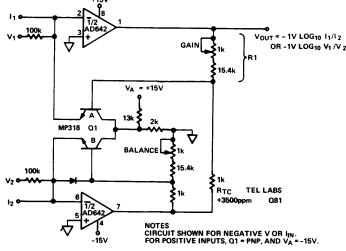

Log amplifiers or log ratio amplifiers are useful in applications requiring compression of wide-range analog input data,

## AD642

linearization of transducers having exponential outputs, and analog computing, ranging from simple translation of natural relationships in log form (e.g., computing absorbance as the logratio of input currents), to the use of logarithms in facilitating analog computation of terms involving arbitrary exponents and multiterm products and ratios.

The picoamp level input current and low offset voltage of the AD642 make it suitable for wide dynamic range log amplifiers. Figure 28 is a schematic of a log ratio circuit employing the AD642 that can achieve less than 1% conformance error over 5 decades of current input, 1 nA to 100  $\mu$ A. For voltage inputs, the dynamic range is typically 50 mV to 10 V for 1% error limited on the low end by the amplifier's input offset voltage.

The conversion between current (or voltage) input and log output is accomplished by the base emitter junctions of the dual transistor Q1. Assuming Q1 has  $\beta$ >100, which is the case for the specified transistor, the base-emitter voltage on side 1 is to a close approximation:

$$V_{BEA} = kT/q \ln I_1/I_{S1}$$

This circuit is arranged to take the difference of the  $V_{BE}$ 's of Q1A and Q1B, thus producing an output voltage proportional to the log of the ratio of the inputs:

$$V_{OUT} = -K(V_{BEA} - V_{BEB}) = -\frac{KkT}{q} (\ln I_1 / I_{S1} - \ln I_2 / I_{S2})$$

$$V_{OUT} = -K kT/q \ln I_1 / I_2$$

The scaling constant, K is set by R1 and  $R_{TC}$  to about 16, to produce 1 V change in output voltage per decade difference in input signals.  $R_{TC}$  is a special resistor with a +3500 ppm/°C temperature coefficient, which makes K inversely proportional to temperature, compensating for the "T" in kT/q. The log-ratio transfer characteristic is therefore independent of temperature.

This particular log ratio circuit is free from the dynamic problems that plague many other log circuits. The -3 dB bandwidth is 50 kHz over the top 3 decades, 100 nA to 100  $\mu$ A, and decreases smoothly at lower input levels. This circuit needs no additional frequency compensation for stable operation from input current sources, such as photodiodes, that may have 100 pF of shunt capacitance. For larger input capacitances a 20 pF integration capacitor around each amplifier will provide a smoother frequency response.

The log ratio amplifier can be readily adjusted for optimum accuracy by following this simple procedure. First, apply V1 =

V2 = -10.00 V and adjust "Balance" for V<sub>OUT</sub> = 0.00 V. Next apply V1 = -10.00 V, V2 = -1.00 V and adjust gain for V<sub>OUT</sub> = +1.00 V. Repeat this procedure until gain and balance readings are within 2 mV of ideal values.

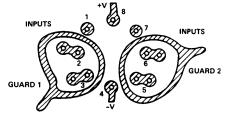

The low input bias current (35 pA) and low noise characteristics of the AD642 make it suitable for electrometer applications such as photo diode preamplifiers and picoampere current-tovoltage converters. The use of guarding techniques in printed circuit board layout and construction is critical in printed circuit board layout and construction is critical for achieving the ultimate in low leakage performance that the AD642 can deliver. The input guarding scheme shown in Figure 29 will minimize leakage as much as possible; the guard ring should be applied to both sides of the board. The guard ring is connected to a low impedance potential at the same level as the inputs. High impedance signal lines should not be extended for any unnecessary length on a printed circuit; to minimize noise and leakage, they must be carried in rigid shielded cables.

Figure 29. Board Layout for Guarding Inputs

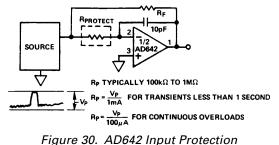

### **INPUT PROTECTION**

The AD642 is guaranteed for a maximum safe input potential equal to the power supply potential. The input stage design also allows differential input voltages of up to  $\pm 0.5$  volts while maintaining the full differential input resistance of  $10^{12} \Omega$ . This makes the AD642 suitable for low speed voltage comparators directly connected to a high impedance source.

Many instrumentation situations, such as flame detectors in gas chromatographs, involve measurement of low level currents from high-voltage sources. In such applications, a sensor fault condition may apply a very high potential to the input of the current-to-voltage converting amplifier. This possibility necessitates some form of input protection. Many electrometer type devices, especially CMOS designs, can require elaborate Zener protection schemes which often compromise overall performance. The AD642 requires input protection only if the source is not current limited, and as such is similar to many JFETinput designs. The failure mode would be overheating from excess current rather than voltage breakdown. If the source is not current-limited, all that is required is a resistor in series with the affected input terminal so that the maximum overload current is 1.0 mA (for example, 100 k $\Omega$  for a 100 volt overload). This simple scheme will cause no significant reduction in performance and give complete overload protection. Figure 30 shows proper connections.