# SIEMENS

# SDA 3202 1.3 GHz PLL with I<sup>2</sup>C Bus

- Low Current Consumption

- Message Transmission Via I2C Bus

- 4 Software-Controlled Outputs

- Cost-Effective and Space-Saving Design

- Prescaler Output Frequency is Free from Interference Radiation

| Pin Configuration       | Pin Def          | Pin Definitions  |                                                |  |  |  |  |

|-------------------------|------------------|------------------|------------------------------------------------|--|--|--|--|

|                         | Pin              | Symbol           | Function                                       |  |  |  |  |

| Top View                | 1                | PD               | Input for Active Filter/Output for Charge Pump |  |  |  |  |

|                         | 2                | Q1               | Crystal                                        |  |  |  |  |

| '9 E                    | <sup>,18</sup> 3 | Q2               | Crystal                                        |  |  |  |  |

| <sup>2</sup> <b>9</b> Þ | 17 4             | SDA              | Data I/O for I <sup>2</sup> C Bus              |  |  |  |  |

| · ¬                     | 16 5             | SCL              | Clock Input for I <sup>2</sup> C Bus           |  |  |  |  |

| • <b>4</b> Þ            | 15 6             | P7 ·             | Port Output (Open Collector)                   |  |  |  |  |

| 5 <b>4</b> Þ            | 14 7             | P6               | Port Output (Open Collector)                   |  |  |  |  |

| 6 <b>d</b> þ            | 13 8             | P5               | Port Output (Open Collector)                   |  |  |  |  |

| <sup>7</sup> <b>d b</b> | 12 9             | P4               | Port Output (Open Collector)                   |  |  |  |  |

| *d P                    | 11 10            | P3               | Port Output (Current Sink)                     |  |  |  |  |

| 1 1                     | 10 11            | P2               | Port Output (Current Sink)                     |  |  |  |  |

|                         | 12               | P1 :             | Port Output (Current Sink)                     |  |  |  |  |

|                         | 0100-12 13       | P0               | Port Output (Current Sink)                     |  |  |  |  |

|                         | 14               | l v <sub>s</sub> | Supply Voltage                                 |  |  |  |  |

|                         | 15               | UHF/VHF          | Signal Input                                   |  |  |  |  |

|                         | 16               | REF              | Amplifier-Reference Input                      |  |  |  |  |

|                         | 17               | GND              | Ground                                         |  |  |  |  |

|                         | 18               | $V_{D}$          | Output of Active Filter                        |  |  |  |  |

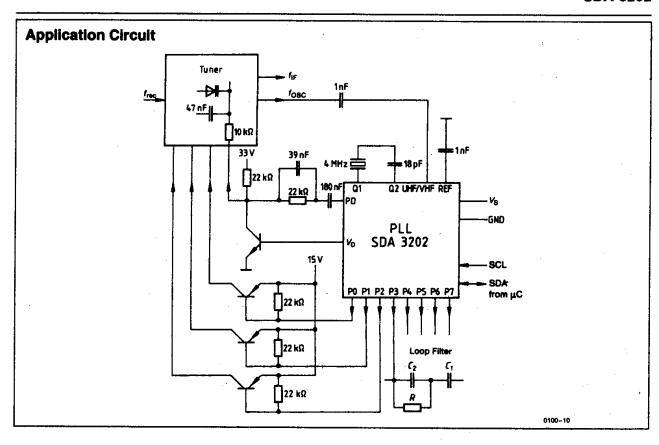

Combined with a VCO (tuner), the SDA 3203 comprises a digital programmable phase-locked loop for television devices designed to use the PLL frequency synthesis tuning principle.

The PLL provides a cyrstal-stable frequency for tuner oscillators between 16 . . . 1300 MHz in the 62.5 KHz raster. By including an external prescaler 1/2, the component can also be used for synthesizing applications of up to 2.4 GHz (e.g. satellite receivers). As a result, the resolution is doubled to 125 KHz. The tuning process is controlled via an I<sup>2</sup>C bus by the microprocessor.

## **Circuit Description**

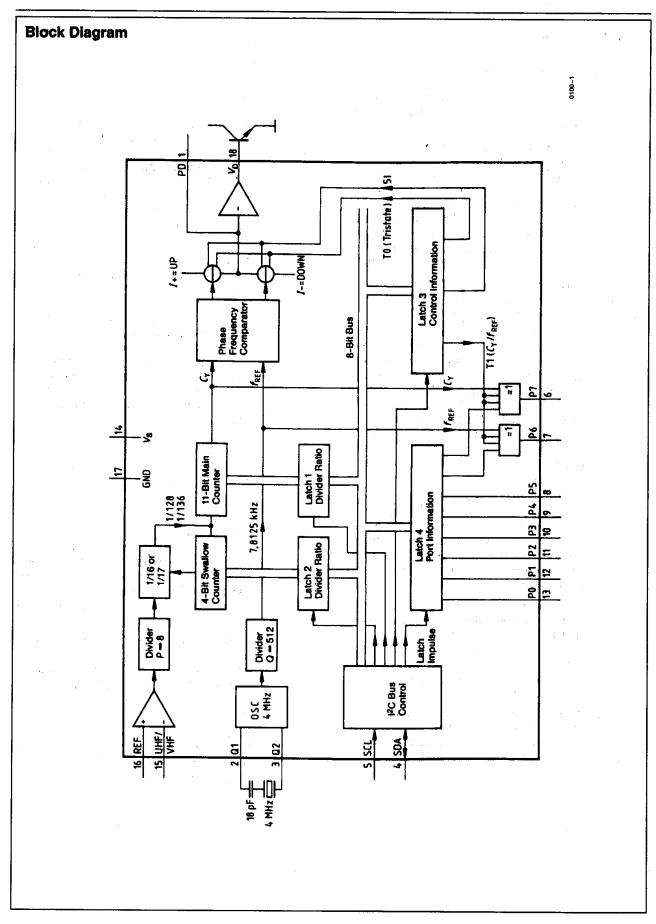

Tuning Section (refer to block diagram)

UHF/VHF The tuner signal is capacitively coupled at the UHF/VHF input and subsequently amplified.

REF The reference input REF should be disabled by a capacitor of low series inductance. The amplified signal passes through an asynchronous divider with a fixed ratio of P = 8 and an adjustable divider N = 256...32767. Subsequent to this process, the signal is compared in a digital frequency phase detector with a reference frequency f<sub>REF</sub> = 7.8125 kHz.

Q1, Q2 This frequency has been derived from a 4 MHz crystal oscillator (pin Q1, Q2) by dividing its output signal by Q = 512.

The phase detector includes two outputs UP and DOWN which control the two current sources I+ and I- of a charge pump. If the negative edge of the divided VCO signal appears prior to the negative edge of the reference signal, the current source I+ will pulsate for the duration of the phase difference. However, during the reversed sequence of the negative edges, the current source I- will begin to pulsate.

PD, V<sub>D</sub> If both signals are in phase, the charge pump output PD changes into the high impedance state (PLL in lock). An active low pass filter (internal amplifier, external output transistor at V<sub>D</sub>, and RC combination) integrates the current pulses as the tuning voltage for the VCO.

With the control bit 5 I the pump current can be switched between two values per software. Through this switch-over, the control characteristics of the PLL during lock-in can be changed, i.e. varying tuner characteristics in the various TV bands can be adjusted.

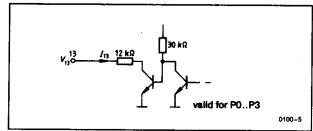

P0...P3 The software-controllable outputs P0, P1, P2 and P3 can drive external PNP transistors (internal current limit) which operate as band selection switch.

P4...P7 The open collector outputs P4, P5, P6, P7 can be used for a variety of different applications.

#### 12C Bus Interface

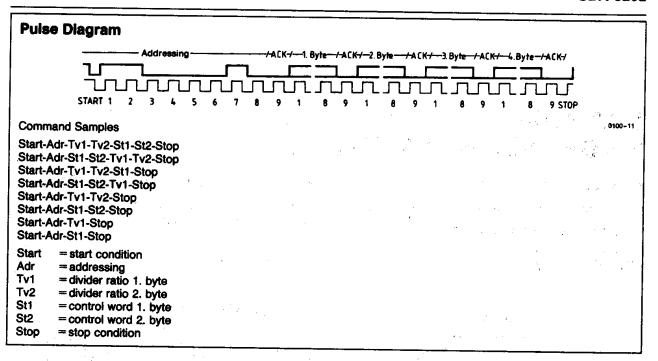

SCL, SDA An asynchronous bidirectional data bus is used for data transfer between the processor and the PLL. As a rule, the clock pulse is supplied by the processor (input SCL), while pin SDA operates as input or output depending on the direction of data flow (open collector, external pull-up resistor).

The data from the processor pass through an I<sup>2</sup>C bus control. Depending on their function, the data are subsequently filed in registers (latch 0-3). If the bus is free, both lines will be in the marking state (SDA, SCL are HIGH). Each tele- begins with the start conditions of SDA returning into Low, while SCL remains in High. All additional information transfer takes place during SCL = Low and the data is forwarded to the control with the positive clock edge. However, if SDA returns to High, while SCL is in High, the message is ended since the PLL acknowledges a stop condition.

For the following, also refer to table "Logic allocation".

All messages are transmitted byte-bybyte, followed by a 9. clock pulse, while the control returns the SDA line to Low (acknowledge conditions). The first byte is comprised of 7 address bits. These are used by the processor to select the PLL from several peripheral components (chip-select). The 8. bit is always Low.

In the data portion of the message the 1. bit of the 1. or 3. data byte determines whether a divider ratio or a control information is to follow. In each case, the 2. byte of the same data type or a stop condition has to follow the 1. byte.

V<sub>S</sub>, GND When the supply voltage is injected, a Power on Reset circuit prevents the PLL from setting the SDA line at Low which would disable the bus.

# **Absolute Maximum Ratings\***

| Supply Voltage (Vs) $\ldots \ldots -0.3V$ to 6V                               |

|-------------------------------------------------------------------------------|

| Output PD (V <sub>1</sub> )0.3V to V <sub>S</sub>                             |

| Crystal Q1 (V2) $-0.3 V$ to $V_{\mbox{\scriptsize S}}$                        |

| Crystal Q2 (V <sub>3</sub> )                                                  |

| Bus Input/Output SDA (V <sub>4</sub> ) $-0.3$ V to V <sub>S</sub>             |

| Bus Input SCL (V5)                                                            |

| Port Output P7 (V <sub>6</sub> ) $\dots -0.3V$ to $+16V$                      |

| Port Output P6 (V <sub>7</sub> ) $-0.3V$ to $+16V$                            |

| Port Output P5 (V8) $\dots -0.3V$ to $+16V$                                   |

| Port Output P4 (V <sub>9</sub> ) $-0.3V$ to $+16V$                            |

| Port Output P3 ( $V_{10}$ )0.3V to +16V                                       |

| Port Output P2 ( $V_{11}$ )0.3V to +16V                                       |

| Port Output P1 (V <sub>12</sub> )0.3V to +16V                                 |

| Port Output P0 ( $V_{13}$ )0.3V to +16V                                       |

| Signal Input UHF/VHF ( $V_{15}$ ) $-0.3V$ to $+2.5V$                          |

| Reference Input REF ( $V_{16}$ )0.3V to +2.5V                                 |

| Output Active Filter V <sub>D</sub> (V <sub>18</sub> ) 0.3V to V <sub>S</sub> |

| Bus Output SDA (I <sub>4L</sub> ) Open Collector1 mA to +5 mA                 |

| Port Output P7 (I <sub>6L</sub> ) Open Collector1 mA to +5 mA                 |

| Port Output P6 (I <sub>7L</sub> ) Open Collector 1 mA to +5 mA                |

\*Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Port Output P5 (I <sub>8L</sub> ) Open Collector | – 1 mA to + 5 mA |

|--------------------------------------------------|------------------|

| Port Output P4 (I <sub>9L</sub> ) Open Collector | – 1 mA to + 5 mA |

| Junction Temperature (T <sub>j</sub> )           | 125°C            |

| Storage Temperature Range (T <sub>stg</sub> )    | 4 · ·            |

| Thermal Resistance<br>System-Air (Rth SA)        | 80 K/W           |

## **Operating Range**

| Supply Voltage (V <sub>S</sub> )       | 4.5V to 5.5V         |

|----------------------------------------|----------------------|

| Ambient Temperature (T <sub>A</sub> )  | 0°C to 85°C          |

| Input Frequency (f <sub>15</sub> )     | . 16 MHz to 1300 MHz |

| Crystal Frequency (f <sub>2, 3</sub> ) | 4 MHz                |

| Divider Factor (N)                     |                      |

# **Characteristics** $V_S = 5V$ ; $T_A = 25$ °C

| Parameter                                     | Symbol              | Test          |                 | Units                |         |              |

|-----------------------------------------------|---------------------|---------------|-----------------|----------------------|---------|--------------|

|                                               | Cymbol              | Circuit       | Min             | Тур                  | Тур Мах |              |

| Current Consumption                           | Is                  | 1             | 35              | 55                   | 75      | mA           |

| Crystal Frequency<br>Series Capacitance 18 pF | f <sub>2, 3</sub> * | . 1           |                 |                      | 4       | MHz          |

| Input Sensitivity UHF/VHF                     |                     |               |                 | •                    |         |              |

| f <sub>15</sub> = 80 500 MHz                  | a <sub>15</sub>     | 2             | -27/10          |                      | 3/315   | dBm/*        |

| f <sub>15</sub> = 500 1000 MHz                | a <sub>15</sub>     | 2             | -24/14          |                      | 3/315   | dBm/*        |

| f <sub>15</sub> = 1200 MHz                    | a <sub>15</sub>     | 2             | -15/40          |                      | 3/315   | dBm/*        |

| Band Selection Outputs P0P                    | 3 (current sink     | s with intern | al resistance f | $R_i = 12  \text{k}$ | Ω)      | <del>.</del> |

| Leakage Current, V <sub>13H</sub> = 13.5V     | I <sub>13H</sub>    | 3             |                 |                      | 10      | μΑ           |

| Sink Current, V <sub>13H</sub> = 12V          | I <sub>13L</sub>    | 3             | 0.7             | 1                    | 1.5     | mA           |

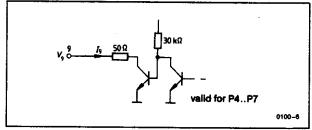

| Port Outputs P4 P7 (switch with               | th open collec      | tor)          |                 |                      |         |              |

| Leakage Current, V <sub>9H</sub> = 13.5V      | I <sub>9H</sub>     | 4             |                 |                      | 10      | μΑ           |

| Residual Voltage, I <sub>9L</sub> = 1.7 mA    | V <sub>9</sub> L    | 4.            |                 |                      | 0.3     | ٧            |

<sup>\*</sup>Listed as mV<sub>rms</sub> with  $50\Omega$

**Characteristics**  $V_S = 5V$ ;  $T_A = 25$ °C (Continued)

| Parameter                                                           | Symbol                                | Test           | Limits               |      |             | Units    |

|---------------------------------------------------------------------|---------------------------------------|----------------|----------------------|------|-------------|----------|

| Laiailielei                                                         | Symbol                                | Circuit        | Min Typ Max          |      | Max         |          |

| Phase Detector Output PD (                                          | /s = 5V)                              | •              |                      |      | <del></del> |          |

| Charge Pump Current<br>5 I = High; V <sub>1</sub> = 2V              | l <sub>1H</sub>                       | 5              | ±90                  | ±220 | ±300        | μА       |

| Charge Pump Current<br>5 I = Low; V <sub>1</sub> = 2V               | 1111                                  | 5              | ± 22                 | ±50  | ±75         | μΑ       |

| Output Voltage Locked                                               | V <sub>IL</sub>                       | 5              | 1.5                  |      | 2.5         | ٧        |

| Active Filter Output V <sub>D</sub> (Test                           | modus T0 =                            | 1, PD = Trista | ate)                 |      |             |          |

| Output Current<br>V <sub>18</sub> = 0.8V; I <sub>14</sub> = 90 μA   | l <sub>18</sub>                       | 5              | 500                  |      |             | νμΑ      |

| Output Voltage, V <sub>1L</sub> = 0V                                | V <sub>18</sub>                       | 5              |                      |      | 100         | mV       |

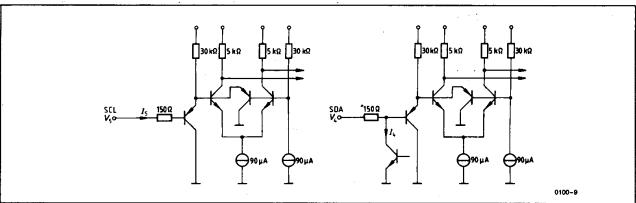

| Bus Inputs SCL, SDA                                                 |                                       |                |                      |      |             |          |

| Input Voltage                                                       | V <sub>5H</sub><br>V <sub>5L</sub>    | 6              | 3                    | ·    | 5.5<br>1.5  | V<br>V   |

| input Current V <sub>5H</sub> = V <sub>S</sub> V <sub>5L</sub> = 0V | 5L<br> 5L                             | 6              |                      |      | 50<br>-100  | μΑ<br>μΑ |

| Output SDA (open collector)                                         |                                       |                |                      |      |             |          |

| Output Voltage V <sub>4H</sub> = 5.5V I <sub>4L</sub> = 2 mA        | V <sub>4H</sub><br>V <sub>4L</sub>    | 6<br>6         |                      |      | 12<br>0.4   | V<br>V   |

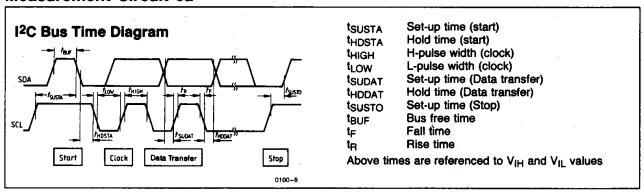

| Edges SCL, SDA                                                      | <u> </u>                              | T              | T                    |      |             | <u> </u> |

| Rise Time                                                           | t <sub>R</sub>                        | 6              |                      |      | 15          | μs       |

| Fall Time                                                           | te                                    | 6              |                      |      | 15          | μs       |

| Shift Register Clock Pulse S                                        | T                                     | T _            |                      |      |             | 141.     |

| Frequency                                                           | f <sub>5</sub>                        | 6              | 0                    |      | 100         | KHz      |

| H-Pulse Width                                                       | t <sub>5</sub> HIGH                   | 6              | 4                    |      |             | μs       |

| L-Pulse Width                                                       | t <sub>5</sub> LOW                    | 6              | 4                    | ,    |             | μs       |

| Start                                                               | 1                                     | T              | 1                    |      | <u> </u>    |          |

| Set-Up Time                                                         | tsusta                                | 6              | 4                    |      |             | μs       |

| Hold Time                                                           | thDSTA                                | 6              | 4                    |      | L           | μs       |

| Stop                                                                | · · · · · · · · · · · · · · · · · · · | <u>.</u>       | <del>'i '' '</del> i |      |             | <u> </u> |

| Set-Up Time                                                         | tsusto                                | 6              | 4                    | · .  |             | μs       |

| Bus Free Time                                                       | t <sub>BUF</sub>                      | 6              | 4                    |      |             | μs       |

| Data Transfer                                                       | 1                                     | <u> </u>       | ·                    |      |             |          |

| Set-Up Time                                                         | <sup>t</sup> SUDAT                    | 6              | 0.3                  |      |             | μs       |

| Hold Time                                                           | <b>t</b> HDDAT                        | 6              | 0                    |      |             | μs       |

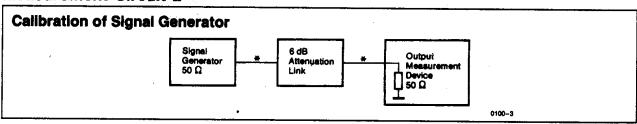

## **Measurement Circuit 1**

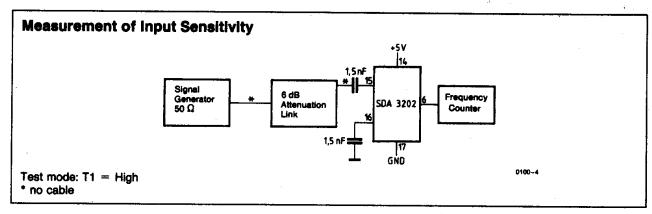

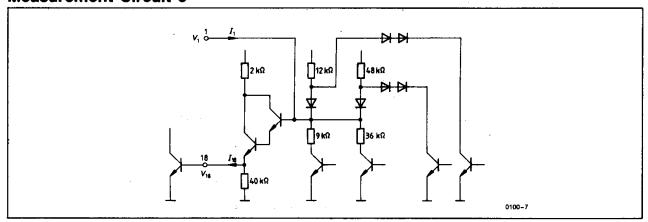

## **Measurement Circuit 2**

## **Measurement Circuit 3**

# **Measurement Circuit 4**

### **Measurement Circuit 5**

to the second of the second of

### Measurement Circuit 6a

### **Measurement Circuit 6b**

## **Computation for Loop Filter**

Loop bandwidth:  $\omega_R = \sqrt{\frac{I_p \times K_{VCO}}{C_1 \times P \times N}}$

Attenuation:  $\zeta = 0.5 \times \omega_R \times R \times C_1$

P = Prescaler

N = Progr. divider

I<sub>P</sub> = Pump current

K<sub>VCO</sub> = Tuner slope

$R, C_1 = Loop filter$

## **Example for Channel 47**

P = 8; N = 11520;  $I_p$  = 100 μA;  $K_{VCO}$  = 18.7 MHz/V; R = 22 kΩ;  $C_1$  = 180 nF;  $\omega_R$  = 336 Hz;  $f_n$  = 54 Hz;  $\zeta$  = 0.67

Standard dimensioning:  $C_2 = C_{1/5}$

## **Description of Function, Application and Circuit**

## **Logic Allocation**

9 1 HE DA

|                         | MSB |     |     |     |     |     | A = | = Acknow | ledge |

|-------------------------|-----|-----|-----|-----|-----|-----|-----|----------|-------|

| Address byte            | 1   | 1   | 0   | 0   | 0   | 0   | 1   | 0        | Α     |

| Prog. divider<br>byte 1 | 0   | n14 | n13 | n12 | n11 | n10 | n9  | n8       | Α     |

| Prog. divider<br>byte 2 | n7  | n6  | n5  | n4  | n3  | n2  | n1  | n0       | A     |

| Control info            | 1   | 51  | T1  | T0  | 1   | 1   | 1   | 0        | Α     |

| Control info<br>byte 2  | P7  | P6  | P5  | P4  | P3  | P2  | P1  | P0       | Α     |

#### Divider ratio:

$$N = 16384 \times n14 + 8192 \times n13 + 4096 \times n12 + 2048 \times n11 + 1024 \times n10 + 512 \times n9 + 256 \times n8 + 128 \times n7 + 64 \times n6 + 32 \times n5 + 16 \times n4 + 8 \times n3 + 4 \times n2 + 2 \times n1 + n0$$

#### Band selection:

P3...P0 = 1 Current sink is active

#### Port outputs:

P7...P4 = 1 Open collector output is active

#### Switch-over of pump current:

51 = 1 High current

#### Test Mode:

T1,T0 = 0,0 Normal operation

T1 = 1 P6 =  $f_{REF}$ ; P7 = Cy

T0 = 1 Tristate charge pump

**Ordering Information**

| Туре     | Package     |          |  |

|----------|-------------|----------|--|

| SDA 3202 | Q67000-Y904 | P-DIP 18 |  |