# **5 V ECL Voltage Controlled Oscillator Amplifier**

#### Description

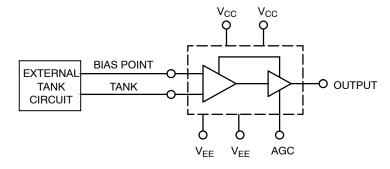

The MC100EL1648 is a voltage controlled oscillator amplifier that requires an external parallel tank circuit consisting of the inductor (L) and capacitor (C). A varactor diode may be incorporated into the tank circuit to provide a voltage variable input for the oscillator (VCO). This device may also be used in many other applications requiring a fixed frequency clock.

The MC100EL1648 is ideal in applications requiring a local oscillator, systems that include electronic test equipment, and digital high–speed telecommunications.

The MC100EL1648 is based on the VCO circuit topology of the MC1648. The MC100EL1648 uses advanced bipolar process technology which results in a design which can operate at an extended frequency range.

The ECL output circuitry of the MC100EL1648 is not a traditional open emitter output structure and instead has an on-chip termination emitter resistor,  $R_E$ , with a nominal value of 510  $\Omega$ . This facilitates direct ac-coupling of the output signal into a transmission line. Because of this output configuration, an external pull-down resistor is not required to provide the output with a dc current path. This output is intended to drive one ECL load (3.0 pF). If the user needs to fanout the signal, an ECL buffer such as the EL16 (EL11, EL14) type Line Receiver/Driver should be used.

## **Features**

- Typical Operating Frequency Up to 1100 MHz

- Low-Power 19 mA at 5.0 Vdc Power Supply

- PECL Mode Operating Range:  $V_{CC} = 4.2 \text{ V}$  to 5.5 V with  $V_{EE} = 0 \text{ V}$

- NECL Mode Operating Range:  $V_{CC} = 0 \text{ V}$  with  $V_{EE} = -4.2 \text{ V}$  to -5.5 V

- Input Capacitance = 6.0 pF (TYP)

- Pb-Free Packages are Available

NOTE: The MC100EL1648 is NOT useable as a crystal oscillator.

Figure 1. Logic Diagram

# ON Semiconductor®

http://onsemi.com

# MARKING DIAGRAMS\*

SOIC-8 D SUFFIX CASE 751

TSSOP-8 DT SUFFIX CASE 948R

SOEIAJ-14 M SUFFIX CASE 965

DFN8 MN SUFFIX CASE 506AA

A = Assembly Location

L, = Wafer Lot

Y = Year

W = Work Week

M = Date Code

G or ■ = Pb-Free Package

(Note: Microdot may be in either location)

\*For additional marking information, refer to

Application Note AND8002/D.

# **ORDERING INFORMATION**

See detailed ordering and shipping information in the package dimensions section on page 12 of this data sheet.

Warning: All  $V_{CC}$  and  $V_{EE}$  pins must be externally connected to Power Supply to guarantee proper operation.

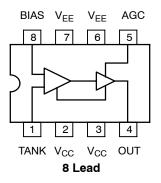

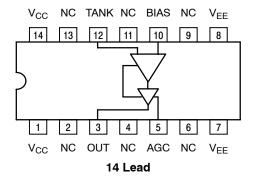

Figure 2. Pinout Assignments

**Table 1. PIN DESCRIPTION**

| Pin No. |                    |                 |                                                                                                                                         |  |

|---------|--------------------|-----------------|-----------------------------------------------------------------------------------------------------------------------------------------|--|

| 8 Lead  | 14 Lead            | Symbol          | Description                                                                                                                             |  |

| 1       | 12                 | TANK            | OSC Input Voltage                                                                                                                       |  |

| 2, 3    | 1, 14              | V <sub>CC</sub> | Positive Supply                                                                                                                         |  |

| 4       | 3                  | OUT             | ECL Output                                                                                                                              |  |

| 5       | 5                  | AGC             | Automatic Gain Control Input                                                                                                            |  |

| 6, 7    | 7, 8               | V <sub>EE</sub> | Negative Output                                                                                                                         |  |

| 8       | 10                 | BIAS            | OSC Input Reference Voltage                                                                                                             |  |

|         | 2, 4, 7, 9, 11, 13 | NC              | No Connect                                                                                                                              |  |

|         |                    | EP              | Exposed pad must be connected to a sufficient thermal conduit. Electrically connect to the most negative supply or leave floating open. |  |

**Table 2. ATTRIBUTES**

| Character                             | Value                                                      |                                          |  |  |  |

|---------------------------------------|------------------------------------------------------------|------------------------------------------|--|--|--|

| Internal Input Pulldown Resistor      | Internal Input Pulldown Resistor                           |                                          |  |  |  |

| Internal Input Pullup Resistor        |                                                            | N/A                                      |  |  |  |

| ESD Protection                        | > 1 kV<br>> 100 V<br>> 1 kV                                |                                          |  |  |  |

| Moisture Sensitivity, Indefinite Time | Pb Pkg                                                     | Pb-Free Pkg                              |  |  |  |

|                                       | Level 1<br>Level 1<br>Level 3<br>Level 1                   | Level 1<br>Level 3<br>Level 3<br>Level 1 |  |  |  |

| Flammability Rating                   | UL 94 V-0                                                  | @ 0.125 in                               |  |  |  |

| Transistor Count                      | 1                                                          | 1                                        |  |  |  |

| Meets or Exceeds JEDEC Standard       | Meets or Exceeds JEDEC Standard EIA/JESD78 IC Latchup Test |                                          |  |  |  |

<sup>1.</sup> For additional Moisture Sensitivity information, refer to Application Note AND8003/D.

**Table 3. MAXIMUM RATINGS**

| Symbol            | Parameter                                          | Condition 1                                    | Condition 2                                                               | Rating            | Unit         |

|-------------------|----------------------------------------------------|------------------------------------------------|---------------------------------------------------------------------------|-------------------|--------------|

| V <sub>CC</sub>   | Power Supply PECL Mode                             | V <sub>EE</sub> = 0 V                          |                                                                           | 7 to 0            | V            |

| V <sub>EE</sub>   | Power Supply NECL Mode                             | V <sub>CC</sub> = 0 V                          |                                                                           | -7 to 0           | V            |

| VI                | PECL Mode Input Voltage<br>NECL Mode Input Voltage | V <sub>EE</sub> = 0 V<br>V <sub>CC</sub> = 0 V | $\begin{array}{c} V_{I}\!\leq\!V_{CC} \\ V_{I}\!\geq\!V_{EE} \end{array}$ | 6 to 0<br>-6 to 0 | V<br>V       |

| l <sub>out</sub>  | Output Current                                     | Continuous<br>Surge                            |                                                                           | 50<br>100         | mA<br>mA     |

| T <sub>A</sub>    | Operating Temperature Range                        |                                                |                                                                           | -40 to +85        | °C           |

| T <sub>stg</sub>  | Storage Temperature Range                          |                                                |                                                                           | -65 to +150       | °C           |

| $\theta_{\sf JA}$ | Thermal Resistance (Junction-to-Ambient)           | 0 lfpm<br>500 lfpm                             | SOIC-8<br>SOIC-8                                                          | 190<br>130        | °C/W<br>°C/W |

| $\theta_{\sf JC}$ | Thermal Resistance (Junction-to-Case)              | Standard Board                                 | SOIC-8                                                                    | 41 to 44          | °C/W         |

| $\theta_{\sf JA}$ | Thermal Resistance (Junction-to-Ambient)           | 0 lfpm<br>500 lfpm                             | TSSOP-8<br>TSSOP-8                                                        | 185<br>140        | °C/W<br>°C/W |

| θЈС               | Thermal Resistance (Junction-to-Case)              | Standard Board                                 | TSSOP-8                                                                   | 41 to 44          | °C/W         |

| $\theta_{\sf JA}$ | Thermal Resistance (Junction-to-Ambient)           | 0 lfpm<br>500 lfpm                             | SOIC-14<br>SOIC-14                                                        | 150<br>110        | °C/W<br>°C/W |

| $\theta_{\sf JC}$ | Thermal Resistance (Junction-to-Case)              | Standard Board                                 | SOIC-14                                                                   | 41 to 44          | °C/W         |

| $\theta_{\sf JA}$ | Thermal Resistance (Junction-to-Ambient)           | 0 lfpm<br>500 lfpm                             | DFN8<br>DFN8                                                              | 129<br>84         | °C/W<br>°C/W |

| T <sub>sol</sub>  | Wave Solder Pb Pb-Free                             | <2 to 3 sec @ 248°C<br><2 to 3 sec @ 260°C     |                                                                           | 265<br>265        | °C           |

Stresses exceeding Maximum Ratings may damage the device. Maximum Ratings are stress ratings only. Functional operation above the Recommended Operating Conditions is not implied. Extended exposure to stresses above the Recommended Operating Conditions may affect device reliability.

Table 4. PECL DC CHARACTERISTICS  $V_{CC} = 5.0 \text{ V}$ ;  $V_{EE} = 0.0 \text{ V} + 0.8 \text{ / } -0.5 \text{ V}$  (Note 2)

|                   |                              |      | -40°C |      |      | 25°C |      |      | 85°C |      |      |

|-------------------|------------------------------|------|-------|------|------|------|------|------|------|------|------|

| Symbol            | Characteristic               | Min  | Тур   | Max  | Min  | Тур  | Max  | Min  | Тур  | Max  | Unit |

| I <sub>EE</sub>   | Power Supply Current         | 13   | 19    | 25   | 13   | 19   | 25   | 13   | 19   | 25   | mA   |

| V <sub>OH</sub>   | Output HIGH Voltage (Note 3) | 3950 | 4170  | 4610 | 3950 | 4170 | 4610 | 3950 | 4170 | 4610 | mV   |

| V <sub>OL</sub>   | Output LOW Voltage (Note 3)  | 3040 | 3410  | 3600 | 3040 | 3410 | 3600 | 3040 | 3410 | 3600 | mV   |

| AGC               | Automatic Gain Control Input | 1690 |       | 1980 | 1690 |      | 1980 | 1690 |      | 1980 | mV   |

| V <sub>BIAS</sub> | Bias Voltage (Note 4)        | 1650 |       | 1800 | 1650 |      | 1800 | 1650 |      | 1800 | mV   |

| V <sub>IL</sub>   |                              | 1.5  |       |      | 1.35 |      |      | 1.2  |      |      | V    |

| V <sub>IH</sub>   |                              |      |       | 2.0  |      |      | 1.85 |      |      | 1.7  | V    |

| IL                | Input Current                |      | -5.0  |      |      | -5.0 |      |      | -5.0 |      | mA   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

- 2. Output parameters vary 1:1 with V<sub>CC</sub>.

- 3.  $1.0 \text{ M}\Omega$  impedance.

- 4. This measurement guarantees the dc potential at the bias point for purposes of incorporating a varactor tuning diode at this point.

Table 5. NECL DC CHARACTERISTICS  $V_{CC} = 0.0 \text{ V}$ ;  $V_{EE} = -5.0 \text{ V} + 0.8 \text{ / } -0.5 \text{ V}$  (Note 5)

|                   |                              |       | -40°C |       |       | 25°C  |       |       | 85°C  |       |      |

|-------------------|------------------------------|-------|-------|-------|-------|-------|-------|-------|-------|-------|------|

| Symbol            | Characteristic               | Min   | Тур   | Max   | Min   | Тур   | Max   | Min   | Тур   | Max   | Unit |

| I <sub>EE</sub>   | Power Supply Current         | 13    | 19    | 25    | 13    | 19    | 25    | 13    | 19    | 25    | mA   |

| V <sub>OH</sub>   | Output HIGH Voltage (Note 6) | -1050 | -830  | -399  | -1050 | -830  | -399  | -1050 | -830  | -399  | mV   |

| V <sub>OL</sub>   | Output LOW Voltage (Note 6)  | -1960 | -1590 | -1400 | -1960 | -1590 | -1400 | -1960 | -1590 | -1400 | mV   |

| AGC               | Automatic Gain Control Input | -3310 |       | -3020 | -3310 |       | -3020 | -3310 |       | -3020 | mV   |

| V <sub>BIAS</sub> | Bias Voltage (Note 7)        | -3350 |       | -3200 | -3350 |       | -3200 | -3350 |       | -3200 | mV   |

| V <sub>IL</sub>   |                              | -3.5  |       |       | -3.65 |       |       | -3.8  |       |       | ٧    |

| V <sub>IH</sub>   |                              |       |       | -3.0  |       |       | -3.15 |       |       | -3.3  | ٧    |

| IL                | Input Current                |       | -5.0  |       |       | -5.0  |       |       | -5.0  |       | mA   |

NOTE: Device will meet the specifications after thermal equilibrium has been established when mounted in a test socket or printed circuit board with maintained transverse airflow greater than 500 lfpm. Electrical parameters are guaranteed only over the declared operating temperature range. Functional operation of the device exceeding these conditions is not implied. Device specification limit values are applied individually under normal operating conditions and not valid simultaneously.

- 5. Output parameters vary 1:1 with V<sub>CC</sub>.

- 6. 1.0  $M\Omega$  impedance.

- 7. This measurement guarantees the dc potential at the bias point for purposes of incorporating a varactor tuning diode at this point.

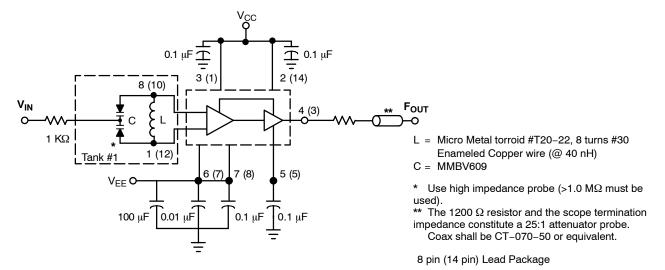

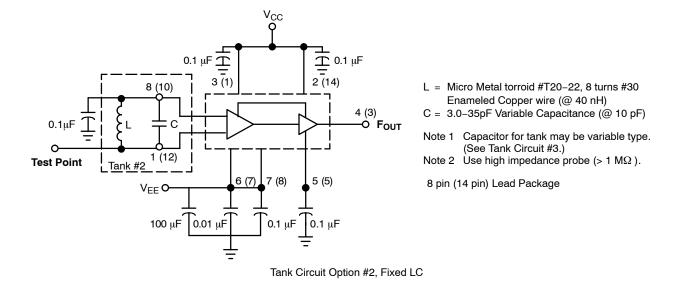

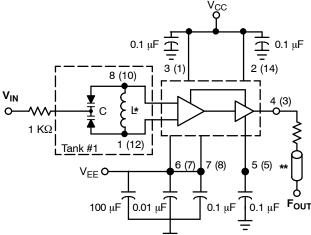

# **GENERIC TEST CIRCUITS: Bypass to Supply Opposite GND**

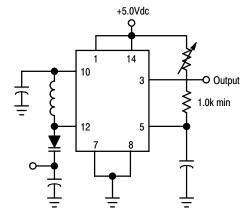

Tank Circuit Option #1, Varactor Diode

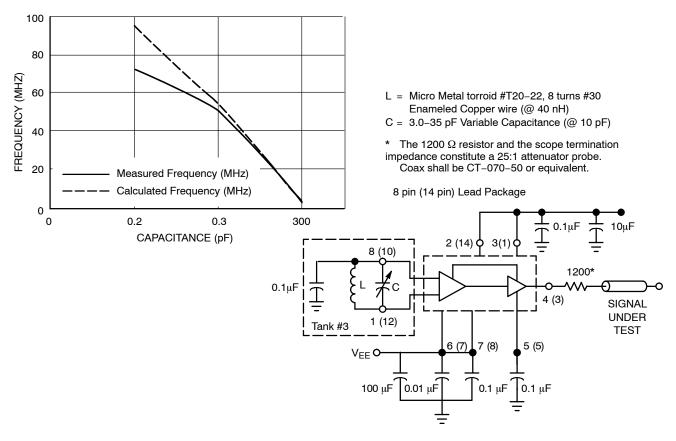

Figure 3. Typical Test Circuit with Alternate Tank Circuits

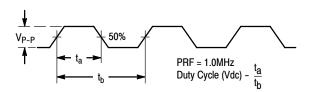

Figure 4. Output Waveform

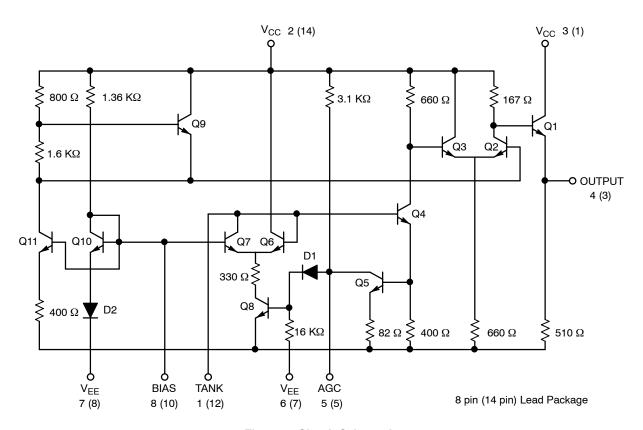

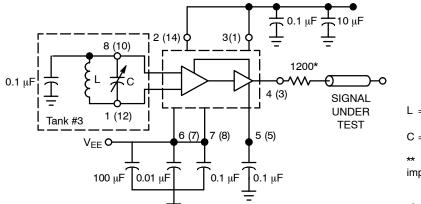

#### **OPERATION THEORY**

Figure 5 illustrates the simplified circuit schematic for the MC100EL1648. The oscillator incorporates positive feedback by coupling the base of transistor Q6 to the collector of Q7. An automatic gain control (AGC) is incorporated to limit the current through the emitter–coupled pair of transistors (Q7 and Q6) and allow optimum frequency response of the oscillator. In order to maintain the high quality factor (Q) on the oscillator, and provide high spectral purity at the output, transistor Q4 is used to translate the oscillator signal to the output differential pair Q2 and Q3. Figure 16 indicates the high spectral purity of the oscillator output (pin 4 on 8–pin SOIC). Transistors

Q2 and Q3, in conjunction with output transistor Q1, provide a highly buffered output that produces a square wave. The typical output waveform can be seen in Figure 4. The bias drive for the oscillator and output buffer is provided by Q9 and Q11 transistors. In order to minimize current, the output circuit is realized as an emitter–follower buffer with an on chip pull–down resistor  $R_{\rm E}$ .

Figure 5. Circuit Schematic

Figure 6. Low Frequency Plot

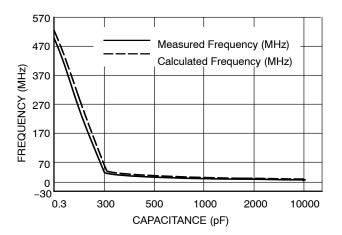

Figure 7. High Frequency Plot

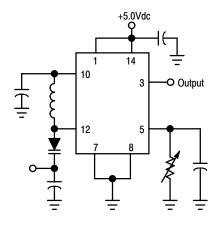

#### **FIXED FREQUENCY MODE**

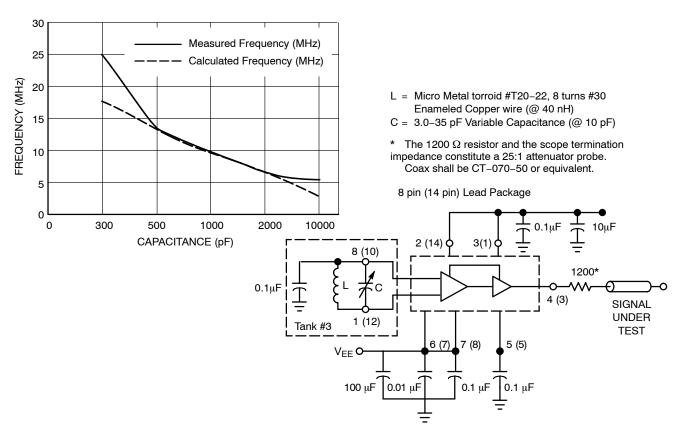

The MC100EL1648 external tank circuit components are used to determine the desired frequency of operation as shown in Figure 8, tank option #2. The tank circuit components have direct impact on the tuning sensitivity,  $I_{\rm EE}$ , and phase noise performance. Fixed frequency of the tank circuit is usually realized by an inductor and capacitor (LC network) that contains a high Quality factor (Q). The plotted curve indicates various fixed frequencies obtained with a single inductor and variable capacitor. The Q of the components in the tank circuit has a direct impact on the resulting phase noise of the oscillator. In general, when the Q is high the oscillator will result in lower phase noise.

L = Micro Metal torroid #T20-22, 8 turns #30 Enameled Copper wire (@ 40 nH)

C = 3.0–35 pF Variable Capacitance (@ 10 pF) Note 1 Capacitor for tank may be variable type. (See Tank Circuit #3.)

Note 2 Use high impedance probe (> 1 M $\Omega$ ).

8 pin (14 pin) lead package

Q<sub>L</sub> ≥ 100

Figure 8. Fixed Frequency LC Tank

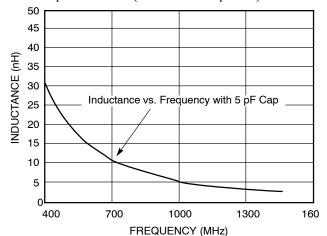

Only high quality surface-mount RF chip capacitors should be used in the tank circuit at high frequencies. These capacitors should have very low dielectric loss (high-Q). At a minimum, the capacitors selected should be operating at 100 MHz below their series resonance point. As the desired frequency of operation increases, the values of the tank capacitor will decrease since the series resonance point is a function of the capacitance value. Typically, the inductor is realized as a surface-mount chip or a wound coil. In addition, the lead inductance and board inductance and capacitance also have an impact on the final operating point. The following equation will help to choose the appropriate values for your tank circuit design.

$$f_0 = \frac{1}{2\pi \sqrt{L_T * C_T}}$$

Where

$$L_T = \text{Total Inductance}$$

$$C_T = \text{Total Capacitance}$$

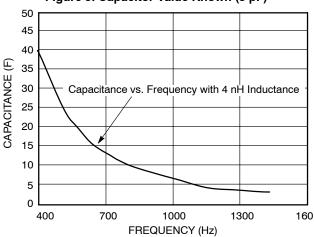

Figure 9 and Figure 10 represent the ideal curve of inductance/capacitance versus frequency with one known tank component. This helps the designer of the tank circuit to choose desired value of inductor/capacitor component for the wanted frequency. The lead inductance and board inductance and capacitance will also have an impact on the tank component values (inductor and capacitor).

Figure 9. Capacitor Value Known (5 pF)

Figure 10. Inductor Value Known (4 nH)

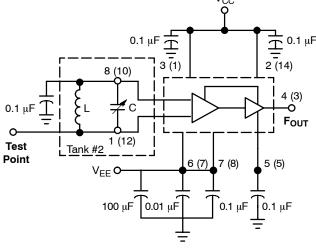

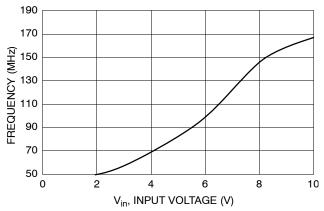

#### **VOLTAGE CONTROLLED MODE**

The tank circuit configuration presented in Figure 11, Voltage Controlled Varactor Mode, allows the VCO to be tuned across the full operating voltage of the power supply. Deriving from Figure 6, the tank capacitor, C, is replaced with a varactor diode whose capacitance changes with the voltage applied, thus changing the resonant frequency at which the VCO tank operates as shown in Figure 3, tank option #1. The capacitive component in Equation 1 also needs to include the input capacitance of the device and other circuit and parasitic elements.

Figure 12. Plot 1. Dual Varactor MMBV609, V<sub>IN</sub> vs. Frequency

\*Use high impedance probe (►1.0 MegΩ must be used).

\*\*The 1200 Ω resistor and the scope termination impedance constitute a 25:1 attenuator probe. Coax shall be CT-070-50 or equivalent.

L = Micro Metal torroid #T20-22, 8 turns #30 Enameled Copper wire (@ 40 nH)

C = MMBV609

8 pin (14 pin) lead package

Figure 11. Voltage Controlled Varactor Mode

When operating the oscillator in the voltage controlled mode with Tank Circuit #1 (Figure 3), it should be noted that the cathode of the varactor diode (D), pin 8 (for 8 lead package) or pin 10 (for 14 lead package) should be biased at least 1.4~V above  $V_{\rm FE}$ .

Typical transfer characteristics employing the capacitance of the varactor diode (plus the input capacitance of the device, about 6.0 pF typical) in the voltage controlled mode is shown in Plot 1, Dual Varactor MMBV609  $V_{\rm in}$  vs. Frequency. Figure 6, Figure 7, and Figure 8 show the accuracy of the measured frequency with the different variable capacitance values. The  $1.0\,\mathrm{k}\Omega$  resistor in Figure 11 is used to protect the varactor diode during testing. It is not necessary as long as the dc input voltage does not cause the diode to become forward biased. The tuning range of the oscillator in the voltage controlled mode may be calculated as follows:

$$\frac{f_{max}}{f_{min}} = \frac{\sqrt{C_D(max) + C_S}}{\sqrt{C_D(min) + C_S}}$$

Where

$$f_{min} = \frac{1}{2\pi \sqrt{(L(C_D(max) + C_S)}}$$

Where

C<sub>S</sub> = Shunt Capacitance (input plus external capacitance)

C<sub>D</sub> = Varactor Capacitance as a function of bias voltage

Good RF and low–frequency bypassing is necessary on the device power supply pins. Capacitors on the AGC pin and the input varactor trace should be used to bypass the AGC point and the VCO input (varactor diode), guaranteeing only dc levels at these points. For output frequency operation between 1.0 MHz and 50 MHz, a 0.1  $\mu F$  capacitor is sufficient. At higher frequencies, smaller values of capacitance should be used; at lower frequencies, larger values of capacitors depends directly on the physical layout of the system. All bypassing should be as close to the package pins as possible to minimize unwanted lead inductance. Several different capacitors may be needed to bypass various frequencies.

## WAVE-FORM CONDITIONING - SINE OR SQUARE WAVE

The peak-to-peak swing of the tank circuit is set internally by the AGC pin. Since the voltage swing of the tank circuit provides the drive for the output buffer, the AGC potential directly affects the output waveform. If it is desired to have a sine wave at the output of the MC100EL1648, a series resistor is tied from the AGC point to the most negative power potential (ground if positive volt supply is used, -5.2 V if a negative supply is used) as shown in

Figure 13. At frequencies above 100 MHz typical, it may be desirable to increase the tank circuit peak–to–peak voltage in order to shape the signal into a more square waveform at the output of the MC100EL1648. This is accomplished by tying a series resistor (1.0 k $\Omega$  minimum) from the AGC to the most positive power potential (+5.0 V if a positive volt supply is used, ground if a –5.2 V supply is used). Figure 14 illustrates this principle.

Figure 13. Method of Obtaining a Sine-Wave Output

Figure 14. Method of Extending the Useful Range of the MC100EL1648 (Square Wave Output)

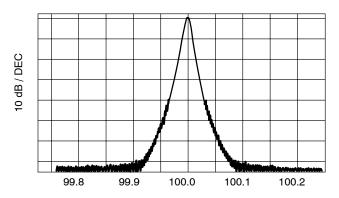

#### **SPECTRAL PURITY**

B.W. = 10 kHz, Center Frequency = 100 MHz Scan Width = 50 kHz/div, Vertical Scale = 10 dB/div

Figure 15. Spectral Purity

- L = Micro Metal torroid #T20-22, 8 turns #30 Enameled Copper wire (@ 40 nH)

- C = 3.0-35 pF Variable Capacitance (@ 10 pF)

- \*\* The 1200  $\Omega$  resistor and the scope termination impedance constitute a 25:1 attenuator probe. Coax shall be CT–070–50 or equivalent.

8 pin (14 pin) Lead Package

Spectral Purity Test Circuit

Figure 16. Spectral Purity of Signal Output for 200 MHz Testing

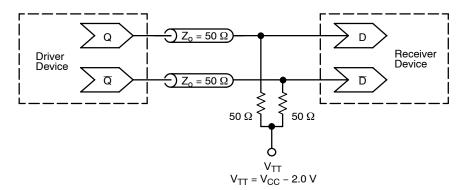

Figure 17. Typical Termination for Output Driver and Device Evaluation (See Application Note AND8020/D – Termination of ECL Logic Devices.)

#### **ORDERING INFORMATION**

| Device           | Package                          | Shipping <sup>†</sup> |  |  |

|------------------|----------------------------------|-----------------------|--|--|

| MC100EL1648D     | SOIC-8, Narrow Body              | 98 Units / Rail       |  |  |

| MC100EL1648DG    | SOIC-8, Narrow Body<br>(Pb-Free) | 98 Units / Rail       |  |  |

| MC100EL1648DR2   | SOIC-8, Narrow Body              | 2500 / Tape & Reel    |  |  |

| MC100EL1648DR2G  | SOIC-8, Narrow Body<br>(Pb-Free) | 2500 / Tape & Reel    |  |  |

| MC100EL1648DT    | TSSOP-8                          | 100 Units / Rail      |  |  |

| MC100EL1648DTG   | TSSOP-8<br>(Pb-Free)             | 100 Units / Rail      |  |  |

| MC100EL1648DTR2  | TSSOP-8                          | 2500 / Tape & Reel    |  |  |

| MC100EL1648DTR2G | TSSOP-8<br>(Pb-Free)             | 2500 / Tape & Reel    |  |  |

| MC100EL1648M     | SOEAIJ-14                        | 50 Units / Rail       |  |  |

| MC100EL1648MG    | SOEAIJ-14<br>(Pb-Free)           | 50 Units / Rail       |  |  |

| MC100EL1648MEL   | SOEAIJ-14                        | 2000 / Tape & Reel    |  |  |

| MC100EL1648MELG  | SOEAIJ-14<br>(Pb-Free)           | 2000 / Tape & Reel    |  |  |

| MC100EL1648MNR4  | DFN8                             | 1000 / Tape & Reel    |  |  |

| MC100EL1648MNR4G | DFN8<br>(Pb-Free)                | 1000 / Tape & Reel    |  |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

# **Resource Reference of Application Notes**

AN1405/D - ECL Clock Distribution Techniques

AN1406/D - Designing with PECL (ECL at +5.0 V)

AN1503/D - ECLinPS™ I/O SPiCE Modeling Kit

AN1504/D - Metastability and the ECLinPS Family

AN1568/D - Interfacing Between LVDS and ECL

AN1672/D - The ECL Translator Guide

AND8001/D - Odd Number Counters Design

AND8002/D - Marking and Date Codes

AND8020/D - Termination of ECL Logic Devices

AND8066/D - Interfacing with ECLinPS

AND8090/D - AC Characteristics of ECL Devices

#### PACKAGE DIMENSIONS

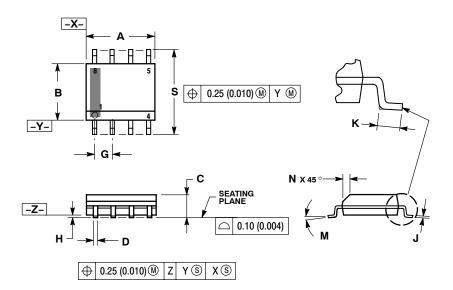

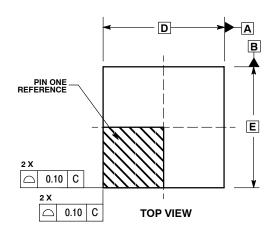

# SOIC-8 NB CASE 751-07 **ISSUE AH**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

4. MAXIMUM MOLD PROTRUSION 0.15 (0.006) PER SIDE.

5. DIMENSION D DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

6. 751-01 THRU 751-06 ARE OBSOLETE. NEW STANDARD IS 751-07.

|     | MILLIN | IETERS | INC       | HES   |  |

|-----|--------|--------|-----------|-------|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |

| Α   | 4.80   | 5.00   | 0.189     | 0.197 |  |

| В   | 3.80   | 4.00   | 0.150     | 0.157 |  |

| С   | 1.35   | 1.75   | 0.053     | 0.069 |  |

| D   | 0.33   | 0.51   | 0.013     | 0.020 |  |

| G   | 1.27   | 7 BSC  | 0.050 BSC |       |  |

| Н   | 0.10   | 0.25   | 0.004     | 0.010 |  |

| J   | 0.19   | 0.25   | 0.007     | 0.010 |  |

| K   | 0.40   | 1.27   | 0.016     | 0.050 |  |

| М   | 0 °    | 8 °    | 0 °       | 8 °   |  |

| N   | 0.25   | 0.50   | 0.010     | 0.020 |  |

| S   | 5.80   | 6.20   | 0.228     | 0.244 |  |

## **SOLDERING FOOTPRINT\***

$\left(\frac{\text{mm}}{\text{inches}}\right)$ SCALE 6:1

<sup>\*</sup>For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

## **PACKAGE DIMENSIONS**

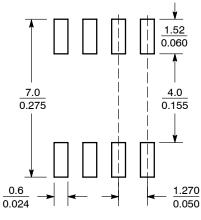

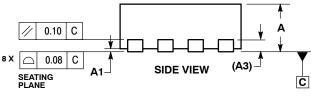

# TSSOP-8 **DT SUFFIX** PLASTIC TSSOP PACKAGE CASE 948R-02 **ISSUE A**

- NOTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSION A DOES NOT INCLUDE MOLD FLASH. PROTRUSIONS OR GATE BURRS. MOLD FLASH OR GATE BURRS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

4. DIMENSION B DOES NOT INCLUDE INTERLEAD FLASH OR PROTRUSION. INTERLEAD FLASH OR PROTRUSION SHALL NOT EXCEED 0.25 (0.010) PER SIDE.

- PER SIDE.

5. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

6. DIMENSION A AND B ARE TO BE DETERMINED AT DATUM PLANE –W-.

|     | MILLIN   | IETERS | INC   | HES   |

|-----|----------|--------|-------|-------|

| DIM | MIN      | MAX    | MIN   | MAX   |

| Α   | 2.90     | 3.10   | 0.114 | 0.122 |

| В   | 2.90     | 3.10   | 0.114 | 0.122 |

| С   | 0.80     | 1.10   | 0.031 | 0.043 |

| D   | 0.05     | 0.15   | 0.002 | 0.006 |

| F   | 0.40     | 0.70   | 0.016 | 0.028 |

| G   | 0.65     | BSC    | 0.026 | BSC   |

| K   | 0.25     | 0.40   | 0.010 | 0.016 |

| L   | 4.90 BSC |        | 0.193 | BSC   |

| M   | 0°       | 6 °    | 0°    | 6°    |

## **PACKAGE DIMENSIONS**

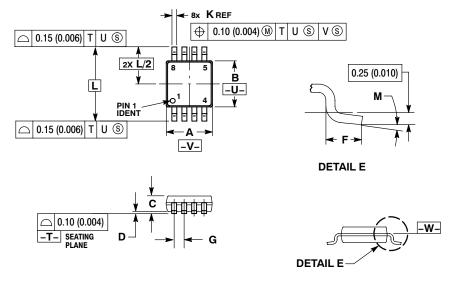

## SOEIAJ-14 CASE 965-01 **ISSUE A**

#### NOTES:

- DTES:

1. DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

2. CONTROLLING DIMENSION: MILLIMETER.

3. DIMENSIONS D AND E DO NOT INCLUDE MOLD FLASH OR PROTRUSIONS AND ARE MEASURED AT THE PARTING LINE. MOLD FLASH OR PROTRUSIONS SHALL NOT EXCEED 0.15 (0.006) PER SIDE.

4. TERMINAL NUMBERS ARE SHOWN FOR REFERENCE ONLY.

5. THE LEAD WIDTH DIMENSION (b) DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.08 (0.003) TOTAL IN EXCESS OF THE LEAD WIDTH DIMENSION AT MAXIMUM MATERIAL CONDITION. DAMBAR CANNOT BE LOCATED ON THE LOWER RADIUS OR THE FOOT. MINIMUM SPACE BETWEEN PROTRUSIONS AND ADJACENT LEAD MILLIMETERS INCHES

|                | MILLIN | IETERS | INC       | HES   |

|----------------|--------|--------|-----------|-------|

| DIM            | MIN    | MAX    | MIN       | MAX   |

| Α              |        | 2.05   |           | 0.081 |

| A <sub>1</sub> | 0.05   | 0.20   | 0.002     | 0.008 |

| b              | 0.35   | 0.50   | 0.014     | 0.020 |

| С              | 0.10   | 0.20   | 0.004     | 0.008 |

| D              | 9.90   | 10.50  | 0.390     | 0.413 |

| E              | 5.10   | 5.45   | 0.201     | 0.215 |

| е              | 1.27   | BSC    | 0.050 BSC |       |

| HE             | 7.40   | 8.20   | 0.291     | 0.323 |

| 0.50           | 0.50   | 0.85   | 0.020     | 0.033 |

| LE             | 1.10   | 1.50   | 0.043     | 0.059 |

| M              | 0 °    | 10 °   | 0 °       | 10 °  |

| Q <sub>1</sub> | 0.70   | 0.90   | 0.028     | 0.035 |

| z              |        | 1.42   |           | 0.056 |

#### PACKAGE DIMENSIONS

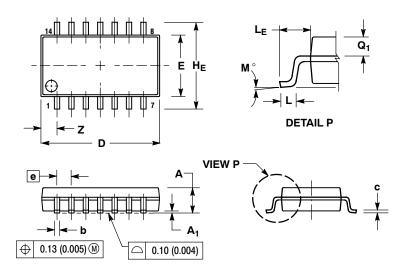

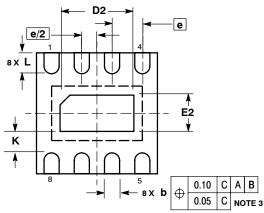

## DFN8 CASE 506AA-01 ISSUE D

- NOTES:

1. DIMENSIONING AND TOLERANCING PER

- ASME Y14.5M, 1994 .

CONTROLLING DIMENSION: MILLIMETERS.

DIMENSION & APPLIES TO PLATED

- TERMINAL AND IS MEASURED BETWEEN 0.25 AND 0.30 MM FROM TERMINAL

- COPLANARITY APPLIES TO THE EXPOSED PAD AS WELL AS THE TERMINALS.

|     | MILLIMETERS |          |  |  |  |  |

|-----|-------------|----------|--|--|--|--|

| DIM | MIN         | MAX      |  |  |  |  |

| Α   | 0.80        | 1.00     |  |  |  |  |

| A1  | 0.00        | 0.05     |  |  |  |  |

| А3  | 0.20 REF    |          |  |  |  |  |

| b   | 0.20        | 0.30     |  |  |  |  |

| D   | 2.00        | BSC      |  |  |  |  |

| D2  | 1.10        | 1.30     |  |  |  |  |

| Е   | 2.00        | BSC      |  |  |  |  |

| E2  | 0.70        | 0.90     |  |  |  |  |

| е   | 0.50        | 0.50 BSC |  |  |  |  |

| K   | 0.20        |          |  |  |  |  |

| L   | 0.25        | 0.35     |  |  |  |  |

ECLinPS is a trademark of Semiconductor Components INdustries, LLC (SCILLC).

**BOTTOM VIEW**

ON Semiconductor and 📖 are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. "Typical" parameters which may be provided in SCILLC data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. SCILLC does not convey any license under its patent rights nor the rights of others. SCILLC products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SCILLC product could create a situation where personal injury or death may occur. Should Buyer purchase or use SCILLC products for any such unintended or unauthorized application, Buyer shall indemnify and hold SCILLC and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that SCILLC was negligent regarding the design or manufacture of the part. SCILLC is an Equal Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner.

# **PUBLICATION ORDERING INFORMATION**

#### LITERATURE FULFILLMENT:

Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303-675-2175 or 800-344-3860 Toll Free USA/Canada

Fax: 303-675-2176 or 800-344-3867 Toll Free USA/Canada Email: orderlit@onsemi.com

N. American Technical Support: 800-282-9855 Toll Free

Europe, Middle East and Africa Technical Support: Phone: 421 33 790 2910 Japan Customer Focus Center

Phone: 81-3-5773-3850

ON Semiconductor Website: www.onsemi.com

Order Literature: http://www.onsemi.com/orderlit

For additional information, please contact your local Sales Representative

MC100EL1648/D