#### **FEATURES**

- Zero input-output propagation delay, adjustable by capacitive load on FBK input

- Multiple configurations, see "Available Configurations" table

- Multiple low-skew outputs

- 10 MHz to 134 MHz operating range

- Low cycle-to-cycle jitter

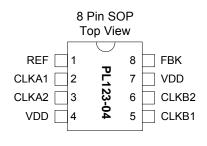

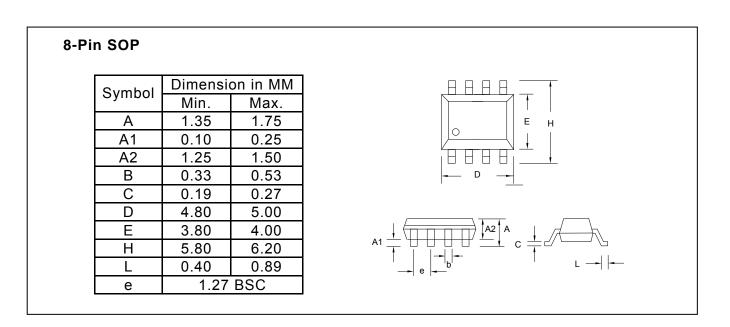

- 8 pin SOP package

- 3.3V operation

- Commercial and industrial temperature available

#### **DESCRIPTION**

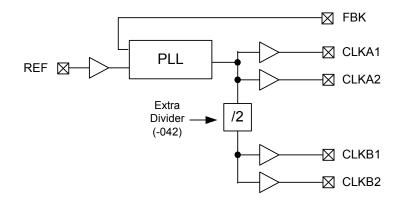

The PL123-04 is a PLL-based zero-delay buffer, used to distribute up to four outputs. An external feedback pin enables removing delay from external components. It also provides adjustable input-to-output delay by varying its loading relative to the output pin loading.

The PL123-042 option allows the user to obtain x1, x2, or x0.5 frequencies on the output bank. The exact multiplier depends on which output is connected to the FBK pin. Refer to the Available Configurations table below for more details

These parts are not intended for 5V input-tolerant applications.

#### **BLOCK DIAGRAM**

#### **AVAILABLE CONFIGURATIONS**

| Device    | Feedback From    | Bank A Frequency | Bank B Frequency |

|-----------|------------------|------------------|------------------|

| PL123-04  | Bank A or Bank B | Reference        | Reference        |

| PL123-042 | Bank A           | Reference        | Reference / 2    |

| PL123-042 | Bank B           | 2 x Reference    | Reference        |

### PIN DESCRIPTION

| Pin | Name                 | Туре | Description               |  |

|-----|----------------------|------|---------------------------|--|

| 1   | REF <sup>[1]</sup>   | I    | Input reference frequency |  |

| 2   | CLKA1 <sup>[2]</sup> | 0    | Clock output, Bank A      |  |

| 3   | CLKA2 <sup>[2]</sup> | 0    | Clock output, Bank A      |  |

| 4   | GND                  | Р    | Ground                    |  |

| 5   | CLKB1 <sup>[2]</sup> | 0    | Clock output, Bank B      |  |

| 6   | CLKB2 <sup>[2]</sup> | 0    | Clock output, Bank B      |  |

| 7   | VDD                  | Р    | 3.3V Supply               |  |

| 8   | FBK                  |      | PLL feedback input        |  |

Notes: 1: Weak pull-down.

2: Weak pull-down on all outputs.

The PLL's feedback path must be closed by connecting FBK to one of the available four outputs. The output driving the FBK pin will drive an (internal) pin load of 7pF plus any additional loading placed on this output pin.

For zero-delay applications, all outputs, including the FBK pin connected to an output pin, must be loaded equally. Varying the loading between the FBK pin and output pins can adjust the input-to-output delay.

#### **MAXIMUM RATINGS**

| Supply Voltage to Ground Potential           | 0.5V to 4.6V  |

|----------------------------------------------|---------------|

| DC Input Voltage (Except REF)0.5\            | to VDD+0.5V   |

| DC Input Voltage REF                         | 0.5V to 4.6V  |

| Storage Temperature                          | 65 to 150 °C  |

| Junction Temperature                         | 150 °C        |

| Static Discharge Voltage (MIL-STD-883, Metho | od 3015)> 2KV |

#### LAYOUT RECOMMENDATIONS

The following guidelines assist in optimizing a PCB design:

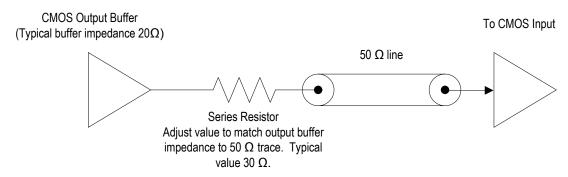

## Signal Integrity and Termination Considerations

- Keep traces short

- Trace = Inductor. Adding a capacitive load may cause ringing.

- Long trace = Transmission Line. Without proper termination this will cause reflections (causing

- Design long traces as "striplines" or "microstrips" with defined impedance.

- Terminate traces with characteristic impedance of the trace to avoid reflections (see figure below).

## **Decoupling and Power Supply Considerations**

- Place decoupling capacitors as close as possible to the VDD pin(s) to bypass noise from the power supply

- Multiple VDD pins should be decoupled separately for best performance.

- Value of decoupling capacitor is frequency dependant. Typical values to use are 0.1µF for designs supporting frequencies below 50MHz (0.01µF for designs supporting frequencies above 50MHz).

## **Typical CMOS termination** Place Series Resistor as close as possible to CMOS output

## **OPERATING CONDITIONS**

| Parameter       | Description                                                                                   | Min. | Max. | Unit |

|-----------------|-----------------------------------------------------------------------------------------------|------|------|------|

| $V_{DD}$        | Supply Voltage                                                                                | 3.0  | 3.6  | V    |

| _               | Commercial Operating Temperature (ambient temperature)                                        | 0    | 70   | °C   |

| T <sub>A</sub>  | Industrial Operating Temperature (ambient temperature)                                        | -40  | 85   | °C   |

| CL              | Load Capacitance, below 100 MHz                                                               | _    | 30   | pF   |

| OL              | Load Capacitance, above 100 MHz                                                               | _    | 15   | pF   |

| C <sub>IN</sub> | Input Capacitance [3]                                                                         | _    | 7    | pF   |

| t <sub>PU</sub> | Power-up time for all VDDs to reach minimum specified voltage (power ramps must be monotonic) | 0.05 | 50   | ms   |

Notes: 3: Applies to both REF clock and FBK inputs.

## **ELECTRICAL CHARACTERISTICS**

| Parameter     | Description                          | Test Conditions                            | Min. | Max.  | Unit |

|---------------|--------------------------------------|--------------------------------------------|------|-------|------|

| VIL           | Input LOW Voltage                    |                                            | _    | 0.8   | V    |

| VIH           | Input HIGH Voltage                   |                                            | 2.0  | _     | V    |

| IIL           | Input LOW Current                    | VIN = 0V                                   | _    | 50.0  | μA   |

| IIH           | Input HIGH Current                   | VIN = VDD                                  | _    | 100.0 | μA   |

| VOL           | Output LOW Voltage <sup>[4]</sup>    | IOL = 8 mA                                 | _    | 0.4   | V    |

| VOH           | Output HIGH Voltage <sup>[4]</sup>   | IOH = –8 mA                                | 2.4  | _     | V    |

| IDD (PD mode) | Power Down Supply Current            | REF = 0 MHz, Commercial Temp.              |      | 12.0  | μA   |

|               |                                      | REF = 0 MHz, Industrial Temp.              | _    | 25.0  | μA   |

|               |                                      | 100-MHz REF<br>Select inputs at VDD or GND | -    | 45.0  | mA   |

| IDD           | Supply Current<br>(Unloaded Outputs) | 66-MHz REF, Commercial Temp.               | _    | 32.0  | mA   |

|               |                                      | 33-MHz REF, Commercial Temp.               | -    | 18.0  | mA   |

|               |                                      | 66-MHz REF, Industrial Temp.               | _    | 35.0  | mA   |

|               |                                      | 33-MHz REF, Industrial Temp.               | _    | 20.0  | mA   |

Notes: 4. Parameter is guaranteed by design and characterization. Not 100% tested in production.

# SWITCHING CHARACTERISTICS [5]

| SWITCHING CHARACTERISTICS 1.                  |                                              |                                                                   |      |      |      |      |

|-----------------------------------------------|----------------------------------------------|-------------------------------------------------------------------|------|------|------|------|

| Pa-<br>rameter                                | Name                                         | Test Conditions                                                   |      | Тур. | Max. | Unit |

| t <sub>1</sub>                                | Output Frequency                             | 30-pF load                                                        |      | _    | 100  | MHz  |

| $t_1$                                         | Output Frequency                             | 15-pF load                                                        |      | _    | 134  | MHz  |

|                                               | Duty Cycle [4] = t2 ÷ t1                     | Measured at 1.4V, F <sub>OUT</sub> = 66.66 MHz 30-pF load         | 40.0 | 50.0 | 60.0 | %    |

|                                               | Duty Cycle [4] = t2 ÷ t1                     | Measured at 1.4V, F <sub>OUT</sub> <50.0 MHz 15-pF load           | 45.0 | 50.0 | 55.0 | %    |

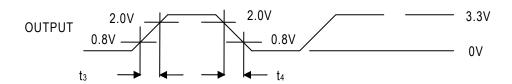

|                                               | Rise Time [4]                                | Measured between 0.8V and 2.0V, 30-pF load Commercial Temperature | _    | -    | 2.20 | ns   |

| t <sub>3</sub>                                |                                              | Measured between 0.8V and 2.0V, 30-pF load Industrial Temperature | -    | -    | 2.50 | ns   |

|                                               |                                              | Measured between 0.8V and 2.0V, 15-pF load                        | -    | _    | 1.50 | ns   |

|                                               |                                              | Measured between 0.8V and 2.0V, 30-pF load Commercial Temperature | -    | -    | 2.20 | ns   |

| t <sub>4</sub>                                | Fall Time [4]                                | Measured between 0.8V and 2.0V, 30-pF load Industrial Temperature |      | -    | 2.50 | ns   |

|                                               |                                              | Measured between 0.8V and 2.0V, 15-pF load                        | -    | -    | 1.50 | ns   |

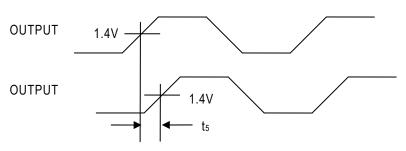

|                                               | Output to Output Skew on same Bank [4]       | All outputs equally loaded                                        | -    | -    | 200  | ps   |

| <b>t</b> <sub>5</sub>                         | Output Bank A to Output<br>Bank B Skew (-04) | All outputs equally loaded                                        | -    | -    | 200  | ps   |

| Output Bank A to Output<br>Bank B Skew (–042) |                                              | All outputs equally loaded                                        | ı    | -    | 400  | ps   |

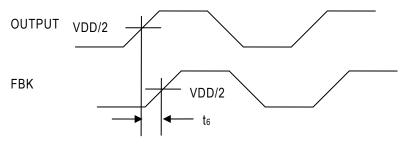

| t <sub>6</sub>                                | Skew, REF Rising Edge to FBK Rising Edge [4] | Measured at VDD/2                                                 |      | 0    | ±250 | ps   |

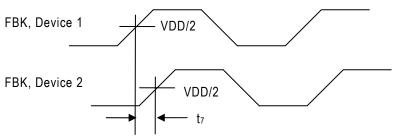

| t <sub>7</sub>                                | Device to Device Skew [4]                    | Measured at VDD/2 on the FBK pins of devices                      | -    | 0    | 500  | ps   |

| t <sub>J</sub>                                | Cycle to Cycle Jitter [4]<br>(-04)           | Measured at 66.67 MHz, loaded outputs, 15-pF load                 | _    | 90   | 175  | ps   |

|                                               |                                              | Measured at 66.67 MHz, loaded outputs, 30-pF load                 | -    | _    | 200  | ps   |

|                                               |                                              | Measured at 133.3 MHz, loaded outputs, 15-pF load                 | _    | _    | 100  | ps   |

| 1                                             | Cycle to Cycle Jitter [4]                    | Measured at 66.67 MHz, loaded outputs 30-pF load                  | _    | _    | 400  | ps   |

| t,                                            | (-042)                                       | Measured at 66.67 MHz, loaded outputs 15-pF load                  | _    | _    | 375  | ps   |

| t <sub>LOCK</sub>                             | PLL Lock Time [4]                            | Stable power supply, valid clocks presented on REF and FBK pins   | _    | _    | 1.0  | ms   |

Notes: 5. All parameters are specified with loaded outputs.

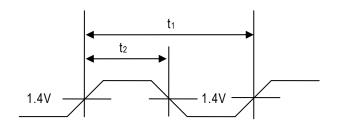

### **SWITCHING WAVEFORMS**

**Duty Cycle Timing**

All Outputs Rise/Fall Time

**Output-Output Skew**

**Input-Output Propagation Delay**

**Device-Device Skew**

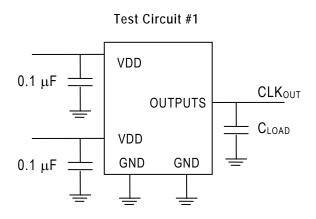

### **TEST CIRCUIT**

## PACKAGE DRAWINGS (GREEN PACKAGE COMPLIANT)

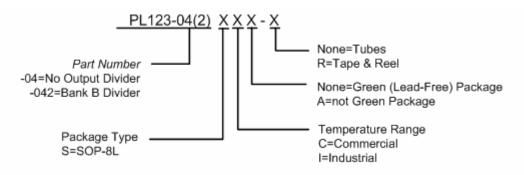

#### ORDERING INFORMATION

For part ordering, please contact our Sales Department: 47745 Fremont Blvd., Fremont, CA 94538, USA Tel: (510) 492-0990 Fax: (510) 492-0991

#### PART NUMBER

The order number for this device is a combination of the following: Part number, Package type and Operating temperature range

| Part/Order Number          | Marking  | Package Option            | Range      |  |  |

|----------------------------|----------|---------------------------|------------|--|--|

| Green (Lead-Free) Packages |          |                           |            |  |  |

| PL123-04SC                 | P123-04  | 8-Pin SOP Tube            | Commercial |  |  |

| PL123-04SC-R               | P123-04  | 8-Pin SOP (Tape and Reel) | Commercial |  |  |

| PL123-042SC                | P123-042 | 8-Pin SOP Tube            | Commercial |  |  |

| PL123-042SC-R              | P123-042 | 8-Pin SOP (Tape and Reel) | Commercial |  |  |

| PL123-04SI                 | P123-04  | 8-Pin SOP Tube            | Industrial |  |  |

| PL123-04SI-R               | P123-04  | 8-Pin SOP (Tape and Reel) | Industrial |  |  |

| PL123-042SIC               | P123-042 | 8-Pin SOP Tube            | Industrial |  |  |

| PL123-042SIC-R             | P123-042 | 8-Pin SOP (Tape and Reel) | Industrial |  |  |

|                            | Not Gr   | reen Packages             |            |  |  |

| PL123-04SCA                | P123-04  | 8-Pin SOP Tube            | Commercial |  |  |

| PL123-04SCA-R              | P123-04  | 8-Pin SOP (Tape and Reel) | Commercial |  |  |

| PL123-042SCA               | P123-042 | 8-Pin SOP Tube            | Commercial |  |  |

| PL123-042SCA-R             | P123-042 | 8-Pin SOP (Tape and Reel) | Commercial |  |  |

| PL123-04SIA                | P123-04  | 8-Pin SOP Tube            | Industrial |  |  |

| PL123-04SIA-R              | P123-04  | 8-Pin SOP (Tape and Reel) | Industrial |  |  |

| PL123-042SICA              | P123-042 | 8-Pin SOP Tube            | Industrial |  |  |

| PL123-042SICA-R            | P123-042 | 8-Pin SOP (Tape and Reel) | Industrial |  |  |

PhaseLink Corporation, reserves the right to make changes in its products or specifications, or both at any time without notice. The information furnished by Phaselink is believed to be accurate and reliable. However, PhaseLink makes no quarantee or warranty concerning the accuracy of said information and shall not be responsible for any loss or damage of whatever nature resulting from the use of, or reliance upon this product.

LIFE SUPPORT POLICY: PhaseLink's products are not authorized for use as critical components in life support devices or systems without the express written approval of the President of PhaseLink Corporation.

Solder reflow profile available at www.phaselink.com/QA/solderingGreen.pdf