# 11-BAND EVR FOR GRAPHIC EQUALIZER

#### GENERAL DESCRIPTION

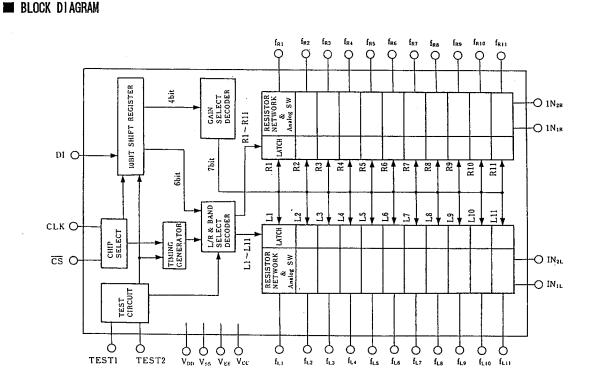

The NJU7307 is a electrical variable resistor (EVR) incorporated 11-band each for left and right channels, especially apply to the stereo type graphic equalizer.

It consists of input controller, channel/band/level selector, 22 latches and resistor network blocks of 11 bands each for left and right channels.

The boost and cut value for each band of each channel can be set independently to each other by the channel/ band/level selector controlled by external controller.

The maximum boost and cut range is  $\pm 18$ dB and the boost and cut value is adjusted by  $\pm 3dB$  step.

- 11 Bands Each for Left and Right Channels

- Stereo Application Graphic Equalizer Each Channel Independent Operation

- Maximum Boost and Cut --- ±18dB

- --- ±3dB Boost and Cut Step

- 10bit Serial Data for the Equalizing

- Flat Level Setting Function

- Operating Voltage --- 15V~30V

- SDIP 42/SOP 40 Package Outline

- C-MOS Technology

New Japan Radio Co., Ltd.

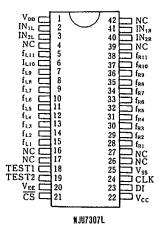

PACKAGE OUTLINE

NJU7307L

NJU7307G

-5-155

Downloaded from Elcodis.com electronic components distributor

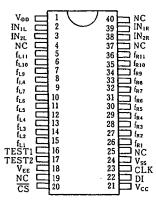

### PIN CONFIGURATION

NJU73076

## TERMINAL DESCRIPTION

| NO.      |          | SYMBOL                | FUNCTION                                                                 |  |  |  |

|----------|----------|-----------------------|--------------------------------------------------------------------------|--|--|--|

| NJU7307L | NJU7307G | STNDUL                | FUNCIIUN                                                                 |  |  |  |

| 1        | 1        | Vdd                   | Power source for Audio signal +15V                                       |  |  |  |

| 25       | 24       | Vss                   | GND OV                                                                   |  |  |  |

| 20       | 18       | Vee                   | Power source for Audio signal -15V                                       |  |  |  |

| 22       | 21       | Vcc                   | Power source for Logic +5.0V                                             |  |  |  |

| 2, 41    | 2,39     | Nil, Nir              | Audio signal input terminal. Connect to Op-amp inverting<br>terminal     |  |  |  |

| 3, 40    | 3,38     | N2L,   N2R            | Audio signal input terminal. Connect to Op-amp<br>non-inverting terminal |  |  |  |

| 5 to 15  | 5 to 15  | $f_{L1}$ to $f_{L11}$ | Band pass filter connecting terminal.                                    |  |  |  |

| 28 to 38 | 26 to 36 | $f_{R1}$ to $f_{R11}$ | ( 22 terminals for left/right)                                           |  |  |  |

| 18       | 16       | TEST1                 | Maker testing terminals.                                                 |  |  |  |

| 19       | 17       | TEST2                 | Normally (except the test) OPEN                                          |  |  |  |

| 21       | 20       | CS                    | Chip-select input.                                                       |  |  |  |

| 23       | 22       | DI                    | Serial data input.                                                       |  |  |  |

| 24       | 23       | CLK                   | Clock signal input.                                                      |  |  |  |

| 4,16,17  | 4,19,25  |                       |                                                                          |  |  |  |

| 26,27,39 | 37,40    | NC                    | Non connection                                                           |  |  |  |

| 42       |          |                       |                                                                          |  |  |  |

5

-New Japan Radio Co.,Ltd.

#### FUNCTIONAL DESCRIPTION

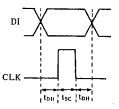

(1) Data set and code format

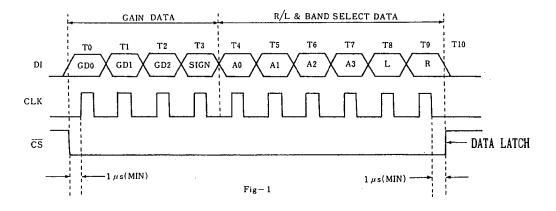

The setting of each band is performed by two signals of data and clock as shown in Fig.1. The 10 bits serial data including the information of channel selection (left/right), band selection and its gain are input from DI terminal.

The clock signal input from the CLK terminal shifts the serial data input form DI terminal into the shift register.

The data input from DI terminal is performed during the CS terminal is "L"level. Then the  $\overline{\text{CS}}$  terminal change from "L" to "H" level, the data in the shift register is latched to the latch.

All "H" of 10 bits code are special code to set OdB for all bands at once. This function is useful for Power On initialization or flat level setting.

< Data and Shift Clock >

The shift clock should be risen after 1 $\mu$ s from the data changing.  $t_{sc}=1\mu s(MIN)$  $t_{DH}=1\mu s(MIN)$

The  $\overline{\text{CS}}$  terminal should be "L" level during the data input. The setting data is latched at the edge of  $\overline{\text{CS}}$  signal rising. If the error data is latched, the correct data must be set again from the top.

New Japan Radio Co., Ltd.

Note: The clock line should be shielded from the noise.

#### < Data Format >

The data is input by the LSB first format as shown bellow. And the gain data GD2 to GD0, left/right and band selection data are also shown in bellow.

| MSB  |            |    |        |    | 11 | Byte |     |        | LSB |

|------|------------|----|--------|----|----|------|-----|--------|-----|

| R    | L          | A3 | A2     | A1 | AO | SIGN | GD2 | GD1    | GD0 |

| RIGH | RIGHT/LEFT |    | f1~f11 |    |    | +/-  |     | 0~18dB |     |

# GAIN DATA CODE

| GAIN              | SIGN | GD2 | GD1 | GD1_ |

|-------------------|------|-----|-----|------|

| 18                | 0    | 1   | 1   | 0    |

| 15                | 0    | 1   | 0   | 1    |

| 12                | 0    | 1   | 0   | 0    |

| 9                 | 0    | 0   | 1   | 1    |

| 6                 | 0    | 0   | 1   | 0    |

| 3                 | 0    | 0   | 0   | 1    |

| 0dB               | 0    | 0   | 0   | 0    |

| -3                | 1    | 0   | 0   | 1    |

| -6                | 1    | 0   | 1   | 0    |

| -9                | 1    | 0   | 1   | 1    |

| -12               | 1    | 1   | 0   | 0    |

| <u>-12</u><br>-15 | 1    | 1   | 0   | 1    |

| -18               | 1    | 1   | 1   | 0    |

| BAND SELECT DATA CODE |    |     |    |    |  |  |  |

|-----------------------|----|-----|----|----|--|--|--|

| BAND                  | A3 | A2  | A1 | A0 |  |  |  |

| f1                    | 0  | 0   | 0  | 1  |  |  |  |

| f2                    | 0  | • 0 | 1  | 0  |  |  |  |

| f3                    | 0  | 0   | 1  | 1  |  |  |  |

| f4                    | 0  | 1   | 0  | 0  |  |  |  |

| f5                    | 0  | 1   | 0  | 1  |  |  |  |

| f6                    | 0  | 1   | 1  | 0  |  |  |  |

| f7                    | 0  | 1   | 1  | 1  |  |  |  |

| f8                    | 1  | 0   | 0  | 0  |  |  |  |

| f9                    | 1  | 0   | 0  | 1  |  |  |  |

| f10                   | 1  | 0   | 1  | 0  |  |  |  |

| f11_                  | 1  | 0   | 1  | 1  |  |  |  |

R/L SELECT DATA CODE

| R/L          | R | <u> </u> |

|--------------|---|----------|

| RIGHT        | 1 | 0        |

| LEFT         | 0 | 1        |

| RIGHT & LEFT | 1 | 1        |

#### (2) Power on initialization

The NJU7307 is not incorporated the Power On Initialization Circuits, so that internal circuits are not defined when the power is turned on. Therefore, the flat setting operation are required as 10 bits of "H" data with 10 clock pulse input during the  $\overline{\text{CS}}$  terminal "L" state, then after change the  $\overline{\text{CS}}$  terminal level from "L" to "H".

The internal circuits of NJU7307 are initialized by the above operation, then the following input will be accepted.

# 5-158\_\_\_\_\_New Japan Radio Co.,Ltd.

(Ta=25℃)

# ABSOLUTE MAXIMUM RATINGS

|                       |         |                                                                               | (14-23 0) |  |

|-----------------------|---------|-------------------------------------------------------------------------------|-----------|--|

| PARAMETER             | SYMBOL  | R A T I N G S                                                                 | UNIT      |  |

|                       | Vdd-Vee | 34                                                                            | V         |  |

| Supply Voltage        | Vcc     | V <sub>ss</sub> ~V <sub>ss</sub> +7(V <sub>DD</sub> ≧V <sub>cc</sub> )        | V         |  |

|                       |         | $V_{ss}$ -0.3 $\sim V_{cc}$ +0.3 (D1,CLK, $\overline{CS}$ )                   | v         |  |

| Input Voltage         | VIN     | $V_{EE} = 0.3 \sim V_{DD} + 0.3 ( _{N1L} \sim  _{N2L},  _{N1R} \sim  _{N2R})$ | Ŷ         |  |

| Power Dissipation     | PD      | 250 (SDIP,SOP)                                                                | mW        |  |

| Operating Temperature | Topr    | -30 ~ +80                                                                     | Ĉ         |  |

| Storage Temperature   | Tstg    | -40 ~ +125                                                                    | C         |  |

### ELECTRICAL CHARACTERISTICS

$(V_{ss}=0V, V_{DD} \ge V_{cc} > V_{ss} \ge V_{EE}, Ta=25^{\circ}C)$

| PARAMETER           | SYMBOL  | CONDITIONS                                        | MIN    | ТҮР    | MAX    | UNIT |  |

|---------------------|---------|---------------------------------------------------|--------|--------|--------|------|--|

| Operating Voltage   | Vdd-Vee | V <sub>EE</sub> ≧-15V                             | 15     | 20     | 30     | v    |  |

| operating voltage   | Vac     |                                                   | 4.5    | 5.0    | 5.5    |      |  |

| Operating Current   | DD      | $V_{DD}-V_{EE}=30V$                               |        |        | 1      | mA   |  |

| operating current   | lcc     | Vcc=5V                                            |        |        | 0.5    | ШК   |  |

| Input Voltage       | Vih     | CLK, DI, <del>CS</del>                            | 0.8Vcc |        | Vcc    | V    |  |

| Input voitage       | VIL     | Terminals                                         | 0      |        | 0.2Vcc | ۷    |  |

| Input Pulse Width   | tpw     | CLK                                               | 1      |        |        | μS   |  |

| Setup Time          | tsu     | DI                                                | 1      |        |        | μS   |  |

| Holding Time        | tHLD    | DI                                                | 1      |        |        | μS   |  |

| Operating Frequency | forr    | CLK                                               |        |        | 330    | kHz  |  |

|                     | THD1    | Flat Status, f=20kHz                              |        | 0.005  | 0.01   |      |  |

| Total Harmonics     | THD2    | Flat Status, f= 1kHz                              |        | 0.0015 | 0.003  | %    |  |

| Distortion          | THD3    | Boost Status, f=20kHz                             |        | 0.05   | 0.10   |      |  |

|                     | THD4    | Boost Status, f= 1kHz                             |        | 0.015  | 0.03   |      |  |

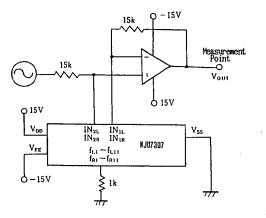

|                     | :       | (Circuit 1)                                       |        |        |        |      |  |

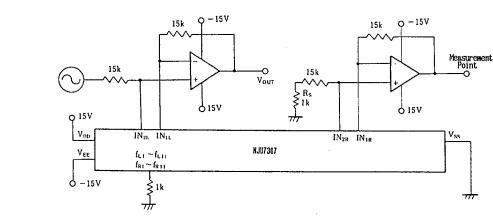

| Crosstalk           | CT      | f= 1kHz (Circuit 2)                               |        | 60     |        | dB   |  |

| Setting Error       | ∆B      | V <sub>DD</sub> -V <sub>EE</sub> =30V (Circuit 1) | -1     |        | 1      | dB   |  |

| Analog SW Off       |         | f <sub>L1</sub> ~f <sub>L11</sub>                 |        |        | 100    |      |  |

| Leakage Current     | loff    | f <sub>R1</sub> ~f <sub>R11</sub>                 |        |        |        | μA   |  |

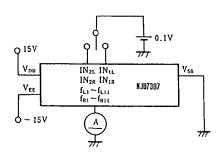

Note) The setting error of gain is specified by mesureing of Circuit 1 based on internal current flown on Circuit 3.

-New Japan Radio Co.,Ltd.-

Actual setting error of gain is affected by external circuit characteristics. Therefore, experimental operation is recommended when designing.

# NJU7307

# MEASUREMENT CIRCUITS

Circuit 1

# Circuit 2

Circuit 3

5

5-160-----New Japan Radio Co., Ltd.

-5-161

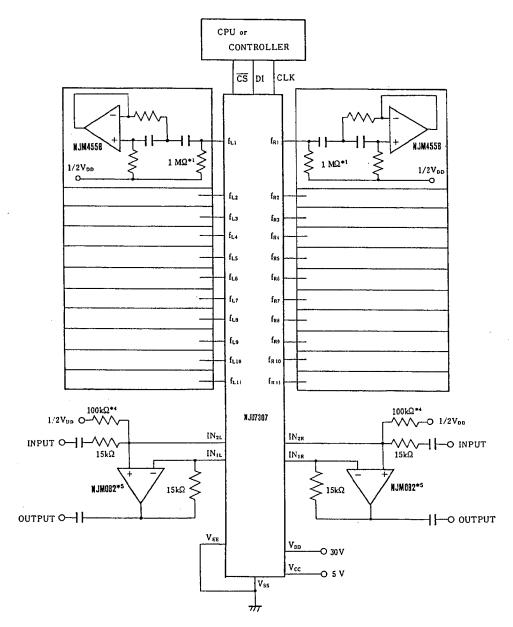

### APPLICATION CIRCUIT 1

< Single power supply operation >

- \*1) In order to reduce the pop-noise, connecting  $f_{L1} \sim f_{L11}$ ,  $f_{R1} \sim f_{R11}$  to 1/2  $V_{DD}$  by 1M $\Omega$  resistance is recommended.

- \*2) The best conditions for 3dB/step are as follows:  $V_{DD} = 30V$ OP-amp feedback resistance:  $15k\Omega$ .

- Equivalent LC resonant impedance:  $1k\Omega$

- \*3) TEST1 and TEST2 terminals are normally OPEN.

- \*4) In order to keep off noise input, connecting to 1/2  $V_{\text{DD}}$  by 100k $\Omega$  resistance is recommended.

New Japan Radio Co., Ltd.:

\*5) J-FET input OP-AMP is recommended.

# NJU7307

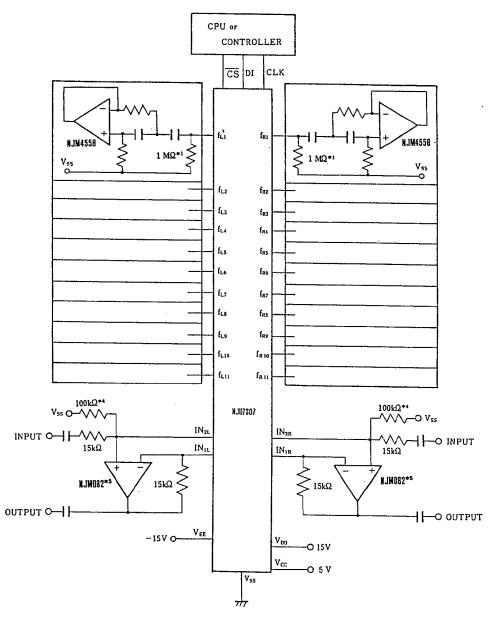

#### APPLICATION CIRCUIT 2

< Dual power supply operation >

- \*1) In order to reduce the pop-noise, connecting  $f_{L1} \sim f_{L11}$ ,  $f_{R1} \sim f_{R11}$  to  $V_{ss}$  by  $1M\Omega$  resistance is recommended.

- \*2) The best conditions for 3dB/step are as follows:  $V_{DD}$  = 15V,  $V_{EE}$  = -15V OP-amp feedback resistance: 15k $\Omega$ . Equivalent LC resonant impedance: 1k $\Omega$

- \*3) TEST1 and TEST2 terminals are normally used as OPEN.

- \*4) In order to keep off noise input, connecting to 1/2  $V_{\text{DD}}$  by 100k $\Omega$  resistance is recommended.

-New Japan Radio Co.,Ltd.

\*5) J-FET input OP-AMP is recommended.

Downloaded from Elcodis.com electronic components distributor

5-162-

5

**MEMO**

[CAUTION] The specifications on this databook are only given for information , without any guarantee as regards either mistakes or omissions. The application circuits in this databook are described only to show representative usages of the product and not intended for the guarantee or permission of any right including the industrial rights.

New Japan Radio Co.,Ltd.