# **PM7312**

# **FREEDM 32A1024L**

# Frame Engine and Data Link Manager 32A1024L

**Data Sheet**

Released

Issue 2:

## **Legal Information**

## Copyright

Copyright 2003 PMC-Sierra, Inc. All rights reserved.

The information in this document is proprietary and confidential to PMC-Sierra, Inc., and for its customers' internal use. In any event, no part of this document may be reproduced or redistributed in any form without the express written consent of PMC-Sierra, Inc.

PMC-2021833 (R2)

#### **Disclaimer**

None of the information contained in this document constitutes an express or implied warranty by PMC-Sierra, Inc. as to the sufficiency, fitness or suitability for a particular purpose of any such information or the fitness, or suitability for a particular purpose, merchantability, performance, compatibility with other parts or systems, of any of the products of PMC-Sierra, Inc., or any portion thereof, referred to in this document. PMC-Sierra, Inc. expressly disclaims all representations and warranties of any kind regarding the contents or use of the information, including, but not limited to, express and implied warranties of accuracy, completeness, merchantability, fitness for a particular use, or non-infringement.

In no event will PMC-Sierra, Inc. be liable for any direct, indirect, special, incidental or consequential damages, including, but not limited to, lost profits, lost business or lost data resulting from any use of or reliance upon the information, whether or not PMC-Sierra, Inc. has been advised of the possibility of such damage.

#### **Trademarks**

PMC-Sierra, FREEDM 32A1024L, Any-PHY, SPECTRA-622, and TEMUX-84 are trademarks of PMC-Sierra, Inc. Other product and company names mentioned herein may be the trademarks of their respective owners.

#### **Patents**

#### Granted

The technology discussed in this document is protected by one or more of the following patent grants:

U.S. Patent Nos. 5,640,398, 6,188,699, 6,333,935 and 6,584,521

Can. Patent Nos. 2,161,921, 2,224,392 and 2,234,493

Other relevant patent grants may also exist.

# **Contacting PMC-Sierra**

PMC-Sierra 8555 Baxter Place Burnaby, BC Canada V5A 4V7

Tel: +1 (604) 415-6000 Fax: +1 (604) 415-6200

Document Information: <a href="mailto:document@pmc-sierra.com">document@pmc-sierra.com</a>

Corporate Information: <a href="mailto:info@pmc-sierra.com">info@pmc-sierra.com</a>

Technical Support: <a href="mailto:apps@pmc-sierra.com">apps@pmc-sierra.com</a>

Web Site: <a href="mailto:http://www.pmc-sierra.com">http://www.pmc-sierra.com</a>

# **Revision History**

| Issue No. | Issue Date   | Details of Change                                                                                                              |

|-----------|--------------|--------------------------------------------------------------------------------------------------------------------------------|

| 2         | October 2003 | Released version. Addresses various documentation issues, including those discussed in issue 2 of the device prototype errata. |

|           |              | Change bars reflect differences between issue 1 and issue 2 of the data sheet.                                                 |

| 1         | July 2003    | First Issue                                                                                                                    |

# **Table of Contents**

| Leg  | jal Info | ormation                       |                                               | 2  |

|------|----------|--------------------------------|-----------------------------------------------|----|

|      | Сору     | right                          |                                               | 2  |

|      | Discla   | aimer                          | O                                             | 2  |

|      | Trade    | emarks                         | <u>6,                                    </u> | 2  |

|      | Pater    | nts                            |                                               | 2  |

| Coı  | ntactin  | g PMC-Sierra                   |                                               | 3  |

|      |          | History                        |                                               |    |

| Tab  | le of C  | Contents                       |                                               | 5  |

| List | of Re    | gisters                        |                                               | 8  |

|      |          | gures                          |                                               |    |

| List | of Tal   | bles                           | 1                                             | 4  |

| 1    | Defin    | itions                         | 1                                             | 16 |

| 2    | Featu    | ıres                           | 1                                             | 8  |

|      | 2.1      | Interfaces                     |                                               |    |

|      | 2.2      | Channelization / HDLC Features | 1                                             | 8  |

|      | 2.3      | PPP Features                   |                                               |    |

|      | 2.4      | Frame Relay Features           |                                               |    |

|      | 2.5      | Statistics                     |                                               |    |

|      | 2.6      | Fault Isolation Features       |                                               |    |

|      | 2.7      | Technologies                   | 2                                             | 21 |

| 3    | Applio   | cations                        |                                               |    |

| 4    |          | rences                         |                                               |    |

|      | 4.1      | PPP                            |                                               |    |

|      | 4.2      | Frame Relay                    |                                               |    |

|      | 4.3      | HDLC Standards                 |                                               |    |

|      | 4.4      | Misc. References               | 2                                             | 23 |

| 5    | Applio   | cation Examples                | 2                                             | 25 |

| 6    |          | Diagram                        |                                               |    |

| 7    |          | ription                        |                                               |    |

| 8    |          | viagram                        |                                               |    |

| 9    |          | pescription                    |                                               |    |

| 10   |          | tional Description             |                                               |    |

| -    |          | Interfaces                     |                                               |    |

|      |          | Memory Port                    |                                               |    |

|      |          | Packet Walkthrough             |                                               |    |

|    | 10.4  | Loop Back                                | 62  |

|----|-------|------------------------------------------|-----|

|    | 10.5  | Initialization Process                   | 62  |

|    | 10.6  | Any-PHY Tear Down Procedure              | 63  |

|    | 10.7  | CI Tear Down Procedure                   | 64  |

|    | 10.8  | Restrictions on Any-PHY to CI Mapping    | 64  |

|    |       | Block Descriptions                       |     |

| 11 | Norm  | nal Mode Register Description            | 95  |

|    | 11.1  | Microprocessor Accessible Registers      | 95  |

|    | 11.2  | Microprocessor Accessible Memories       | 227 |

| 12 |       | Features Description                     |     |

|    | 12.1  | Test Mode Registers                      | 247 |

|    | 12.2  | JTAG Test Port                           | 247 |

| 13 | Oper  | ation                                    | 249 |

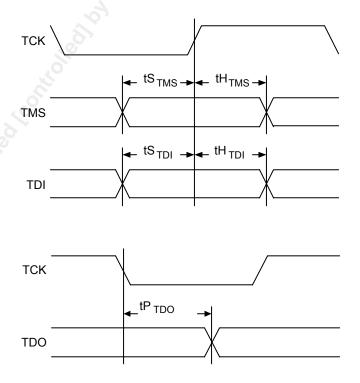

|    | 13.1  | JTAG Support                             | 249 |

| 14 | Func  | tional Timing                            | 253 |

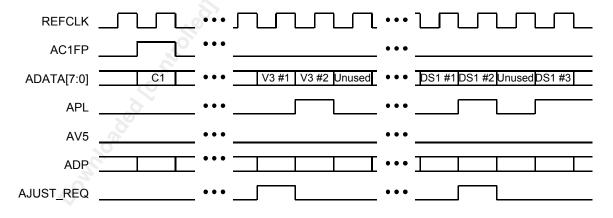

|    | 14.1  | SBI Drop Bus Interface Timing            | 253 |

|    | 14.2  | SBI Add Bus Interface Timing             | 253 |

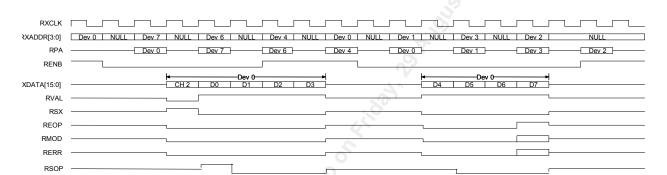

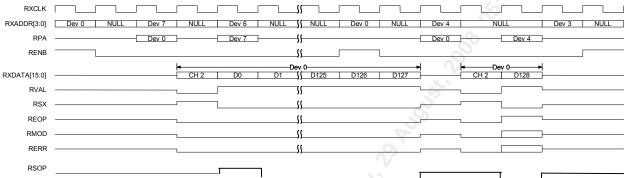

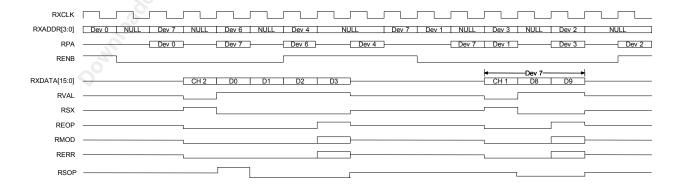

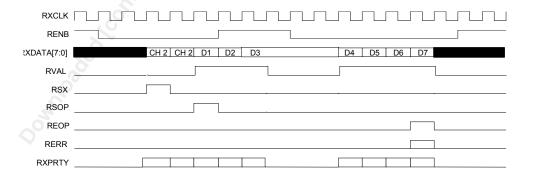

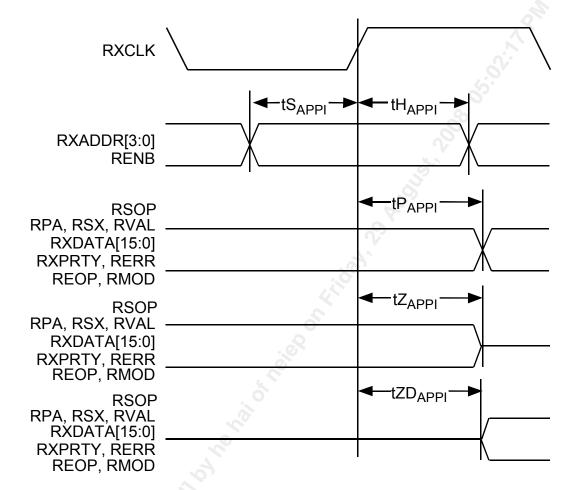

|    | 14.3  | Receive APPI Timing (Any-PHY Level 2)    | 254 |

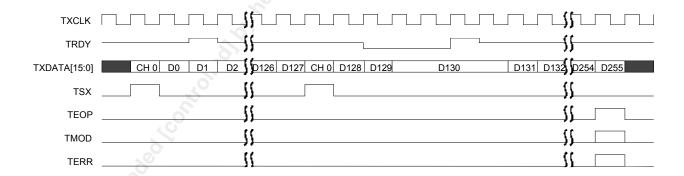

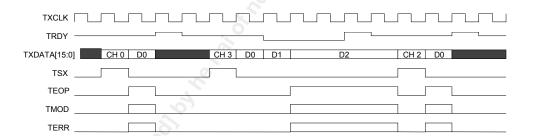

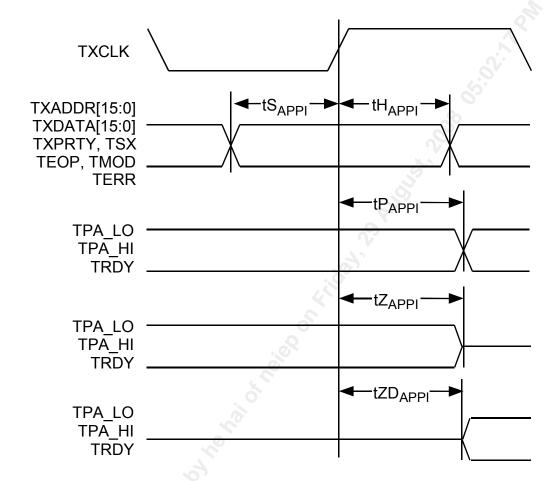

|    | 14.4  | Transmit APPI Timing (Any-PHY Level 2)   | 257 |

|    | 14.5  | Receive APPI Timing (Any-PHY Level 3)    | 259 |

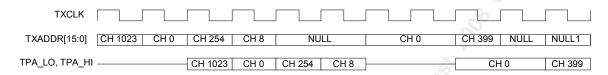

|    | 14.6  | Transmit APPI Timing (Any-PHY Level 3)   | 260 |

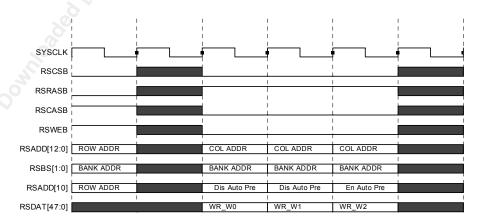

|    | 14.7  | Re-Sequencing SDRAM Interface            | 262 |

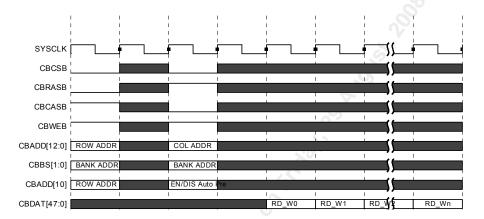

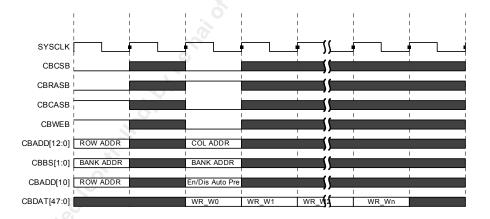

|    | 14.8  | Chunk Buffer SDRAM Interface             | 263 |

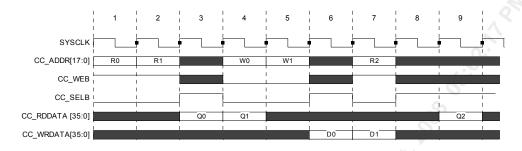

|    | 14.9  | Context SSRAM Interface (ZBT SSRAM mode) | 263 |

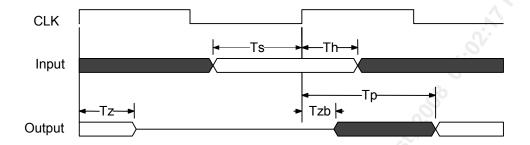

|    | 14.10 | Microprocessor Interface                 | 264 |

| 15 | Abso  | lute Maximum Ratings                     | 267 |

| 16 | Norm  | nal Operating Conditions                 | 268 |

| 17 | Powe  | er Information                           | 269 |

|    | 17.1  | Power Requirements                       | 269 |

|    | 17.2  | Power Sequencing                         | 269 |

|    | 17.3  | Power Supply Filtering                   | 270 |

| 18 | D.C.  | Characteristics                          | 271 |

| 19 | A.C.  | Timing Characteristics                   | 272 |

|    | 19.1  | SBI Bus Interface Timing                 | 272 |

|    | 19.2  | SBI Add Bus Interface Timing             | 273 |

|    | 19.3  | Any-PHY Timing                           | 275 |

|    | 19.4  | Microprocessor Timing                    | 277 |

|    | 19.5  | Memory Timing                            | 278 |

|----|-------|------------------------------------------|-----|

|    | 19.6  | JTAG Timing                              | 279 |

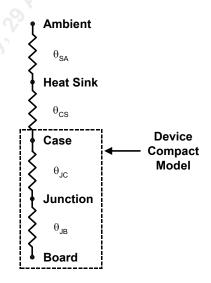

| 20 | Therr | mal Information                          | 280 |

|    | 20.1  | Central Office Environment – No Heatsink | 280 |

|    |       | Outside Plant Environment                |     |

| 21 | Mech  | anical Information                       | 282 |

| Nο | tes   |                                          | 283 |

# **List of Registers**

| Register 0x000: Master Reset and Control                                        | 96  |

|---------------------------------------------------------------------------------|-----|

| Register 0x004: FREEDM 32A1024L Master High Priority Interrupt Enable           | 98  |

| Register 0x008: Master High Priority Interrupt Status                           | 99  |

| Register 0x00C: Master Clock / Frame Pulse Activity Monitor                     |     |

| Register 0x018: Master Low Priority Interrupt Enable                            | 106 |

| Register 0x01C: Master Low Priority Interrupt Status                            | 107 |

| Register 0x020: Miscellaneous Control                                           | 110 |

| Register 0x048: SBI DROP BUS Master Configuration                               | 111 |

| Register 0x04C: SBI ADD BUS Master Configuration                                |     |

| Register 0x068: DLL Configuration                                               |     |

| Register 0x06C: DLL Vernier Control                                             |     |

| Register 0x070: DLL Delay Tap Status                                            | 115 |

| Register 0x074: DLL Control Status                                              | 116 |

| Register 0x100: RCAS Indirect Context RAM Link Select                           | 118 |

| Register 0x104: RCAS Indirect Context RAM Data                                  | 120 |

| Register 0x108: RCAS Indirect Channel Provision RAM Link Select                 | 121 |

| Register 0x10C: RCAS Indirect Channel Provision RAM Timeslot and Control Select | 122 |

| Register 0x110: RCAS Indirect Channel Data and Loop Back Enable                 |     |

| Register 0x200: RHDL Indirect Channel Select                                    | 125 |

| Register 0x204: RHDL Indirect Channel Data Register #1                          | 127 |

| Register 0x208: RHDL Indirect Channel Data Register #2                          | 129 |

| Register 0x210: RHDL Indirect Block Select                                      | 131 |

| Register 0x214: RHDL Indirect Block Data                                        | 132 |

| Register 0x220: RHDL Configuration                                              | 133 |

| Register 0x224: RHDL Maximum Packet Length                                      | 134 |

| Register 0x380: THDL Indirect Channel Select                                    | 135 |

| Register 0x384: THDL Indirect Channel Data #1                                   | 136 |

| Register 0x388: THDL Indirect Channel Data #2                                   | 138 |

| Register 0x38C: THDL Indirect Channel Data #3                                   | 140 |

| Register 0x390: THDL Indirect Channel Data Register #4                          | 144 |

| Register 0x394: THDL Indirect Channel Data Register #5                          | 146 |

| Register 0x398: THDL Indirect Channel Data Register #6                          | 147 |

| Register 0x3A0: THDL Indirect Block Select                                      | 148 |

| Register 0x3A4: THDL Indirect Block Data                                        | 149 |

| Register 0x3B0: THDL Configuration                                              | 150 |

|---------------------------------------------------------------------------------|-----|

| Register 0x400: TCAS Indirect Context RAM Link Select                           | 151 |

| Register 0x404: TCAS Indirect Context RAM Data                                  | 153 |

| Register 0x408: TCAS Indirect Channel Provision RAM Select                      | 154 |

| Register 0x40C: TCAS Indirect Channel Provision RAM Timeslot and Control Select | 155 |

| Register 0x410: TCAS Indirect Channel Data enable                               | 156 |

| Register 0x418: TCAS Idle Time-slot Fill Data                                   | 157 |

| Register 0x580: RAPI Control Register                                           | 158 |

| Register 0x584: RAPI Device Base Address Register                               | 160 |

| Register 0x588: RAPI Channel Base Address Register                              |     |

| Register 0x58C: RAPI Status Register                                            |     |

| Register 0x5C0: SBI EXTRACT Control                                             | 163 |

| Register 0x5D4: SBI EXTRACT Tributary Indirect Access Address                   | 164 |

| Register 0x5DC: SBI EXTRACT Tributary RAM Indirect Access Data                  | 166 |

| Register 0x5E0H: SBI EXTRACT SBI SPE Configuration Register                     | 167 |

| Register 0x600H: TAPI Control Register                                          | 168 |

| Register 0x604: TAPI Indirect Channel Provisioning Register                     | 170 |

| Register 0x608: TAPI Indirect Channel Data Register                             | 171 |

| Register 0x60C: TAPI Reserved Register                                          | 173 |

| Register 0x610: TAPI Status Register                                            | 174 |

| Register 0x614: TAPI Base Address Register                                      | 175 |

| Register 0x618: TAPI Range Address Register                                     | 176 |

| Register 0x680: SBI INSERT Control                                              | 177 |

| Register 0x68C: SBI INSERT T1 Frame Pulse Offset Register                       | 178 |

| Register 0x690: SBI INSERT E1 Frame Pulse Offset                                | 179 |

| Register 0x694: SBI INSERT Tributary Indirect Access Address                    | 180 |

| Register 0x69C: SBI INSERT Tributary Indirect Access Data                       | 182 |

| Register 0x6A0: SBI INSERT SBI SPE Configuration Register                       | 184 |

| Register 0x800: Memory Port Control                                             | 185 |

| Register 0x804-0x810: Memory Write Data N, N=03 (Burstable)                     | 187 |

| Register 0x814: Memory Write Data Overflow 1 (Burstable)                        | 188 |

| Register 0x818: Memory Write Data Overflow 2 (Burstable)                        | 189 |

| Register 0x81C-0x828: Memory Read Data N, N=03 (Burstable)                      | 190 |

| Register 0x82C: Memory Read Data Overflow 1 (Burstable)                         | 191 |

| Register 0x830: Memory Read Data Overflow 2 (Burstable)                         | 192 |

| Register 0x884: Unexpected SN CI (USNCI)                                        | 193 |

| Register 0x888: Lost SN CI (LSNCI)                                       | 194 |

|--------------------------------------------------------------------------|-----|

| Register 0x88C: SRAM Parity Error Address (SPERRADD)                     | 195 |

| Register 0x890: Excessive number of Fragments CI (ENFCI)                 | 196 |

| Register 0x894: Chunk Buffer Lower Threshold Exceeded Channel (CBLTEXCH) | 197 |

| Register 0x898: Auto Do Not Re-Sequence CI (AUTODRICI)                   |     |

| Register 0x900 CB_DRAMC Status and Control Register                      |     |

| Register 0x904: CB_DRAMC_COECCE Register                                 |     |

| Register 0x908: CB_DRAMC_UNCOECCE Register                               |     |

| Register 0x918 RS_DRAMC Status and Control Register                      |     |

| Register 0x91C: RS_DRAMC_COECCE Register                                 |     |

| Register 0x920: RS_DRAMC_UNCOECCE Register                               |     |

| Register 0x9A0: BIST Controller                                          |     |

| Register 0x9A4: BIST Enable                                              |     |

| Register 0x9A8: BIST Result                                              |     |

| Register 0x9AC: BIST End                                                 | 210 |

| Register 0x9B0: EXSBI BIST ERROR                                         |     |

| Register 0x9B4: INSBI BIST ERROR                                         |     |

| Register 0x9B8: RCAS-12 BIST ERROR                                       | 213 |

| Register 0x9BC: TCAS-12 BIST ERROR                                       | 214 |

| Register 0x9C0: RHDL-12 BIST ERROR                                       | 215 |

| Register 0x9C4: THDL-12 BIST ERROR                                       | 216 |

| Register 0x9C8: PM-12 BIST ERROR                                         | 217 |

| Register 0x9CC: RFRAG BIST ERROR                                         | 218 |

| Register 0x9D0: TFRAG BIST ERROR                                         | 219 |

| Register 0x9D4: RS_DRAMC BIST ERROR                                      | 220 |

| Register 0x9D8: CB_DRAMC BIST ERROR                                      | 221 |

| Register 0x9DC: IQM-12 BIST ERROR                                        | 222 |

| Register 0x9E0: EQM-12 BIST ERROR                                        | 223 |

| Register 0x9E4: FRMBLD BIST ERROR                                        | 224 |

| Register 0x9E8: RAPI-12 BIST ERROR                                       | 225 |

| Register 0x9EC: TAPI-12 BIST ERROR                                       | 226 |

# **List of Figures**

| Figure 1 32xT1/E1 Access Card for a Router                                                                                                                 | 25 |

|------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| Figure 2 Block Diagram of FREEDM 32A1024L                                                                                                                  | 26 |

| Figure 3 Pin Diagram                                                                                                                                       | 28 |

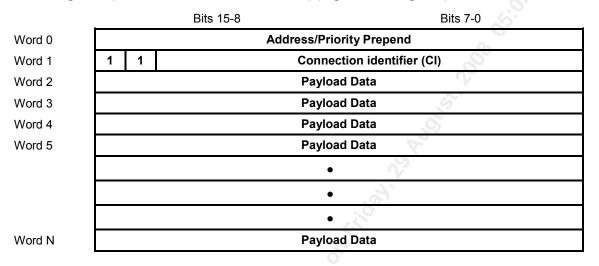

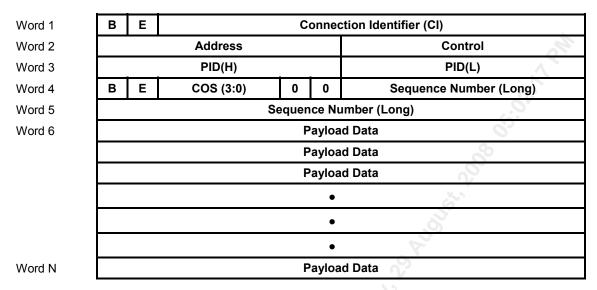

| Figure 4 Any-PHY Level 2 Mode Header Segment Transfer – Non Sequenced PPP or FR Datagrams (i.e. Control, LCP, NCP Packets) (Ingress and Egress)            |    |

| Figure 5 Any-PHY Level 2 Mode Segment Transfer – PPP/FR Non-Header Segment (i.e. Not First Segment of a Datagram) or Transparent Mode (Ingress and Egress) | 54 |

| Figure 6 Any-PHY Level 2 Mode Header Segment – PPP (Ingress and Egress)                                                                                    |    |

| Figure 7 Any-PHY Level 2 Mode Header Segment – FR (Ingress and Egress)                                                                                     |    |

| Figure 8 Any-PHY Level 2 Mode Header Segment – ML-PPP Fragment Out Mode (Ingress Only)                                                                     |    |

| Figure 9 Any-PHY Level 2 Mode Header Segment – PPP With Address and Control Field Header Compression (Ingress and Egress)                                  | 56 |

| Figure 10 Any-PHY Level 2 Mode Header Segment – PPP With PID Header Compression (Ingress and Egress)                                                       | 56 |

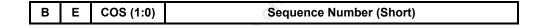

| Figure 11 Any-PHY Level 2 Mode Header Segment – PPP With Address/Control Field and PID Header Compression (Ingress and Egress)                             | 57 |

| Figure 12 Any-PHY Level 3 Mode Segment Transfer – PPP/FR Non-Header Segment or Transparent Mode (Ingress and Egress)                                       | 58 |

| Figure 13 Any-PHY Level 3 Mode Header Segment – FR (Ingress and Egress)                                                                                    | 58 |

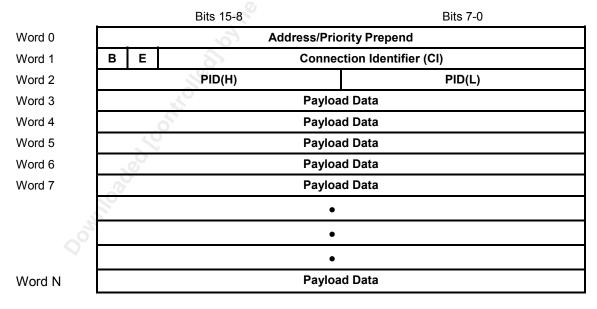

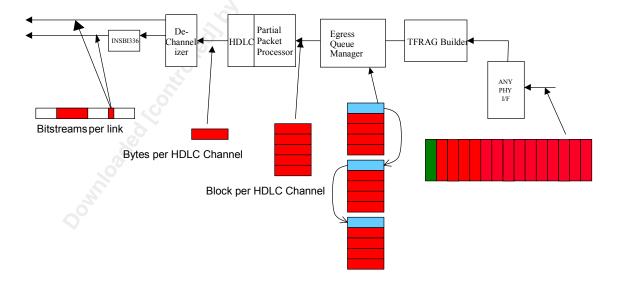

| Figure 14 Ingress Data Flow                                                                                                                                | 60 |

| Figure 15 Egress Data Flow                                                                                                                                 | 61 |

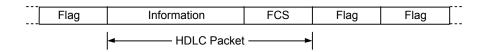

| Figure 16 HDLC Frame                                                                                                                                       | 66 |

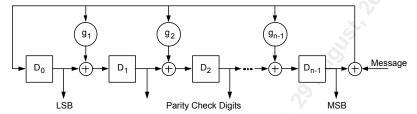

| Figure 17 CRC Generator                                                                                                                                    | 67 |

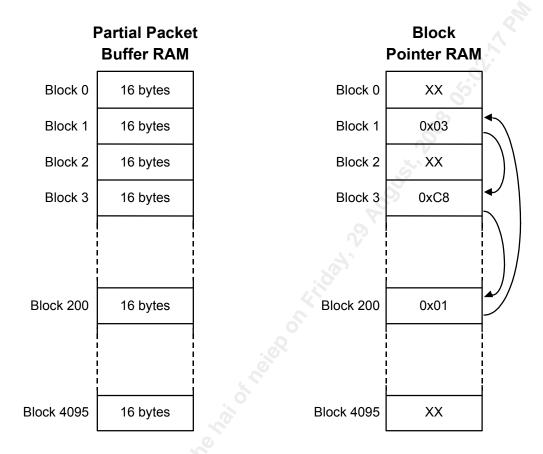

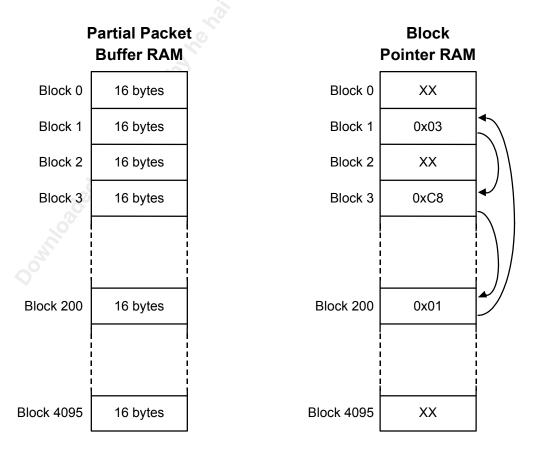

| Figure 18 Partial Packet Buffer Structure                                                                                                                  | 68 |

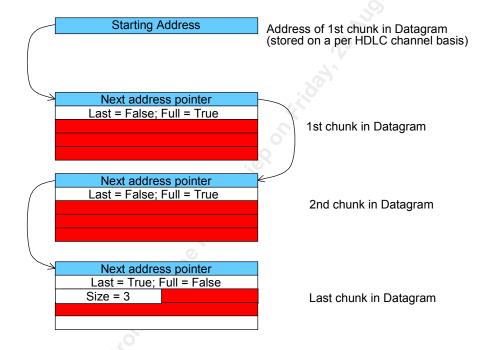

| Figure 19 Encapsulated Chunk Structures (Full = True)                                                                                                      | 70 |

| Figure 20 Encapsulated Chunk Structure (Full = False)                                                                                                      | 70 |

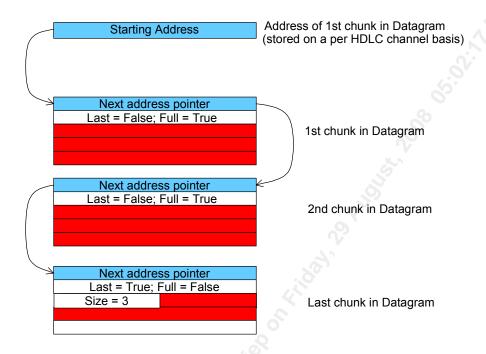

| Figure 21 Linked List Data Structure of a Datagram                                                                                                         | 71 |

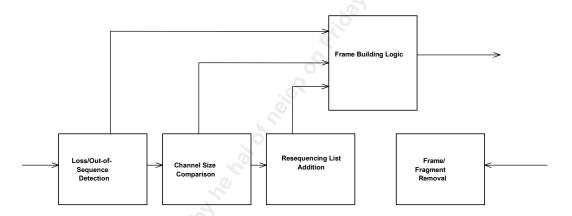

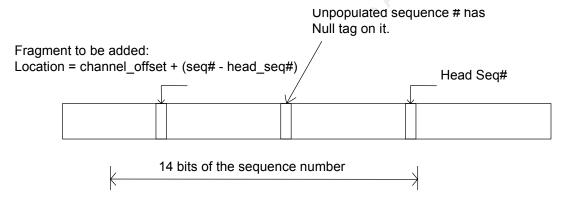

| Figure 22 Elements in the Re-sequencing Block                                                                                                              |    |

| Figure 23 14-bit Sliding Window Used for Re-sequencing                                                                                                     | 73 |

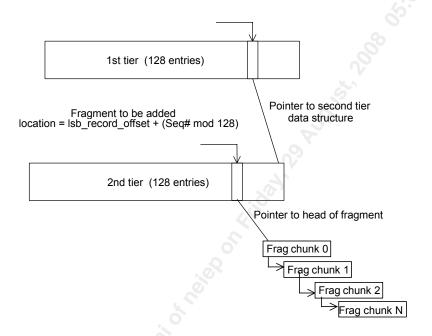

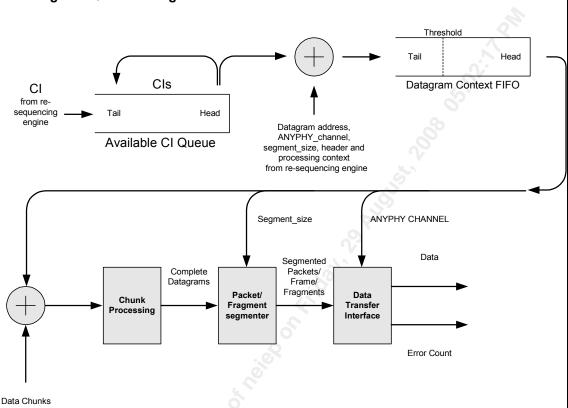

| Figure 24 Elements in the Re-sequencing Block                                                                                                              | 74 |

| Figure 25 - Ingress Queue Manager                                                                                                                          | 76 |

| Figure 26 Encapsulated Chunk Structure (Full = True)                                                                                                       |    |

| Figure 27 Encapsulated Chunk Structure (Full = False)                                                                                                      |    |

| Figure 28 Linked List Data Structure of a Datagram                                                                                                         |    |

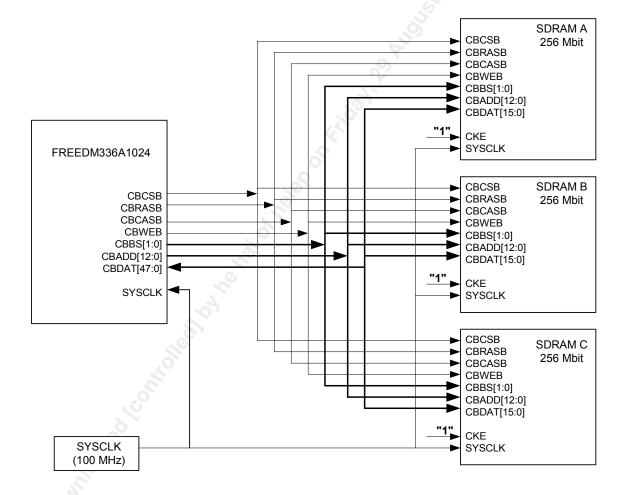

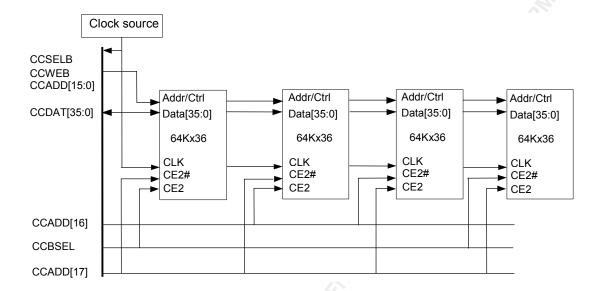

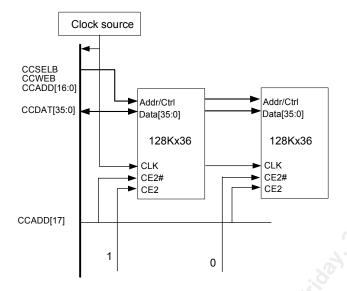

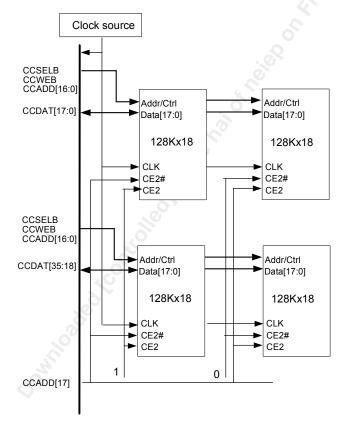

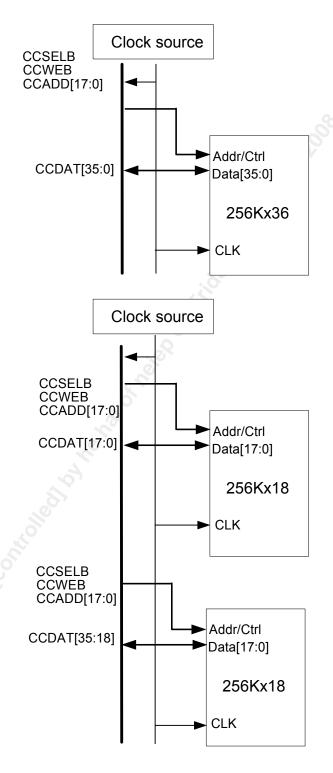

| Figure 29 DRAM Configuration for the Chunk Buffer Interface                                                                                                |    |

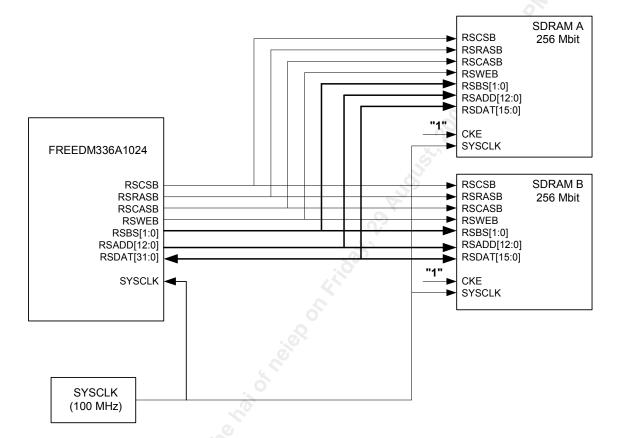

| Figure 30 DRAM Configuration for the Re-Sequencing Memory Interface                                                                                        |    |

| Figure 31 | 4-Bank Configuration for 8 MB of ZBT or Standard SSRAM              | 83  |

|-----------|---------------------------------------------------------------------|-----|

|           | 2-Bank Configuration for Eight Mbit/s of ZBT-Compatible or Standard |     |

|           | M                                                                   |     |

| •         | 1-Bank Configuration for Eight Mbit/s of ZBT or Standard SSRAM      |     |

| •         | Partial Packet Buffer Structure                                     |     |

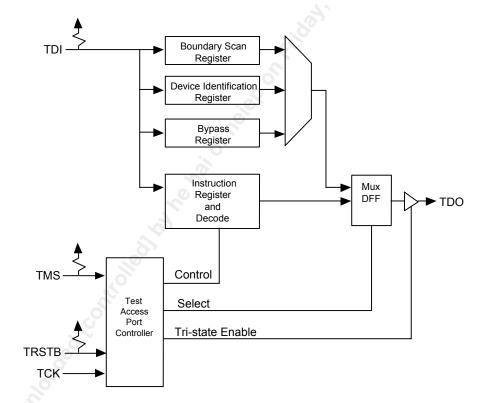

|           | Boundary Scan Architecture                                          |     |

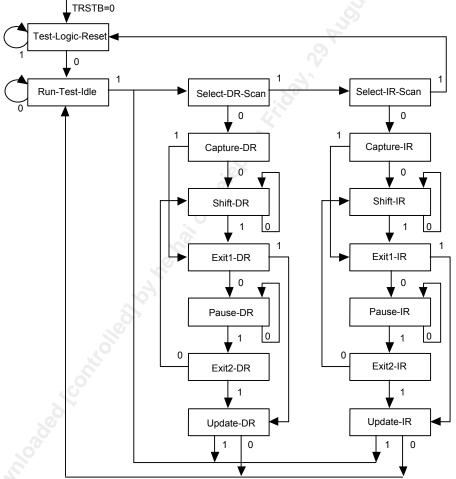

|           | TAP Controller Finite State Machine                                 |     |

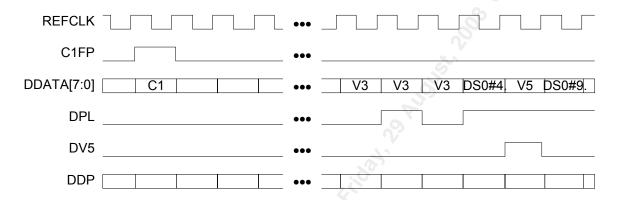

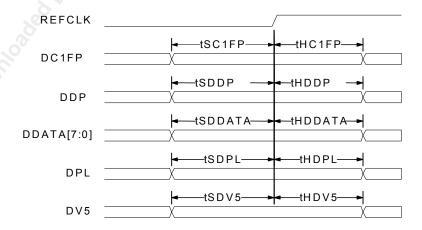

| Figure 37 | T1/E1 Drop Bus Functional Timing                                    | 253 |

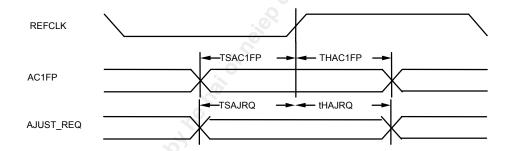

| Figure 38 | T1/E1 Add Bus Adjustment Request Functional Timing                  | 253 |

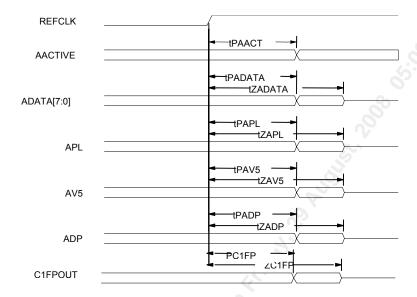

| Figure 39 | Receive APPI Timing (Normal Transfer 16 bit 52 MHz)                 | 254 |

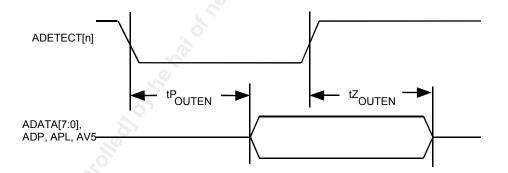

|           | Receive APPI Timing (Auto Deselection)                              |     |

| Figure 41 | Receive APPI Timing (Optimal Reselection)                           | 256 |

| Figure 42 | Receive APPI Timing (Boundary Condition)                            | 256 |

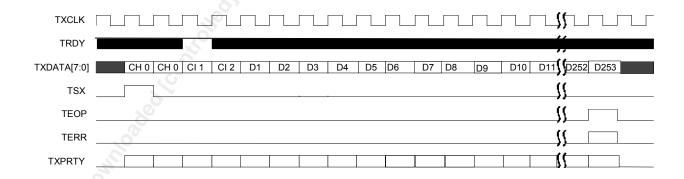

| Figure 43 | Transmit APPI Timing (Normal Transfer)                              | 257 |

| Figure 44 | Transmit APPI Timing (Special Conditions)                           | 258 |

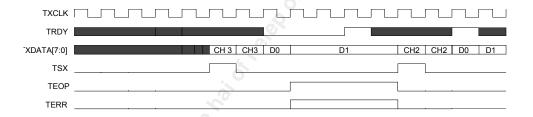

| Figure 45 | Transmit APPI Poll Timing                                           | 259 |

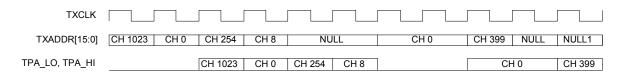

| Figure 46 | Receive APPI Timing (Normal Transfer 8 bit 104 MHz)                 | 259 |

| Figure 47 | Transmit APPI Timing Any-PHY Level 3 (Normal Transfer)              | 260 |

| Figure 48 | Transmit APPI Timing Any-PHY Level 3 (Special Condition)            | 261 |

| Figure 49 | Transmit APPI Polling Timing (Any-PHY Level 3)                      | 261 |

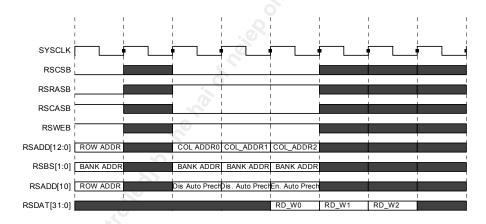

| Figure 50 | Read Timing for Re-Sequencing Memory                                | 262 |

| Figure 51 | Write Timing Re-Sequencing Memory                                   | 262 |

| Figure 52 | Read Timing for Chunk Buffer Memory                                 | 263 |

| Figure 53 | Write Timing for Chunk Buffer Memory                                | 263 |

| Figure 54 | Read Followed by Write Timing for ZBT Mode                          | 264 |

| Figure 55 | Read Followed by Write Timing for Standard SSRAM Mode               | 264 |

| Figure 56 | Read and Write to Non-burstable Register Space                      | 265 |

| Figure 57 | Read and Write to Burstable Address Space                           | 265 |

| Figure 58 | Consecutive Write Accesses Using WRDONEB                            | 266 |

| Figure 59 | SBI336 Drop Bus Input Interface Timing                              | 272 |

| Figure 60 | SBI336 Add Bus Input Interface Timing                               | 273 |

| Figure 61 | SBI336 Add Bus Output Interface Timing                              | 274 |

| Figure 62 | SBI ADD BUS Collision Avoidance Timing                              | 274 |

| Figure 63 | Receive Any-PHY Interface Timing                                    | 276 |

| Figure 64 | Transmit Any-PHY Interface Timing                                   | 277 |

| Figure 65 | Synchronous I/O Timing                                              | 278 |

| Figure 66 | JTAG Port Interface Timing                                          | 279 |

# **List of Tables**

| Table 1 Definitions                                                 | 16  |

|---------------------------------------------------------------------|-----|

| Table 2 SBI Interface Signals (30 Pins)                             |     |

| Table 3 Any-PHY Packet Interface Signals (71 Pins)                  | 31  |

| Table 4 Re-Sequencing SDRAM Interface (52 Signals)                  | 40  |

| Table 5 Context Memory Synchronous SSRAM Interface (57 Signals)     |     |

| Table 6 Chunk Buffer SDRAM Interface (67 Signals)                   | 43  |

| Table 7 Microprocessor Interface Signals (44)                       | 44  |

| Table 8 Miscellaneous Interface Signals (10 Pins)                   |     |

| Table 9 Power and Ground Signals                                    | 47  |

| Table 10 SBI SPE/Tributary to RCAS Link Mapping                     | 65  |

| Table 11 SBI-SPE Tributary to TCAS Link Mapping                     | 89  |

| Table 12 Normal Mode Microprocessor Accessible Registers Memory Map | 91  |

| Table 13 Memory mode Configuration                                  | 97  |

| Table 14 SBI Mode                                                   |     |

| Table 15 Reserved Bit Settings                                      | 129 |

| Table 16 CRC[1:0] Settings                                          |     |

| Table 17 CRC[1:0] Settings                                          |     |

| Table 18 FLAG[2:0] Settings                                         | 141 |

| Table 19 Level[3:0]/TRANS Settings                                  | 142 |

| Table 20 SBI Mode                                                   | 153 |

| Table 21 Any-PHY Encoding                                           | 158 |

| Table 22 Reserved/Unused Bit Settings                               | 163 |

| Table 23 TRIB_TYP Encoding                                          | 166 |

| Table 24 SBI EXTRACT SPE_TYP[2:0]                                   | 167 |

| Table 25 Any-PHY Encoding                                           | 169 |

| Table 26 Valid BLEN                                                 | 171 |

| Table 27 TRIB_TYP Encoding                                          | 182 |

| Table 28 SBI INSERT SPE_TYP[2:0]                                    | 184 |

| Table 29 MPMEMSelect Function                                       | 185 |

| Table 30 MPBurstLength Function                                     | 186 |

| Table 31 MPCommand functions                                        | 186 |

| Table 32 PM-12 Memory Map                                           | 227 |

| Table 33 EQM-12 Memory Map                                          | 230 |

| Table 34 TFRAG Any-PHY Channel RAM Memory Map                       | 233 |

| Table 35 RFRAG Memory Map                                           | 234 |

| Table 36 | RS Memory Map                                                        | 237 |

|----------|----------------------------------------------------------------------|-----|

| Table 37 | Sequenced Connection Identifier Lookup Record                        | 238 |

| Table 38 | Non-sequenced Connection Identification Lookup Record                | 239 |

| Table 39 | Control Connection Identifier Lookup Record                          | 239 |

|          | Corrupt Connection Identifier Lookup Record                          |     |

| Table 41 | LSB Records Status Record                                            | 239 |

|          | MSB Records Record                                                   |     |

| Table 43 | LSB Record Freelist Record                                           | 240 |

|          | Chunk Buffer Memory Map (Only Even Addresses are Valid)              |     |

| Table 45 | Connection Context Memory Addressing                                 | 243 |

| Table 46 | CC Memory Map                                                        | 243 |

| Table 47 | Test Mode Register Memory Map                                        | 247 |

| Table 48 | Instruction Register (Length - 3 Bits)                               | 248 |

|          | FREEDM 32A1024L Absolute Maximum Ratings                             |     |

| Table 50 | Normal Operating Conditions                                          | 268 |

| Table 51 | Power Requirements                                                   | 269 |

| Table 52 | FREEDM 32A1024L D.C. Characteristics                                 | 271 |

| Table 53 | REFCLK Timing                                                        | 272 |

| Table 54 | SBI336 Drop Bus Input Timing (Referenced to Figure 59)               | 273 |

| Table 55 | SBI336 Add Bus Input Timing (Referenced to Figure 60 )               | 273 |

| Table 56 | SBI336 Add Bus Output Timing (Referenced to Figure 61 and Figure 62) | 274 |

| Table 57 | Any-PHY Level 2 Interface (Figure 63 and Figure 64)                  | 275 |

| Table 58 | Any-PHY Level 3 Interface (Figure 63 and Figure 64)                  | 275 |

| Table 59 | Microprocessor Interface (Figure 65)                                 | 277 |

| Table 60 | SYSCLK Timing                                                        | 278 |

| Table 61 | Resequencing SDRAM Interface (Figure 65)                             | 278 |

| Table 62 | Chunk Buffer SDRAM Interface (Figure 65)                             | 278 |

| Table 63 | Connection Context Memory SSRAM Interface (Figure 65)                | 278 |

| Table 64 | JTAG Port Interface (Figure 66)                                      | 279 |

| Table 65 | Central Office Thermal Information                                   | 280 |

| Table 66 | Thermal Resistance vs. Air Flow <sup>3</sup>                         | 280 |

| Table 67 | Device Compact Model <sup>4</sup>                                    | 280 |

|          | Outside Plant Thermal Information                                    |     |

| Table 69 | Device Compact Model <sup>3</sup>                                    | 281 |

| Table 70 | Heat Sink Requirements                                               | 281 |

# 1 Definitions

The following table defines terms and abbreviations used in this document.

**Table 1 Definitions**

| Term      | Definition                                                                                                                                |

|-----------|-------------------------------------------------------------------------------------------------------------------------------------------|

| ADDR      | The Address Field in a PPP header                                                                                                         |

| Any-PHY   | Saturn Interface Specification and Interoperability Framework for Packet and Cell transfers between Physical layer and Link Layer devices |

| APPI      | Any-PHY Packet Interface                                                                                                                  |

| В         | The Begin bit of a fragment                                                                                                               |

| BECN      | Backward Explicit Congestion Notification                                                                                                 |

| C/R       | Command/Response bit in the Q.922 Header                                                                                                  |

| CI        | Connection Identifier                                                                                                                     |

| CRC       | Cyclic Redundancy Check                                                                                                                   |

| CRC-CCITT | Cyclic Redundancy Check as specified by the CCITT                                                                                         |

| CNTL      | Control field in a PPP header                                                                                                             |

| cos       | Class of Service                                                                                                                          |

| Datagram  | A fragment, packet or frame                                                                                                               |

| DE        | Discard Eligibility                                                                                                                       |

| DLL       | Digital Delay Lock Loop                                                                                                                   |

| DSLAM     | Digital Subscriber Line Access Multiplexer                                                                                                |

| E         | The End bit of a fragment                                                                                                                 |

| EC        | Error Code                                                                                                                                |

| ECC       | Error Correcting Code                                                                                                                     |

| Egress    | Traffic flow from the switch to the line is defined as Egress traffic – equivalent to transmit                                            |

| EOP       | End of Packet                                                                                                                             |

| FECN      | Forward Explicit Congestion Notification                                                                                                  |

| FIFO      | First In First Out                                                                                                                        |

| FCS       | Frame Check Sequence                                                                                                                      |

| FR        | Frame Relay                                                                                                                               |

| Fragment  | A sub-unit of a packet of frame                                                                                                           |

| Frame     | A Frame Relay unit of transfer                                                                                                            |

| FUNI      | Frame Relay User to Network Interface                                                                                                     |

| HDLC      | High level Data Link Control                                                                                                              |

| Ingress   | Traffic flow from the line side to switch is defined as Ingress traffic – equivalent to receive                                           |

| IETF      | Internet Engineering Task Force                                                                                                           |

| MIB       | Management Information Database                                                                                                           |

| ML        | Multi-link                                                                                                                                |

| ML-FR     | Multi-link Frame Relay                                                                                                                    |

| ML-PPP    | Multi-link PPP                                                                                                                            |

| Term   | Definition                                                                               |  |  |  |  |

|--------|------------------------------------------------------------------------------------------|--|--|--|--|

| MTU    | Maximum Transmission Unit                                                                |  |  |  |  |

| MRU    | Maximum Receive Unit                                                                     |  |  |  |  |

| NNI    | Network-to-Network Interface                                                             |  |  |  |  |

| Packet | An IP data unit                                                                          |  |  |  |  |

| PID    | Protocol ID field in a PPP header                                                        |  |  |  |  |

| PPP    | Point to Point Protocol                                                                  |  |  |  |  |

| Q.922  | ISDN Data Link Layer Specification for Frame Mode Bearer Services                        |  |  |  |  |

| RFC    | Request For Comments                                                                     |  |  |  |  |

| SBI    | Scalable Bandwidth Interface                                                             |  |  |  |  |

| SBI336 | A Scalable Bandwidth Interface operating at 77.76 MHz capable of supporting 336 T1 links |  |  |  |  |

| SDRAM  | Synchronous Dynamic Random Access Memory                                                 |  |  |  |  |

| SN     | Sequence Number                                                                          |  |  |  |  |

| SPE    | Synchronous Payload Envelope                                                             |  |  |  |  |

| SSRAM  | Synchronous Static Random Access Memory                                                  |  |  |  |  |

| TM     | Traffic Management                                                                       |  |  |  |  |

| UNI    | User-to-Network Interface                                                                |  |  |  |  |

| ZBT    | Zero Bus Turnaround                                                                      |  |  |  |  |

## 2 Features

The PM7312 FREEDM 32A1024L is a Frame Engine and Data Link Manager with these features:

- Single-chip multi-channel HDLC controller with either a 52 MHz 16 bit Any-PHY Level 2 or a 104 MHz 8 bit Any-PHY Level 3 packet interface for transfer of packet, frame data using an external controller

- Supports line rate throughput for 32 T1s or E1s. (40 byte packets encapsulated in PPP over HDLC (50 byte transfers (RFC 1661) or 55 byte transfers (RFC 1990))).

- Provides simultaneous support of PPP, Frame Relay, multi-link-PPP and multi-link-Frame Relay protocols. Alternative protocols supported via HDLC termination and full packet store of the data within the HDLC structure.

- Supports 2 levels of priority queuing in the egress direction. When the device is configured to fragment low priority traffic, high priority traffic, if present, will be inserted in between low priority fragments on a link.

## 2.1 Interfaces

- A 52MHz, 16-bit Any-PHY Level 2 or 104MHz, 8-bit Any-PHY Level 3 packet interface for system side connection.

- o The interface is capable of supporting full datagram transfer on a per Any-PHY channel basis or

- o Fragmented packets or frames on a per Any-PHY channel basis.

- A single 19.44 MHz SBI or 77.76 MHz SBI336 bus supporting up to 32 links.

- A 100 MHz, 48-bit SDRAM interface for ingress and egress per packet/fragment storage.

- A 100 MHz, 32-bit SDRAM interface for ingress re-sequencing data structures.

- A 100 MHz, 36-bit SSRAM interface for Ingress/Egress Context storage.

- The device provides the standard 5 signal P1149.1 JTAG test port for boundary scan.

- A 32-bit microprocessor interface for configuration and status monitoring.

## 2.2 Channelization / HDLC Features

- Support for up to 1024 HDLC channels in both the ingress and egress direction, with individual HDLC channel speeds ranging from 56Kbps to 2 Mbps.

- The 1024 HDLC channels can be assigned to a mixture of physical links via the SBI interface. The SBI transports the equivalent of 3 STS-1 synchronous payload envelopes (SPE). Each STS-1 SPE can be individually configured to carry 28 T1/J1s or 21 E1s. The FREEDM 32A1024 can flexibly carry up to 32 T1s or E1s on these SPEs.

- In a channelized application, the number of time-slots assigned to an HDLC channel is programmable from 1 to 24 (for T1/J1) and from 1 to 31 (for E1).

- For each channel, the HDLC receiver supports programmable flag sequence detection, bit destuffing and frame check sequence validation. The receiver supports the validation of both CRC-CCITT and CRC-32 frame check sequences.

- For each HDLC channel, the receiver checks for packet abort sequences, octet alignment, and for minimum and maximum packet length.

- For each HDLC channel, time-slots are selectable to be in 56 Kbps format or 64 Kbps clear channel format.

- For each HDLC channel, the HDLC transmitter supports programmable flag sequence generation, bit stuffing and frame check sequence generation. The transmitter supports the generation of both CRC-CCITT and CRC-32 frame check sequences. The transmitter also aborts packets under the direction of the external TM engine or automatically when the channel underflows.

- Support for 2 levels of transmit priority per HDLC channel. (Only single link channels support this feature, not multi-link bundles.) High and low priority packets are queued separately. High priority traffic, when present, is always transmitted before low priority traffic. When low priority traffic is fragmented, high priority traffic is inserted in between low priority fragments.

## 2.3 PPP Features

- Link Control Protocol packet identification. Packets are identified by the PID as control protocols and will be forwarded to the Any-PHY interface.

- Capable of supporting line rate transfers of packet sizes from 40 to 9.6K bytes.

- Support for PPP header compression as per RFC 1661 on sequenced links. On receive, compressed headers are detected and processed appropriately as they arrive on an HDLC channel. Compressed PPP headers are passed to the system side via the Any-PHY interface. On transmit, compressed headers are accepted from the system side device via the Any-PHY interface. On sequenced links, all required processing is provided to correctly insert the compressed PPP headers into the 1024 HDLC channels. On non-sequenced links, header compression is only supported through the use of transparent mode.

- RFC-1990 Multi-link PPP bundles:

- Capable of supporting fragment sizes from 6 to 9.6K bytes with the restriction that the maximum number of fragments per packet is 81.

- Support for 3 egress fragmentation sizes (128, 256, and 512 bytes) configurable per connection. Optionally, full packet transfers are supported on a per connection basis. The FREEDM 32A1024L supports header compression but does not perform it.

- Either 12 bit or 24 bit sequence number, with short and long fragment header formats, is supported.

- Supports 16 bundles in ingress direction. These bundles are composed of independent HDLC channels.

- Supports 16 bundles in egress direction. These bundles are composed of independent HDLC channels.

- Support for fragmentation on a single HDLC channel.

- Support for 16 COS levels in accordance with RFC 2686.

- Support for up to 100ms of intra bundle skew in the receive direction when supporting the minimum fragment size. Capable of supporting larger skews (<400ms) with larger fragment sizes. The intra-bundle skew is limited by 12 bit sequence number capabilities.

- o Up to 12 member links per bundle.

Each member link is required to operate at the same speed. Either T1/J1 or E1 rates.

## 2.4 Frame Relay Features

- Link layer address lookup can be performed based on HDLC or Any-PHY channel and DLCI for HDLC channels supporting Frame Relay protocols.

- Capable of supporting line rate transfers of frame sizes from 40 to 9.6K bytes.

- FRF.16 Multi-link FR bundles and FRF.12 UNI, NNI or End-to-End fragmentation:

- Capable of supporting fragment sizes from 4 to 9.6K bytes with the restriction that the maximum number of fragments per packet is 81.

- 10-bit DLCI format supported for channels operating in Frame Relay mode. Alternative DLCI formats supported when the lookup is based on HDLC channel only.

- The lookup algorithm can support a maximum of 16K connection identifiers (CIs) amongst all channels in use.

- FRF.16 Control Frames (Link Integrity Protocol) are identified and forwarded to the Any-PHY interface

- Support for 3 egress fragmentation sizes (128, 256, and 512 bytes) configurable per connection. Optionally, full packet transfers are supported on a per connection basis.

- o 12 bit sequence numbers supported.

- o Support for fragmentation on a single HDLC channel. (Note End-to-End fragmentation is only supported on single HDLC channels, not multilink bundles.)

- 16 bundles in ingress direction. These bundles are composed of independent HDLC channels.

- 16 bundles in egress direction. These bundles are composed of independent HDLC channels.

- O Support for up to 100ms intra-bundle skew within the limits of 12-bit sequence number capabilities when supporting the minimum fragment size. Capable of supporting larger skews (<400ms) with larger fragment sizes.

- o Up to 12 member links per bundle.

- Each member link operates at the same speed either T1/J1 or E1.

- FECN, BECN, and DE ingress processing as per FRF.12. The C/R value passed out in frame out mode is the value received on the Begin fragment.

#### 2.5 Statistics

- FREEDM 32A1024L maintains the following counters on a per-HDLC channel basis:

- CRC Errors observed by the HDLC framer.

- o HDLC framing aborts.

- Non-Octet aligned frames.

- o HDLC MRU exceeded.

- o Bytes and datagrams received.

- o Bytes and datagrams transmitted.

- Additionally, the FREEDM 32A1024L provides the following counters per Ingress CI:

- Number of Lost Sequence Number events.

- Number of Unexpected Sequence Number events.

- o Number of Frame Relay datagrams received with DE bit set.

- Additionally, the FREEDM 32A1024L provides the following global error counters:

- o Number of bytes discarded due to transmit overflows, receive overflows in the presence of link failures, and line rate arrivals of small (< 40 byte) packets.

- Number of Lost fragment events

- o FIFO overflows and underruns.

- Additional error states are also tracked.

- Additionally, FREEDM 32A1024L supports the MFR MIB by detecting and informing the host of unexpected sequence numbers and time outs.

#### 2.6 Fault Isolation Features

- Two levels of loop-back are provided:

- SBI tributary loopback

- System side loop-back per HDLC channel.

## 2.7 Technologies

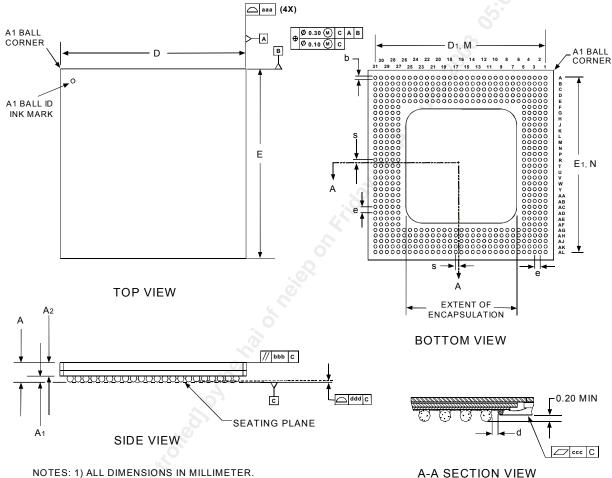

- 520 pin (1.27 mil pitch) thermally enhanced ball grid array (TEBGA) package.

- 331 signal pins, 3.3V I/O.

- Low power 0.18µm CMOS technology using 1.8V core power.

# 3 Applications

- IETF PPP interfaces for routers.

- Frame Relay interfaces for ATM or Frame Relay switches and multiplexers.

- FUNI or Frame Relay service inter-working interfaces for ATM switches and multiplexers.

- Internet/Intranet access equipment.

- Multi-service DSLAM equipment.

## 4 References

#### 4.1 PPP

- 1. RFC 1661, The Point-to-Point Protocol (PPP).

- 2. RFC 1990, PPP Multi-link Protocol.

- 3. RFC-2686, Multi-class Multi-link PPP.

## 4.2 Frame Relay

- 1. ANSI T1.617a-1994, Annex F.

- 2. RFC 1490, Multi-protocol Interconnect over Frame Relay.

- 3. FRF.1.1, User-to-Network (UNI) Implementation Agreement.

- 4. FRF.3.1, Multi-protocol Encapsulation Implementation Agreement (MEI).

- 5. FRF.4.1, Frame Relay User-to-Network SVC Implementation Agreement.

- 6. FRF.12, Frame Relay Fragmentation Implementation Agreement.

- 7. FRF.16, Multi-link Frame Relay (MFR) PVC Implementation Agreement.

#### 4.3 HDLC Standards

- 1. International Organization for Standardization, ISO Standard 3309-1993, "Information Technology Telecommunications and information exchange between systems High-Level Data Link Control (HDLC) procedures Frame structure", December 1993.

- 2. RFC-1662 "PPP in HDLC-like Framing" Internet Engineering Task Force, July 1994.

#### 4.4 Misc. References

1. PMC-2011402 – "High Density 32 Channel T1/E1 Framer Standard Product Data Sheet", PMC-Sierra Inc.

Electronic Industries Association. *Methodology for the Thermal Measurement of Component Packages (Single Semiconductor Device)*: EIA/JESD51. December 1995.

- 2. Electronic Industries Alliance 1999. *Integrated Circuit Thermal Test Method Environmental Conditions -Junction-to-Board: JESD51-8*. October 1999.

- 3. Telcordia Technologies. *Network Equipment-Building System (NEBS) Requirements: Physical Protection: Telcordia Technologies Generic Requirements GR-63-CORE*. Issue 1. October 1995.

4. SEMI (Semiconductor Equipment and Materials International). SEMI G30-88 Test Method for Junction-to-Case Thermal Resistance Measurements of Ceramic Packages. 1988.

# 5 Application Examples

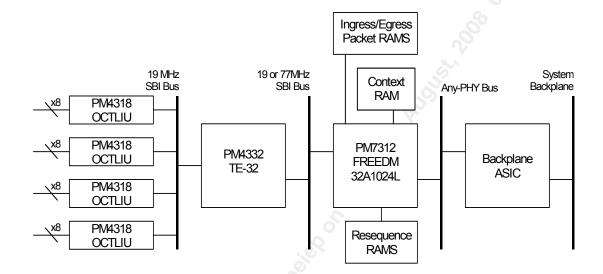

Figure 1 32xT1/E1 Access Card for a Router

## 6 Block Diagram

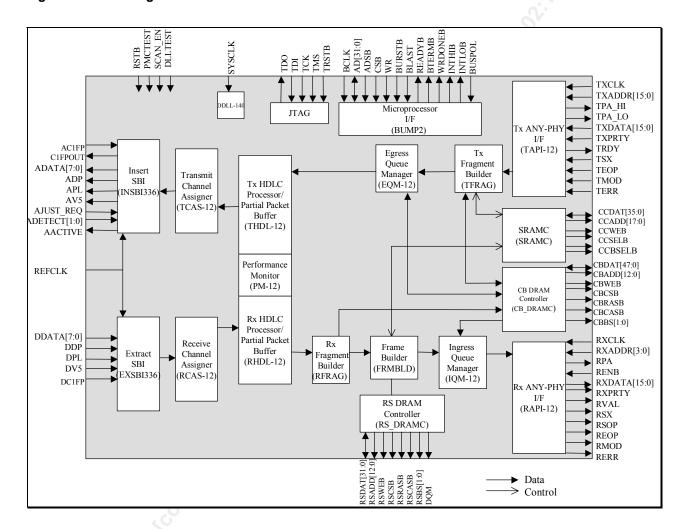

Figure 2 Block Diagram of FREEDM 32A1024L

## 7 Description

The FREEDM 32A1024L device is a monolithic integrated circuit supporting highly channelized termination of HDLC-framed Point to Point Protocol (PPP) and Frame Relay, including multi-link variants.

On the Line side, the FREEDM 32A1024L device supports an SBI interface supporting up to 1024 HDLC channels. On the system side, the FREEDM 32A1024L provides a Level 2 and Level 3 APPI presenting a channelized interface capable of supporting full frame/packet transfers as well as fragment data transfers. Rate adaptation between the line and system side interfaces is provided by external buffers.

The FREEDM 32A1024L terminates up to 1024 HDLC channels of HDLC framed PPP or Frame Relay with speeds ranging from 56 Kbps to 2 Mbps in the ingress direction. HDLC channels may contain a mix of protocols and speeds up to an aggregate of 2 Mbps. FREEDM 32A1024L provides HDLC header removal, CRC checking and stripping. Data path termination including frame/packet re-assembly and multi-link termination is provided in hardware.

In the egress direction, the FREEDM 32A1024L receives packets from the external controller. The FREEDM 32A1024L provides support for ML-FR and ML-PPP protocols by fragmenting transmitted packets, appending the appropriate sequence number and assigning the fragment to an HDLC channel within the multi-link bundle. FREEDM 32A1024L is also capable of supporting full packet transfer on up to 1024 HDLC channels that are not configured to support multi-link. The HDLC processor within FREEDM 32A1024L encapsulates the data with HDLC flags, CRC bytes and performs the appropriate bit stuffing.

The FREEDM 32A1024L supports two levels of priority for egress traffic on HDLC channels that are not configured as part of a multi-link bundle. The priority of each packet received from the external controller is indicated by an additional address bit in the Any-PHY in-band address header word. Packets received with different priorities on a given channel are stored in separate queues for transmission. If the FREEDM 32A1024L is configured to fragment low-priority packets, any high priority data received following a low priority packet will be transmitted at the first available opportunity, and will be interleaved between fragments of the low priority packet if possible.

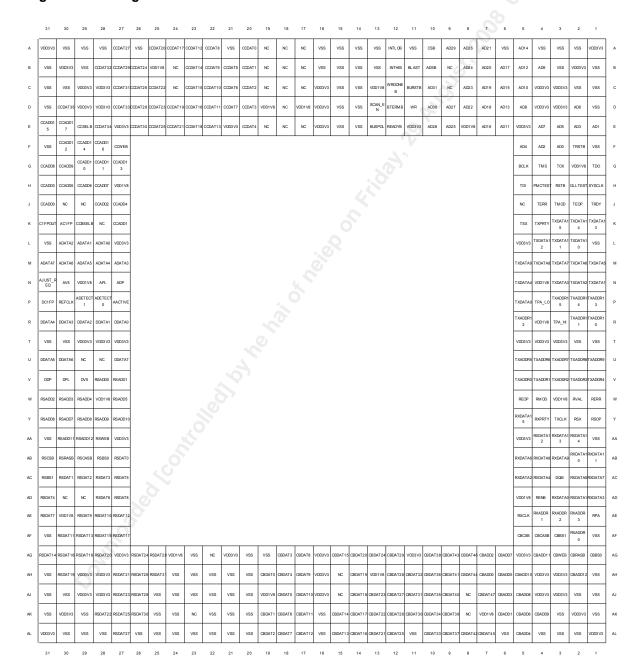

# 8 Pin Diagram

The FREEDM 32A1024L is manufactured in a 520-pin (1.27 mil pitch) thermally enhanced ball grid array package. (Bottom View)

Figure 3 Pin Diagram

# 9 Pin Description

Table 2 SBI Interface Signals (30 Pins)

| Pin Name                                                                | Туре   | Pin No.                                              | Function                                                                                                                                                                                                                                                                                                                                                                                                |

|-------------------------------------------------------------------------|--------|------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFCLK                                                                  | Input  | P30                                                  | The SBI reference clock signal (REFCLK) provides reference timing for the SBI ADD and DROP buses.                                                                                                                                                                                                                                                                                                       |

|                                                                         |        |                                                      | REFCLK is nominally a 50% duty cycle clock of frequency 19.44 MHz ±50ppm for SBI bus operation or 77.76 MHz ±20ppm for SBI336 bus operation                                                                                                                                                                                                                                                             |

| DC1FP                                                                   | Input  | P31                                                  | The C1 octet frame pulse signal (DC1FP) for the drop bus provides frame synchronization for devices connected via an SBI interface. DC1FP must be asserted for 1 REFCLK cycle every 500 µs or multiples thereof (i.e. every 38880 x n REFCLK cycles, where n is a positive integer). All devices interconnected via the SBI drop interface must be synchronized to a DC1FP signal from a single source. |

|                                                                         |        |                                                      | DC1FP is sampled on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                          |

|                                                                         |        |                                                      | Note – If the SBI bus is being operated in synchronous mode, DC1FP must be asserted for 1 REFCLK cycle every 6 ms or multiples thereof.                                                                                                                                                                                                                                                                 |

| AC1FP                                                                   | Input  | K30                                                  | The C1 octet frame pulse signal (AC1FP) for the add bus provides frame synchronization for devices connected via an SBI interface. AC1FP must be asserted for 1 REFCLK cycle every 500 µs or multiples thereof (i.e. every 38880 n REFCLK cycles, where n is a positive integer). All devices interconnected via the add SBI interface must be synchronized to an AC1FP signal from a single source.    |

|                                                                         |        |                                                      | AC1FP is sampled on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                          |

|                                                                         |        | 8                                                    | Note – If the SBI bus is being operated in synchronous mode, AC1FP must be asserted for 1 REFCLK cycle every 6 ms or multiples thereof.                                                                                                                                                                                                                                                                 |

| C1FPOUT                                                                 | Output | K31                                                  | The C1 octet frame pulse output signal (C1FPOUT) may be used to provide frame synchronization for devices interconnected via an SBI interface. C1FPOUT is asserted for 1 REFCLK cycle every 500 µs (i.e. every 38880 REFCLK cycles).                                                                                                                                                                    |

|                                                                         | (      |                                                      | C1FPOUT is updated on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                        |

|                                                                         |        |                                                      | Note – The C1FPOUT pulse is not suitable for use in systems in which the SBI bus is operated in synchronous mode.                                                                                                                                                                                                                                                                                       |

| DDATA[0] DDATA[1] DDATA[2] DDATA[3] DDATA[4] DDATA[5] DDATA[6] DDATA[7] | Input  | R27<br>R28<br>R29<br>R30<br>R31<br>U31<br>U30<br>U27 | The SBI DROP bus data signals (DDATA[7:0]) contain the time division multiplexed receive data from the up to 32 independently timed links. Data from each link is transported as a tributary within the SBI TDM bus structure. Multiple PHY devices can drive the SBI DROP bus at uniquely assigned tributary column positions. DDATA[7:0] are sampled on the rising edge of REFCLK.                    |

| Pin Name                                                                                     | Type               | Pin No.                                              | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|----------------------------------------------------------------------------------------------|--------------------|------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DDP                                                                                          | Input              | V31                                                  | The SBI DROP bus parity signal (DDP) carries the even or odd parity for the DROP bus signals. The parity calculation encompasses the DDATA[7:0], DPL and DV5 signals.                                                                                                                                                                                                                                                                                                                                                                    |

|                                                                                              |                    |                                                      | Multiple PHY devices can drive DDP at uniquely assigned tributary column positions. This parity signal is intended to detect accidental PHY source clashes in the column assignment.                                                                                                                                                                                                                                                                                                                                                     |

|                                                                                              |                    |                                                      | DDP is sampled on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DPL                                                                                          | Input              | V30                                                  | The SBI DROP bus payload signal (DPL) indicates valid data within the SBI TDM bus structure. This signal is asserted during all octets making up a tributary. This signal may be asserted during the V3 octet within a tributary to accommodate negative timing adjustments between the tributary rate and the fixed TDM bus structure. This signal may be de-asserted during the octet following the V3 octet within a tributary to accommodate positive timing adjustments between the tributary rate and the fixed TDM bus structure. |

|                                                                                              |                    |                                                      | Multiple PHY devices can drive DPL at uniquely assigned tributary column positions.                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                                                                                              |                    |                                                      | DPL is sampled on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DV5                                                                                          | Input              | V29                                                  | The SBI DROP bus payload indicator signal (DV5) locates the position of the floating payloads for each tributary within the SBI TDM bus structure. Timing differences between the port timing and the TDM bus timing are indicated by adjustments of this payload indicator relative to the fixed TDM bus structure.                                                                                                                                                                                                                     |

|                                                                                              |                    |                                                      | Multiple PHY devices can drive DV5 at uniquely assigned tributary column positions. All movements indicated by this signal must be accompanied by appropriate adjustments in the DPL signal.                                                                                                                                                                                                                                                                                                                                             |

|                                                                                              |                    |                                                      | DV5 is sampled on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| ADATA[0]<br>ADATA[1]<br>ADATA[2]<br>ADATA[3]<br>ADATA[4]<br>ADATA[5]<br>ADATA[6]<br>ADATA[7] | Tristate<br>Output | L28<br>L29<br>L30<br>M27<br>M28<br>M29<br>M30<br>M31 | The SBI ADD bus data signals (ADATA[7:0]) contain the time division multiplexed transmit data from the up to 32 independently timed links. Data from each link is transported as a tributary within the SBI TDM bus structure. Multiple link layer devices can drive the SBI ADD bus at uniquely assigned tributary column positions. When the FREEDM 32A1024L is not outputting data on a particular tributary column the ADATA[7:0] are driven or tri-stated based on the DEFAULT_DRV register value.                                  |

|                                                                                              | ۷, ۲               |                                                      | ADATA[7:0] are updated on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| ADP                                                                                          | Tristate<br>Output | N27                                                  | The SBI ADD bus parity signal (ADP) carries the even or odd parity for the ADD bus signals. The parity calculation encompasses the ADATA[7:0], APL and AV5 signals.                                                                                                                                                                                                                                                                                                                                                                      |

| Oon                                                                                          |                    |                                                      | Multiple link layer devices can drive this signal at uniquely assigned tributary column positions. When the FREEDM 32A1024L is not outputting data on a particular tributary column, ADP is driven or tri-stated based on the DEFAULT_DRV register value. This parity signal is intended to detect accidental link layer source clashes in the column assignment.                                                                                                                                                                        |

|                                                                                              |                    |                                                      | ADP is updated on the rising edge of REFCLK.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| APL                                                                                          | Tristate<br>Output | N28                                                  | The SBI ADD bus payload signal (APL) indicates valid data within the SBI TDM bus structure. This signal is asserted during all octets making up a tributary. This signal may be asserted during the V3 octet within a tributary to accommodate negative timing adjustments between the tributary rate and the fixed TDM bus structure. This signal may be de-asserted during the octet following the V3 octet within a tributary to accommodate positive timing                                                                          |

| Pin Name                 | Type               | Pin No.    | Function                                                                                                                                                                                                                                                                                                                                                    |

|--------------------------|--------------------|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                          |                    |            | adjustments between the tributary rate and the fixed TDM bus structure.                                                                                                                                                                                                                                                                                     |

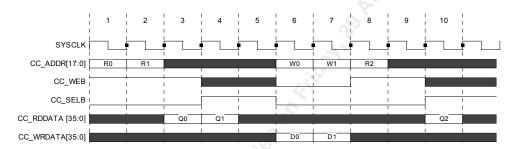

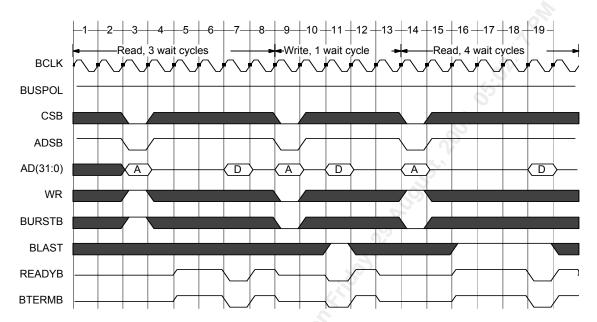

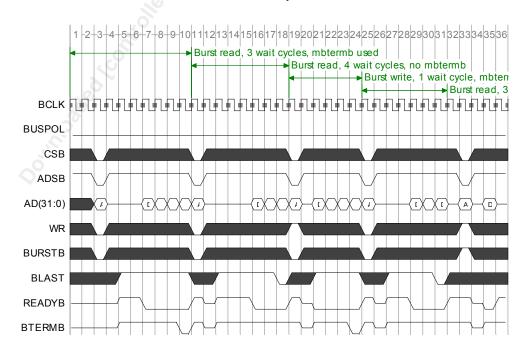

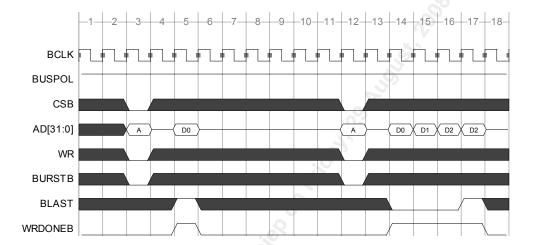

|                          |                    |            | Multiple link layer devices can drive this signal at uniquely assigned tributary column positions. When the FREEDM 32A1024L is not outputting data on a particular tributary column, APL is driven or tristated based on the DEFAULT_DRV register value.                                                                                                    |