# CMOS **MT90732 E2/E3 Framer (E2/E3F)**

**Advance Information**

#### **Features**

- Framer for CCITT Recommendations

- G.742 (8448 kbit/s)

- G.745 (8448 kbit/s)

- G.751 (34368 kbit/s)

- G.753 (34368 kbit/s)

- · Line side interface

- Dual rail or NRZ

- HDB3 codec for dual rail I/O

- · Terminal side interface

- Nibble-parallel

- Bit-serial

- Transmit reference generator for bit-serial I/O

- Microprocessor or control leads

- I/O port for service bits

# **Applications**

- · Line terminals

- Wideband data or video transport

- · Test equipment

- Multiplexer systems

ISSUE 1 May 1995

#### **Ordering Information**

MT90732AP 68 Pin PLCC -40°C to +85°C

## **Description**

The MT90732 E2/E3 Framer (E2/E3F) is a CMOS VLSI device that provides the functions needed to frame a wideband payload to one of four CCITT Recommendations. G.742, G.745, G.751, or G.753. The E2/E3 Framer interfaces to line circuitry with either dual rail or NRZ signals. On the terminal side, the interface can be either nibble-parallel or bit-serial.

The MT90732 can be operated with or without a microprocessor. When interfaced with microprocessor, the E2/E3 Framer provides an 8byte memory map for control, performance counters and alarm status. The MT90732 provides a transmit and receive interface port for accessing the overhead bits from each of the four recommendations. The overhead bits can also be accessed by the microprocessor via the memory map.

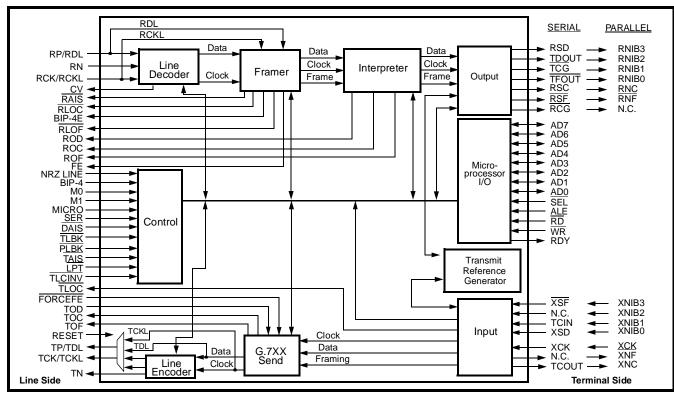

Figure 1 - Functional Block Diagram

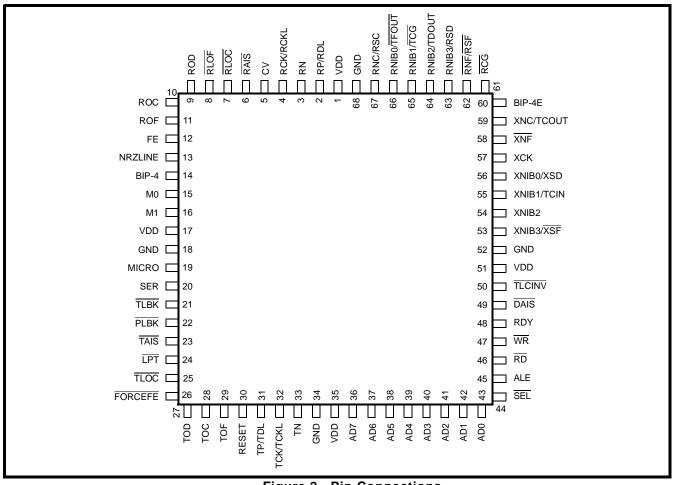

Figure 2 - Pin Connections

# **Pin Description**

## **Power Supply and Ground**

| Pin #       | Name | I/O/P | Description                        |  |  |  |

|-------------|------|-------|------------------------------------|--|--|--|

| 1,17,35,51  | VDD  | Р     | VDD. 5-volt supply voltage, +/- 5% |  |  |  |

| 18,34,52,68 | GND  | Р     | Ground.                            |  |  |  |

Note: I = Input; O = Output; P = Power

#### **Line Side Receive**

| Pin # | Name     | I/O/P | Description                                                                                                   |

|-------|----------|-------|---------------------------------------------------------------------------------------------------------------|

| 2     | RP/RDL   |       | Receive Positive Rail/Receive NRZ Data. Receive positive rail/NRZ data generated from line interface circuit. |

| 3     | RN       |       | Receive Negative Rail Data. Receive negative rail data generated from line interface circuit.                 |

| 4     | RCK/RCKL |       | Receive Clock Rail/Receive Clock NRZ. The receive clock is used for clocking in the rail/NRZ data signals.    |

Note: I = Input; O = Output; P = Power

# **Line Side Transmit**

| Pin # | Name     | I/O/P | Description                                                                                                                                                                         |

|-------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 31    | TP/TDL   | 0     | <b>Transmit Positive Rail/Transmit NRZ Data.</b> Transmit positive rail/NRZ data sent out of E2/E3 Framer.                                                                          |

| 32    | TCK/TCKL | 0     | <b>Transmit Clock Rail/Transmit Clock NRZ.</b> The transmit clock is used for clocking out the dual rail/NRZ data signals. The TCK/TCKL clock signal is derived from the XCK clock. |

| 33    | TN       | 0     | <b>Transmit Negative Rail Data.</b> Transmit negative rail data sent out of E2/E3 Framer.                                                                                           |

Note: I = Input; O = Output; P = Power

## **Terminal Interface**

| Pin # | Name            | I/O/P | Description                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

|-------|-----------------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 61    | RCG             | 0     | Receive Clock Gapped. An active low signal indicates the receive framing and service bit locations in the serial mode only.                                                                                                                                                                                                                                           |  |  |  |

| 62    | RNF/RSF         | 0     | <b>Receive Framing Pulse.</b> Framing pulse is synchronous with the last nibble for the nibble-parallel interface, and with the first bit in the frame for the bit-serial interface.                                                                                                                                                                                  |  |  |  |

| 63    | RNIB3/RSD       | 0     | Receive Nibble Bit 3/Receive Serial Data. Bit 3 is the most significant bit in the nibble and corresponds to the first bit received in the nibble. The framing pattern, service bits, and BIP-4 nibble are not provided as parallel data. In the serial mode receive data signal consists of all bits, including the framing pattern and service bits.                |  |  |  |

| 64    | RNIB2/TDO<br>UT | 0     | Receive Nibble Bit 2/Transmit Reference Generator Data Output. In the nibble-parallel mode, it is Bit 2 of the received nibble. The reference generator is enabled in the serial mode. The output data signal (TDOUT) consists of all ones in place of the framing bits and zeros elsewhere in the frame.                                                             |  |  |  |

| 65    | RNIB1/TCG       | 0     | Receive Nibble Bit 1/Transmit Reference Generator Clock Gap Signal. In the nibble-parallel mode, it is Bit 1 of the received nibble. The active low TCG signal indicates the location of the framing pattern and the service bits in the frame.                                                                                                                       |  |  |  |

| 66    | RNIB0/TFO<br>UT | 0     | Receive Nibble Bit 0/Transmit Reference Generator Framing Pulse. Bit 0 is the least significant bit in the nibble and is the last bit received. The active low TFOUT signal is synchronous with the first bit in the frame.                                                                                                                                           |  |  |  |

| 67    | RNC/RSC         | 0     | Receive Nibble Clock/Receive Serial Clock. The nibble and serial clocks are derived from the line side dual rail/NRZ clock signal (RCK/RCKL). RNC is gapped during framing pattern, service bit and BIP-4 bit times.                                                                                                                                                  |  |  |  |

| 53    | XNIB3/XSF       | l     | <b>Transmit Nibble Bit 3/Transmit Serial Framing Pulse.</b> In the nibble-parallel mode, bit 3 is the most significant bit in the nibble and corresponds to the first bit transmitted in the nibble. When the terminal interface is serial, the negative framing pulse is synchronous with the first bit in the frame.                                                |  |  |  |

| 54    | XNIB2           | I     | Transmit Nibble Bit 2. Bit 2 in the 4-bit nibble.                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 55    | XNIB1/TCI<br>N  | I     | <b>Transmit Nibble Bit 1/Transmit Reference Generator Clock In.</b> Bit 1 in the transmit nibble. For a serial interface, the TCIN is used to derive the clock out (TCOUT), data signal (TDOUT), framing pulse (TFOUT), and gapped clock signal (TCG). The reference generator signals are provided for multiplexing the external payload data into the serial frame. |  |  |  |

## **Terminal Interface**

| Pin # | Name          | I/O/P | Description                                                                                                                                                                                                                                                                                                                                                                  |

|-------|---------------|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 56    | XNIB0/XSD     | I     | <b>Transmit Nibble Bit 0/Transmit Serial Data.</b> In the nibble-parallel mode, bit 0 is the least significant bit in the nibble. For a serial interface, the input must consist of all the bits in the frame.                                                                                                                                                               |

| 57    | XCK           | I     | <b>Transmit Clock.</b> For the terminal side nibble-parallel interface, the XCK is used for all transmit timing functions, including deriving the nibble output clock (XNC) and framing pulse (XNF). For the serial interface, this clock may be derived from the transmit reference generator clock output (TCOUT).                                                         |

| 58    | XNF           | 0     | Transmit Nibble Framing Pulse. The XNF and clock signal (XNC) are provided for multiplexing nibble data into the E2/E3 Framer from external circuitry. The negative framing pulse identifies the first bit in the frame.                                                                                                                                                     |

| 59    | XNC/TCOU<br>T | 0     | Transmit Nibble Clock/Transmit Reference Generator Clock Out. The XNC is derived from the transmit clock (XCK) and is used as a time base for clocking data out of the external multiplexer and into the E2/E3 Framer. XNC is gapped during the framing pattern, service bit and BIP-4 bit times. TCOUT is derived from the input clock (TCIN), and has the same duty cycle. |

Note: I = Input; O = Output; P = Power

## **Service Bit Interface**

| Pin # | Name | I/O/P | Description                                                                                                                                                        |  |

|-------|------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 9     | ROD  | 0     | <b>Receive Service Data Bits.</b> These service bits are clocked out of E2/E3 Framer on positive transitions of clock signal (ROC).                                |  |

| 10    | ROC  | 0     | Receive Service Bits Clock. A gapped clock that clocks out the service bits. The clock is active only for clocking out the receive service data bits(ROD).         |  |

| 11    | ROF  | 0     | Receive Service Bits Framing Pulse. A positive framing pulse that is synchronous with the first bit in the frame.                                                  |  |

| 27    | TOD  | I     | <b>Transmit Service Data Bits.</b> The service bits are clocked into E2/E3 Framer on positive transitions of clock signal (TOC).                                   |  |

| 28    | TOC  | 0     | <b>Transmit Service Bits Clock.</b> A gapped clock that clocks in the service bits. The clock is active only for clocking in the transmit service data bits (TOD). |  |

| 29    | TOF  | 0     | <b>Transmit Service Bits Framing Pulse.</b> A positive framing pulse that is synchronous with the first bit in the frame.                                          |  |

Note: I = Input; O = Output; P = Power

# **Microprocessor Interface**

| Pin # | Name    | I/O/P | Description                                                                                                                                                             |

|-------|---------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 36-43 | AD(7-0) | I/O   | Address/Data Bus. These leads constitute the time-multiplexed address and data bus for accessing the registers which reside in the E2/E3F.                              |

| 44    | SEL     | I     | <b>Select.</b> A low enables the microprocessor to access the E2/E3F memory map for control, status, and alarm information.                                             |

| 45    | ALE     | I     | <b>Address Latch Enable.</b> An active high signal generated by the microprocessor. Used by the microprocessor to hold an address stable during a read/write bus cycle. |

| 46    | RD      | I     | <b>Read.</b> An active low signal generated by the microprocessor for reading the registers which reside in the memory map.                                             |

# **Microprocessor Interface**

| Pin # | Name | I/O/P | Description                                                                                                                                                          |

|-------|------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 47    | WR   | I     | <b>Write.</b> An active low signal generated by the microprocessor for writing to the registers which reside in the memory map.                                      |

| 48    | RDY  |       | <b>Ready.</b> An active high signal indicating an E2/E3F acknowledgment to the microprocessor that the addressed memory map location can complete the data transfer. |

Note: I = Input; O = Output; P = Power

## **Control Interface**

| Pin #    | Name     | I/O/P |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                   |         | Description               |                                |

|----------|----------|-------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------|---------|---------------------------|--------------------------------|

| 13       | NRZLINE  | I     | <b>Non-Return to Zero Line Selection.</b> A high enables an NRZ line input (RP and TP), and causes the HDB3 decoder/encoder to be bypassed. When low enables the dual rail interface (RP/RN and TP/TN) and the HDB3 decoder/encoder.                                                                                                                                                                                                                  |                                                                                                                   |         |                           |                                |

| 14       | BIP-4    | I     | <b>Bit Interleaved Parity - 4.</b> A high enables the BIP-4 function. In the transmit direction, the BIP-4 is calculated for data nibbles only, and is sent as the last nibble in the frame format. In the receive direction, the BIP-4 is calculated for the data bits only and compared against the received value which is present in the last four bits of the frame. An output indication (BIP-4E) occurs when one or more columns do not match. |                                                                                                                   |         |                           |                                |

| 16<br>15 | M1<br>M0 | I     |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | <b>Mode Control.</b> The two controls select the operating rate of the E2/E3F according to the table given below. |         |                           |                                |

|          |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | M1                                                                                                                | МО      | Recommendation            | Rate (kbit/s)                  |

|          |          |       | _                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0                                                                                                                 | 0       | G.745                     | 8448                           |

|          |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 0                                                                                                                 | 1       | G.742                     | 8448                           |

|          |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                 | 0       | G.753                     | 34368                          |

|          |          |       |                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1                                                                                                                 | 1       | G.751                     | 34368                          |

| 19       | MICRO    | I     | <b>Microprocessor Mode.</b> A high enables the microprocessor interface. When the microprocessor is enabled, the following hardware control leads are disabled. BIP-4, Mode (M0 and M1), Serial I/O (SER), and transmit AIS (TAIS). Bits are provided in the memory map for controlling these functions.                                                                                                                                              |                                                                                                                   |         |                           |                                |

| 20       | SER      | I     |                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                   |         | ects the bit-serial inter | face for the terminal side ce. |

| 21       | TLBK     | I     | Terminal Loop side.                                                                                                                                                                                                                                                                                                                                                                                                                                   | back                                                                                                              | . A low | enables a transmit to     | receive loopback at the line   |

| 22       | PLBK     | I     | Payload Loopback. A low enables a receive to transmit loopback at the terminal side in the serial mode of operation only.                                                                                                                                                                                                                                                                                                                             |                                                                                                                   |         |                           |                                |

| 23       | TAIS     | I     | <b>Transmit Alarm Indication Signal.</b> A low causes an all ones signal (AIS) to be sent in place of a G.7XX frame format.                                                                                                                                                                                                                                                                                                                           |                                                                                                                   |         |                           |                                |

| 24       | LPT      | I     | <b>Loop Timing.</b> A low enables the loop timing feature. Loop timing disables the transmit clock and enables the receive clock to be used as the transmit clock.                                                                                                                                                                                                                                                                                    |                                                                                                                   |         |                           |                                |

| 26       | FORCEFE  | I     | Force Framing high-to-low tran                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                   |         |                           | the framing pattern upon the   |

#### **Control Interface**

| Pin # | Name   | I/O/P | Description                                                                                                                                                                                                                                                                                               |  |  |

|-------|--------|-------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 30    | RESET  | I     | <b>Reset.</b> A positive pulse applied to this pin resets the internal counters, logic circuits, and the performance counters and control bits in the memory map to zero. The reset pulse is applied after the power becomes stable.                                                                      |  |  |

| 49    | DAIS   | I     | <b>Disable AIS.</b> A low disables the automatic insertion of AIS into the terminal side receive nibble/serial bit stream.                                                                                                                                                                                |  |  |

| 50    | TLCINV | I     | <b>Transmit Line Clock Invert.</b> A low inverts the output clock TCK/TCKL when operating in the dual rail mode.                                                                                                                                                                                          |  |  |

| 5     | CV     | 0     | <b>Coding Violation.</b> A positive pulse, one clock cycle wide, is generated when an <b>illegal</b> coding violation is detected.                                                                                                                                                                        |  |  |

| 6     | RAIS   | 0     | <b>Receive Alarm Indication Signal.</b> An active low alarm occurs within one millisecond after the E2/E3F detects an all ones condition, including in the presence of a 10 <sup>-3</sup> error rate. An incoming signal with a framing pattern and all ones in the data field is not mistaken as an AIS. |  |  |

| 7     | RLOC   | 0     | <b>Receive Loss of Clock.</b> An active low alarm occurs when there are no transitions in the received clock (RCK/RCKL). Recovery occurs on the first clock transition.                                                                                                                                   |  |  |

| 8     | RLOF   | 0     | Receive Loss of Frame. An active low alarm occurs when a valid frame cannot be detected accordingly to G.7XX recommendations.                                                                                                                                                                             |  |  |

| 12    | FE     | 0     | Framing Error. An active high alarm occurs when one or more framing bits are in error.                                                                                                                                                                                                                    |  |  |

| 25    | TLOC   | 0     | <b>Transmit Loss of Clock.</b> An active low alarm occurs when there are no transitions in the transmit clock (TCK). Recovery occurs on the first clock transition.                                                                                                                                       |  |  |

| 60    | BIP-4E | 0     | <b>BIP-4E.</b> A positive pulse occurs when the comparison between the received BIP-4 value and the calculated value does not match in a column.                                                                                                                                                          |  |  |

Note: I = Input, O = Output, P = Power

# **Functional Description**

The block diagram for the E2/E3F is shown in Figure 1. The E2/E3F receives NRZ data signal (RDL) and clock signal (RCKL), or a positive (RP) and negative (RN) rail signal and clock signal (RCK), from a line interface circuit. The selection of the line interface, dual rail or NRZ, is controlled by the external lead labeled NRZ LINE. Indications of HDB3 coding violation errors are provided on an external signal lead (CV) as pulses. Coding violation errors are also counted in an 8-bit saturating counter accessed by the microprocessor through the memory map.

The selection of the framing format (G.742, G.745, G.751 or G.753) is done by external control leads (M1 and M0), or by the microprocessor. The Framer Block performs frame alignment and alarm detection including Loss of Frame (RLOF), Loss of Clock (RLOC), AlS detection (RAIS) and BIP-4 detection (BIP-4E). A framing error (FE) output is also provided to indicate when any of the framing bits in the G. 7XX frame are in error. The disable AIS (DAIS) control lead permits the E2/E3F to provide receive data on the terminal side

regardless of frame alignment. The external alarm indications (latched and unlatched states) are provided in the memory map, and unlatched alarm indications are provided at signal leads.

The E2/E3F terminal side output block provides either a bit-serial or a nibble-parallel interface. The interface is selected by an external control lead (SER) or by the microprocessor. The bit-serial interface consists of the following signals: a data output signal (RSD), a clock output signal (RSC), a receive clock gapped output signal (RCG), and a framing pulse (RSF). The receive clock gapped signal (RCG) identifies framing and service bit times. The nibble-parallel interface consists of data output signal having a nibble format (RNIB3 through RNIB0), a clock output signal (RNC), and a framing pulse (RNF). In the nibble mode, the framing pattern, service bits and BIP-4 nibble are not provided at the interface. The receive nibble clock (RNC) is gapped during framing pattern, service bit and BIP-4 times.

The transmitter operates independently of the receiver, unless the loop timing feature( $\overline{LPT}$ ) is selected, when the receive clock becomes the transmitted clock. In the transmit direction, the terminal side bit-serial interface consists of: data input signal (XSD), a clock input signal (XCK), and a framing pulse ( $\overline{XSF}$ ). The nibble-parallel interface consists of the following signals: a data input signal having a nibble format (XNIB3 - XNIB0), a clock input signal (XCK), a framing output pulse ( $\overline{XNF}$ ), and a nibble output clock signal (XNC). The transmit nibble clock (XNC) is stretched to accommodate the framing pattern, service bit and BIP-4 times.

MT90372 provides interface to service bits as defined in G.7XX recommendations. The receive service bit interface consists of: data output (ROD), clock output (ROC), and framing pulse (ROF) output. The clock signal (ROC) is gapped and is provided for clocking out the service bits. The service bit states are also written into E2/E3F memory locations, which can be read by the microprocessor. The transmitted service bits are inserted into the frame format from either an external interface or from memory map locations. The transmit service bit interface consists of data input signal (TOD), a clock output (TOC), and a framing pulse (TOF) output.

To fix transmit time-base for the terminal payload multiplexer circuitry, while operating in the bit-serial mode, the E2/E3F provides a transmit frame reference generator. The transmit frame reference generator accepts an external 8.448 or 34.368 MHz clock signal (TCIN) and produces a clock out signal (TCOUT), a framing pulse (TFOUT), a clock gap signal (TCG), and a data signal (TDOUT). The data signal consists of G.7XX framing bits and zeros elsewhere.

The selection of the transmit line interface, dual rail or NRZ, is controlled by the NRZLINE control lead, which

also controls the receive interface selection. When the internal HDB3 Encoder Block is bypassed, the transmit line interface consists of a data signal (TDL) and a clock signal (TCKL). When the HDB3 encoder is enabled, the transmit line interface consists of positive (TP) and negative (TN) rail signals and a clock signal (TCK).

A high placed on the microprocessor control lead (MICRO) selects the microprocessor interface. All the external control leads, except the loop timing (LPT), receive AIS disable (DAIS), and the line interface control leads (NRZLINE) are disabled when the microprocessor interface is selected.

The microprocessor interface consists of eight bidirectional data and address leads (AD7 - AD0), along with other microprocessor control leads, including a ready (RDY) signal.

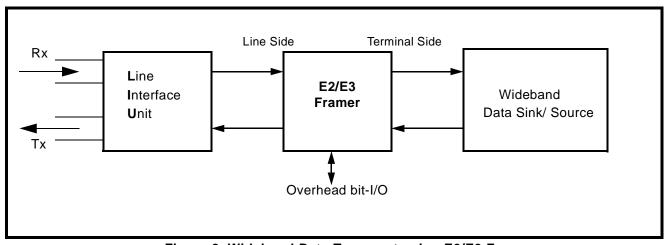

# **Typical Application**

The E2/E3 Framer is used for wideband data transport as shown in Figure 2. In the receive direction, the E2/E3 Framer receives NRZ or dual rail data from LIU, removes overhead bits and puts out only the payload of the incoming signal to the terminal. Overhead bits can be accessed through microprocessor or by service bit interface. In the transmit direction, the E2/E3 Framer receives data generated from Data Source, adds framing pattern and service bits and sends it out to LIU. The E2/E3 Framer handles wideband data at either 8448 or 34 368 Kb/s, and can optionally perform BIP-4 making data transport more reliable.

Figure 2. Wideband Data Transport using E2/E3 Framer

Notes.