CR TIMER S-8081B

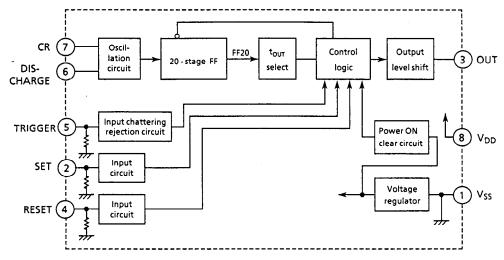

The S-8081B is a CMOS CR timer developed for appliances and industrial equipment use. It consists of a CR oscillator, a 20-stage divider, a power-on clear circuit, a trigger input chattering rejection circuit, an internal voltage regulator, a level shift circuit, and an output driver. It can be used as a high-precision, long-time monostable timer.

### ■ Features

- · Wide power supply operating range: 4.5 to 16.5 V

- Low current consumption: 200  $\mu$ A max.(C = 200 k $\Omega$ ,

$R = 0.0047 \mu F$ , open output)

- · Time can be set by external CR

- · Excellent oscillation stability because of built-in voltage regulator

- · Power-on clear circuit is integrated

- Both trigger I/O inverting operation and set/reset operation can be performed

# Applications

- · Time switch

- Long time delay generator

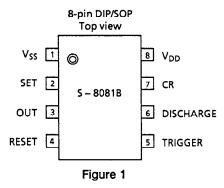

### ■ Pin Assignment

### Block Diagram

Figure 2

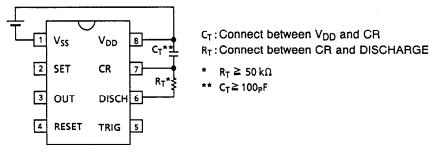

### Timer Setting

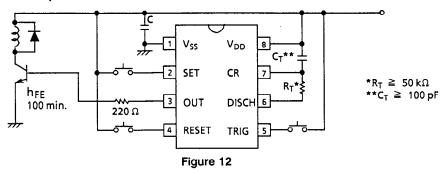

The timer time tout is decided by an external resistor RT and an external capacitor CT.

$t_{OUT} = (K \times R_T \times C_T \times 2^{19})$  sec.

K = time constant coefficient

10 s≤t<sub>OUT</sub>≤10 hours (recommended)

$R_T \ge 50 \text{ k}\Omega$ ,  $C_T \ge 100 \text{ pF (recommended)}$

Note: If other C<sub>T</sub> or R<sub>T</sub> is used than above recommended, the internal C and R influence t<sub>OUT</sub> and it becomes different in each unit.

Figure 3 Connection of external C<sub>T</sub> and R<sub>T</sub>

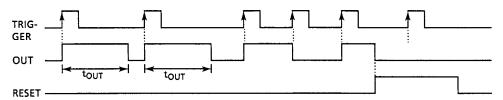

Figure 4 TRIGGER operation timing chart

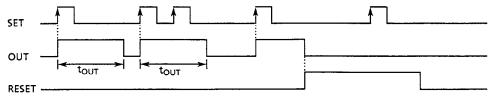

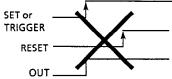

Figure 5 SET operation timing chart

$$\begin{split} t_{OUT} &= t_{OSC} \times 2^{19} \\ t_{OSC} &\leftrightarrows K \times R_T \times C_T \\ &\quad \text{(Recommended: } R_T \geq 50 \text{ k}\Omega, \text{ } C_T \geq 100 \text{ pF)} \end{split}$$

### Operation

### 1. SET terminal

At the rise of SET terminal, OUT goes high  $(V_{DD})$  and frequency dividing operation starts. This terminal has a pull-down resistor built in.

## 2. RESET terminal

By bringing RESET terminal high  $(V_{DD})$ , OUT goes low  $(V_{SS})$  and the internal counter is reset. Set or trigger input is ignored when reset is high.

This terminal has a pull-down resistor built in.

#### 3. TRIGGER terminal

At the rise of TRIGGER terminal, OUT level is inverted. When OUT changes from low (VSS) to high (VDD), frequency dividing operation starts. When OUT changes from high (VDD) to low (VSS), the internal counter is reset. When starting TRIGGER operation during setting operation, reset the S-8081B before TRIGGER input. This terminal has a chattering rejection circuit and a pull-down resistor built in. Chattering rejection time ≈ tosc×7

### 4. CR and DISCHARGE terminals

CR oscillation circuit can be constructed by connecting a timing capacitor  $C_T$  between  $V_{DD}$  and CRterminals, and by connecting a timing resistor R<sub>T</sub> between CR and DISCHARGE terminals. Set the oscillation period (tosc) following the formula below.

$t_{OSC} = K \times R_T \times C_T$

K: time constant coefficient

### 5. OUT terminal

At the rise of SET or TRIGGER terminal, OUT goes high (VDD) and frequency dividing operation starts. OUT goes low ( $V_{SS}$ ) after  $t_{OSC} \times 2^{19}$ .

When OUT is high (VDD) if TRIGGER rises or RESET goes high (VDD), OUT goes low (VSS) and the internal counter is reset.

### Absolute Maximum Ratings

Table 1

Unless otherwise specified: Ta = 25°C Unit Ratings v  $V_{SS} - 0.3$  to  $V_{DD} + 0.3$ ٧ - 30 to + 85 °C

Symbol **Conditions Parameter** Power supply voltage  $V_{SS} = 0 V$  $V_{DD}$ Input/output voltage<sup>4</sup>  $V_{IN}$ ,  $V_{OUT}$ Operating temperature Topr Storage temperature - 40 to + 125 °C  $T_{stg}$  $P_{D}$ at 25°C 300 Power dissipation mW

### **Electrical Characteristics**

Table 2

$V_{DD} = 12 \text{ V}, V_{SS} = 0 \text{ V}, Ta = 25^{\circ}\text{C}$

|                                | Parameter                               | Symbol                       | Conditions                                                         | Min.                | Тур.  | Max.                | Unit          |

|--------------------------------|-----------------------------------------|------------------------------|--------------------------------------------------------------------|---------------------|-------|---------------------|---------------|

| Operating power supply voltage |                                         | V <sub>DD</sub>              |                                                                    | 4.5                 |       | 16.5                | V             |

| Operating current consumption  |                                         | I <sub>DD</sub>              | R = 200 kΩ Open output<br>C = 0.0047 $\mu$ F                       | -                   |       | 200                 | μΑ            |

|                                | RESET, TRIGGER input<br>down resistance | R <sub>down</sub>            | V <sub>IH</sub> = V <sub>DD</sub>                                  | 50                  | _     | 400                 | kΩ            |

| High level input voltage       |                                         | V <sub>IH</sub>              |                                                                    | 0.8×V <sub>DD</sub> | _     | V <sub>DD</sub>     |               |

| Low level input voltage        |                                         | V <sub>IL</sub>              |                                                                    | Vss                 | _     | $0.2 \times V_{DD}$ | V             |

| High level output current      |                                         | I <sub>OH</sub> I            | V <sub>OH</sub> = 5.7 V V <sub>DD</sub> = 8.0 V                    | 10                  | 15    | T - 1               |               |

| Low level output current       |                                         | loL                          | $V_{OL} = 2.3 \text{ V } V_{DD} = 8.0 \text{ V}$                   | 20                  | 30    | 1 - 1               | mA            |

| Low level output voltage       |                                         | V <sub>OL</sub>              | V <sub>DD</sub> = 5.0 V I <sub>OUT</sub> = 3.2 mA                  | <b>—</b>            | _     | 0.4                 | V             |

| Time                           | constant coefficent                     | К                            | $C = 0.0047 \mu F$<br>$R = 200 k\Omega$                            | 1.276               | 1.450 | 1.624               | _             |

| CR                             | Power supply voltage fluctuation*       | △f/fosc<br>/△V <sub>DD</sub> | $V_{DD}$ = 4.5 to 16 V<br>C = 0.0047 $\mu$ F<br>R = 200 k $\Omega$ | _                   | 0.05  | _                   | %∧            |

| osc                            | Temperature fluctuation*                | △f/fosc<br>/△T               | Ta = $-20$ to $+60$ °C<br>C = $0.0047 \mu$ F<br>R = $200 k\Omega$  | _                   | 0.10  | _                   | % <i>/</i> °C |

<sup>\*</sup> Fluctuation of IC only

<sup>\*</sup> Excluding DISCHARGE terminal

## ■ AC Electrical Characteristics

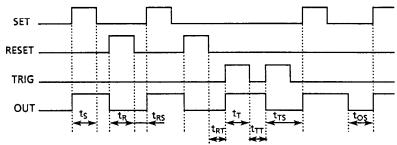

### 1. Input signal timing

Table 3

|                                                        |                   | $V_{DD} = 12 \text{ V}, V_{SS} = 0 \text{ V}, Ta = 25^{\circ}\text{C}$ |      |      |      |  |

|--------------------------------------------------------|-------------------|------------------------------------------------------------------------|------|------|------|--|

| Parameter                                              | Symbol            | Min.                                                                   | Тур. | Max. | Unit |  |

| SET pulse width                                        | ts                | 10                                                                     | _    | _    | μS   |  |

| RESET pulse width                                      | t <sub>R</sub>    | 10                                                                     | _    | _    | μ\$  |  |

| TRIG pulse width                                       | t <sub>T</sub>    | 16 x tosc                                                              | _    | _    | μS   |  |

| RESET-SET pulse interval                               | t <sub>RS</sub>   | 10                                                                     |      | _    | μS   |  |

| RESET-TRIG pulse interval                              | t <sub>RT</sub>   | 10                                                                     | _    |      | μs   |  |

| TRIG pulse interval                                    | t <sub>TT</sub>   | 10                                                                     | _    |      | μς   |  |

| SET input timing                                       | , t <sub>TS</sub> | t <sub>T</sub> + 10                                                    | _    | _    | μs   |  |

| Pulse interval between timer operation finish and SET  | tos               | 10                                                                     | _    | _    | μS   |  |

| Pulse interval between timer operation finish and TRIG | tor               | 10                                                                     | _    |      | μs   |  |

$t_{OSC}$ : oscillating frequency,  $(t_{OSC} = K \times R_T \times C_T)$

RESET input has the precedence over SET or TRIG input.

Figure 6

## 2. TRIG input pulse width and operation status

Table 4

| <u> </u>                                      | 2 4, 455 - 0 4, 18 - 23 C |

|-----------------------------------------------|---------------------------|

| TRIG input pulse width                        | Operation                 |

| TRIG input pulse width≥ 16 × t <sub>OSC</sub> | TRIG operation            |

| 7 x tosc < TRIG input pulse width < 16 x tosc | Indefinite*               |

| TRIG input pulse width ≤ 7 × t <sub>OSC</sub> | No TRIG operation         |

<sup>\*</sup>TRIG operation does not always start.

tosc: oscillating frequency

### Notes

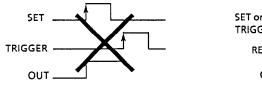

- 1. Notes on operation

- · Do not start TRIGGER operation during setting operation (see Figure 7). When starting TRIGGER operation during setting operation, reset the S-8081B before TRIGGER input.

- Do not set the RESET terminal high while SET or TRIGGER terminal is at high level. Or, the S-8081B will enter acceleration test mode. (see Figure 8)

Figure 7

Figure 8

#### 2. Status just after power-ON

A power-on clear circuit is built in the S-8081B and it initializes this IC at power-ON. During initialization, the S-8081B does not perform normal operation. Initialization time can not be defined clearly because it differs according to the voltage fluctuation at power-ON. See Table 5 for reference. Pay sufficient attention to the operation just after power-ON.

Table 5

|  | . Rise time | Initialization time*                    |  |  |

|--|-------------|-----------------------------------------|--|--|

|  | <1 ms       | 1 ms                                    |  |  |

|  | ≥ 1 ms      | Time duration from power-ON to the time |  |  |

|  |             | when V <sub>DD</sub> reaches 4.5 V.     |  |  |

Time duration from power-ON. At this time, the S-8081B does not operate normally.

#### 3. CR oscillation

CR oscillation circuit is always operating while power supply voltage is applied.

### 4. VIH level of input signal

When pulling up the SET, RESET or TRIGGER terminal, pay attention to  $V_{\text{IH}}$  level because they have pull-down resistors built in.

#### Acceleration Test Mode

The S-8081B has the acceleration test mode to check its F. F. function in a short time. This mode is performed as follows.

- (1) Put SET terminal from low to high level.

- (2) After (1), put RESET terminal from low to high level.

- (3) With keeping (1) and (2) status, input 511 clocks whose levels are the same as V<sub>DD</sub> from CR terminal. (From 1st to 9th and from 11th to 19th stages of 20-stage F.F. are all high. The 20-stage F.F. starts operation at the falling of input signal.)

- (4) Put RESET terminal low.

- (5) Put SET terminal low.

- (6) Input 514th clock from CR terminal.

- (7) 20th stage of the 20-stage F.F. goes high from low, and the OUT terminal goes low.

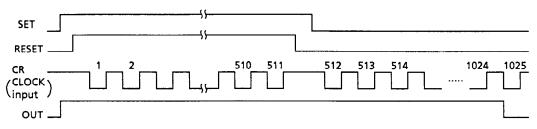

Figure 9

When releasing from acceleration test mode, initialize the S-8081B according to (a) or (b) below.

- (a) Turn the power off, and on again.

- (b) Put RESET terminal high level.

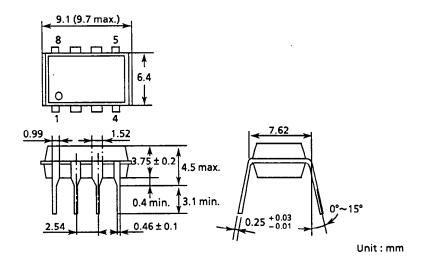

## Dimensions

## 1. 8-pin DIP

Figure 10

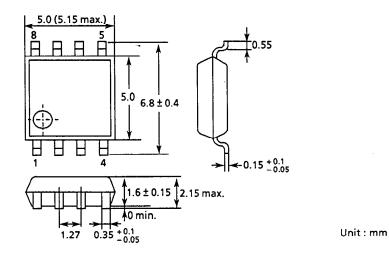

# 2. 8-pin SOP

Figure 11

## ■ Application Circuit Example

### Characteristics

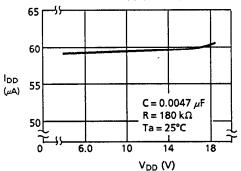

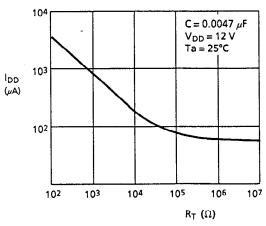

- 1. Current consumption characteristics

- 1.1 Operating current consumption I<sub>DD</sub> Power supply voltage V<sub>DD</sub>

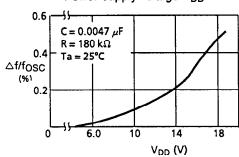

2. Oscillation frequency  $\Delta f/f_{OSC}$  - Power supply voltage  $V_{DD}$

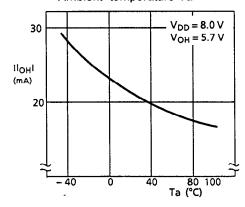

4. High level output current II<sub>OH</sub>I – Ambient temperature Ta

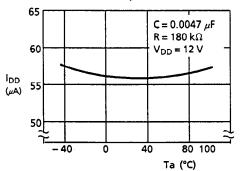

1.2 Operating current consumption I<sub>DD</sub> - Ambient temperature Ta

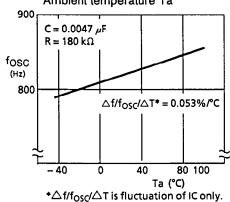

3. Oscillation frequency f<sub>OSC</sub> - Ambient temperature Ta

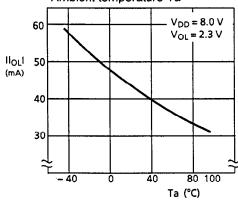

5. Low level output current II<sub>OL</sub>I --Ambient temperature Ta

:

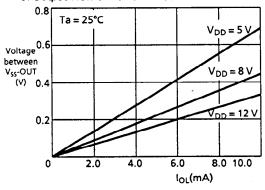

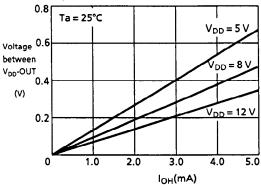

6. Output Nch driver characteristics

# 7. Output Pch driver characteristics

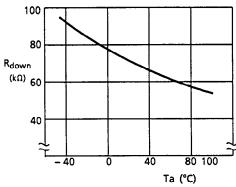

8. Pull-down resistance R<sub>down</sub> - Ambient temperature Ta

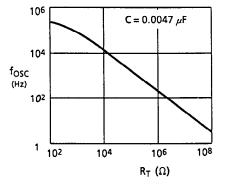

## 10. Oscillation frequency fosc -External resistance RT

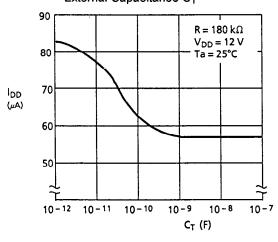

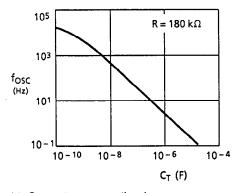

9. Oscillation frequency f<sub>OSC</sub> - External capacitance C<sub>T</sub>

11. Current consumption I<sub>DD</sub> - External resistance R<sub>T</sub>

12. Current consumption I<sub>DD</sub> - External Capacitance C<sub>T</sub>