#### DS34LV86T

## 3V Enhanced CMOS Quad Differential Line Receiver

#### **General Description**

The DS34LV86T is a high speed quad differential CMOS receiver that meets the requirements of both TIA/EIA-422-B and ITU-T V.11. The CMOS DS34LV86T features typical low static  $I_{CC}$  of 9 mA which makes it ideal for battery powered and power conscious applications. The TRI-STATE® enables, EN, allow the device to be disabled when not in use to minimize power consumption. The dual enable scheme allows for flexibility in turning receivers on and off.

The receiver output (RO) is guaranteed to be High when the inputs are left open. The receiver can detect signals as low as ±200 mV over the common mode range of ±10V. The receiver outputs (RO) are compatible with TTL and LVCMOS levels

#### **Features**

- Low power CMOS design (30 mW typical)

- Interoperable with existing 5V RS-422 networks

- Industrial temperature range

- Meets TIA/EIA-422-B (RS-422) and ITU-T V.11 recommendation

- 3.3V Operation

- ±7V common mode range @ V<sub>ID</sub> = 3V

- ±10V common mode range @ V<sub>ID</sub> = 0.2V

- Receiver OPEN input failsafe feature

- Guaranteed AC parameter:

Maximum Receiver Skew: 4 ns

Transition time: 10 ns

- Pin compatible with DS34C86T

- 32 MHz Toggle Frequency

- >6.5k ESD Tolerance (HBM)

- Available in SOIC packaging

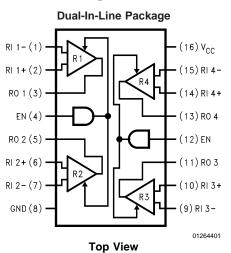

#### **Connection Diagram**

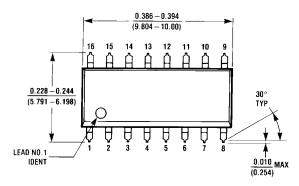

Order Number DS34LV86TM See NS Package Number M16A

#### **Truth Table**

| Enable | Inputs              | Output |

|--------|---------------------|--------|

| EN     | RI+-RI-             | RO     |

| L      | X                   | Z      |

| Н      | $V_{ID} \ge +0.2V$  | Н      |

| Н      | $V_{ID} \leq -0.2V$ | L      |

| Н      | Open†               | Н      |

L = Logic Low

H = Logic High

X = Irrelevant

Z = TRI-STATE

† = Open, Not Terminated

TRI-STATE® is a registered trademark of National Semiconductor Corporation.

#### **Absolute Maximum Ratings** (Note 1)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

Receiver Input Voltage

$(V_{ID}: RI+, RI-)$  ±14V

Receiver Input Voltage

$(V_{CM}: RI+, RI-)$   $\pm 14V$ Receiver Output Voltage (RO) -0.5V to  $V_{CC}+0.5V$ Receiver Output Current (RO)  $\pm 25$  mA

Maximum Package Power Dissipation @ +25°C

M Package 1190 mW

Derate M Package 9.8 mW/°C above +25°C Storage Temperature Range 65°C to +150°C

Lead Temperature Range

Soldering (4 Seconds) +260°C

ESD Ratings (HBM, 1.5k, 100 pF)

Receiver Inputs and

Enables  $\geq$  6.5 kV Other Pins  $\geq$  2 kV

# Recommended Operating Conditions

|                                   | Min | Тур | Max | Units |

|-----------------------------------|-----|-----|-----|-------|

| Supply Voltage (V <sub>CC</sub> ) | 3.0 | 3.3 | 3.6 | V     |

| Operating Free Air                |     |     |     |       |

| Temperature (T <sub>A</sub> )     | -40 | +25 | +85 | °C    |

#### **Electrical Characteristics** (Notes 2, 3)

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified.

| Symbol          | Parameter                                               | Conditions                                                                        | Pin             | Min  | Тур                   | Max  | Units |

|-----------------|---------------------------------------------------------|-----------------------------------------------------------------------------------|-----------------|------|-----------------------|------|-------|

| $V_{TH}$        | Differential Input Threshold                            | $V_{OUT} = V_{OH} \text{ or } V_{OL}$                                             | RI+,            | -200 | ±17.5                 | +200 | mV    |

|                 |                                                         | $-7V < V_{CM} < +7V$                                                              | RI-             |      |                       |      |       |

| V <sub>HY</sub> | Hysteresis                                              | V <sub>CM</sub> = 1.5V                                                            |                 |      | 35                    |      | mV    |

| V <sub>IH</sub> | Minimum High Level Input<br>Voltage                     |                                                                                   | EN              | 2.0  |                       |      | V     |

| $V_{IL}$        | Minimum Low Level Input<br>Voltage                      |                                                                                   | → EN            |      |                       | 0.8  | V     |

| R <sub>IN</sub> | Input Resistance                                        | $V_{IN} = -7V$ , +7V                                                              |                 | 5.0  | 8.5                   |      | kΩ    |

|                 |                                                         | (Other Input = GND)                                                               |                 |      |                       |      |       |

| I <sub>IN</sub> | Input Current                                           | V <sub>IN</sub> = +10V                                                            | RI+,            | 0    | 1.1                   | 1.8  | mA    |

|                 | (Other Input = 0V,<br>Power On or V <sub>CC</sub> = 0V) | $V_{IN} = +3V$                                                                    | RI+,            | 0    | 0.27                  |      | mA    |

|                 |                                                         | $V_{IN} = 0.5V$                                                                   |                 |      | -0.02                 |      | mA    |

|                 |                                                         | $V_{IN} = -3V$                                                                    |                 | 0    | -0.43                 |      | mA    |

|                 |                                                         | $V_{IN} = -10V$                                                                   |                 | 0    | -1.26                 | -2.2 | mA    |

| I <sub>EN</sub> |                                                         | $V_{IN} = 0V \text{ to } V_{CC}$                                                  | EN              |      |                       | ±1   | μΑ    |

| V <sub>OH</sub> | High Level Output Voltage                               | $I_{OH} = -6 \text{ mA}, V_{ID} = +1V$<br>$I_{OH} = -6 \text{ mA}, V_{ID} = OPEN$ |                 | 2.4  | 3                     |      | V     |

| V <sub>OH</sub> | High Level Output Voltage                               | $I_{OH} = -100 \mu A, V_{ID} = +1V$<br>$I_{OH} = -100 \mu A, V_{ID} = OPEN$       |                 |      | V <sub>CC</sub> - 0.1 |      | V     |

| V <sub>OL</sub> | Low Level Output Voltage                                | $I_{OL} = +6 \text{ mA}, V_{ID} = -1 \text{V}$                                    | RO              |      | 0.13                  | 0.5  | V     |

| l <sub>OZ</sub> | Output TRI-STATE<br>Leakage                             | $V_{IN} = V_{CC}$ or GND                                                          |                 |      |                       | ±50  | μΑ    |

|                 | Current                                                 | $EN = V_{IL}$                                                                     |                 |      |                       |      |       |

| I <sub>SC</sub> | Output Short Circuit Current                            | $V_O = 0V, V_{ID} \ge  200 \text{ mV} $ (Note 4)                                  |                 | -10  | -35                   | -70  | mA    |

| I <sub>cc</sub> | Power Supply Current                                    | No Load, All RI+, RI- = Open,<br>EN = V <sub>CC</sub> or GND                      | V <sub>CC</sub> |      | 9                     | 15   | mA    |

#### Switching Characteristics (Notes 3, 9, 10)

Over Supply Voltage and Operating Temperature ranges, unless otherwise specified.

| Symbol           | Parameter                                            | Conditions             | Min | Тур  | Max | Units |

|------------------|------------------------------------------------------|------------------------|-----|------|-----|-------|

| t <sub>PHL</sub> | Propagation Delay High to Low                        | C <sub>L</sub> = 15 pF | 6   | 17.5 | 35  | ns    |

| t <sub>PLH</sub> | Propagation Delay Low to High                        | (Figures 1, 2)         | 6   | 17.8 | 35  | ns    |

| t <sub>r</sub>   | Rise Time (20% to 80%)                               |                        |     | 4.1  | 10  | ns    |

| t <sub>f</sub>   | Fall Time (80% to 20%)                               |                        |     | 3.3  | 10  | ns    |

| t <sub>PHZ</sub> | Disable Time                                         | C <sub>L</sub> = 50 pF |     |      | 40  | ns    |

| t <sub>PLZ</sub> | Disable Time                                         | (Figures 3, 4)         |     |      | 40  | ns    |

| t <sub>PZH</sub> | Enable Time                                          |                        |     |      | 40  | ns    |

| t <sub>PZL</sub> | Enable Time                                          |                        |     |      | 40  | ns    |

| t <sub>SK1</sub> | Skew,  t <sub>PHL</sub> - t <sub>PLH</sub>  (Note 5) | C <sub>L</sub> = 15 pF |     | 0.3  | 4   | ns    |

| t <sub>SK2</sub> | Skew, Pin to Pin (Note 6)                            |                        |     | 0.6  | 4   | ns    |

| t <sub>SK3</sub> | Skew, Part to Part (Note 7)                          |                        |     | 7    | 17  | ns    |

| f <sub>MAX</sub> | Maximum Operating Frequency                          | C <sub>L</sub> = 15 pF | 32  |      |     | MHz   |

|                  | (Note 8)                                             |                        |     |      |     |       |

**Note 1:** "Absolute Maximum Ratings" are those values beyond which the safety of the device cannot be guaranteed. They are not meant to imply that the devices should be operated at these limits. The table of "Electrical Characteristics" specifies conditions of device operation.

Note 2: Current into device pins is defined as positive. Current out of device pins is defined as negative. All voltages are referenced to ground except V<sub>ID</sub>.

Note 3: All typicals are given for:  $V_{CC}$  = +3.3V,  $T_A$  = +25°C.

Note 4: Short one output at a time to ground. Do not exceed package power dissipation ratings.

Note 5: t<sub>SK1</sub> is the |t<sub>PHL</sub> - t<sub>PLH</sub>| of a channel.

Note 6:  $t_{SK2}$  is the maximum skew between any two channels within a device, on either edge.

Note 7:  $t_{SK3}$  is the difference in propagation delay times between any channels of any devices. This specification (maximum limit) applies to devices within  $V_{CC} \pm 0.1V$  of one another, and a Delta  $T_A = \pm 5^{\circ}C$  (between devices) within the operating temperature range. This parameter is guaranteed by design and characterization.

Note 8: All channels switching, output duty cycle criteria is 40%/60% measured at 50% Input = 1V to 2V, 50% Duty Cycle,  $t_r/t_f \le 5$  ns. This parameter is guaranteed by design and characterization.

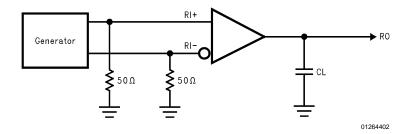

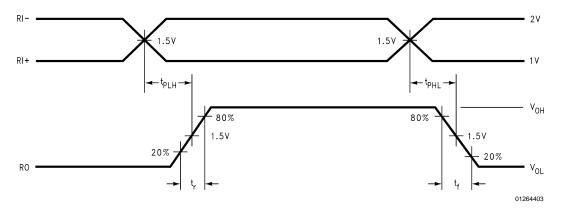

#### **Parameter Measurement Information**

FIGURE 1. Receiver Propagation Delay and Transition Time Test Circuit (Notes 9, 10)

FIGURE 2. Receiver Propagation Delay and Transition Time Waveform (Notes 9, 10)

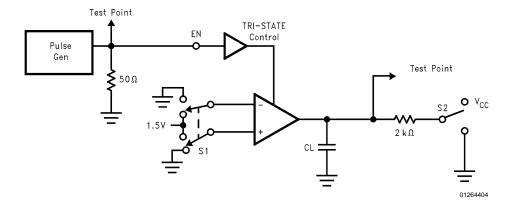

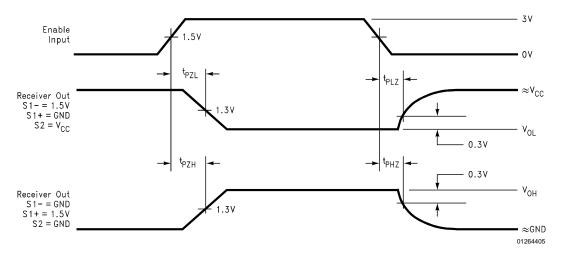

#### Parameter Measurement Information (Continued)

Note 9: Generator waveform for all tests unless otherwise specified: f = 1 MHz, Duty Cycle = 50%,  $Z_O = 50\Omega$ ,  $t_f \le 10$  ns,  $t_f \le 10$  ns. Note 10:  $C_L$  includes probe and jig capacitance.

FIGURE 3. Receiver TRI-STATE Test Circuit

FIGURE 4. Receiver TRI-STATE Output Enable and Disable Waveforms (Notes 9, 10)

## **Typical Application Information**

General application guidelines and hints for differential drivers receivers may be found in the following application notes:

AN-214, AN-457, AN-805, AN-847, AN-903, AN-912, AN-916 Power Decoupling Recommendations: Bypass caps must be used on power pins. High frequency ceramic (surface mount is recommended) 0.1  $\mu$ F in parallel with 0.01  $\mu$ F at the power supply pin. A 10  $\mu$ F or greater solid tantalum or electrolytic should be connected at the power entry point on the printed circuit board.

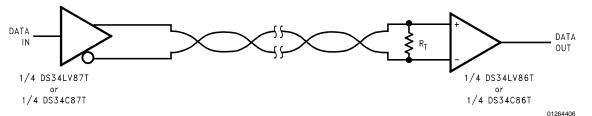

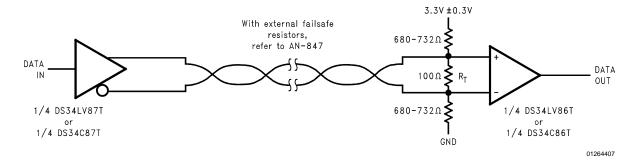

## Typical Application Information (Continued)

$\ensuremath{R_{T}}$  is optional although highly recommended to reduce reflection

**FIGURE 5. Typical Receiver Connections**

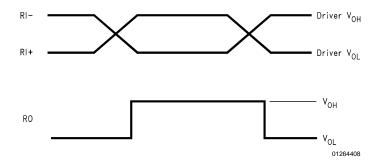

FIGURE 6. Typical Receiver Output Waveforms

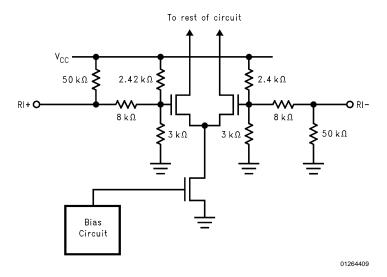

FIGURE 7. Typical Receiver Input Circuit

# Typical Application Information (Continued)

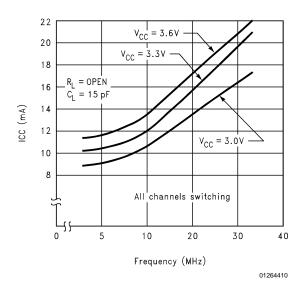

FIGURE 8. Typical  $I_{\text{CC}}$  vs Frequency

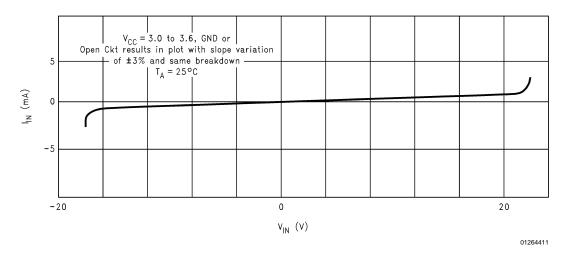

FIGURE 9.  $I_{IN}$  vs  $V_{IN}$  (Power On, Power Off)

# Typical Application Information (Continued)

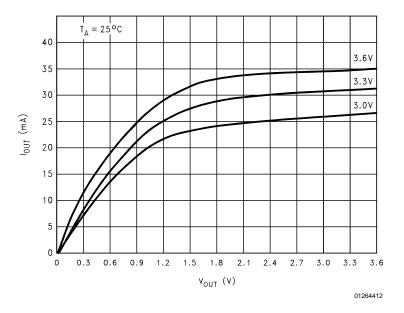

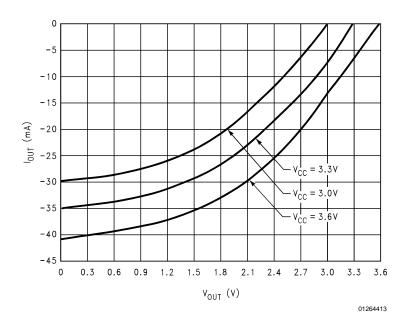

FIGURE 10.  $I_{OL}$  vs  $V_{OL}$

FIGURE 11.  $I_{OH}$  vs  $V_{OH}$

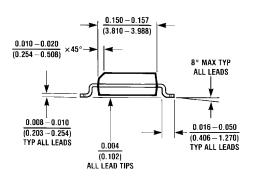

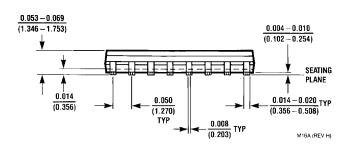

#### Physical Dimensions inches (millimeters) unless otherwise noted

**Dual-In-Line Package** Order Number DS34LV86TM **NS Package Number M16A**

#### LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

**National Semiconductor** Corporation

Email: support@nsc.com

www.national.com

**National Semiconductor**

Europe

Fax: +49 (0) 180-530 85 86 Email: europe.support@nsc.com Deutsch Tel: +49 (0) 69 9508 6208 English Tel: +44 (0) 870 24 0 2171

Français Tel: +33 (0) 1 41 91 8790

**National Semiconductor** Asia Pacific Customer Response Group Tel: 65-2544466

Fax: 65-2504466 Email: ap.support@nsc.com **National Semiconductor**

Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.