DEVICE PERFORMANCE SPECIFICATION

# **KODAK KSC-1000 Timing Generator**

July 12, 2003 Revision 1.0

# **TABLE OF CONTENTS**

| TABLE OF FIGURES                                | 3  |

|-------------------------------------------------|----|

| TABLE 05 TABLE 0                                |    |

| TABLE OF TABLES                                 |    |

| SUMMARY SPECIFICATION                           |    |

|                                                 |    |

| DEVICE DESCRIPTION                              | 5  |

| Architecture                                    | Ę  |

| Overall                                         |    |

| Sequence of Operations                          | 6  |

| Horizontal Line Synchronization                 |    |

| Pin Description and Device Orientation          | S  |

| OPERATING CONDITIONS                            |    |

| ABSOLUTE MAXIMUM RATINGS                        |    |

| RECOMMENDED OPERATING CONDITIONS                |    |

| DECOUPLING, GROUNDING AND POWER-UP REQUIREMENTS |    |

| ELECTROSTATIC DISCHARGE PROTECTION.             |    |

| Power Dissipation                               |    |

| CONDITIONS:                                     |    |

| ELECTRICAL CHARACTERISTICS                      |    |

| DC Characteristics                              |    |

| AC Characteristics                              |    |

| Oscillator Buffer Characteristics               |    |

| DLL Specifications                              |    |

| SERIAL INTERFACE SPECIFCATIONS                  | 21 |

| TIMING SPECIFICATIONS                           | 21 |

| REGISTER DESCRIPTIONS                           |    |

| Register Map                                    |    |

| Frame Table Pointer Register                    |    |

| General Setup Register                          |    |

| General Control Register                        |    |

| INTG_STRT Setup Register                        |    |

| INTG_STRT Line Register                         |    |

| Signal Polarity Register                        |    |

| Offset Register                                 | 31 |

| Width Register                                  | 32 |

| Frame Table Access Register                     | 32 |

| Frame Table Sequence Control                    |    |

| Line Table Access Register                      |    |

| Status Register                                 |    |

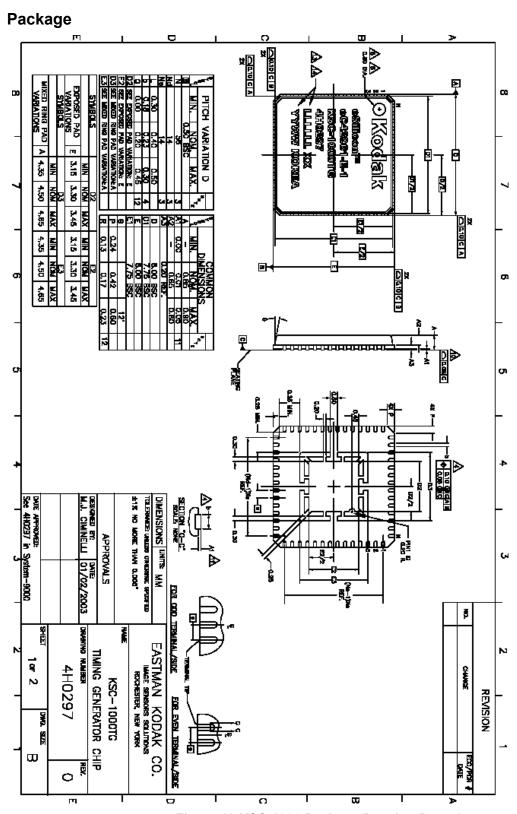

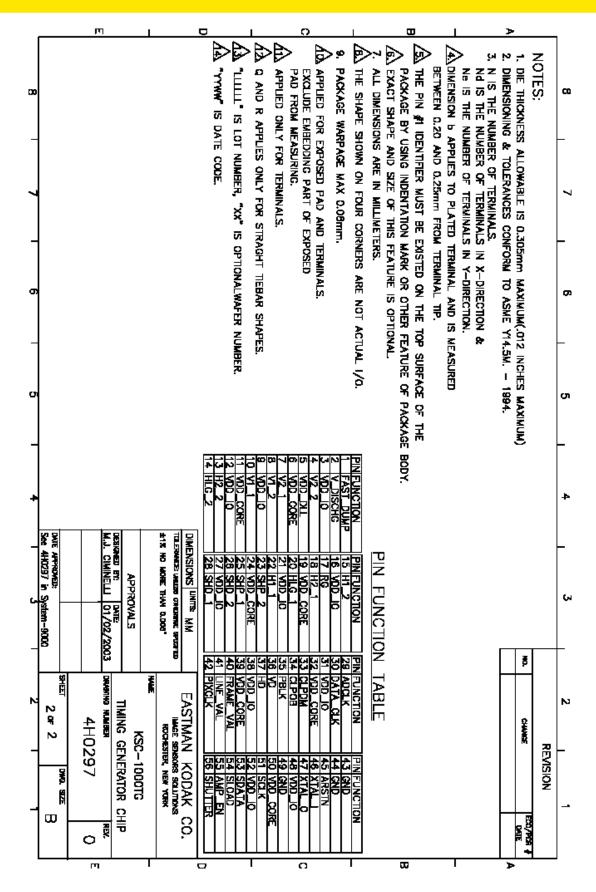

| MECHANICAL DRAWINGS                             | 38 |

| Package                                         | રા |

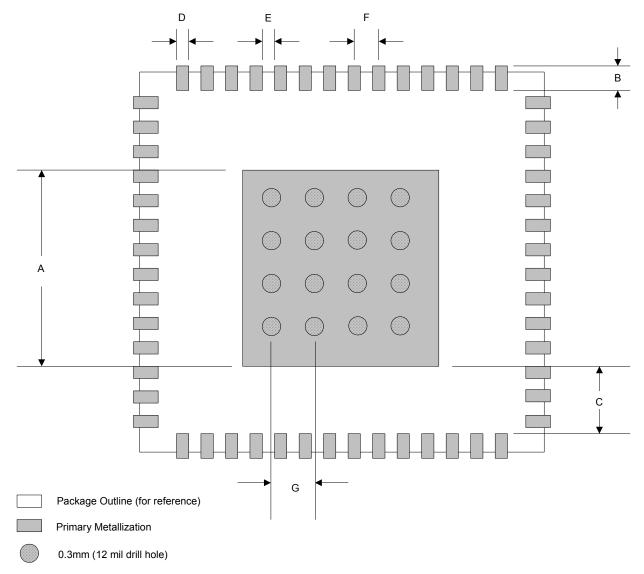

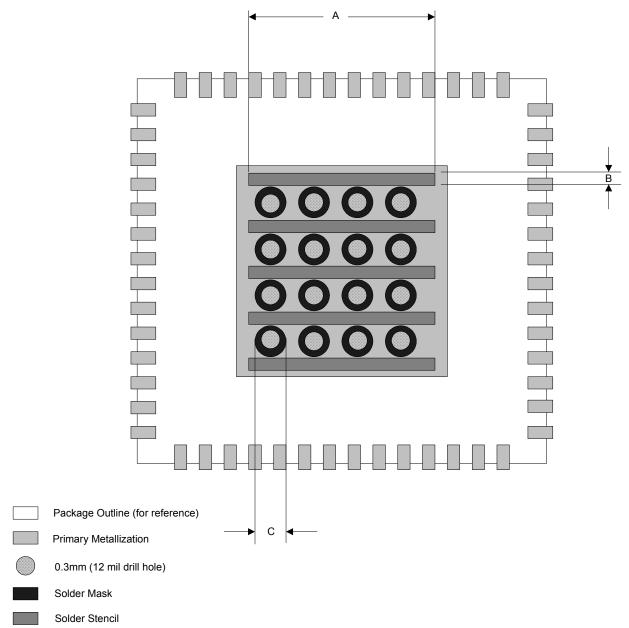

| PC Board Geometry and Attachment                |    |

| PACKAGE MOISTURE SENSITIVITY LEVEL              |    |

| QUALITY ASSURANCE AND RELIABILITY               |    |

|                                                 |    |

| ORDERING INFORMATION                            | 45 |

| AVAILABLE PART CONFIGURATIONS                   | 45 |

| REVISION CHANGES                                | 46 |

# **FIGURES**

| FIGURE 1 KSC 1000 BLOCK DIAGRAM                                                |    |

|--------------------------------------------------------------------------------|----|

| FIGURE 2 KSC-1000 SEQUENCE FLOW DIAGRAM                                        |    |

| FIGURE 3 HD FUNCTIONALITY                                                      | 8  |

| FIGURE 4 KSC-1000 PIN DIAGRAM                                                  |    |

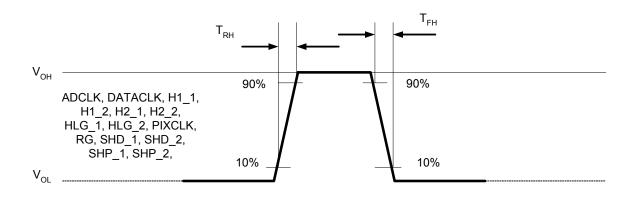

| FIGURE 5 PIXEL RATE SIGNAL RISE AND FALL TIME                                  |    |

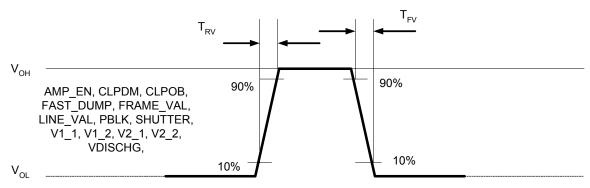

| FIGURE 6 LINE AND FRAME RATE SIGNAL RISE AND FALL TIME                         | 17 |

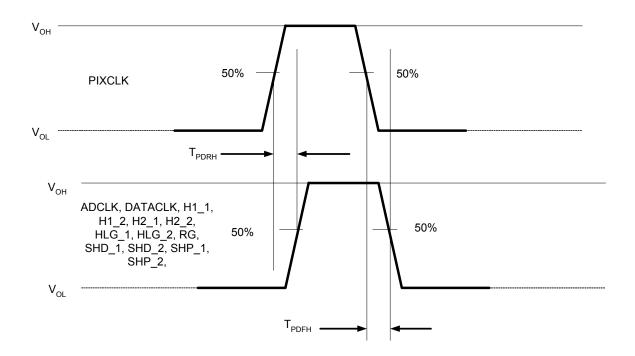

| FIGURE 7 PIXEL RATE SIGNAL RISE AND FALL TIME DELTA PROPAGATION DELAY          |    |

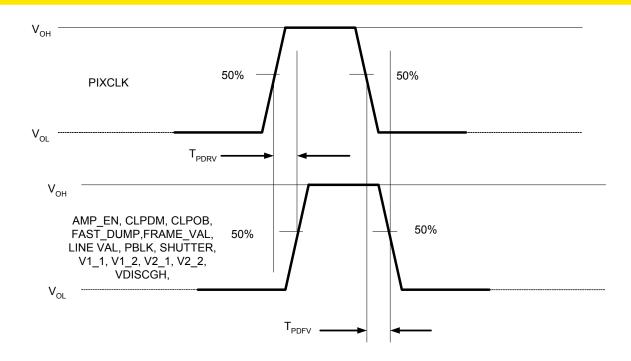

| FIGURE 8 LINE AND FRAME RATE SIGNAL RISE AND FALL TIME DELTA PROPAGATION DELAY |    |

| FIGURE 9 CRYSTAL OSCILLATOR CIRCUIT                                            |    |

| FIGURE 10 SERIAL WRITE TIMING                                                  |    |

| FIGURE 11 SERIAL READ TIMING                                                   |    |

| FIGURE 12 INTG_STRT TIMING                                                     |    |

| FIGURE 13 KSC-1000 PACKAGE DRAWING PAGE 1                                      | 38 |

| FIGURE 14 KSC-1000 PACKAGE DRAWING PAGE 2                                      |    |

| FIGURE 15 KSC-1000 PC BOARD GEOMETRY                                           |    |

| FIGURE 16 KSC-1000 GROUND PADDLE SOLDER STENCIL AND SOLDER MASK                | 42 |

| TABLES                                                                         |    |

| TABLE 1 KSC-1000 PIN DESCRIPTIONS                                              |    |

| TABLE 2 KSC-1000 ABSOLUTE MAXIMUM RATINGS                                      |    |

| TABLE 3 KSC-1000 RECOMMENDED OPERATING CONDITIONS                              |    |

| TABLE 4 POWER SUPPLY CURRENT REQUIREMENTS                                      |    |

| Table 5 KSC-1000 DC Characteristics                                            |    |

| Table 6 KSC-1000 AC Characteristics                                            |    |

| TABLE 7 OSCILLATOR BUFFER CHARACTERISTICS                                      |    |

| TABLE 9 SERIAL INTERFACE TIMING SPECIFICATIONS                                 |    |

| TABLE 10 SERIAL INTERFACE REGISTER MAP                                         |    |

| TABLE 10 SERIAL INTERFACE REGISTER MAP                                         | ∠ა |

| TABLE 12 GENERAL SETUP REGISTER MAP                                            |    |

| TABLE 13 LINE VALID QUADRATURE START DESCRIPTOR TABLE                          |    |

| TABLE 14 GENERAL CONTROL REGISTER MAP                                          |    |

| TABLE 15 INTG STRT SETUP REGISTER MAP.                                         |    |

| TABLE 16 INTG STRT LINE REGISTER MAP                                           |    |

| TABLE 17 SIGNAL POLARITY REGISTER MAP                                          |    |

| TABLE 18 OFFSET REGISTER MAP.                                                  |    |

| Table 19 Width Register Map                                                    |    |

| TABLE 20 FRAME TABLE ACCESS REGISTER MAP                                       |    |

| TABLE 21 FRAME TABLE ADDRESS DESCRIPTOR                                        |    |

| TABLE 22 FRAME TABLE DATA DESCRIPTOR                                           |    |

| TABLE 23 FRAME TABLE EVENT DESCRIPTOR                                          |    |

| Table 24 Horizontal Binning Factor Descriptor                                  |    |

| TABLE 25 LINE TABLE ACCESS REGISTER MAP                                        |    |

| TABLE 26 LINE TABLE ADDRESS DESCRIPTOR                                         |    |

| TABLE 27 LINE TABLE DATA DESCRIPTOR                                            |    |

| TABLE 28 STATUS REGISTER MAP.                                                  |    |

| TABLE 29 KSC-1000 PC BOARD GEOMETRY DIMENSIONS                                 |    |

| TARLE 30 KSC-1000 GROUND PADDLE SOLDER STENCIL AND SOLDER MASK DIMENSIONS      |    |

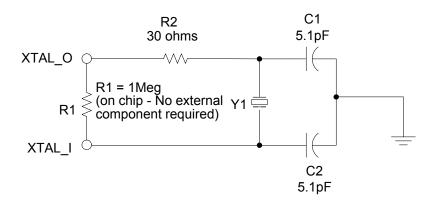

**Clock Oscillator**

#### **SUMMARY SPECIFICATION**

# **KODAK KSC-1000 Timing Generator**

#### **Description**

The Kodak KSC-1000 Timing Generator simplifies camera design by providing all of the timing signals necessary to operate the entire family of Kodak area array image sensors (Full Frame and Interline CCDs) and associated analog front-end (AFE) circuits. Full programability through a simple 3-wire serial interface allows maximum flexibility in sensor operation. Frame tables and line tables, in conjunction with control registers, permit the customization of the timing outputs to meet applicationspecific requirements. Multiple outputs, binning, electronic shuttering, and fast line dump are fully supported. The use of a Delay Locked Loop (DLL) circuit provides for precise control and sub-pixel positioning of timing signals, and stability over variations in voltage and temperature.

KSC-1000 Rev. 1.0 July 12, 2003

| Parameter                | Value                                                         |  |  |  |

|--------------------------|---------------------------------------------------------------|--|--|--|

| Maximum Image Size       | 8192 (H) x 8192 (V)                                           |  |  |  |

| Pixel Rate               | 4.13MHz to 60 MHz                                             |  |  |  |

| Integration Time         | 1 pixel clock to infinity                                     |  |  |  |

| Packaging                | 8 mm x 8 mm, 56-pin MLF                                       |  |  |  |

| Power Dissipation        | 265mW @40MHz, 12m/<br>Pixel Rate Clock Outpu<br>Drive Leve    |  |  |  |

| Power Supply Voltage     | 1.8 and 3.3 V                                                 |  |  |  |

| Input Clock              | 2x pixel clock                                                |  |  |  |

|                          | 8.26 MHz to 10 MHz<br>Clock Oscillator                        |  |  |  |

| Input Clock Requirements | 10 MHz to 60 MHz<br>Crystal Oscillator or Clock<br>Oscillator |  |  |  |

|                          | 60 MHz to 120 MHz                                             |  |  |  |

| Vertical Binning                        | no limit                   |

|-----------------------------------------|----------------------------|

| <b>Horizontal Binning</b>               | x4 max                     |

| V pulse min                             | 1 pixel clock              |

| V pulse max                             | 8192 pixel clocks          |

| Independent HCLK                        | Duty cycle: 25% to 75%     |

| control                                 | Offset: 1/64 pixel period  |

| Independent reset gate                  | Width: to 50%              |

| (RG) and AFE signal control             | Offfset: 1/64 pixel period |

| Pixel Rate Clock Output<br>Drive Levels | 12mA or 24mA               |

| Asynchronous triggered capture          | supported                  |

| Operating Temperature                   | -20°C to +70°C             |

|                                         |                            |

#### **DEVICE DESCRIPTION**

#### **Architecture**

#### **Overall**

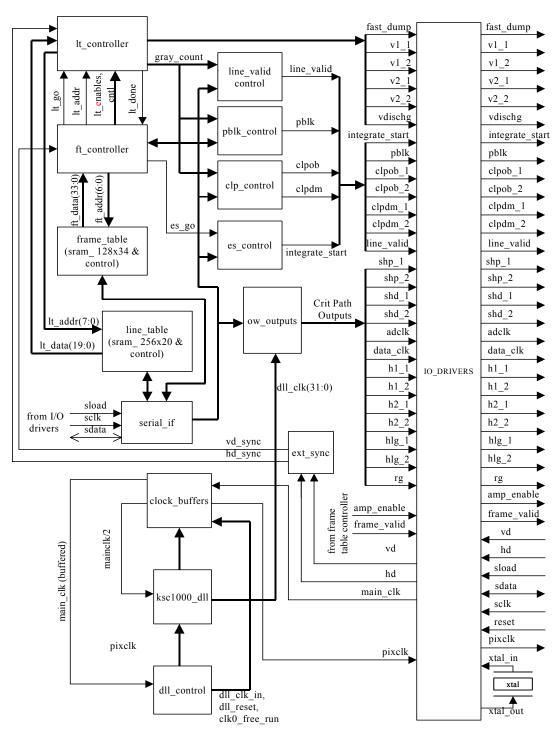

Figure 1 KSC 1000 Block Diagram

The KSC-1000 provides all of the signals necessary for an imaging system using Kodak Full Frame (KAF) or Interline (KAI) family of image sensors. It also provides the signals necessary for operation of 2 analog front-end (AFE) chips, enabling independent optimization of the AFE chips for dual channel readout devices.

The KSC-1000 utilizes a Delay Locked Loop (DLL) to maintain precise control of the pixel clock rate signals over process, temperature and voltage variations. There are 8 independent DLLs, with only one being switched on at any given time. The DLLs operate from 4.13MHz to 60MHz. The output frequency of the DLL is ½ the input oscillator frequency. The output of the DLL provides 64 positions within the pixel clock period for precise control of the positioning of the pixel rate clock signals.

The KSC-1000 has 8 control registers, along with 2 blocks of Static Random Access Memory (SRAM) configured as Frame Tables and Line Tables. The fast dump gate signal and vertical clocks are defined in the line tables in terms of number of pixel clocks. This architecture provides

complete flexibility in positioning these signals relative to one another. For example, 3 line tables could be used to define a flush, integrate and readout sequence. There are 16 line tables available. Line Table sequencing is controlled by Frame Tables.

In conjunction with the control registers, frame tables are used to control AFE clamping and blanking pulses, horizontal binning, frame and line valid signals, AFE clocks, a CCD video amplifier power supply switch and integration control. Sequencing between frame table entries or between frame tables can occur either by a programmed counts, or can be synchronized by an external controller.

The KSC-1000 supports imager array sizes up to 8192 pixels by 8192 pixels. Gray coding is used on the internal horizontal pixel counter to minimize the risk of digital noise coupling into the analog signal processing. A 3 wire serial interface is used to program the device. Binary to Gray code conversion is performed internally where needed to allow programming using standard binary counts.

# **Sequence of Operations**

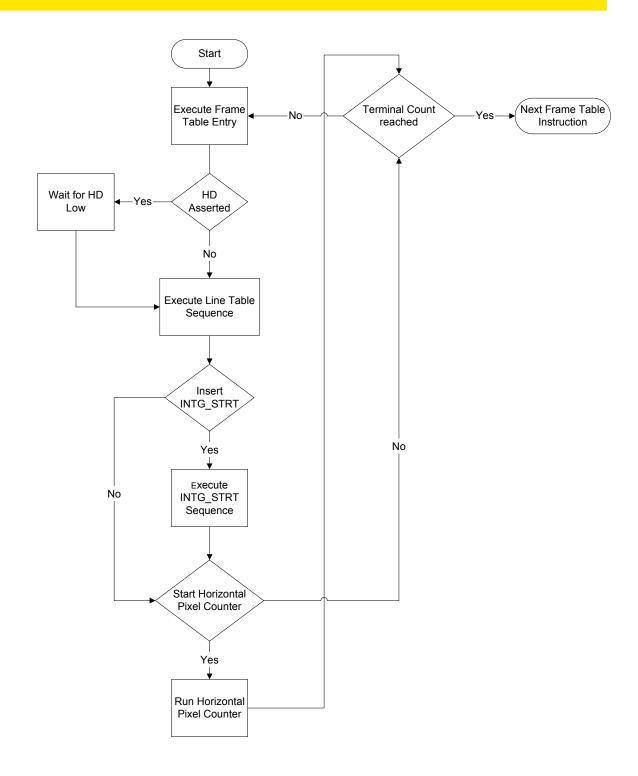

The KSC-1000 must be programmed via the serial interface prior to operation. A sequence of operations is initiated by placing the device in execution mode and full power mode in the General Control register. Execution will start at the first entry of the frame table indicated in the frame table pointer register.

Each frame table entry will either execute a line table sequence or perform a jump instruction.

Figure 2 is a flow diagram of the sequence of operation. Normally a line table will be called by the first entry of the frame table. After the line table sequence is executed, a test is performed to see if the INTG\_STRT signal needs to be asserted. This could occur if the Force INTG\_STRT bit is set in the frame table entry, or if the line counter equals the value set in the INTG\_STRT Line Register and the Check and Increment Line Counter bit is set in the frame table

entry. If the test is positive, the INTG\_STRT sequence is inserted immediately after completion of the line table.

Next, another test is performed to determine if the horizontal counter needs to be started. This would be the case for image readout. However for image sensor flush operations, the counter would not be started. Setting the hclk\_h bit in the last valid line table entry forces the horizontal counter to start.

Finally a test is performed to determine if the frame table entry needs to be executed again. If this frame table entry has been executed the number of times indicated in the count field, operation continues with the next entry in the frame table. Otherwise this entry is executed again.

Figure 2 KSC-1000 Sequence Flow Diagram

# **Horizontal Line Synchronization**

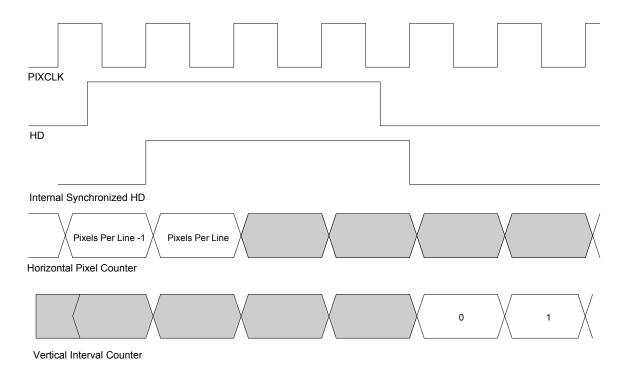

Horizontal line timing is controlled by the state of the HD signal. Asserting the HD signal high prior to reaching the terminal count of the horizontal pixel counter holds off the start of line table execution (start of the vertical interval counter). Line table execution will not begin until HD is driven low. This feature allows an external controller to synchronize horizontal line readout. Holding the HD signal low gives the KSC-1000 full control over horizontal line readout. HD functionality is illustrated in Figure 3.

Figure 3 HD Functionality

#### **Physical Description**

# **Pin Description and Device Orientation**

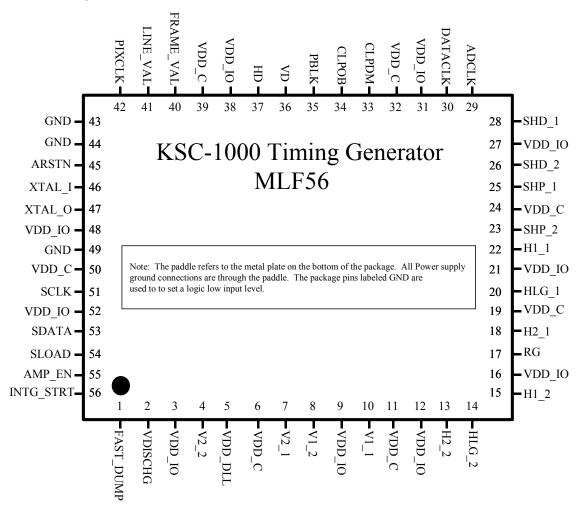

Figure 4 KSC-1000 Pin Diagram

| Pin | Name      | Description                                    |

|-----|-----------|------------------------------------------------|

| 1   | FAST_DUMF | Fast Dump Gate Output                          |

| 2   | VDISCHG   | Vertical Phase Discharge Switch Control Output |

| 3   | VDD_IO    | 3.3V I/O Power Supply                          |

| 4   | V2_2      | Vertical Clock Phase 2 Output 2                |

| 5   | VDD_DLL   | 1.8V DLL Power Supply                          |

| 6   | VDD_C     | 1.8V Core Logic Power Supply                   |

| 7   | V2_1      | Vertical Clock Phase 2 Output 1                |

| 8   | V1_2      | Vertical Clock Phase 1 Output 2                |

Email: imagers@kodak.com

| 9  | VDD_IO    | 3.3V I/O Power Supply                                           |

|----|-----------|-----------------------------------------------------------------|

| 10 | V1_1      | Vertical Clock Phase 1 Output 1                                 |

| 11 | VDD_C     | 1.8V Core Logic Power Supply                                    |

| 12 | VDD_IO    | 3.3V I/O Power Supply                                           |

| 13 | H2_2      | Horizontal Clock Phase 2 Output 2                               |

| 14 | HLG_2     | Horizontal Last Gate Output 2                                   |

| 15 | H1_2      | Horizontal Clock Phase 1 Output 2                               |

| 16 | VDD_IO    | 3.3V I/O Power Supply                                           |

| 17 | RG        | Reset Gate Output Pulse                                         |

| 18 | H2_1      | Horizontal Clock Phase 2 Output 1                               |

| 19 | VDD_C     | 1.8V Core Logic Power Supply                                    |

| 20 | HLG_1     | Horizontal Last Gate Output 1                                   |

| 21 | VDD_IO    | 3.3V I/O Power Supply                                           |

| 22 | H1_1      | Horizontal Clock Phase 1 Output 1                               |

| 23 | SHP_2     | AFE 2 Reset Level Sampling Pulse                                |

| 24 | VDD_C     | 1.8V Core Logic Power Supply                                    |

| 25 | SHP_1     | AFE 1 Reset Level Sampling Pulse                                |

| 26 | SHD_2     | AFE 2 Video Level Sampling Pulse                                |

| 27 | VDD_IO    | 3.3V I/O Power Supply                                           |

| 28 | SHD_1     | AFE 1 Video Level Sampling Pulse                                |

| 29 | ADCLK     | A/D Clock                                                       |

| 30 | DATACLK   | Data Latch Clock                                                |

| 31 | VDD_IO    | 3.3V I/O Power Supply                                           |

| 32 | VDD_C     | 1.8V Core Logic Power Supply                                    |

| 33 | CLPDM     | AFE Input Optical Black Level Clamp                             |

| 34 | CLPOB     | AFE Post Analog to Digital Conversion Optical Black Level Clamp |

| 35 | PBLK      | AFE Pre-Blanking Clock                                          |

| 36 | VD        | Vertical Sync (Frame Request) Input                             |

| 37 | HD        | Horizontal Sync (Line Request) Input                            |

| 38 | VDD_IO    | 3.3V I/O Power Supply                                           |

| 39 | VDD_C     | 1.8V Core Logic Power Supply                                    |

| 40 | FRAME_VAL | Frame Valid (Vertical Sync) Output                              |

| 41 | LINE_VAL  | Line Valid (Horizontal Sync) Output                             |

| 42 | PIXCLK    | Pixel Clock Output                                              |

| 43 | GND       | Ground                                                          |

| 44 | GND       | Ground                                                          |

| 45 | ARSTN     | Asynchronous Reset Input                                        |

|    |           |                                                                 |

| 46 | XTAL_I    | Crystal Oscillator or Clock Oscillator Input (2X Pixel Clock) |

|----|-----------|---------------------------------------------------------------|

| 47 | XTAL_O    | Crystal Oscillator Output (2X Pixel Clock)                    |

| 48 | VDD_IO    | 3.3V I/O Power Supply                                         |

| 49 | GND       | Ground                                                        |

| 50 | VDD_C     | 1.8V Core Logic Power Supply                                  |

| 51 | SCLK      | Serial Clock Input                                            |

| 52 | VDD_IO    | 3.3V I/O Power Supply                                         |

| 53 | SDATA     | Serial Data I/O                                               |

| 54 | SLOAD     | Serial Load Input                                             |

| 55 | AMP_EN    | Video Amplifier Enable Control Output                         |

| 56 | INTG_STRT | Integration initiation pulse                                  |

|    |           |                                                               |

**Table 1 KSC-1000 Pin Descriptions**

# **OPERATING CONDITIONS**

# **Absolute Maximum Ratings**

| Parameter                 | Symbol           | Min       | Max          | Unit |

|---------------------------|------------------|-----------|--------------|------|

| IO Supply Voltage         | VDD_IO           | VSS - 0.3 | 4.6          | V    |

| Core Supply Voltage       | VDD_C            | VSS - 0.3 | 2.5          | V    |

| DLL Supply Voltage        | VDD_DLL          | VSS - 0.3 | 2.5          | V    |

| All Input Voltages        | VI               | VSS - 0.3 | VDD_IO + 0.3 | V    |

| Temperature Range Storage | T <sub>STG</sub> | -55       | +150         | °C   |

# **Table 2 KSC-1000 Absolute Maximum Ratings**

Long term exposure to absolute maximum ratings may affect device reliability and damage may occur if exposed to conditions exceeding the absolute maximums.

# **Recommended Operating Conditions**

| Parameter           | Symbol           | Min | Тур | Max | Unit |

|---------------------|------------------|-----|-----|-----|------|

| IO Supply Voltage   | VDD_IO           | 3.0 | 3.3 | 3.6 | V    |

| DLL Supply Voltage  | VDD_DLL          | 1.7 | 1.8 | 1.9 | V    |

| Core Supply Voltage | VDD_CORI         | 1.7 | 1.8 | 1.9 | V    |

| Temperature Range   | T <sub>OPR</sub> | -20 |     | +70 | °C   |

| Operating           |                  |     |     |     |      |

**Table 3 KSC-1000 Recommended Operating Conditions**

# **Decoupling, Grounding and Power-Up Requirements**

Each of the power supply pins (VDD\_C, VDD\_IO, VDD\_DLL) shall have at a minimum, local 0.1uF ceramic de-coupling capacitors. It is recommended that the IO\_VDD\_3P3V connections also have 10 uF de-coupling where possible to supply current during simultaneous switching of multiple outputs. Preferred configuration for the VDD\_DLL is a 10uF tantalum, 0.1 uF ceramic, and 100 pF ceramic connected from the pin to ground, with a 10 ohm series resistance connecting the pin to the 1.8 V supply.

A single, common ground plane is recommended to reduce ground loops and local Eddy currents. The Micro Lead Frame (MLF) package of the KSC-1000 has a die attach 'paddle' on the PCB side of the package. This paddle is connected internally to the VSS nodes for VDD\_C, VDD\_IO, and VDD\_DLL. It must be externally connected to the ground plane of the PCB during manufacturing.

To prevent latch-up, it is required that the higher voltage (3.3 V) supply be powered up first. To

minimize the potential from power drain (crowbar effects) during power-up, the 1.8 V supply should follow the 3.3V supply relatively soon after. Since a linear regulator is required for the 1.8 V supply, it is recommended that the 1.8 V regulator be driven off of the 3.3 V regulated supply on board. In this manner, the above conditions should be obtained. The DLL supply (VDD\_DLL) and the core supply (VDD\_C ) should be brought up together.

Alternately, a Schottky barrier diode can be applied between the 3.3V and 1.8V voltage supply pins to prevent race condition issues. In this implementation, the anode should be attached to the lower voltage supply (1.8 V) and the cathode to the higher voltage supply (3.3 V). In this case, if power is applied to the lower voltage first, the upper supply will track the lower less the threshold of the diode, thus preventing latch-up.

#### **Electrostatic Discharge Protection**

The KSC-1000TG contains protection circuitry that is rated class B using the machine model for Electrostatic Discharge (ESD) testing. Proper

ESD precautions are recommended to avoid performance degradation or device failure.

# **Power Dissipation**

Power dissipation is a function of the operating frequency, the number of outputs that are enabled, and the drive level of the pixel rate outputs. The table below lists current require-

ments of VDD\_IO, VDD\_C and VDD\_DLL as a function of frequency and pixel rate output drive level.

| Frequency<br>(MHz) | VDD_DLL<br>(mA Max) | VDD_C<br>(mA Max) | Single CCD<br>Output<br>12mA Drive<br>(mA Max) | Single CCD<br>Output<br>24mA Drive<br>(mA Max) | Dual CCD<br>Outputs<br>12mA Drive<br>(mA Max) | Dual CCD<br>Outputs<br>24mA Drive<br>(mA Max) |

|--------------------|---------------------|-------------------|------------------------------------------------|------------------------------------------------|-----------------------------------------------|-----------------------------------------------|

| 4.13               | 0.25                | 4.9               | 24                                             | 27                                             | 31                                            | 50                                            |

| 5.94               | 0.32                | 5.8               | 25                                             | 28                                             | 33                                            | 52                                            |

| 8.53               | 0.37                | 7.1               | 26                                             | 29                                             | 36                                            | 55                                            |

| 13.82              | 0.42                | 9.1               | 29                                             | 35                                             | 42                                            | 61                                            |

| 17.55              | 0.53                | 10.8              | 32                                             | 39                                             | 45                                            | 66                                            |

| 26.04              | 0.66                | 14.2              | 37                                             | 47                                             | 55                                            | 76                                            |

| 31.88              | 0.80                | 16.9              | 41                                             | 52                                             | 61                                            | 85                                            |

| 42.22              | 0.98                | 21.4              | 49                                             | 60                                             | 74                                            | 98                                            |

| 60                 | 1.40                | 30                | 64                                             | 80                                             | 97                                            | 128                                           |

**Table 4 Power Supply Current Requirements**

#### Conditions:

Values for VDD\_IO at 3.3V, VDD\_C and VDD\_DLL at 1.8V

Outputs driving CMOS gate load.

Enabled Outputs for Single CCD Output Cases: H1\_1, H2\_1, HLG\_1, RG, ADCLK, DATACLK, SHP\_1, SHD\_1, and PIXCLK along with all line and frame rate outputs

Enabled Outputs for Single CCD Output Cases: All pixel rate outputs, along with all line and frame rate outputs.

# **Electrical Characteristics**

# **DC Characteristics**

(Conditions: VDD =  $3.0 \sim 3.6 \text{V}$ , Ta =  $-20 ^{\circ}\text{C} \sim +70 ^{\circ}\text{C}$ )

| Pin Name                                                                                               | Symbol            | Parameter                 | Min | Тур | Max | Unit |

|--------------------------------------------------------------------------------------------------------|-------------------|---------------------------|-----|-----|-----|------|

| Inputs:                                                                                                | $V_{IH}$          | High Level Input Voltage  | 2.0 |     |     | V    |

| VD, HD, SCLK, SLOAD,                                                                                   | V <sub>IL</sub>   | Low Level Input Voltage   |     |     | 0.8 | V    |

| SDATA, ARSTN                                                                                           | I <sub>IH</sub>   | High Level Input Current  |     |     | 10  | uA   |

|                                                                                                        | I <sub>IL</sub>   | Low Level Input Current   |     |     | 10  | uA   |

|                                                                                                        | C <sub>IN</sub>   | Input Capacitance         |     |     | 10  | pF   |

| All Outputs                                                                                            |                   | High Level Output Current | 2.9 | VDD |     | V    |

|                                                                                                        | V <sub>OH</sub>   | $I_{OUT} = -50uA$         |     |     |     |      |

|                                                                                                        |                   | High Level Output Current | 2.6 | VDD |     | V    |

|                                                                                                        |                   | $I_{OUT} = -8mA$          |     |     |     |      |

|                                                                                                        |                   | Low Level Output Current  |     | 0   | 0.1 | V    |

|                                                                                                        | V <sub>OL</sub>   | I <sub>OUT</sub> = 50uA   |     |     |     |      |

|                                                                                                        |                   | Low Level Output Current  |     | 0   | 0.4 | V    |

|                                                                                                        |                   | $I_{OUT} = 8mA$           |     |     |     |      |

| ADCLK, DATACLK, H1_1,<br>H1_2, H2_1, H2_2, HLG_1,<br>HLG_2, PIXCLK, RG, SHD_1,<br>SHD_2, SHP_1, SHP_2, | l <sub>Omax</sub> | Maximum Output Current    | -24 |     | 24  | mA   |

| AMP_EN, CLPDM, CLPOB,<br>FRAME_VAL, FAST_DUMP,<br>LINE_VAL, PBLK, V1_1, V1_2,<br>V2_1, V2_2, VDISCHG   | l <sub>Omax</sub> | Maximum Output Current    | -12 |     | 12  | mA   |

**Table 5 KSC-1000 DC Characteristics**

# **AC Characteristics**

(Conditions: Vdd = 3.0V - 3.6V, Ta =  $-20^{\circ}C - +70^{\circ}C$ )

| Pin Name                                                                                       | Symbol            | Parameter                                | Min | Тур  | Max  | Units | C <sub>LOAD</sub> |

|------------------------------------------------------------------------------------------------|-------------------|------------------------------------------|-----|------|------|-------|-------------------|

| ADCLK, DATACLK ,<br>H1_1, H1_2, H2_1, H2_2,                                                    | t <sub>RHF</sub>  | High Speed Clock Rise Time @ 24mA Drive  | 445 | 580  | 840  | pS    | 10pf              |

| HLG_1, HLG_2, PIXCLK,<br>RG, SHD_1, SHD_2,<br>SHP_1, SHP_2,                                    | t <sub>FHF</sub>  | High Speed Clock Fall Time @ 24mA Drive  | 445 | 580  | 890  | pS    | 10pf              |

|                                                                                                | t <sub>RHS</sub>  | High Speed Clock Rise Time<br>12mA drive | 770 | 1030 | 1500 | pS    | 10pf              |

|                                                                                                | t <sub>FHS</sub>  | High Speed Clock Fall Time<br>12mA drive | 820 | 1070 | 1630 | pS    | 10pf              |

|                                                                                                | t <sub>PDRH</sub> | Rise Time Delta Propagation Delay        | 1   | 5    | 10   | nS    |                   |

|                                                                                                | t <sub>PDFH</sub> | Fall Time Delta Propagation Delay        | 1   | 5    | 10   | nS    |                   |

| AMP_EN, CLPDM,<br>CLPOB, FAST_DUMP,<br>FRAME_VAL, LINE_VAL,<br>PBLK,<br>INTG-STRT, V1_1, V1_2, | t <sub>RV</sub>   | Low Speed Clock Rise Time                | 770 | 1030 | 1500 | pS    | 10pf              |

|                                                                                                | t <sub>FV</sub>   | Low Speed Clock Fall Time                | 820 | 1070 | 1630 | pS    | 10pf              |

|                                                                                                | t <sub>PDRV</sub> | Rise Time Delta Propagation Delay        |     | 1    | 5    | nS    |                   |

| V2_1, V2_2, VDISCGH,                                                                           | t <sub>PDFV</sub> | Fall Time Delta Propagation Delay        |     | 1    | 5    | nS    |                   |

#### **Table 6 KSC-1000 AC Characteristics**

Figure 5 Pixel Rate Signal Rise and Fall Time

Figure 6 Line and Frame Rate Signal Rise and Fall Time

Figure 7 Pixel Rate Signal Rise and Fall Time Delta Propagation Delay

Figure 8 Line and Frame Rate Signal Rise and Fall Time Delta Propagation Delay

# **Oscillator Buffer Characteristics**

| Pin Name            | Symbol          | Parameter                   | Min  | Тур      | Max | Unit | Comments                                                                                                                                                                     |

|---------------------|-----------------|-----------------------------|------|----------|-----|------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Xtal_I<br>Xtal_O    | f               | Operating<br>Frequency      | 8.26 |          | 120 | MHz  | 8.26MHz to 10MHz input, as well as 60MHz to 120MHz operation require the use of a clock oscillator. 10MHz to 60MHz input may use a crystal oscillator or a clock oscillator. |

| On Chip<br>Resistor | R1              | Resistance                  |      | 1        |     | Mohm | On chip resistor formed in N-well diffusion                                                                                                                                  |

|                     | TC1             | Temperature<br>Coefficient  |      | 2.97 e-3 |     |      | R = R0 * (1 + (TC1 * dT) + (TC2 * dT * dT)), where dT = T - 25°C                                                                                                             |

|                     | TC2             | Temperature<br>Coefficient  |      | 1.1e-5   |     |      |                                                                                                                                                                              |

|                     | C <sub>R1</sub> | Parasitic<br>Capacitance    | 858  | 908      | 957 | fF   | Parasitic Capacitance between N-well diffusion and the substrate.                                                                                                            |

|                     | R2              | Series Resistor             |      | 30       |     | ohms |                                                                                                                                                                              |

|                     | C1              | Crystal Load<br>Capacitance |      | 5.1      |     | pf   |                                                                                                                                                                              |

|                     | C2              | Crystal Load<br>Capacitance |      | 5.1      |     | pf   |                                                                                                                                                                              |

**Table 7 Oscillator Buffer Characteristics**

**Figure 9 Crystal Oscillator Circuit**

# **DLL Specifications**

| Pin Name              | Parameter                     | Symbol               | Min  | Тур | Max  | Unit | Comments                                                                                                                                                                                                                                         |

|-----------------------|-------------------------------|----------------------|------|-----|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                       | Lock Range                    | fRANGE               | 4    |     | 65   | MHz  | Dividing the xtal_in input by 2 will                                                                                                                                                                                                             |

| CLK_IN                | Lock Time                     | tLOCK                |      |     | 10   | mS   | create the clk_in input signal. This guarantees a 50% duty                                                                                                                                                                                       |

| (input)               | Duty Cycle                    | dclk_in              |      | 50  |      | %    | cycle                                                                                                                                                                                                                                            |

|                       | Input Clk Freq                | fclk_in              | 8.26 |     | 120  | MHz  |                                                                                                                                                                                                                                                  |

|                       | Output Clk Freq.              | f <sub>CLK_OUT</sub> | 4.13 |     | 60   | MHz  | t <sub>PHASE INC</sub> = 1/64 * t <sub>CLK IN</sub> where                                                                                                                                                                                        |

|                       | Output Clk Phase<br>Increment | tphase_inc           | 260  |     | 3783 | pS   | $t_{\text{CLK\_IN}}$ is the period of clk_in $t_{\text{TAP\_TOL}}$ = percentage of $t_{\text{PHASE\_INC}}$                                                                                                                                       |

| CLK(0:63)<br>(output) | Output Clk Tap<br>Tolerance   | t <sub>TAP_TOL</sub> | 0    |     | 50   | %    | clk(0) offset = (0 * t <sub>PHASE INC</sub> ) +/-                                                                                                                                                                                                |

|                       | Output Clk Duty<br>Cycle      | d <sub>CLK_OUT</sub> |      | 50  |      | %    | t <sub>TAP_TOL</sub> clk(1) offset = (1 * t <sub>PHASE_INC</sub> ) +/- t <sub>TAP_TOL</sub> clk(2) offset = (2 * t <sub>PHASE_INC</sub> ) +/- t <sub>TAP_TOL</sub> etc  clk(63) offset = (63 * t <sub>PHASE_INC</sub> ) +/- t <sub>TAP_TOL</sub> |

**Table 8 DLL Specifications**

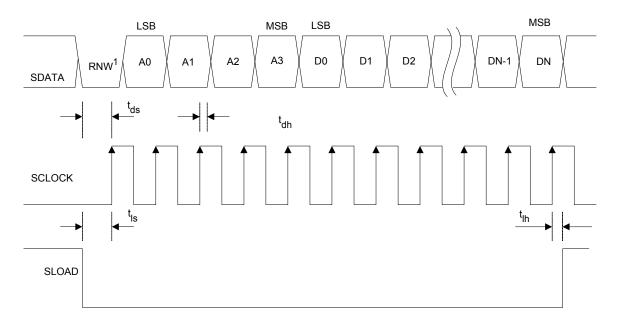

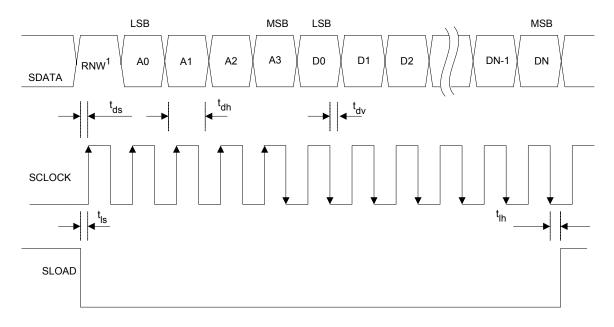

#### SERIAL INTERFACE SPECIFCATIONS

# **Timing Specifications**

The KSC-1000 utilizes a 3 wire serial interface. Both read and write operations are supported. Individual Registers can be written/read by writing the appropriate address bits and asserting SCLK only for the number of bits in that register. Multiple registers can be written/read by writing the appropriate starting address and asserting SCLK for the total number of bits in the desired registers. When the last bit of one register is reached, the next SCLK assertion writes/reads to the first bit of the

next register in the address map. After the last bit of the last register is reached, the serial interface stops writing/reading data, regardless of the state of SL. Note that all address and data transfers proceed from their respective LSBs to MSBs.

For read operation, the address bits are latched on the rising edge. After the 4 address bits are latched in, the data is presented on the subsequent SCLK falling edges.

Figure 10 Serial Write Timing

Note 1: RNW Read-Not-Write. Set low for write operation and high for read operation.

Figure 11 Serial Read Timing

Note 1: RNW Read-Not-Write. Set low for write operation and high for read operation.

| Parameter        | Description                                | Min | Тур | Max | Units |

|------------------|--------------------------------------------|-----|-----|-----|-------|

| f <sub>sck</sub> | SCLK frequency                             |     |     | 20  | MHz   |

| t <sub>ls</sub>  | SLOAD to SCLK setup time                   | 10  |     |     | nS    |

| t <sub>lh</sub>  | SCLK to SLOAD hold time                    | 10  |     |     | nS    |

| t <sub>ds</sub>  | SDATA valid to SCLK rising edge setup time | 10  |     |     | nS    |

| t <sub>dh</sub>  | SCLK rising edge to SDATA valid hold time  | 10  |     |     | nS    |

| t <sub>dv</sub>  | SCLK falling edge to SDATA valid read      | 10  |     |     | nS    |

**Table 9 Serial Interface Timing Specifications**

# **Register Descriptions**

# **Register Map**

| Register Name       | Address   |           |           |           | Total | LSB                                      | MSB                                       |  |

|---------------------|-----------|-----------|-----------|-----------|-------|------------------------------------------|-------------------------------------------|--|

|                     | <b>A0</b> | <b>A1</b> | <b>A2</b> | <b>A3</b> | Bits  |                                          |                                           |  |

| Frame Table Pointer | 0         | 0         | 0         | 0         | 3     | Frame Table Address (0)                  | Frame Table Address (2)                   |  |

| General Setup       | 1         | 0         | 0         | 0         | 202   | Pixels Per Line (0)                      | DLL Frequency Range<br>Select (3)         |  |

| General Control     | 0         | 1         | 0         | 0         | 2     | Low Power Enable                         | Memory Table Mode                         |  |

| INTG_STRT Setup     | 1         | 1         | 0         | 0         | 30    | Electronic Shutter Setup<br>Clocks (0)   | Electronic Shutter Hold<br>Clocks (9)     |  |

| INTG_STRT Line      | 0         | 0         | 1         | 0         | 13    | Integrate Start Pulse Line<br>Number (0) | Integrate Start Pulse Line<br>Number (12) |  |

| Signal Polarity     | 1         | 0         | 1         | 0         | 25    | H1_1_IDLE _VAL                           | FAST_DUMP_IDLE_VAL                        |  |

| Offset              | 0         | 1         | 1         | 0         | 78    | H1_1_OFFSET                              | DATA_CLK_OFFSET                           |  |

| Width               | 1         | 1         | 1         | 0         | 65    | H1_1_WIDTH                               | DATA_CLK_WIDTH                            |  |

| Frame Table Access  | 0         | 0         | 0         | 1         | 34    | Frame Table Entry (0)                    | Address (3)                               |  |

| Line table Access   | 1         | 0         | 0         | 1         | 20    | Line Table Entry (0)                     | V1_1                                      |  |

| Status              | 0         | 1         | 0         | 1         | 31    | DLL Locked                               | Line Counter Value (12)                   |  |

**Table 10 Serial Interface Register Map**

# Frame Table Pointer Register

The KSC-1000 uses frame tables to define the clocking sequence of an image sensor. The Frame Table Register entry points to one of the unique frame tables. The KSC-1000 frame table implementation supports sequencing from mode to mode without writing to the frame pointer register. Writes to the frame pointer register supercede the sequence defined by the frame table and are executed immediately as long as the Memory Table Mode bit in the General Setup

Register is set. The low power mode is the only mode where the operation of KSC-1000 is predetermined and therefore does not require a unique frame table. KSC-1000 supports up to 8 frame tables. The numbering of the frame tables is arbitrary. A frame table can potentially describe a single or multiple operating modes. Conversely, a complex operating mode could require multiple frame tables concatenated together.

| Register 0  | Frame Table Pointer               | Default |

|-------------|-----------------------------------|---------|

| Data Length | Register Field                    | Decimal |

| 3 bits      | Frame Table Address (0 through 7) | 0       |

**Table 11 Frame Table Pointer Register Map**

# **General Setup Register**

The General Setup Register controls the following parameters:

- Horizontal Line Length

- Line sync start and stop pixel locations

- AFE clamping signal start and stop pixel locations

- AFE blanking signal start and stop pixel locations

- Pixel rate clock signal enables

- Pixel rate clock signal drive levels

- DLL frequency range select

Pixels Per Line defines the number of pixels in a horizontal line. Horizontal clocking ends after the number of clock cycles entered in this field has occurred. This count includes all dark, active, buffer, and over-clocked pixels. The Horizontal Pixel Counter starts at count 0 and counts up to the number entered in this field – 1. At that point the vertical clocking interval defined by the current line table starts.

Line Valid Pixel Start defines the pixel on which the line valid signal is asserted. Line Valid Quadrature Start defines where the LINE\_VALID signal is asserted relative to the PIXCLK signal. Refer to the Line Valid Quadrature Start Descriptor Table below for a description of the functionality of these bits. Line Valid Pixel End defines the pixel on which the line valid signal is de-asserted. If Line Valid Pixel Start and Line Valid Pixel End are programmed to the same value, the LINE\_VALID output will not be asserted.

The CLPOB1\_Pix\_Start, CLPOB2\_Pix\_Start, CLPDM1 Pix Start, CLPDM2 Pix Start, and PBLK Pix Start entries define the pixel on which these signals are asserted. CLPOB1 Pix End, CLPOB2 Pix End, CLPDM1 Pix End, CLPDM2 Pix End PBLK Pix End entries define the pixel on which these signals are de-asserted. The lines on which the signals are enabled are defined in the frame table. The polarity of the signals is defined in the Signal Polarity Register, except for PBLK. PBLK polarity is defined in the frame table. If the Start and End entries are the same value, the signals will not be asserted. Note that there are only a single CLOPB and CLPDM output pins. The purpose of having CLPOB1, CLOPB2, CLPDM1, and CLPDM2 register settings is to permit 2 unique pulse width signals to be used at different points in the image capture sequence. For example, CLPDM and CLPOB could be asserted for the entire line during the readout of dark lines and during the dark pixels of active image readout lines. If the PBLK signal is used, it is asserted at its programmed location on the end of a line, remains asserted during the entire vertical clocking interval, and is de-asserted at the programmed location on the new line. Therefore, the minimum PBLK pulse width is the vertical clocking interval period + 1 pixel.

There are enable bits for the following signals: RG, H1\_1, H2\_1, HLG\_1, SHP\_1, SHD\_1, ADCLK, DATACLK, PIXCLK, H1\_2, H2\_2, HLG\_2, SHP\_2, and SHD\_2. Clearing these signals drives the outputs to the state defined in the signal polarity register. Setting these signals allows them to toggle as defined in the frame The PIXCLK signal is not controlled tables. therefore within frame table. PIXCLK\_Enable bit functions as a global enable bit. Setting PIXCLK Enable bit low drives the PIXCLK output low, while setting the bit high allows the PIXCLK signal to toggle. The purpose of the rest of the enable bits is to disable those signals that are not needed for any given application.

The High Speed Clock Drive Select bit sets the output current drive capability of the following outputs: RG, H1\_1, H2\_1, HLG\_1, SHP\_1, SHD\_1, ADCLK, DATACLK, PIXCLK, H1\_2, H2\_2, HLG\_2, SHP\_2, and SHD\_2. The 12mA setting allows for power savings and slower rise and fall times for those applications that run at slower clock frequencies.

The DLL Frequency Select bits are used to select the appropriate DLL. The definition of the frequency ranges is described in the register field below.

| Register 1  | General Setup Register                                                    | Default |

|-------------|---------------------------------------------------------------------------|---------|

| Data Length | Register Field                                                            | Decimal |

| 13 bits     | Pixels Per Line                                                           | 1024    |

| 13 bits     | Line Valid Pixel Start                                                    | 0       |

| 2 bits      | Line Valid Pixel Quadrature Start                                         | 0       |

| 13 bits     | Line Valid Pixel End                                                      | 0       |

| 13 bits     | CLPOB1_Pix_Start (Dark Line Frame Rate Clamp)                             | 0       |

| 13 bits     | CLPOB1_Pix_End (Dark Line Frame Rate Clamp)                               | 0       |

| 13 bits     | CLPOB2_Pix_Start (Active Readout Line Rate Clamp)                         | 0       |

| 13 bits     | CLPOB2_Pix_End (Active Readout Line Rate Clamp)                           | 0       |

| 13 bits     | CLPDM1_Pix_Start (Dark Line Frame Rate Clamp)                             | 0       |

| 13 bits     | CLPDM1_Pix_End (Dark Line Frame Rate Clamp)                               | 0       |

| 13 bits     | CLPDM2_Pix_Start (Active Readout Line Rate Clamp)                         | 0       |

| 13 bits     | CLPDM2_Pix_End (Active Readout Line Rate Clamp)                           | 0       |

| 13 bits     | PBLK_Pix_Start                                                            | 0       |

| 13 bits     | PBLK_Pix_End                                                              | 0       |

| 1 bit       | RG_Enable (0 = RG at Idle State, 1 = RG enabled to toggle)                | 1       |

| 1 bit       | H1_1_Enable (0 = H1_1 at Idle State, 1 = H1_1 enabled to toggle)          | 1       |

| 1 bit       | H2_1_Enable (0 = H2_1 at Idle State, 1 = H2_1 enabled to toggle)          | 1       |

| 1 bit       | HLG_1_ Enable (0 = HLG_1 at Idle State, 1 = HLG_1 enabled to toggle)      | 0       |

| 1 bit       | SHP_1_Enable (0 = SHP_1 at Idle State, 1 = SHP_1 enabled to toggle)       | 1       |

| 1 bit       | SHD_1_Enable (0 = SHD_1 at Idle State, 1 = SHD_1 enabled to toggle)       | 1       |

| 1 bit       | ADCLK_Enable (0 = ADCLK at Idle State, 1 = ADCLK enabled to toggle)       | 1       |

| 1 bit       | DATACLK_Enable (0 = DATACLK at Idle State, 1 = DATACLK enabled to toggle) | 0       |

| 1 bit       | PIXCLK_Enable (0 = PIXCLK de-asserted, 1 = PIXCLK on)                     | 1       |

| 1 bit       | H1_2_Enable (0 = H1_2 at Idle State, 1 = H1_2 enabled to toggle)          | 0       |

| 1 bit       | H2_2_Enable (0 = H2_2 at Idle State, 1 = H2_2 enabled to toggle)          | 0       |

| 1 bit       | HLG_2_Enable (0 = HLG_2 at Idle State, 1 = HLG_2 enabled to toggle)       | 0       |

| 1 bit       | SHP_2_Enable (0 = SHP_2 at Idle State, 1 = SHP_2 enabled to toggle)       | 0       |

| 1 bit       | SHD_2_Enable (0 = SHD_2 at Idle State, 1 = SHD_2 enabled to toggle)       | 0       |

| 1 bit       | H1_1 24mAoutput enable (0 = 12mA, 1 = 24mA)                               | 0       |

| 1 bit       | H2_1 24mA output enable (0 = 12mA, 1 = 24mA)                              | 0       |

| 1 bit       | HLG_1 24mA output enable (0 = 12mA, 1 = 24mA)                             | 0       |

| 1 bit       | SHP_1 24mA output enable (0 = 12mA, 1 = 24mA)                             | 0       |

| 1 bit       | SHD_1 24mA output enable (0 = 12mA, 1 = 24mA)                             | 0       |

| 1 bit       | ADCLK 24mA output enable (0 = 12mA, 1 = 24mA)                             | 0       |

| 1 bit       | DATACLK 24mA output enable (0 = 12mA, 1 = 24mA)                           | 0       |

| 1 bit       | PIXCLK 24mA output enable (0 = 12mA, 1 = 24mA)                            | 0       |

| 1 bit  | H1_2 24mA output enable (0 = 12mA, 1 = 24mA)  | 0 |

|--------|-----------------------------------------------|---|

| 1 bit  | H2_2 24mA output enable (0 = 12mA, 1 = 24mA)  | 0 |

| 1 bit  | HLG_2 24mA output enable (0 = 12mA, 1 = 24mA) | 0 |

| 1 bit  | SHP_2 24mA output enable (0 = 12mA, 1 = 24mA) | 0 |

| 1 bit  | SHD_2 24mA output enable (0 = 12mA, 1 = 24mA) | 0 |

| 4 bits | DLL Frequency Range Select                    | 9 |

|        | 0000 Invalid                                  |   |

|        | 0001 Invalid                                  |   |

|        | 0010 Invalid                                  |   |

|        | 0011 Invalid                                  |   |

|        | 0100 4.13MHz to 5.94MHz                       |   |

|        | 0101 5.94MHz to 8.53MHz                       |   |

|        | 0110 8.53MHz to 13.52MHz                      |   |

|        | 0111 13.52MHz to 17.55MHz                     |   |

|        | 1000 17.55MHz to 26.04MHz                     |   |

|        | 1001 26.04MHz to 31.88MHz                     |   |

|        | 1010 31.88MHz to 42.22MHz                     |   |

|        | 1011 42.22MHz to 60.0MHz                      |   |

|        | 1100 Invalid                                  |   |

|        | 1101 Invalid                                  |   |

|        | 1110 Invalid                                  |   |

|        | 1111 Invalid                                  |   |

**Table 12 General Setup Register Map**

| Line Valid Pixel Quadrature Start Description | ı |

|-----------------------------------------------|---|

|-----------------------------------------------|---|

| 00 | Assert LINE_VALID signal coincident with PIXCLK leading edge (DLL core_clk_0)               |

|----|---------------------------------------------------------------------------------------------|

| 01 | LINE_VALID signal assertion delayed 90 degrees from PIXCLK leading edge (DLL core_clk_90)   |

| 10 | LINE_VALID signal assertion delayed 180 degrees from PIXCLK leading edge (DLL core_clk_180) |

| 11 | LINE_VALID signal assertion delayed 270 degrees from PIXCLK leading edge (DLL core_clk_270) |

**Table 13 Line Valid Quadrature Start Descriptor Table**

# **General Control Register**

The General Control Register controls the following functions:

- Power Management

- Operation state

The Low Power Enable bit is used to place the KSC-1000 in its low power mode. In this mode the DLL and other clocks except PIXCLK are shut down. Serial programming is enabled in the low power mode. The RAM tables and all registers retain their settings.

Memory table reprogramming is allowed at any time. However, to prevent unexpected operation,

it is recommended that the user halt execution of the current frame and line tables prior to reprogramming. De-asserting the Memory Table Mode bit halts execution at the completion of the current line table. Asserting this bit will initiate execution of the frame table pointed to by the Frame Table Pointer Register. The memory tables can also be programmed in the low power mode.

| Register 2  | General Control Register                                     | Default |

|-------------|--------------------------------------------------------------|---------|

| Data Length | Register Field                                               | Decimal |

| 1 bit       | Low Power Enable (0 = Full Power, 1 = Low Power)             | 1       |

| 1 bit       | Memory Table Mode (0 = Programming Mode, 1 = Execution Mode) | 0       |

**Table 14 General Control Register Map**

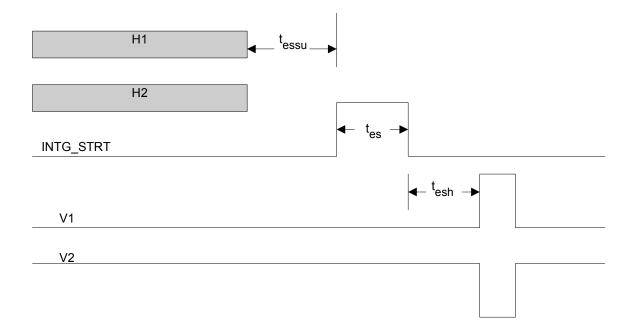

# **INTG\_STRT Setup Register**

Electronic shuttering is used with the Kodak family of interline sensors. The figure below illustrates the electronic shutter timing with respect to the image sensor horizontal and vertical clocks. tessu, the electronic shutter setup time, is the time from the end of the horizontal clocks to the start of the electronic shutter pulse.

tes is the electronic shutter pulse width. tesh, the electronic shutter hold time, is the time from the trailing edge of the electronic shutter pulse to the start of the vertical clocking interval. Note that the line time on which the integrate start pulse is generated is extended by the setup time, shutter pulse width and hold time.

Figure 12 INTG\_STRT Timing

| Register 3  | INTG_STRT Setup Register                                    | Default   |

|-------------|-------------------------------------------------------------|-----------|

| Data Length | Register Field                                              | (Decimal) |

| 10 bits     | Electronic Shutter Setup Clocks (Pixel clock period counts) | 0         |

| 10 bits     | Electronic Shutter Pulse Width (Pixel clock period counts)  | 0         |

| 10 bits     | Electronic Shutter Hold Clocks (Pixel clock period counts)  | 0         |

Table 15 INTG\_STRT Setup Register Map

# **INTG\_STRT** Line Register

The value in this register generates the INTG\_STRT clock sequence described in the Integrate Start Setup Register at the start of the programmed line number. The vertical line counter starts at count 0 and counts up. Note

that the Check and Increment Line Counter bit in the frame table must be set to allow INTG\_STRT pulse generation. Also the Vertical Line Counter must be set to zero at the appropriate time by the Clear Line Counter bit in the frame table.

| Register 4  | INTG_STRT Line Register           | Default   |

|-------------|-----------------------------------|-----------|

| Data Length | Register Field                    | (Decimal) |

| 13 bits     | Integrate Start Pulse Line Number | 0         |

Table 16 INTG\_STRT Line Register Map

# **Signal Polarity Register**

Each of the outputs associated with this table have an XOR in their logic path to control the polarity of the output signal. A '0' in the following register means that the output will be '0' when it is inactive. A '1' in the following register inverts the polarity defined in the line table for the V1\_1, V1\_2, V2\_1, V2\_2,V\_DISCGH, and FAST\_DUMP signals, and

means that the output will be '1' when it is inactive for the other signals. For example, an H clock's idle value is the level it is held at during vertical clocking. For PBLK, CLPOB, and CLDPM, the idle value is the level it is held at during horizontal clocking in readout mode.

| Register 5  | Signal Polarity Register                                                                                 |           |  |

|-------------|----------------------------------------------------------------------------------------------------------|-----------|--|

| Data Length | Register Field                                                                                           | (Decimal) |  |

| 1 bit       | H1_1_IDLE_VAL ( level held during vertical clocking)                                                     |           |  |

| 1 bit       | H1_2_IDLE_VAL ( level held during vertical clocking)                                                     | 0         |  |

| 1 bit       | H2_1_IDLE_VAL ( level held during vertical clocking)                                                     | 1         |  |

| 1 bit       | H2_2_IDLE_VAL ( level held during vertical clocking)                                                     | 1         |  |

| 1 bit       | HLG_1_IDLE_VAL ( level held during vertical clocking)                                                    | 0         |  |

| 1 bit       | HLG_2_IDLE_VAL ( level held during vertical clocking)                                                    | 0         |  |

| 1 bit       | RG_IDLE_VAL (level held during de-asserted state)                                                        | 0         |  |

| 1 bit       | SHP_1_IDLE_VAL (level held during de-asserted state)                                                     | 1         |  |

| 1 bit       | SHP_2_IDLE_VAL (level held during de-asserted state)                                                     | 1         |  |

| 1 bit       | SHD_1_IDLE_VAL (level held during de-asserted state)                                                     | 1         |  |

| 1 bit       | SHD_2_IDLE_VAL (level held during de-asserted state)                                                     | 1         |  |

| 1 bit       | ADCLK_IDLE_VAL (level held when signal is disabled)                                                      | 0         |  |

| 1 bit       | DATA_CLK_IDLE_VAL (level held when signal is disabled)                                                   | 0         |  |

| 1 bit       | CLPOB_IDLE_VAL (level held during de-asserted state)                                                     |           |  |

| 1 bit       | CLPDM_IDLE_VAL (level held during de-asserted state)                                                     |           |  |

| 1 bit       | AMP_ENABLE_IDLE_VAL (level held during de-asserted state)                                                |           |  |

| 1 bit       | FRAME_VALID_IDLE_VAL (level held during de-asserted state)                                               |           |  |

| 1 bit       | LINE_VALID_IDLE_VAL (level held during de-asserted state)                                                | 0         |  |

| 1 bit       | INTEGRATE_START_IDLE_VAL (level held during de-asserted state)                                           | 0         |  |

| 1 bit       | V1_1_IDLE_VAL (used in conjunction with V1_2 to define non-clocking state of KSC-2000 clock driver ASIC) | 1         |  |

| 1 bit       | V1_2_IDLE_VAL (used in conjunction with V1_1 to define non-clocking state of KSC-2000 clock driver ASIC) | 0         |  |

| 1 bit       | V2_1_IDLE_VAL (used in conjunction with V2_2 to define non-clocking state of KSC-2000 clock driver ASIC) | 1         |  |

| 1 bit       | V2_2_IDLE_VAL (used in conjunction with V2_1 to define non-clocking state of KSC-2000 clock driver ASIC) | 0         |  |

| 1 bit       | V_DISCHG_IDLE_VAL (level held during de-asserted state)                                                  | 0         |  |

| 1 bit       | FAST_DUMP_IDLE_VAL (level held during de-asserted state)                                                 | 0         |  |

**Table 17 Signal Polarity Register Map**

# **Offset Register**

This register controls the offset of the leading edge of the signals listed below relative to the DLL clk(0) signal for given output.

The offset is defined in units of  $1/64^{th}$  the pixel period. Each entry is 6 bits in length.

| Register 6  | Offset Register |           |  |

|-------------|-----------------|-----------|--|

| Data Length | Register Field  | (Decimal) |  |

| 6 bits      | H1_1_OFFSET     | 0         |  |

| 6 bits      | H1_2_OFFSET     | 0         |  |

| 6 bits      | H2_1_OFFSET     | 0         |  |

| 6 bits      | H2_2_OFFSET     | 0         |  |

| 6 bits      | HLG_1_OFFSET    | 0         |  |

| 6 bits      | HLG_2_OFFSET    | 0         |  |

| 6 bits      | RG_OFFSET       | 0         |  |

| 6 bits      | SHP_1_OFFSET    | 0         |  |

| 6 bits      | SHP_2_OFFSET    | 0         |  |

| 6 bits      | SHD_1_OFFSET    | 32        |  |

| 6 bits      | SHD_2_OFFSET    | 32        |  |

| 6 bits      | ADCLK_OFFSET    | 0         |  |

| 6 bits      | DATA_CLK_OFFSET | 0         |  |

|             |                 |           |  |

**Table 18 Offset Register Map**

# Width Register

This register controls the width of the signals listed below. The width is defined in units of 1/64<sup>th</sup> the pixel period. Each entry is 5 bits in length, providing a maximum width of ½ the pixel period. The Offset Register Setting positions the leading edge of these signals. The trailing edge of these signals is positioned by setting of this

register relative to the setting of the Offset Register. The H1, H2, HLG, ADCLK, and DATACLK outputs are adjustable from 1/4 duty cycle to 47/64 duty cycle. The SHP, SHD, and RG outputs are adjustable from 1/64 duty cycle to ½ duty cycle.

| Width Register                                                                                          | Default                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|---------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register Field                                                                                          | (Decimal)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| H1_1 WIDTH (0 = $\frac{1}{4}$ duty cycle, 16 = $\frac{1}{2}$ duty cycle, 31 = 47/64 duty cycle)         | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| H1_2 WIDTH (0 = $\frac{1}{4}$ duty cycle, 16 = $\frac{1}{2}$ duty cycle, 31 = 47/64 duty cycle)         | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| H2_1 WIDTH (0 = $\frac{1}{4}$ duty cycle, 16 = $\frac{1}{2}$ duty cycle, 31 = 47/64 duty cycle)         | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| H2_2 WIDTH (0 = $\frac{1}{4}$ duty cycle, 16 = $\frac{1}{2}$ duty cycle, 31 = 47/64 duty cycle)         | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HLG_1 WIDTH (0 = $\frac{1}{4}$ duty cycle, 16 = $\frac{1}{2}$ duty cycle, 31 = 47/64 duty cycle)        | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| HLG_2 WIDTH (0 = $\frac{1}{4}$ duty cycle, 16 = $\frac{1}{2}$ duty cycle, 31 = 47/64 duty cycle)        | 16                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| RG_WIDTH (0 = $\frac{1}{2}$ duty cycle, 1 = $\frac{1}{64}$ duty cycle, 31 = $\frac{31}{64}$ duty cycle) | 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |