# Features

- Overvoltage Monitoring

- Undervoltage Monitoring

- Cell Temperature Monitoring

- Self-diagnosis including

- Comparator Functions

- Communication Lines

- Short and Open Measuring Lines

- Hot Plug-in Capable

- Less than 10 µA Stand-by Current

- Low Cell Imbalance Current (< 10 μA)</li>

- Circuit Customization, e.g. for Over/Undervoltage Thresholds Possible for Adequate Volumes

- Cost-efficient Solution Due to Cost Optimized 30V CMOS Technology

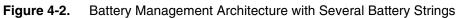

- Daisy-chainable

- Each IC Monitors 6 Battery Cells

- 16 ICs (96 Cells) per String

- No Limit on Number of Strings

- Reliable Communication between Stacked ICs Due to Level Shifters with Current Sources

- Package SSO28

# Applications

- Backup Battery-Cell Monitoring System for Li-ion Batteries

- Emergency Indicator in Li-ion Batteries

- Monitoring System in Li-ion Batteries

# **Benefits**

- Highest Safety Level for Li-ion Battery Systems

- Circuit Customization, e.g. Over and Undervoltage Thresholds, Possible for Large Production Volumes

# 1. General Description

The ATA6871 is a battery cell monitoring circuit designed to act as an emergency, safety, or backup circuit in Li-ion battery systems for electrical and hybrid electrical vehicles (EV/HEV). It monitors overvoltage, undervoltage, and the cell temperature in Li-ion batteries without the need of a microcontroller. The circuit has an advanced self-test functionality, which checks the proper functionality of the monitoring comparators as well as the communication lines. It can be used as a monitoring circuit as well as an emergency indicator or as a backup system in Li-ion battery management systems. The ATA6871 can monitor four, five, or six battery cells. Up to 16 IC's can be cascaded. If one or more battery cells exceed the over or undervoltage thresholds for longer than 2 seconds, or if the temperature input exceeds the temperature limit for more than 2 seconds, a digital output signal is set to high.

www.DataSheet4U.com

Li-ion Battery Management Monitoring Emergency and Backup Circuit

ATA6871

# Preliminary

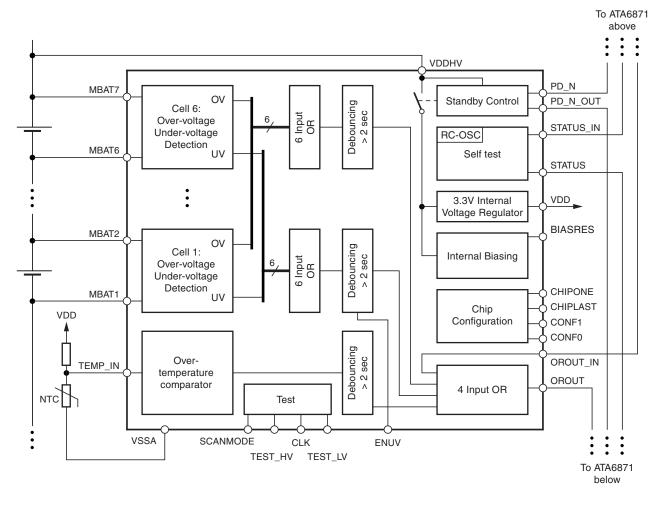

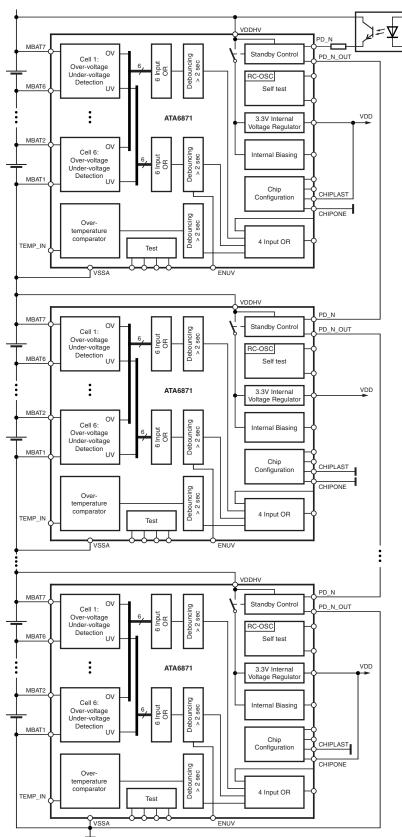

## 2. Block Diagram

Figure 2-1. Top-level Block Diagram

www.DataSheet4U.com

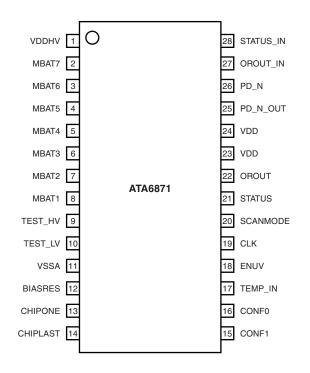

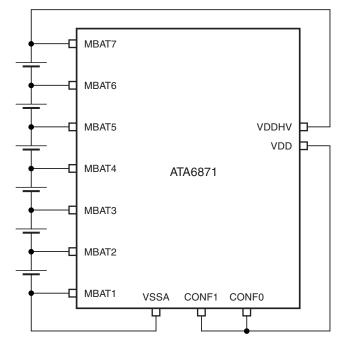

# 3. Pin Configuration

Figure 3-1. Pinning SSO28

### Table 3-1.Pin Description

| Pin | Symbol   | Function                                                               | Remark                 |

|-----|----------|------------------------------------------------------------------------|------------------------|

| 1   | VDDHV    | Supply voltage                                                         |                        |

| 2   | MBAT7    | Battery monitoring line                                                |                        |

| 3   | MBAT6    | Battery monitoring line                                                |                        |

| 4   | MBAT5    | Battery monitoring line                                                |                        |

| 5   | MBAT4    | Battery monitoring line                                                |                        |

| 6   | MBAT3    | Battery monitoring line                                                |                        |

| 7   | MBAT2    | Battery monitoring line                                                |                        |

| 8   | MBAT1    | Battery monitoring line                                                |                        |

| 9   | TEST_HV  | Test-mode pin                                                          | Keep pin open (output) |

| 10  | TEST_LV  | Test-mode pin                                                          | Keep pin open (output) |

| 11  | VSSA     | Negative supply voltage                                                |                        |

| 12  | BIASRES  | Internal supply current adjustment                                     |                        |

| 13  | CHIPONE  | Indicates circuit position in battery string (first, middle, last)     |                        |

| 14  | CHIPLAST | Indicates circuit position in battery string (first, middle, last)     |                        |

| 15  | CONF1    | Programs how many cells will be monitored (4, 5, or 6 cells operating) |                        |

| 16  | CONF0    | Programs how many cells will be monitored (4, 5, or 6 cells operating) |                        |

| 17  | TEMP_IN  | Input for battery-cell temperature monitoring                          |                        |

| 18  | ENUV     | Enable/Disable under-voltage detection                                 |                        |

#### Table 3-1.Pin Description

| Pin | Symbol    | Function                                                 | Remark                         |

|-----|-----------|----------------------------------------------------------|--------------------------------|

| 19  | CLK       | Test-mode pin                                            | Connected to VSSA              |

| 20  | SCANMODE  | Test-mode pin                                            | Connected to VSSA              |

| 21  | STATUS    | Status output                                            |                                |

| 22  | OROUT     | Output signal battery-cells in limits/out of limits      |                                |

| 23  | VDD       | Voltage regulator output                                 |                                |

| 24  | VDD       | Voltage regulator output                                 | Internally connected to pin 23 |

| 25  | PD_N_OUT  | Power down output                                        |                                |

| 26  | PD_N      | Power down input                                         |                                |

| 27  | OROUT_IN  | Input for the OROUT signal of the upper ATA6871 circuit  |                                |

| 28  | STATUS_IN | Input for the STATUS signal of the upper ATA6871 circuit |                                |

www.DataSheet4U.com

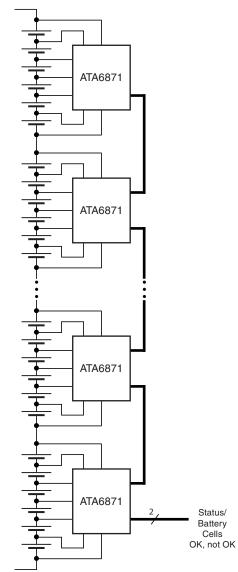

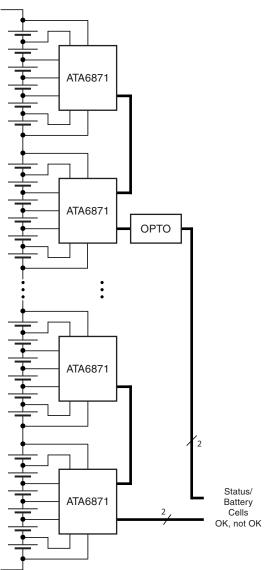

# 4. System Overview

The ATA6871 can be stacked in one string up to 16 times.

Figure 4-1. Battery Management Architecture with one Battery String

www.DataSheet4U.com

www.DataSheet4U.com

# 5. Absolute Maximum Ratings

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Unless otherwise specified all voltages refer to pin VSSA. Logic Levels: 0 = VSSA, 1 = VDD.

| Parameters                                                  | Pin                                                                                       | Symbol                                                                                                                                                                                                                               | Min.        | Max.        | Unit |

|-------------------------------------------------------------|-------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------|-------------|------|

| Ambient temperature                                         |                                                                                           | Т <sub>А</sub>                                                                                                                                                                                                                       | -40         | +85         | °C   |

| Junction temperature                                        |                                                                                           | Тј                                                                                                                                                                                                                                   | -40         | +125        | °C   |

| Storage temperature                                         |                                                                                           | Τ <sub>S</sub>                                                                                                                                                                                                                       | -40         | +150        | °C   |

| Battery cell voltage                                        |                                                                                           | V <sub>(MBATi+1)</sub> - V <sub>MBATi</sub>                                                                                                                                                                                          | -0.3        | +5.5        | V    |

| V <sub>VDDHV</sub> - V <sub>VMBAT7</sub> max                |                                                                                           | V <sub>VDDHV</sub> - V <sub>VMBAT7</sub>                                                                                                                                                                                             | -5.5        | +0.3        | V    |

| V <sub>MBAT1</sub>                                          | MBAT1                                                                                     | V <sub>MBAT1</sub>                                                                                                                                                                                                                   | -0.3        | +0.3        | V    |

| Supply voltage                                              | VDDHV                                                                                     | V <sub>VDDHV</sub>                                                                                                                                                                                                                   | -0.3        | +30         | V    |

| Supply voltage (regulator is off)                           | VDD                                                                                       | V <sub>VDD</sub>                                                                                                                                                                                                                     | -0.3        | +5.5        | V    |

| Input voltage for logic I/O pins                            | CHIPONE, CHIPLAST,<br>CONF0, CONF1,<br>SCANMODE, CLK,<br>TEST_HV, TEST_LV,<br>ENUV, OROUT | V <sub>CHIPONE</sub> , V <sub>CHIPLAST</sub> ,<br>V <sub>CONF0</sub> , V <sub>CONF1</sub> ,<br>V <sub>SCANMODE</sub> , V <sub>CLK</sub> ,<br>V <sub>TEST_HV</sub> , V <sub>TEST_LV</sub> ,<br>V <sub>ENUV</sub> , V <sub>OROUT</sub> | -0.3        | VDD + 0.3   | V    |

| Input voltage for analog low voltage input pins             | BIASRES, TEMP_IN                                                                          | $V_{BIASRES}, V_{TEMP_IN}$                                                                                                                                                                                                           | -0.3        | VDD + 0.3   | V    |

| Input voltage for digital high voltage input pins           | OROUT_IN, STATUS_IN                                                                       | V <sub>OROUT_IN</sub> , V <sub>STATUS_IN</sub>                                                                                                                                                                                       | VDDHV – 0.3 | VDDHV + 0.3 | V    |

| Logic output pin STATUS                                     | STATUS                                                                                    | V <sub>STATUS</sub>                                                                                                                                                                                                                  | -0.3        | +5.5        | V    |

| Input                                                       | PD_N                                                                                      | V <sub>PD_N</sub>                                                                                                                                                                                                                    | VDDHV – 5.5 | VDDHV + 0.3 | V    |

| Output                                                      | PD_N_OUT                                                                                  | V <sub>PD_N_OUT</sub>                                                                                                                                                                                                                | -5.5        | +0.3        | V    |

| HBM ESD<br>ANSI/ESD-STM5.1<br>JESD22-A114<br>AEC-Q100 (002) |                                                                                           | ESD                                                                                                                                                                                                                                  | ±2          |             | kV   |

| CDM ESD STM 5.3.1                                           |                                                                                           |                                                                                                                                                                                                                                      | 500         |             | V    |

| CDM ESD STM 5.3.1                                           | VDDHV, CHIPLAST,<br>CONF1, STATUS_IN                                                      | ESD                                                                                                                                                                                                                                  | 750         |             | V    |

| Latch Up according to AECQ100-004                           |                                                                                           | LATCH-UP                                                                                                                                                                                                                             | ±100        |             | mA   |

# 6. Thermal Resistance

| Parameters                                  | Symbol                | Value | Unit |

|---------------------------------------------|-----------------------|-------|------|

| Maximum thermal resistance junction-ambient | R <sub>thja</sub> max | 49    | K/W  |

## 7. Circuit Description and Electrical Characteristics

Unless otherwise specified, all parameters in this section are valid for a supply voltage range of 6.9V <  $V_{VDDHV}$  < 30V and a battery cell voltage of  $V_{(MBATi+1)} - V_{MBATi} = 0V$  to 5V, -40°C < TA < 85°C, all values refer to pin VSSA, unless otherwise specified.

## 7.1 Operating Modes

The ATA6871 has two operation modes:

1) Power-down Mode

2) ON Mode/Selfdiagnosis

### 7.1.1 Power-down Mode

In Power-down Mode all blocks of the IC are switched off.

The circuit can be switched from Power-down to ON Mode or back via the PD\_N input. If the pin is connected to VDDHV, for example, via an external optocoupler the circuit is in ON Mode. If several ATA6871 are stacked, the power-down signal must be only provided for the IC on the top level of the stack. The next lower IC is getting this information from the PD\_N\_OUT output of it's upper IC. The PD\_N\_OUT pin must be connected either to the PD\_N pin of the next lower ATA6871 or to VSSA.

www.DataSheet4U.com

# <u>AIMEL</u>

### Table 7-1. Electrical Characteristics

| No. | Parameters                                                                                          | Test Conditions                 | Pin  | Symbol                                    | Min. | Тур. | Max. | Unit | Type* |

|-----|-----------------------------------------------------------------------------------------------------|---------------------------------|------|-------------------------------------------|------|------|------|------|-------|

| 1.1 | Maximum allowed input<br>current in Power-down<br>Mode (e.g., leakage current<br>of an optocoupler) |                                 | PD_N | I <sub>PD_N</sub>                         |      |      | 50   | μΑ   | A     |

| 1.2 | Input current in ON Mode                                                                            |                                 | PD_N | I <sub>PD_N</sub>                         | 2.5  |      | 5    | mA   | А     |

| 1.3 | Current consumption in<br>Power-down Mode<br>IVDDHV + IMBATi_max <sup>(1)</sup>                     | VMBAT(i+1) –<br>VMBAT(i) = 3.7V |      |                                           |      |      | 10   | μΑ   | A     |

| 1.4 | Imbalance from battery cell<br>to battery cell in<br>Power-down Mode                                | VMBAT(i+1) –<br>VMBAT(i) = 3.7V |      |                                           |      |      | 10   | μΑ   | A     |

| 1.5 | Maximum input voltage<br>(Power-down Mode)                                                          | $I_{PD_N} = 0$ to 50 µA         | PD_N | V <sub>VDDHV</sub> -<br>V <sub>PD_N</sub> |      |      | 5    | v    | A     |

| 1.6 | Propagation delay time<br>from Power-down Mode to<br>ON Mode                                        | C <sub>VDD</sub> = 10 nF        | VDD  | t <sub>VDDON</sub>                        |      |      | 1    | ms   | A     |

| 1.7 | Propagation delay time<br>from ON Mode to<br>Power-down Mode                                        | C <sub>VDD</sub> = 10 nF        | VDD  |                                           |      |      | 11   | ms   | А     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

Note: 1. Largest input current of the inputs MBAT1 to MBAT7

### 7.1.2 ON Mode/Selfdiagnosis

When the PD\_N-signal goes from low to high, the self diagnosis of the ATA6871 starts. During this self diagnosis the following tests are performed:

- Test if over/undervoltage or overtemperature comparators are able to switch or if they stuck to 0 or 1

- Test if pins OROUT\_IN, OROUT in stacked ICs are able to switch or if they stuck to 0 or 1 and if the connection to next ATA6871 is available or not

- Test if pins STATUS\_IN, STATUS are able to switch or if they stuck to 0 or 1 and if the connection to next ATA6871/MCU is available or not

- Detect open or shorted input pins MBAT1 to MBAT7

- Detect wrong setting of CONF0, CONF1 (e.g. 4 cell configuration programmed, 6 cells used)

If self diagnosis fails, the STATUS of the lowest ATA6871 is constant low. If the self diagnosis succeeds, the STATUS of the lowest ATA6871 is toggling.

www.DataSheet4U.com

The circuit will suppress failures detected during the self test and provide only results from good tested comparators connections to pin OROUT. This enables the system to monitor the rest of the battery cells if one connection/comparator fails. If, for example, the connection of the OROUT signal between two ATA6871s is open, the OROUT\_IN signal of the lower ATA6871 will be ignored, but all the cells of this ATA6871 and ICs below will be observed in the normal way. If the battery cell voltage exceeds 4.9V or is below 1.5V during the self-diagnosis, the affected comparator will be detected as defect, and the output of the affected comparator will be also suppressed until the next self diagnosis.

If, after the self test has passed, one of the comparator in the stack detects under or overtemperature at a battery cell, the output OROUT switches from low to high. The battery cell undervoltage detection can be disabled with the digital input ENUV.

| No. | Parameters            | Test Conditions                  | Pin       | Symbol                | Min.            | Тур.            | Max.                    | Unit                | Type* |                     |    |    |

|-----|-----------------------|----------------------------------|-----------|-----------------------|-----------------|-----------------|-------------------------|---------------------|-------|---------------------|----|----|

| 2.1 | Supply voltage        |                                  | VDDHV     | V <sub>VDDHV</sub>    | 6.9             |                 | 30                      | V                   | Α     |                     |    |    |

| 2.2 | Current consumption   | No external load                 | VDDHV     | I <sub>VDDHV</sub>    |                 |                 | 6                       | mA                  | Α     |                     |    |    |

| 2.3 | Input current         |                                  | MBAT(i)   | I <sub>MBAT(i)</sub>  |                 |                 | 5                       | μA                  | Α     |                     |    |    |

| 2.4 |                       | Self diagnosis ongoing or failed | ed STATUS | M                     |                 | Constant<br>low |                         |                     | A     |                     |    |    |

| 2.4 | Digital output signal | Self diagnosis passed successful |           | 51A105                | 51AI U5         | 51AI U5         | STATUS V <sub>ST/</sub> | V <sub>STATUS</sub> | 15    | Toggle<br>frequency | 50 | Hz |

| 2.5 | Self diagnosis time   | i = number of stacked<br>ICs     |           | t <sub>selfdiag</sub> | 2 +<br>0.85 × i |                 | 8 +<br>2.2 × i          | ms                  | В     |                     |    |    |

Table 7-2.

Electrical Characteristics

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

## 7.2 Battery Cell Over and Undervoltage Detection

If, after the self diagnosis of the chip has passed, one of the monitored battery cell voltages  $V_{(MBATi+1)} - V_{MBATi}$  is above the overvoltage threshold or below the undervoltage threshold for  $t > t_{Debounce}$ , the OROUT output goes high. The battery cell undervoltage detection can be disabled with the digital input ENUV.

Table 7-3. Truth Table:

| PIN  | Symbol  | Value | Function                        |

|------|---------|-------|---------------------------------|

| ENUV | 0 Under |       | Undervoltage detection disabled |

|      | V ENUV  | 1     | Undervoltage detection enabled  |

### **Table 7-4.**Electrical Characteristics

| No. | Parameters                           | Test Conditions | Pin     | Symbol                                               | Min. | Тур. | Max. | Unit | Type* |

|-----|--------------------------------------|-----------------|---------|------------------------------------------------------|------|------|------|------|-------|

| 3.1 | Overvoltage detection on threshold   |                 | MBAT(i) | V <sub>(MBAT(i+1))</sub><br>– V <sub>MBAT(i)</sub>   | 4.3  | 4.45 | 4.6  | V    | A     |

| 3.2 | Overvoltage detection off threshold  |                 | MBAT(i) | V <sub>(MBAT(i+1))</sub><br>– V <sub>MBAT(i)</sub>   | 4.2  | 4.35 | 4.5  | V    | А     |

| 3.3 | Overvoltage detection<br>hysteresis  |                 | MBAT(i) | ${}^{\Delta V}_{(MBAT(i+1))} - V_{MBAT(i)}$          | 70   |      |      | mV   | A     |

| 3.4 | Undervoltage detection on threshold  |                 | MBAT(i) | V <sub>(MBAT(i+1))</sub><br>– V <sub>MBAT(i)</sub>   | 1.7  | 1.8  | 1.9  | V    | A     |

| 3.5 | Undervoltage detection off threshold |                 | MBAT(i) | V <sub>(MBAT(i+1))</sub><br>– V <sub>MBAT(i)</sub>   | 1.8  | 1.9  | 2.0  | V    | A     |

| 3.6 | Undervoltage detection hysteresis    |                 | MBAT(i) | <sup>ΔV</sup> (MBAT(i+1))<br>– V <sub>MBAT(i</sub> ) | 70   |      |      | mV   | А     |

| 3.7 | Debouncing time                      |                 |         | t <sub>Debounce</sub>                                | 1    |      | 3    | S    | А     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

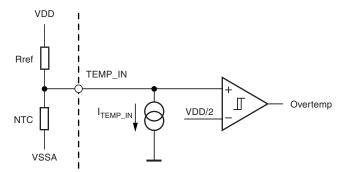

## 7.3 Battery Cell Overtemperature Detection

If the voltage at the input TEMP\_IN is less than the half of VDD threshold for  $t > t_{Debounce}$ , the OROUT output goes high.

To disable this function, connect TEMP\_IN to VDD.

If the input is open (high impedance), an internal current will force the comparator to the overtemperature state and OROUT will switch to high.

### Figure 7-2. Overtemperature Detection

www.DataSheet4U.com

| No. | Parameters                              | Test Conditions             | Pin     | Symbol                                                         | Min.              | Тур.             | Max.              | Unit | Type* |

|-----|-----------------------------------------|-----------------------------|---------|----------------------------------------------------------------|-------------------|------------------|-------------------|------|-------|

| 4.1 | Overtemperature detection on threshold  |                             | TEMP_IN | V <sub>TEMP_IN</sub>                                           | VDD/2 –<br>100 mV | VDD/2            | VDD/2 +<br>100 mV | V    | A     |

| 4.2 | Overtemperature detection off threshold |                             | TEMP_IN | $V_{\text{TEMP}_{\text{IN}}}$                                  | VDD/2 –<br>50 mV  | VDD/2 +<br>50 mV | VDD/2 +<br>150 mV | V    | A     |

| 4.3 | Overtemperature detection hysteresis    |                             | TEMP_IN | $\Delta V_{\text{TEMP}_{\text{IN}}}$                           | 30                |                  |                   | mV   | A     |

| 4.4 | Resistor Divider                        |                             |         | R <sub>Divider</sub> =<br>R <sub>NTC</sub> + R <sub>Rref</sub> | 3                 |                  | 1000              | kΩ   | D     |

| 4.5 | Input Current                           | V <sub>TEMP_IN</sub> =1.65V | TEMP_IN | I <sub>TEMP_IN</sub>                                           | 0.4               |                  | 0.6               | μA   | А     |

| 4.6 | Debouncing Time                         |                             |         | t <sub>Debounce</sub>                                          | 1                 |                  | 3                 | S    | Α     |

#### Table 7-5. Electrical Characteristics

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

## 7.4 ATA6871 Configuration

### 7.4.1 Device Position

The ATA6871 can be cascaded up to 16 times in one string. The input pins CHIPONE and CHIPLAST define the first and the last IC in a string.

| CHIPONE | CHIPLAST | Configuration                                            |

|---------|----------|----------------------------------------------------------|

| 0       | 0        | ICs between the first and the last IC (up to 14 ICs)     |

| 0       | 1        | Last cascaded chip, connected to power down optocoupler  |

| 1       | 0        | First chip in a string (master)                          |

| 1       | 1        | First and last chip: (if only one IC is used per string) |

### 7.4.2 Number of Cells Configuration

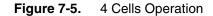

The ATA6871 can work with either four, five, or six cells. This can be programmed with the input pins CONF0 and CONF1. When used with 5 cells, the inputs MBAT5 and 6 must be connected together, when used with 4 cells the inputs MBAT4, MBAT5 and MBAT6 must be connected together (see also Figure 7-3 to Figure 7-5).

| Table 7-7. | Cells Configuration |

|------------|---------------------|

|------------|---------------------|

| CONF1 | CONF0 | Configuration                          | Notes                                                                      |

|-------|-------|----------------------------------------|----------------------------------------------------------------------------|

| 0     | 0     | 4 cells configuration                  | Over/undervoltage comparators<br>between MBAT4,5 and MBAT6 are<br>disabled |

| 0     | 1     | 5 cells configuration                  | Over/undervoltage comparator<br>between MBAT5 and MBAT6 is<br>disabled     |

| 1     | 0     | Do not use, reserved for test purposes |                                                                            |

| 1     | 1     | 6 cells configuration                  |                                                                            |

www.DataSheet4U.com

### Figure 7-3. 6 Cells Operation

Figure 7-4. 5 Cells Operation

www.DataSheet4U.com

# 7.5 Supplies

## 7.5.1 Voltage Regulator

The circuit includes a linear 3.3V voltage regulator, which supplies internal blocks as well as external components, e.g., the resistor divider for the over-temperature measurement. The regulator is supplied out of VDDHV. A load capacitor of 10 nF has to be used for stabilization purposes.

### Table 7-8. Electrical Characteristics

| No. | Parameters                                     | Test Conditions | Pin | Symbol           | Min. | Тур. | Max. | Unit | Type* |

|-----|------------------------------------------------|-----------------|-----|------------------|------|------|------|------|-------|

| 5.1 | Output voltage                                 |                 | VDD | V <sub>VDD</sub> | 3.1  | 3.3  | 3.5  | V    | А     |

|     | Maximum output current for external components |                 | VDD | I <sub>VDD</sub> | -5   |      |      | mA   | А     |

| 5.3 | Load capacitor                                 |                 | VDD | Cload            | 8    | 10   | 12   | nF   | D     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

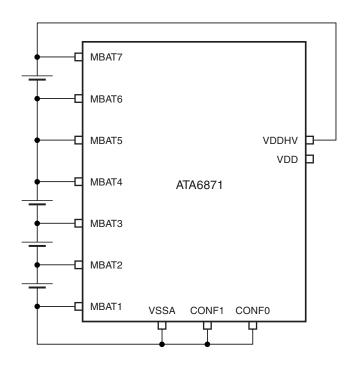

## 7.5.2 Central Biasing

This block generates a precise bias current to supply internal blocks of the IC.

External load cannot be connected to this pin.

| <b>Table 7-9.</b> Electrical Characteristics |

|----------------------------------------------|

|----------------------------------------------|

| No. | Parameters                           | Test Conditions | Pin     | Symbol                      | Min. | Тур. | Max. | Unit | Type* |

|-----|--------------------------------------|-----------------|---------|-----------------------------|------|------|------|------|-------|

| 6.1 | Biasing voltage                      |                 | BIASRES | V <sub>BIASRES</sub>        |      | 1.2  |      | V    | А     |

| 6.2 | External resistor                    |                 |         | R <sub>Refbias</sub>        |      | 121  |      | kΩ   | D     |

| 6.3 | Tolerance                            |                 |         | $\Delta R_{\text{Refbias}}$ | -1   |      | +1   | %    | D     |

| 6.4 | Maximum external parasitic capacitor |                 | BIASRES | C <sub>External</sub>       |      |      | 50   | pF   | D     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

www.DataSheet4U.com

## 7.6 Digital Inputs and Outputs

### 7.6.1 Digital Output Characteristics

If the ATA6871 is configured as first IC (master) in a string (CHIPONE = 1, CHIPLAST = 0 or 1), the output OROUT acts as a push-pull output, the output STATUS as an open drain output. If the ATA6871 is configured to be a stacked IC (CHIPONE = 0, CHIPLAST = 0 or 1), the output signals STATUS and OROUT coming from the upper IC need to be transferred to the STATUS and OROUT output of the master in the string via the STATUS\_IN and OROUT\_IN inputs. In this case the OROUT and STATUS outputs act as level shifters based on current sources.

Table 7-10.

Digital Output Characteristics (OROUT, STATUS)

| No. | Parameters                | Test Conditions                            | Pin              | Symbol                                      | Min.         | Тур. | Max.         | Unit | Type* |

|-----|---------------------------|--------------------------------------------|------------------|---------------------------------------------|--------------|------|--------------|------|-------|

| 7.1 | High-level output voltage | lout = -5 mA<br>CHIPONE = 1                | OROUT            | V <sub>OROUT</sub> ,                        | 0.8 ×<br>VDD |      |              | V    | A     |

| 7.2 | Low-level output voltage  | lout = +5 mA<br>CHIPONE = 1                | OROUT,<br>STATUS | V <sub>OROUT</sub> ,<br>V <sub>STATUS</sub> |              |      | 0.2 ×<br>VDD | V    | А     |

| 7.3 | Low-level output current  | Vout = $-0.3V$ to $+0.3V$ ,<br>CHIPONE = 0 | OROUT,<br>STATUS | I <sub>orout</sub> , I <sub>status</sub>    | -13          |      | -8           | μA   | А     |

| 7.4 | High-level output current | Vout = $-0.3V$ to $+0.3V$ ,<br>CHIPONE = 0 | OROUT,<br>STATUS | I <sub>OROUT</sub> , I <sub>STATUS</sub>    | -65          |      | -44          | μA   | А     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

### 7.6.2 Digital Input Characteristics

Table 7-11.

Digital Input Characteristics (OROUT\_IN, STATUS\_IN)

| No. | Parameters               | Test Conditions           | Pin                    | Symbol                                            | Min. | Тур. | Max. | Unit | Type* |

|-----|--------------------------|---------------------------|------------------------|---------------------------------------------------|------|------|------|------|-------|

| 8.1 | Low-level input current  | (VDDHV + 1.4V)<br>±300 mV | OROUT_IN,<br>STATUS_IN | I <sub>orout_in</sub> ,<br>I <sub>status_in</sub> | 15   |      |      | μA   | Α     |

| 8.2 | High-level input current | (VDDHV + 1.4V)<br>±300 mV | OROUT_IN,<br>STATUS_IN | I <sub>OROUT_IN</sub> ,<br>I <sub>STATUS_IN</sub> |      |      | 42   | μA   | A     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

www.DataSheet4U.com

| No. | Parameters               | Test Conditions | Pin                                               | Symbol                                                                                                                 | Min.          | Тур. | Max.         | Unit | Type* |

|-----|--------------------------|-----------------|---------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------|------|--------------|------|-------|

| 9.1 | High-level input voltage |                 | CHIPONE,<br>CHIPLAST,<br>CONF0,<br>CONF1,<br>ENUV | V <sub>CHIPONE</sub> ,<br>V <sub>CHIPLAST</sub> ,<br>V <sub>CONF0</sub> ,<br>V <sub>CONF1</sub> ,<br>V <sub>ENUV</sub> | 0.7 ×<br>VDD  |      | VDD          | v    | A     |

| 9.2 | Low-level input voltage  |                 | CHIPONE,<br>CHIPLAST,<br>CONF0,<br>CONF1,<br>ENUV | $V_{CHIPONE}, V_{CHIPLAST}, V_{CONF0}, V_{CONF1}, V_{ENUV}$                                                            |               |      | 0.3 ×<br>VDD | V    | A     |

| 9.3 | Hysteresis               |                 | CHIPONE,<br>CHIPLAST,<br>CONF0,<br>CONF1,<br>ENUV | V <sub>CHIPONE</sub> ,<br>V <sub>CHIPLAST</sub> ,<br>V <sub>CONF0</sub> ,<br>V <sub>CONF1</sub> ,<br>V <sub>ENUV</sub> | 0.05 ×<br>VDD |      |              | v    | с     |

| 9.4 | Input current            |                 | CHIPONE,<br>CHIPLAST,<br>CONF0,<br>CONF1,<br>ENUV | V <sub>CHIPONE</sub> ,<br>V <sub>CHIPLAST</sub> ,<br>V <sub>CONF0</sub> ,<br>V <sub>CONF1</sub> ,<br>V <sub>ENUV</sub> |               |      | 1            | μΑ   | A     |

#### Table 7-12. Digital Input Characteristics PINs CHIPONE, CHIPLAST, CONF0, CONF1, ENUV

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

#### 7.6.3 Test-mode Pins

The test-mode pins TEST\_HV, TEST\_LV (outputs) have to be kept open in the application. The test-mode pins CLK, SCANMODE (inputs) have to be connected to VSSA. These inputs have an internal pull-down resistor.

| Table 7-13. | Digital Input Characteristics PINs SCANMODE, CLK |

|-------------|--------------------------------------------------|

|-------------|--------------------------------------------------|

| No.  | Parameters         | Test Conditions | Pin              | Symbol                                      | Min. | Тур. | Max. | Unit | Type* |

|------|--------------------|-----------------|------------------|---------------------------------------------|------|------|------|------|-------|

| 10.1 | Pull-down resistor |                 | SCANMODE,<br>CLK | R <sub>scanmode</sub> ,<br>R <sub>clk</sub> | 50   |      | 200  | kΩ   | А     |

\*) Type means: A = 100% tested, B = 100% correlation tested, C = Characterized on samples, D = Design parameter

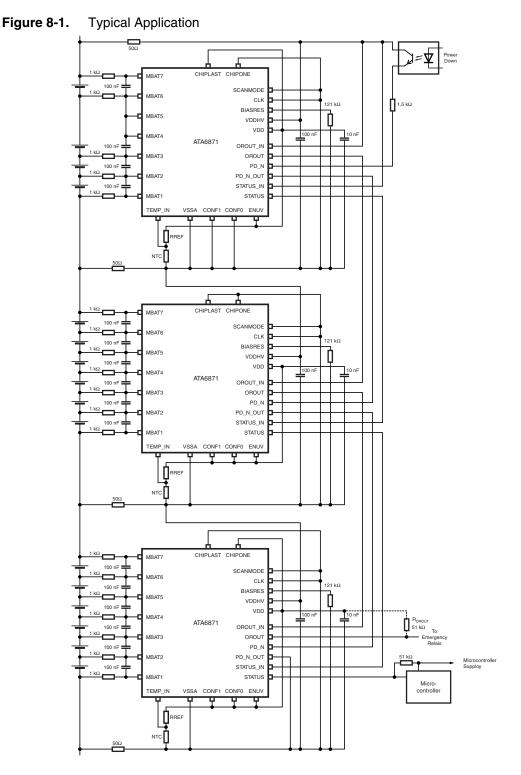

## 8. Application

Figure 8-1 shows an application with 3 stacked ATA6871s. The ATA6871 on the highest potential, is configured to monitor only four instead of six battery cells.

Note: R<sub>OROUT</sub> can be used to check if the connection between the lowest ATA6871 and the emerging Relays is available.

www.DataSheet4U.com

# 9. Ordering Information

| Extended Type Number | Package | MOQ          |

|----------------------|---------|--------------|

| ATA6871-TLPW         | SSO28   | 1,000 pieces |

| ATA6871-TLQW         | SSO28   | 4,000 pieces |

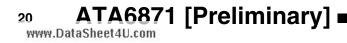

# 10. Package Information

The IC is packaged in a SSO28 package — green (lead-free/RoHS) package.

Drawing-No.: 6.543-5056.03-4 Issue: 1; 10.03.04

# **11. Revision History**

Please note that the following page numbers referred to in this section refer to the specific revision mentioned, not to this document.

| Revision No.     | History                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 9123B-AUTO-07/09 | <ul> <li>Table 5 "Absolute Maximum Ratings" on page 7 changed</li> <li>Table 7-1 "Electrical Characteristics" on page 10 changed</li> <li>Heading "ON-Mode/Selfdiagnosis" on page 10 changed</li> <li>Table 7-4 "Electrical Characteristics" on page 12 changed</li> <li>Table 7-8 "Electrical Characteristics" on page 16 changed</li> <li>Table 7-10 "Digital Output Characteristics (OROUT, STATUS)"<br/>on page 19 changed</li> <li>Table 7-11 "Digital Input Characteristics (OROUT_IN, STATUS_IN)"<br/>on page 19 changed</li> <li>Table 7-12 "Digital Input Characteristics PINS CHIPONE, CHIPLAST,<br/>CONF0, CONF1, ENUV" on page 19 changed</li> </ul> |

#### Headquarters

*Atmel Corporation* 2325 Orchard Parkway San Jose, CA 95131 USA Tel: 1(408) 441-0311 Fax: 1(408) 487-2600

### International

Atmel Asia Unit 1-5 & 16, 19/F BEA Tower, Millennium City 5 418 Kwun Tong Road Kwun Tong, Kowloon Hong Kong Tel: (852) 2245-6100 Fax: (852) 2722-1369 Atmel Europe Le Krebs 8, Rue Jean-Pierre Timbaud BP 309 78054 Saint-Quentin-en-Yvelines Cedex France Tel: (33) 1-30-60-70-00 Fax: (33) 1-30-60-71-11

#### Atmel Japan

9F, Tonetsu Shinkawa Bldg. 1-24-8 Shinkawa Chuo-ku, Tokyo 104-0033 Japan Tel: (81) 3-3523-3551 Fax: (81) 3-3523-7581

#### **Product Contact**

Web Site www.atmel.com *Technical Support* auto\_control@atmel.com Sales Contact www.atmel.com/contacts

Literature Requests www.atmel.com/literature

Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN ATMEL'S TERMS AND CONDI-TIONS OF SALE LOCATED ON ATMEL'S WEB SITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNTIVE, SPECIAL OR INCIDEN-TAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS OF PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and product descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel's products are not intended, authorized, or warranted for use as components in applications intended to support or sustain life.

© 2009 Atmel Corporation. All rights reserved. Atmel<sup>®</sup>, Atmel logo and combinations thereof, and others are registered trademarks or trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others.