# W90210F PA-RISC Embedded Controller

## Table of Contents

| TABLE OF CONTENTS                                                                                                                                                                                                                                                                                                 | 2                                |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 1. GENERAL DESCRIPTION                                                                                                                                                                                                                                                                                            | 5                                |

| 2. FEATURES                                                                                                                                                                                                                                                                                                       | 6                                |

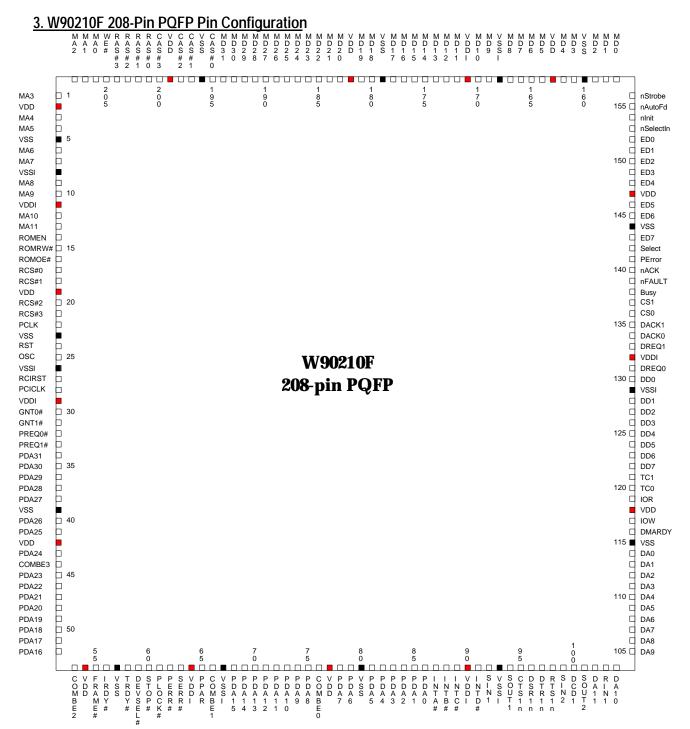

| 3. W90210F 208-PIN PQFP PIN CONFIGURATION                                                                                                                                                                                                                                                                         | 7                                |

| 4. W90210F PIN DESCRIPTION                                                                                                                                                                                                                                                                                        | 8                                |

| 5. W90210F CPU CORE                                                                                                                                                                                                                                                                                               | 12                               |

| 5.1 Architecture 5.1.1 PA-RISC Rev. 1.1 third edition 5.1.2 Level 0 implementation 5.1.3 Multimedia Extension Instruction Set                                                                                                                                                                                     | 12<br>12<br>12<br>12             |

| <ul> <li>5.2 CPU resources</li> <li>5.2.1 General registers</li> <li>5.2.2 Shadow registers</li> <li>5.2.3 Processor Status Word (PSW)</li> <li>5.2.4 Control registers</li> <li>5.2.5 W90210F External Interrupt Request register (EIRR; CR23)</li> <li>5.2.6 AIRs (Architecture Invisible Registers)</li> </ul> | 12<br>12<br>13<br>13<br>14<br>15 |

| <ul> <li>5.3 Implementation of the PA-RISC instructions</li> <li>5.3.1 Implementation of Level 0 instructions</li> <li>5.3.2 Implementation of cache-related instructions</li> <li>5.3.3 PA-RISC multimedia extension instruction set</li> <li>5.3.4 DIAG instruction</li> </ul>                                  | 15<br>16<br>16<br>17             |

| 5.4. Debug Special Function Unit                                                                                                                                                                                                                                                                                  | 19                               |

| 5.5 Addressing and access control 5.5.1 Memory and I/O space 5.5.2 RESET addresses 5.5.3 Access control  5.6 Interruptions                                                                                                                                                                                        | 20<br>20<br>20<br>20<br>20       |

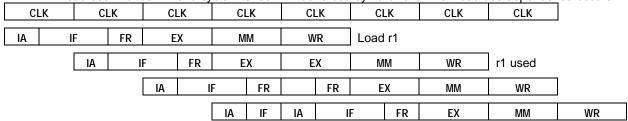

| 6. PIPELINE ARCHITECTURE                                                                                                                                                                                                                                                                                          | 22                               |

| Winbond Electronics Corp.                                                                                                                                                                                                                                                                                                             | W90210I                          |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------|

| 6.1 Branch prediction                                                                                                                                                                                                                                                                                                                 | 22                               |

| 6.2 Load use interlock                                                                                                                                                                                                                                                                                                                | 23                               |

| 7. ON-CHIP CACHE MEMORIES                                                                                                                                                                                                                                                                                                             | 24                               |

| 7.1 Instruction cache                                                                                                                                                                                                                                                                                                                 | 24                               |

| <b>7.2 Data cache</b> 7.2.1 Write-through Cache Support                                                                                                                                                                                                                                                                               | <b>24</b> 25                     |

| 7.3 Non-cacheable address space                                                                                                                                                                                                                                                                                                       | 25                               |

| 8. MEGACELLS DESCRIPTION                                                                                                                                                                                                                                                                                                              | 26                               |

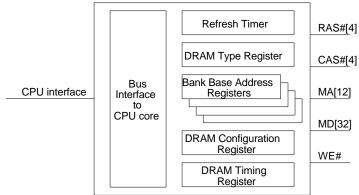

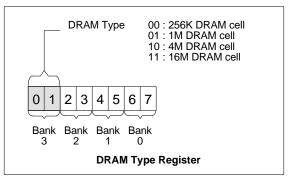

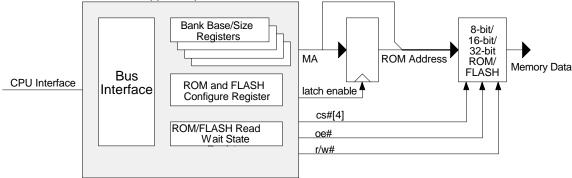

| 8.1 DRAM Controller & ROM Controller 8.1.1 DRAM controller 8.1.2 ROM controller 8.1.3 Memory controller registers                                                                                                                                                                                                                     | 26<br>26<br>27<br>27             |

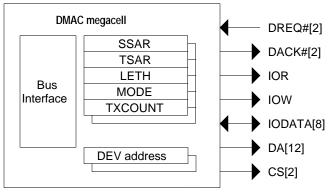

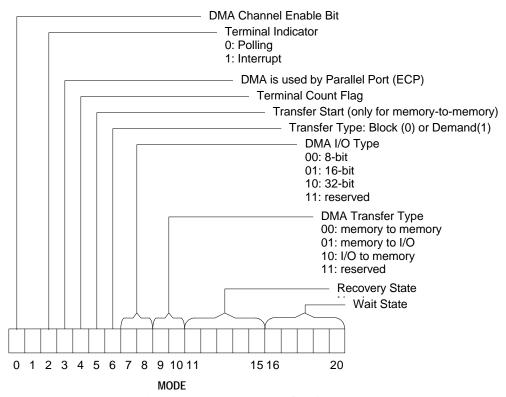

| 8.2 DMA Controller (DMAC) 8.2.1 Register Description:                                                                                                                                                                                                                                                                                 | <b>30</b><br>30                  |

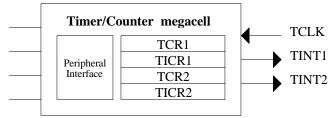

| 8.3 Timer / Counter                                                                                                                                                                                                                                                                                                                   | 32                               |

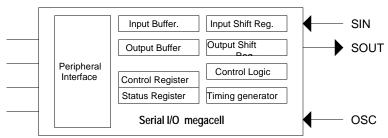

| 8.4 Serial I/O 8.4.1 UART Register Definition                                                                                                                                                                                                                                                                                         | <b>33</b> 33                     |

| 8.5 Parallel Port 8.5.1 ECP Register Description                                                                                                                                                                                                                                                                                      | <b>36</b> 36                     |

| 9. TIMING DIAGRAM                                                                                                                                                                                                                                                                                                                     | 39                               |

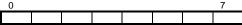

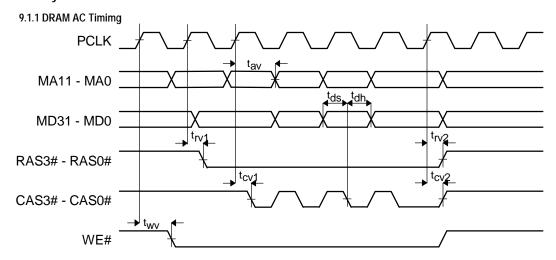

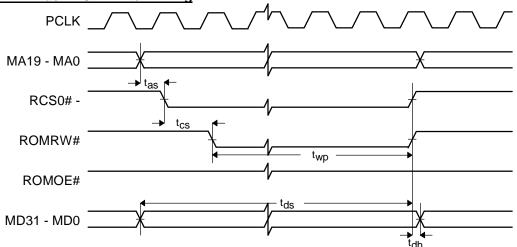

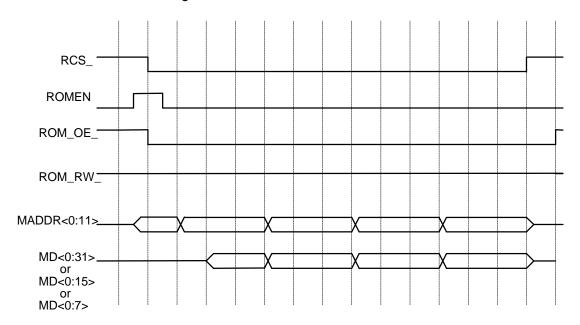

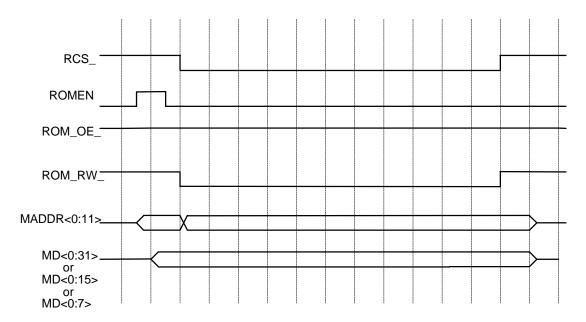

| 9.1 Memory controller 9.1.1 DRAM AC Timimg 9.1.2 ROM AC Timimg                                                                                                                                                                                                                                                                        | <b>39</b> 39 39                  |

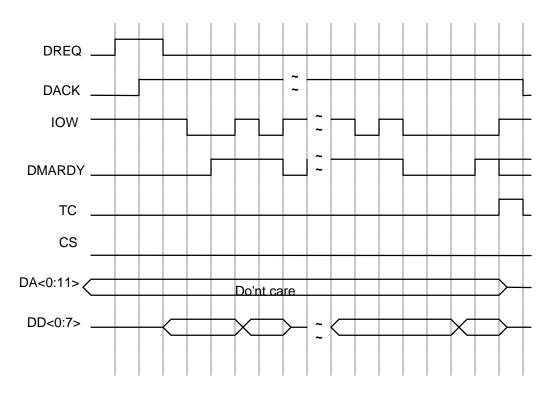

| <ul> <li>9.2 DMA Controller</li> <li>9.2.1 DMA device register read timing</li> <li>9.2.2 DMA device register write timing</li> <li>9.2.3 DMA demand mode data read cycles</li> <li>9.2.4 DMA demand mode data write cycles</li> <li>9.2.5 DMA block mode data read cycles</li> <li>9.2.6 DMA block mode data write cycles</li> </ul> | 41<br>41<br>42<br>43<br>44<br>45 |

| APPENDIX A. PA-RISC MULTIMEDIA INSTRUCTION SET                                                                                                                                                                                                                                                                                        | 48                               |

| APPENDIX B. DIAGNOSTIC INSTRUCTIONS                                                                                                                                                                                                                                                                                                   | 53                               |

### 1. General Description

The W90210F Embedded Controller is part of Winbond's W90K Embedded processor family. The processor is a high-performance, highly integrated 32-bit processor intended for a wide range of embedded applications, such as set-top box, web browser, X-terminal, and visual/data communication devices..

The W90210F CPU core is based on the HP PA-RISC architecture and is upward code compatible with the W90K. The PA-RISC architecture incorporates traditional RISC elements, such as instruction pipelining, a register-to-register instruction set and a large, general-purpose register file. Separate on-chip instruction and data caches allow the W90210F to fetch an instruction and access data in a single processor cycle.

The W90210F includes several features that greatly increase performance, reduce system component count and ease the overall system design task. In addition to its cache memories, the W90210F's on-chip support features include a DRAM controller, ROM/FLASH ROM interface, PCI bridge, DMA controller, two serial ports with FIFO, IEEE 1284 parallel port, timer/counters, and enhanced debug support- all features that are commonly required in embedded applications.

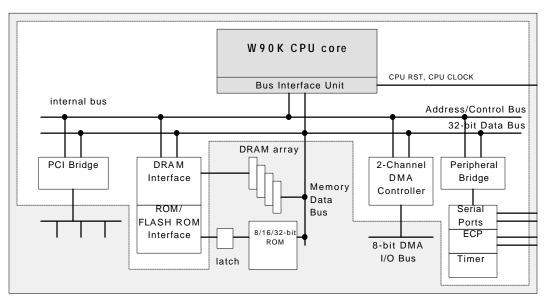

Figure 1.1 shows the system diagram of W90210F.

Figure 1.1 W90210F System Diagram

### 2. Features

Main features of the W90210F

PA-RISC architecture

PA-RISC 1.1 third edition instruction set

PA-RISC level zero implementation

Support PA-RISC Multimedia Extension 1.0 instruction set

W90K binary compatible for user software

• High-performance implementation

Five-stage pipeline

Precise, efficient handling of pipeline stalls and exceptions

Delayed branch with static branch prediction

Forward: not taken Backward: taken

One-cycle stall when prediction is wrong

HIT under miss

Both load and store can be queued when miss

Load/store single cycle execution after previous miss

On-chip cache memory

Internal I-cache: Direct mapped, 4 KB cache (256 entries, four words/entry)

Wrap around fetching when cache miss

Cache freeze capability

Internal D-cache: 2-way set associative, 2 KB cache X64 entries, four words/entry)

Write-back cache with write buffer

Write-through option

New line send to CPU before dirty line write back

Enhanced debug capability

Debug SFU supports both instruction breakpoints and data breakpoints

• High on-chip integration and simple I/O interface

486-like bus interface for CPU core

Memory controller to support four banks of DRAM and ROM/FLASH ROM

2-channel 8-bit DMA controller

PCI bridge

Two Serial ports with FIFO

Extended Capabilities Port (ECP)

Two 24-bit timer/counters

Power Down mode

Provide power down mode for power saving operation

## 4. W90210F Pin Description

| PIN Name      | DIR | PIN# | DESCRIPTION                                                                      |

|---------------|-----|------|----------------------------------------------------------------------------------|

| CPU Signal    |     |      |                                                                                  |

| RST           | 1   | 24   | CPU RESET input, high active                                                     |

| PCLK          | 1   | 22   | CPU CLOCK input                                                                  |

| OSC           | 1   | 25   | 14.318Mhz Oscillator input for Timer, UART                                       |

| PCI LOCAL BUS |     |      | for more detail description of the PCI signals please refer to the PCI LOCAL BUS |

|               | T - | T    | SPECIFICATION                                                                    |

| INTA#         |     | 87   | PCI Interrupt input, level senstive, low active signal. Once the                 |

| INTB#         |     | 88   | INTx# signal is asserted, it remains asserted until the device drive             |

| INTC#         |     | 89   | clear the pending request. When the request is cleared, the device               |

| INTD#         |     | 91   | deasserts its INTx# signal.                                                      |

| PREQ0#        | 1   | 32   | PCI Request input, indicates to the PCI arbiter that this agent                  |

| PREQ1#        |     | 33   | desires use of the bus.                                                          |

| GNT0#         | 0   | 30   | PCI Grant output, indicates to the agent that access to the bus                  |

| GNT1#         |     | 31   | has been granted.                                                                |

| PLOCK#        | 1   | 61   | PCI Lock signal, indicates an atomic operation that may require                  |

|               |     |      | multiple transactions to complete. When PLOCK# is asserted,                      |

|               |     |      | non-exclusive transactions may proceed to an address that is not                 |

|               |     |      | currently locked.                                                                |

| PCIRST#       | 0   | 27   | PCI Reset output, is used to bring PCI-specific registers,                       |

|               |     |      | sequencers, and signals to a consistent state. Low active.                       |

| PCICLK        | 0   | 28   | PCI Clock output, provides timing for all transactions on PCI and                |

|               |     |      | an input to every PCI device.                                                    |

| SERR#         | 1   | 63   | PCI System Error is for reporting address parity errors, data parit              |

|               |     |      | errors on the Special Cycle command, or any other system error                   |

|               |     |      | where the result will be catastrophic. The assertion of SERR# is                 |

|               |     |      | synchronous to the clock and meets the setup and hold times of                   |

|               |     |      | all bused signals.                                                               |

| PERR#         | I/O | 62   | PCI Parity Error is only for the reporting of data parity errors during          |

|               |     |      | all PCI transactions except a Special Cycle. The PERR# pin is                    |

|               |     |      | sustained tri-state and must be driven active by the agent receivir              |

|               |     |      | data two clocks following the data when a data parity error is                   |

|               |     |      | detected. The minimum duration of PERR# is one clock for each                    |

|               |     |      | data phase that a data parity error is detected. An agent cannot                 |

|               |     |      | report a PERR# until it has claimed the access by asserting                      |

|               |     |      | DEVSEL# (for a target) and completed a data phase or is the                      |

|               |     |      | master of the current transaction.                                               |

| PDA[31:0]           | tri-state<br>I/O | 34-38, 40-41, 43,<br>45-52, 68-75, 78-<br>79, 81-86 | PCI tri-state Address/Data bus, Address and Data are multiplexed on the same PCI pins. A bus transaction consists of an address phase followed by one or more data phases. PCI supports both read and write bursts. The address phase is the clock cycle in which FRAME# is asserted. During the address phase PDA[31:0] contain a physical address. During data phases PDA[7:0] contain the least significant byte (Isb) and PDA[31:24] contain the most significant byte (msb). Write data is stable and valid when IRDY# asserted and read data is stable and valid when TRDY# is asserted. Data is transferred during those clocks where both IRDY# and TRDY# are asserted. |

|---------------------|------------------|-----------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STOP#               | I/O              | 60                                                  | PCI Stop indicates the current target is requesting the master to stop the current transaction.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| TRDY#               | I/O              | 58                                                  | PCI Target Ready indicates the selected device's ability to complete the current data phase of the transaction. A data phase is completed on any clock both TRDY# and IRDY# are sampled asserted. During a read, TRDY# indicates that valid data is prese on PDA[31:0]. During a write, it indicates the target is prepared to accept data. Wait cycles are inserted until both IRDY# and TRDY are asserted together.                                                                                                                                                                                                                                                           |

| DEVSEL#             | I/O              | 59                                                  | PCI Device Select, when actively driven, indicates the driving device has decoded its address as the target of the current access. As an input, DEVSEL# indicates whether any device on the bus has been selected.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| C/BE[3:0]#          | I/O              | 44,53,66,76                                         | PCI Bus Command and Byte Enables are multiplexed on the same PCI pins. During the address phase of a transaction, C/BE[3:0]# define the bus command. During the data phase C/BE[3:0]# are used as Byte Enables. The Byte Enables are valid for the entire data phase and determine which byte lanes carry meaningful data. C/BE[0]# applies to byte 0 (lsb) and C/BE[3]# applies to byte 3 (msb).                                                                                                                                                                                                                                                                               |

| FRAME#              | I/O              | 55                                                  | PCI Cycle Frame is driven by the current master to indicate the beginning and duration of an access. FRAME# is asserted to indicate a bus transaction is beginning. While FRAME# is asserted, data transfers continue. When FRAM# is deasserted, the transaction is in the final data phase or has completed.                                                                                                                                                                                                                                                                                                                                                                   |

| IRDY#               | I/O              | 56                                                  | PCI Initiator Ready indicates the bus master's ability to complete the current data phase of the transaction. A data phase is completed on any clock both IRDY# and TRDY# are sampled asserted. During a write, IRDY# indicates that valid data is preser on PDA[31:0]. During a read, it indicates the master is prepared to accept data. Wait cycles are inserted until both IRDY# and TRDY are asserted together.                                                                                                                                                                                                                                                            |

| PPAR  DMA Interface | I/O              | 65                                                  | PCI Parity is even parity across PDA[31:0] and C/BE[3:0]#. PPAR is stable and valid one clock after the address phase. For data phases, PPAR is stable and valid one clock after either IRDY# is asserted on a write transaction or TRDY# is asserted on a read transaction. (PPAR has the same timing as PDA[31:0], but it is delayed by one clock.) The mater drives PPAR for address and write data phases; the target drives PPAR for read data phase.                                                                                                                                                                                                                      |

| DREQ0             | 1         | 131             | DMA Request signals request an external transfer on DMA                                                      |

|-------------------|-----------|-----------------|--------------------------------------------------------------------------------------------------------------|

| DREQ1             |           | 133             | channel 0 (DREQ0) or DMA channel 1 (DREQ1).                                                                  |

| DACK0             | 0         | 134             | DMA Acknowledge signals acknowledge an external transfer on                                                  |

| DACK1             |           | 135             | DMA channel 0 (DREQ0) or DMA channel 1 (DREQ1).                                                              |

| DMARDY            | ı         | 116             | DMA Device Ready signal is used to extend the length of DMA                                                  |

|                   |           |                 | bus cycles. If a device wants to extend the DMA bus cycles, it wil                                           |

|                   |           |                 | force the DMARDY signal low when it decodes its address and                                                  |

|                   |           |                 | receives a IOR or IOW command.                                                                               |

| CS0               | 0         | 136             | DMA Chip Select signals select the corresponding I/O devices for                                             |

| CS1               |           | 137             | programming or DMA transfers.                                                                                |

| DA[0:11]          | 0         | 114-104,102     | 12-bit DMA I/O Address Bus, bit 0 is the most significant bit.                                               |

| IOR               | 0         | 119             | DMA I/O read signal is used to indicate to the I/O device that the                                           |

|                   |           |                 | present bus cycle is an I/O read cycle.                                                                      |

| IOW               | 0         | 117             | DMA I/O write signal is used to indicate to the I/O device that the present bus cycle is an I/O write cycle. |

| TC0               | 0         | 120             | Terminal count for DMA channels, the pin is driven active for one                                            |

| TC1               |           | 121             | clock when byte count reaches zero and after the last transfer for                                           |

|                   |           |                 | a DAM has completed.                                                                                         |

| DD[0:7]           | I/O       | 130,128-122     | 8-bit DMA I/O Data bus, bit 0 is the most significant bit.                                                   |

| ECP Interface     | '         |                 | For more detail description of the ECP interface signals, please                                             |

|                   |           |                 | refer to the IEEE P1284 Standard                                                                             |

| Busy              | I         | 138             | ECP busy input signal                                                                                        |

| nFault            | I         | 139             | ECP fault input                                                                                              |

| nAck              | I         | 140             | ECP acknowledge input                                                                                        |

| PError            | I         | 141             | ECP parity error                                                                                             |

| Select            | I         | 142             | ECP Select                                                                                                   |

| nSelectIn         | 0         | 153             | ECP select output                                                                                            |

| nlnit             | 0         | 154             | ECP initialization                                                                                           |

| nAutoFd           | 0         | 155             | ECP Autofeed                                                                                                 |

| nStrobe           | 0         | 156             | ECP Strobe                                                                                                   |

| ED[0:7]           | I/O       | 152-148,146-    | Bi-directional ECP Data bus, ED[0] is the most significant bit                                               |

|                   |           | 145,143         | (msb).                                                                                                       |

| Memory Controller | Interface |                 |                                                                                                              |

| RAS#[0:3]         | 0         | 201-204         | DRAM Row Address Strobe, Banks 0-3. These signals are used                                                   |

|                   |           |                 | to select the DRAM row address. A High-to-Low transition on one                                              |

|                   |           |                 | of these signals causes a DRAM in the corresponding bank to                                                  |

|                   |           |                 | latch the row address and begin an access.                                                                   |

| CAS#[0:3]         | 0         | 195,197-198,200 | DRAM Column Address Strobes, Byte 0-3. These signals are                                                     |

|                   |           |                 | used to select the DRAM column address. A High-to-Low                                                        |

|                   |           |                 | transition on these signals causes the DRAM selected by                                                      |

|                   |           |                 | RAS#[0:3] to latch the column address and complete the access.                                               |

| WE#               | 0         | 205             | DRAM Write Enable signal is used to write the selected DRAM                                                  |

|                   |           |                 | bank.                                                                                                        |

| RCS#[0:3]         | 0         | 17-18,20-21     | ROM Chip Selects, Banks 0-3. A low level on one of these signals                                             |

| 501151:           |           | 1               | selects the memory devices in the corresponding ROM bank.                                                    |

| ROMEN             | 0         | 14              | ROM Address Latch, ROM address are divided into two portions,                                                |

|                   |           |                 | higher address bits and lower address bits, the address will be pu                                           |

|                   |           |                 | out on the MA bus in two consecutive cycles. The ROMEN signal                                                |

|                   |           |                 | is used to latch the higher address bits in the first ROM address                                            |

|                   |           |                 | cycle.                                                                                                       |

| ROMRW#             | 0      | 15                                                                  | FLASH ROM write enable. This signal is used to write data into the mrmory in a ROM bank (such as Flash ROM).                                                                                                                                                                                                                                                  |

|--------------------|--------|---------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ROMOE#             | 0      | 16                                                                  | ROM output enable. This signal enables the selected ROM Bank to drive the MD bus.                                                                                                                                                                                                                                                                             |

| MA[0:11]           | 0      | 206-208,1,3-4,6-<br>7,9-10,12-13                                    | Memory controller Memory Address bus. For DRAM access, MA[0:11] is the DRAM row address and the DRAM column address. For ROM/FLASH ROM access, MA[0:11] is the higher portion ROM space address bits in the first ROM address cycle, and the lower portion ROM space address bits after the first ROM address cycle. MA[0] is the most significant bit (msb). |

| MD[0:31]           | I/O    | 157-159,161-<br>162,164-167,169-<br>170,172-178,180-<br>181,183-194 | Memory controller Data bus for both DRAM data and ROM space data. Bit 0 is the most significant bit (msb).                                                                                                                                                                                                                                                    |

| COM1 Serial Port S | Signal |                                                                     |                                                                                                                                                                                                                                                                                                                                                               |

| SIN1               | I      | 92                                                                  | COM1 serial data input from the communication link (modem or peripheral device).                                                                                                                                                                                                                                                                              |

| SOUT1              | 0      | 94                                                                  | COM1 serial data output to the communication link (modem or peripheral device).                                                                                                                                                                                                                                                                               |

| CTS1n              | 1      | 95                                                                  | COM1 clear to send signal                                                                                                                                                                                                                                                                                                                                     |

| DSR1n              | 0      | 96                                                                  | COM1 data set ready                                                                                                                                                                                                                                                                                                                                           |

| DTR1n              | 1      | 97                                                                  | COM1 data terminal ready                                                                                                                                                                                                                                                                                                                                      |

| RTS1n              | 0      | 98                                                                  | COM1 request to send                                                                                                                                                                                                                                                                                                                                          |

| DCD1n              | 1      | 100                                                                 | COM1 data carrier detect                                                                                                                                                                                                                                                                                                                                      |

| RIN1n              | 0      | 103                                                                 | COM1 ring indicator                                                                                                                                                                                                                                                                                                                                           |

| COM2 Serial Port S | Signal |                                                                     |                                                                                                                                                                                                                                                                                                                                                               |

| SIN2               | I      | 99                                                                  | COM2 serial data input from the communication link (modem or peripheral device).                                                                                                                                                                                                                                                                              |

| SOUT2              | 0      | 101                                                                 | COM2 serial data output to the communication link (modem or peripheral device).                                                                                                                                                                                                                                                                               |

### 5. W90210F CPU Core

The key characteristics of the W90210F CPU core have been designed specifically to meet the requirements of embedded control applications. The following subsections describe the essential features of the W90210F CPU core, including its architecture, implementations, and registers.

#### 5.1 Architecture

The W90210F CPU core is designed based on the powerful PA-RISC architecture. Since our target is highend embedded applications, a great deal of design effort has been devoted to taking full advantage of this powerful architecture.

#### 5.1.1 PA-RISC Rev. 1.1 third edition

The core of the W90210F is a processor unit that complies with PA-RISC architecture Rev. 1.1 third edition specifications. There are three kinds of operations to be executed by the processor; branch, load/store, and data transform. Most RISC architecture chooses to execute one of the three operations in an instruction. On the contrary, most PA-RISC instructions perform two operations listed above. For example, "ADD and BRANCH on the result of the ADD" can be done with one PA-RISC instruction. W90210F CPU core implements these powerful instructions and executes them in a single cycle. With such a powerful combined operation instruction set, the code size of W90210F can be much smaller than other RISC system. With the single cycle execution capability of these instructions, W90210F deliver very high throughput.

#### 5.1.2 Level 0 implementation

In the PA-RISC architecture, a processor without an MMU is defined as the Level 0 implementation. All memory and I/O accesses in a level 0 PA-RISC processor are in real mode. W90210F is a level 0 implementation of PA-RISC architecture.

#### 5.1.3 Multimedia Extension Instruction Set

The PA-RISC Multimedia extensions consists of a set of instructions which speed up the execution of common operations found in multimedia applications. In a 32-bit integer datapath, each multimedia instruction allows generic arithmetic operations to be executed in parallel on two pairs of 16-bit data. The PA-RISC multimedia extensions 1.0 instruction set is implemented by the W90210F CPU core.

### 5.2 CPU resources

The W90210F CPU core implements all the registers needed for a Level 0 processor as defined in the PA-RISC specifications. Some registers or register bits are not needed in a Level 0 processor and are defined as nonexistent registers or register bits. The W90210F CPU implements three AIRs (Architecture Invisible Registers) that can be accessed by executing DIAG instructions.

#### 5.2.1 General registers

Thirty-two 32-bit general registers provide the central resource for all computation. They are numbered GR 0 through GR 31, and are available to all program at all privilege levels. GR 0, when referenced as source operand, delivers zeros. When GR 0 is used as destination, the result is discarded. GR 1 is the target of the ADD IMMEDIATE LEFT instruction. GR 31 is the instruction address offset link register for the base relative interspace procedure call instruction. GR 1 and GR 31 can also be used as general register.

|       | 0 31                                 |

|-------|--------------------------------------|

| GR 0  | Permanent zero                       |

| GR 1  | Target for ADDIL or General use      |

| GR 2  | General use                          |

|       | •                                    |

|       | •                                    |

|       | •                                    |

| GR 30 | General use                          |

| GR 31 | Link register for BLE or General use |

Figure 5.1 General Registers

### 5.2.2 Shadow registers

W90210F CPU core provides seven registers called shadow registers as defined in the PA-RISC architecture. The contents of GR1,8,9,16,17,24 and 25 are copied upon interruptions. Shadow registers reduce the state save and restore time by eliminating the need for general register saves and restores in interruption handlers. The behavior of the shadow registers is described below.

Before entering interrupt routine: Contents of seven general registers are copied into shadow registers in one cycle. When executing RFIR: Contents of shadow registers are copied into general registers automatically in one cycle.

#### 5.2.3 Processor Status Word (PSW)

The processor state of W90K is encoded in a 32-bit register called the Processor Status Word (PSW). The format of PSW is shown in figure 5.2. The old value of the PSW is saved in the Interrupt Processor Status Word (IPSW) when interruption occurs. The PSW is set to the contents of the IPSW by the RFIR (RETURN FROM INTERRUPTION and RESTORE) instruction.

| 0     | 1 | 2 4  | 5                                                                                                  | 6      | 7      | 8      | 9      | 0      | 1                | 2      | 3      | 4     | 5      | 6     |         | 3       | 4     | 5        | 6      | 7      | 8      | 9     | 0       | 1 |

|-------|---|------|----------------------------------------------------------------------------------------------------|--------|--------|--------|--------|--------|------------------|--------|--------|-------|--------|-------|---------|---------|-------|----------|--------|--------|--------|-------|---------|---|

| Υ     | Z | rv   | Е                                                                                                  | S      | Т      | Н      | L      | N      | Χ                | В      | С      | ٧     | М      |       | C/B     |         | rv    | G        | F      | R      | Q      | Р     | D       | ١ |

| Field | d |      |                                                                                                    |        |        |        |        |        |                  |        |        | De    | script | ion   |         |         |       |          |        |        |        |       |         | l |

| rv    |   | Re   | serve                                                                                              | d bits | i.     |        |        |        |                  |        |        |       |        |       |         |         |       |          |        |        |        |       |         |   |

| Υ     |   | Da   | ta det                                                                                             | oug tr | ap d   | isabl  | e.     |        |                  |        |        |       |        |       |         |         |       |          |        |        |        |       |         | l |

| Z     |   | Ins  | tructio                                                                                            | n de   | bug    | trap   | disal  | ole.   |                  |        |        |       |        |       |         |         |       |          |        |        |        |       |         |   |

| Е     |   | Litt | e end                                                                                              | lian r | mode   | e ena  | ble.   | Whe    | n 1,             | all in | struc  | tion  | fetch  | es an | d loads | s/store | s are | e little | e end  | dian.  | The    | E bit | t after | l |

|       |   | RE   | SET i                                                                                              | s set  | acco   | ordin  | g to   | the s  | tate             | of E   | NDI    | N p   | in.    |       |         |         |       |          |        |        |        |       |         | l |

| S     |   |      |                                                                                                    |        |        |        |        |        |                  |        |        |       |        |       | only by |         |       |          | _      |        | most   | privi | leged   |   |

|       |   |      |                                                                                                    |        |        |        |        |        |                  |        |        |       |        |       | ting at |         |       |          |        |        |        |       |         | l |

| Т     |   | Ta   | ken bi                                                                                             | anch   | ena    | ble.   | Whe    | n 1, a | any <sup>·</sup> | take   | n bra  | ınch  | is te  | rmina | ted wit | h a ta  | ken   | bran     | ch tr  | ар.    |        |       |         | l |

| Н     |   | Hiç  | her-p                                                                                              | rivile | ge tr  | ansfe  | er tra | p en   | able             |        |        |       |        |       |         |         |       |          |        |        |        |       |         | 1 |

| L     |   | Lo   | ver-pr                                                                                             | ivileg | ge tra | ansfe  | r tra  | o ena  | able.            |        |        |       |        |       |         |         |       |          |        |        |        |       |         | l |

| N     |   | Nu   | lify. T                                                                                            | he c   | urrer  | nt ins | truct  | ion is | s nul            | lified | d whe  | en th | is bit | is 1. |         |         |       |          |        |        |        |       |         | l |

| Χ     |   | No   | n-exis                                                                                             | tent   | regis  | ter b  | it.    |        |                  |        |        |       |        |       |         |         |       |          |        |        |        |       |         | l |

| В     |   | Ta   | Taken branch. The B-bit is set to 1 by any taken branch instruction and set to 0 otherwise.        |        |        |        |        |        |                  |        |        |       |        |       |         |         |       |          |        |        |        |       |         |   |

| С     |   | No   | Non-existent register bit.                                                                         |        |        |        |        |        |                  |        |        |       |        |       |         |         |       |          |        |        |        |       |         |   |

| V     |   | Div  | ide st                                                                                             | ер со  | orrec  | tion.  | The    | integ  | er p             | rimit  | ive ir | nstru | ction  | recor | ds inte | rmedi   | ate s | tatus    | s in t | this t | oit to | prov  | vide a  |   |

|       |   |      | n-rest                                                                                             |        |        |        |        |        |                  |        |        |       |        |       |         |         |       |          |        |        |        |       |         | 1 |

| M     |   | _    | -                                                                                                  | -      |        |        |        |        |                  |        |        | -     |        | -     | hine C  |         |       | MCs      | s) are | e ma   | sked   | . Nor | mally   |   |

|       |   |      | 0, this bit is set to 1 after HPMC and set to 0 after all other interruptions.                     |        |        |        |        |        |                  |        |        |       |        |       |         |         |       |          |        |        |        |       |         |   |

| C/E   | 3 |      | Carry/borrow bits. These bits are updated by some instructions from the corresponding carry/borrow |        |        |        |        |        |                  |        |        |       |        |       |         |         |       |          |        |        |        |       |         |   |

|       |   |      | outputs of the 4-bit digit of the ALU.                                                             |        |        |        |        |        |                  |        |        |       |        |       |         |         |       |          |        |        |        |       |         |   |

| G     |   | De   | oug tr                                                                                             | ap er  | nable  | €.     |        |        |                  |        |        |       |        |       |         |         |       |          |        |        |        |       |         | l |

| F     |   | No   | Non-existent register bit.                                                                         |        |        |        |        |        |                  |        |        |       |        |       |         |         |       |          |        |        |        |       |         |   |

13 Version 1.4, 10/8/97

| R | Recovery counter enable. When 1, recovery counter traps occur if bit 0 of the recovery counter is a 1. This |

|---|-------------------------------------------------------------------------------------------------------------|

|   | bit also enables decrementing of the recovery counter.                                                      |

| Q | Interrupt state collection enable. When 1, interruption state is collected.                                 |

| Р | Non-existent register bit.                                                                                  |

| D | Non-existent register bit.                                                                                  |

| 1 | External interruption, power failure interrupt, and low-priority machine check interruption unmask. When 1, |

|   | these interruptions are unmasked and can cause an interruption.                                             |

Figure 5.2 Processor Status Word

#### 5.2.4 Control registers

There are twenty-five control registers in W90210F, numbered CR0, and CR8 through CR31, which contain system state information. Figure 5.3 shows the control registers. The access of CR 11, 16, 26, and 27 are described in the following table (table 5.4). Those control registers not listed in table 5.4 are only accessible by code executing at the most privileged level. Control registers 1 through 7 are reserved registers. The unused bits of the Coprocessor Configuration Register are reserved bits. The unused bits of the Shift Amount Register are nonexistent bits. In Level systems, CRs 8, 9, 12, 13, 17, and 20 are nonexistent registers.

| 0     |                                               |             | 3            |  |  |  |  |  |

|-------|-----------------------------------------------|-------------|--------------|--|--|--|--|--|

| CR 0  | Recovery Coun                                 | ter         |              |  |  |  |  |  |

| CR 1  | reserved                                      |             |              |  |  |  |  |  |

|       | •                                             |             |              |  |  |  |  |  |

|       | •                                             |             |              |  |  |  |  |  |

| CR 7  | reserved                                      |             |              |  |  |  |  |  |

| CR 8  | Nonexistent regis                             | sters       |              |  |  |  |  |  |

| CR 9  | Nonexistent regis                             |             |              |  |  |  |  |  |

| CR 10 | 1                                             | CR (8 bits) | CCR (8 bits) |  |  |  |  |  |

| CR 11 | nonexistent                                   | ( (         | SAR (5)      |  |  |  |  |  |

| CR 12 | Nonexistent regis                             | sters       | 1 - (-)      |  |  |  |  |  |

| CR 13 | Nonexistent registers                         |             |              |  |  |  |  |  |

| CR 14 | Interruption Vector Address reserved          |             |              |  |  |  |  |  |

| CR 15 | External Interrupt Enable Masks               |             |              |  |  |  |  |  |

| CR 16 | Interval Timer                                |             |              |  |  |  |  |  |

| CR 17 | Nonexistent registers                         |             |              |  |  |  |  |  |

| CR 18 | Interruption Instruction Address Offset Queue |             |              |  |  |  |  |  |

| CR 19 | Interruption Instruction                      | n Register  |              |  |  |  |  |  |

| CR 20 | Nonexistent regis                             |             |              |  |  |  |  |  |

| CR 21 | Interruption Offset F                         |             |              |  |  |  |  |  |

| CR 22 | Interruption Processor S                      |             |              |  |  |  |  |  |

| CR 23 | External Interrupt Reque                      |             |              |  |  |  |  |  |

| CR 24 | Temporary Regis                               | sters       |              |  |  |  |  |  |

|       | •                                             |             |              |  |  |  |  |  |

|       | •                                             |             |              |  |  |  |  |  |

| CR 31 | Temporary Regis                               | sters       |              |  |  |  |  |  |

| ,J.   | Figure 5.3 Control                            |             |              |  |  |  |  |  |

| Privilege level for the access  |

|---------------------------------|

| i fivilege level for the access |

| CR 11     | read/write at any privilege level            |

|-----------|----------------------------------------------|

| CR 16     | PSW 'S'=0: read/write by any privilege level |

|           | PSW 'S'=1: read/write by privileged software |

| CR 26, 27 | readable at any privilege level              |

|           | writable at the most privileged level        |

| Others    | Accessible only at most privileged level     |

Table 5.4 Access of control registers

#### 5.2.5 W90210F External Interrupt Request register (EIRR; CR23)

| Bit     | EI[0:4] | External     | Description                             |

|---------|---------|--------------|-----------------------------------------|

| Number  |         | Interrupt    |                                         |

| 0       | 00000   | Timer_Int    | Interval Timer (CR16) interrupt request |

| 1       | 10000   | -            |                                         |

| 2       | 01000   | -            |                                         |

| 3       | 11000   | Serial       | Serial port interrupt request from COM2 |

| 4       | 00100   | INTA         | PCI bus INTA# interrupt request         |

| 5       | 10100   | INTB         | PCI bus INTB# interrupt request         |

| 6       | 01100   | INTC         | PCI bus INTC# interrupt request         |

| 7       | 11100   | INTD         | PCI bus INTD# interrupt request         |

| 8       | 00010   | Parallel_Int | Parallel port interrupt request         |

| 9       | 10010   | Serial_Int   | Serial port interrupt request from COM1 |

| 10      | 01010   | DMA_Int      | DMA interrupt request                   |

| 11      | 11010   | TC_Int       | Timer/Counter interrupt request         |

| 12 - 31 | -       | -            | Reserved                                |

|         |         |              |                                         |

Table 5.5 External Interrupt Request Register

#### 5.2.6 AIRs (Architecture Invisible Registers)

There are eight AIRs in the W90210F. AIR[0] controls the internal cache configuration, burst mode, and default endian. AIR[0] is documented in this data sheet. AIR[1] and AIR[2] are reserved for chip testing by Winbond, and their functions will not be disclosed to users. Attempting to access these two registers may cause programs to be executed with unpredictable results. Memory configuration registers are used for programming the configuration of W90210F memory space. AIR[7] is the PCO register, this AIR can only be accessed through the JTAG ICE interface.

| J | io uno i o o rogiotor, t | mermer same only we accessed unrough the critical |

|---|--------------------------|---------------------------------------------------|

|   | AIR[0]                   | Internal configuration register                   |

|   | AIR[1]                   | PSW register                                      |

|   | AIR[2]                   | TMR register                                      |

|   | AIR[3]                   | Memory configuration register 1                   |

|   | AIR[4]                   | Memory configuration register 2                   |

|   | AIR[5]                   | Memory configuration register 3                   |

|   | AIR[6]                   | Memory configuration register 4                   |

|   | AIR[7]                   | PCO register (program counter)                    |

Table 5.6 W90210F CPU core AIRs

Important: Enabling or disabling the internal I-cache with MTAIR[0] will invalidate all I-cache entries automatically. Enabling the internal D-cache with MTAIR[0] will invalidate all cache entries without dirty data entries being written back. Disabling the D-cache, however, will not invalidate cache entries.

Disabling the internal D-cache with MTAIR[0] will cause dirty data to be left in the D-Cache and not automatically written into memory. When a program references the dirty data location, stale data in memory will be returned. To prevent this, a cache invalidation routine should be performed before the internal D-cache is disabled. The invalidation routine must flush all cache entries one by one. This will invalidate the cache and also write back any dirty data.

AIR[1] and AIR[2] are reserved registers and should never be written to or read from them. Accessing these registers will cause unpredictable result.

### 5.3 Implementation of the PA-RISC instructions

The W90210F CPU core implements all the instructions specified in the PA-RISC Rev. 1.1 third edition. W90210F executes these instructions with results that comply to the PA-RISC architecture. MMU related instructions are executed by W90210F as defined in the PA-RISC architecture for a Level 0 processor. PA-RISC multimedia extension 1.0 instruction set is also supported by W90210F. To speed up multimedia operations in some applications, three additional instructions are defined through the diagnostic instructions. In addition to that, debug SFU is provided to enhance the debug capability. The chip also implements DIAG instructions defined by Winbond for chip testing, diagnostics, and programming the internal AIR (architecture invisible register). These DIAG instructions comply with the PA-RISC DIAG instructions.

### 5.3.1 Implementation of Level 0 instructions

In the Level 0 processor implementation, the S-fields of all instructions are ignored and have no effect on the device functions. The following instructions for TLB handling are executed as null instructions, as specified in the architecture reference manual:

| architecture reference mariaan. |                                   |  |  |  |

|---------------------------------|-----------------------------------|--|--|--|

| Instruction                     | Function                          |  |  |  |

| PDTLB                           | Purge data TLB                    |  |  |  |

| PITLB                           | Purge instruction TLB             |  |  |  |

| PDTLBE                          | Purge data TLB entry              |  |  |  |

| PITLBE                          | Purge instruction TLB entry       |  |  |  |

| IDTLBA                          | Insert data TLB address           |  |  |  |

| IITLBA                          | Insert instruction TLB address    |  |  |  |

| IDTLBP                          | Insert data TLB protection        |  |  |  |

| IITLBP                          | Insert instruction TLB protection |  |  |  |

Table 5.7 Instructions executed as null instructions

Table 5.8 lists the differences in instruction execution results in a Level 0 processor.

| Instruction | Description                       | Difference                                                  |

|-------------|-----------------------------------|-------------------------------------------------------------|

| LPA         | Load physical address             | Undefined instruction                                       |

| LCI         | Load coherence index              | Undefined instruction                                       |

| LDWAX       | Load word absolute index          | Same as LDWX if priv=0                                      |

| LDWAS       | Load word absolute short          | Same as LDWS if priv=0                                      |

| STWAS       | Store word absolute short         | Same was STWS if priv=0                                     |

| GATE        | Gateway                           | Always promote priv to 0                                    |

| BV          | Branch vectored                   | Demote priv to any non zero value                           |

| BE          | Branch external                   | Demote priv to any non zero value, IASQ is nonexistent      |

| BLE         | Branch and link external          |                                                             |

| RFI         | Return from interrupt             | IASQ is nonexistent                                         |

| RFIR        | Return from interrupt and restore |                                                             |

| LDSID       | Load space identifier             | 0 is written into specified GR                              |

| MTSP        | Move to space register            | Executed as null instruction                                |

| MTCTL       | Move to control register          | Executed as null instruction if target is 8,9,12,13,17 or   |

|             |                                   | 20                                                          |

| MFSP        | Move from space register          | is written into specified GR                                |

| MFCTL       | Move from control register        | 0 is written into specified GR if source is 8,9,12,13,17 or |

|             |                                   | 20                                                          |

| PROBER      | Probe read access                 | Always set target GR to 1                                   |

| PROBERI     | Probe read access immediate       | Always set target GR to 1                                   |

| PROBEW      | Probe write access                | Always set target GR to 1                                   |

| PROBEWI     | Probe write access immediate      | Always set target GR to 1                                   |

Table 5.8 Summary of Level 0 instruction differences

### 5.3.2 Implementation of cache-related instructions

It is assumed that in the W90210F application system all DMA transfers will be completed in order. The instruction for DMA cache synchronization SYNCDMA will be executed as a null instruction. The W90210F CPU core does not snoop the external bus to check the coherence of the cache. To ensure that the contents of the memory remain consistent, devices outside the W90210F CPU can access only non-cacheable memory. FLUSH and purge cache instructions will flush the internal cache only. The W90210F will not broadcast a flush or purge operation to the secondary cache or other bus master (if any).

FICE and FDCE are implemented as described below.

- FICE will flush all instruction cache entries. All instruction entries become invalid after the execution of FICE

- FDCE is used to flush an individual cache entry. This instruction causes dirty data to be written back to memory.

The data cache in the W90210F has 2 x 64 entries. To flush the entire data cache, a loop that execute a flush to a single entry can be used to flush the entire data cache.

| Instruction               | Execution result                                                  |

|---------------------------|-------------------------------------------------------------------|

| SYNCDMA                   | Null                                                              |

| FDCE, FICE                | See description above                                             |

| FDC, FDCE, FIC, FICE, PDC | Affect internal cache only and are not broadcast to external bus. |

Table 5.9 Cache-related instructions and execution results

#### 5.3.3 PA-RISC multimedia extension instruction set

The PA-RISC Multimedia extensions consists of a set of instructions which speed up the execution of common operations found in multimedia applications. Multimedia instructions perform multiple parallel operations in a single cycle.

| Instruction | Description                           |  |

|-------------|---------------------------------------|--|

| HADD        | Halfword parallel add                 |  |

| HSUB        | Halfword parallel subtract            |  |

| HAVE        | Halfword parallel average             |  |

| HSHRADD     | Parallel halfword shift right and add |  |

| HSHLADD     | Parallel halfword shift left and add  |  |

Table 5.10 PA-RISC multimedia instructions

### 5.3.4 DIAG instruction

DIAG instructions are a special instruction format defined by PA-RISC; the functions of these instructions depend on the specific implementation. These instructions are used to program special control registers in the W90K that are not visible in the PA-RISC architecture.

The DIAG instruction syntax is not supported by the assembler. A special macro file provided by Winbond must be included in user programs. The macro converts DIAG assembly instructions into a format recognized by the assembler. With the help of this file, users can employ the DIAG syntax described below for programming.

| Instruction | Description                                                             |

|-------------|-------------------------------------------------------------------------|

| HALT        | Force W90210F CPU enter the HALT state                                  |

| MTAIR       | Copies value into a specified AIR from a general register               |

| MFAIR       | Copies value into a general register from AIR register                  |

| MTITAG      | Copies value into a specified Instruction Tag from a general register   |

| MFITAG      | Copies value into a general register from a instruction tag             |

| MTICAH      | Copies value into a specified Instruction cache from a general register |

| MFICAH      | Copies value into a general register from a instruction cache entry     |

| MTDTAG      | Copies value into a specified data Tag from a general register          |

| MFDTAG      | Copies value into a general register from a data tag                    |

| MTDCAH      | Copies value into a specified data cache from a general register        |

| MFDCAH      | Copies value into a general register from a data cache entry            |

| LDHU        | Load halfword and unpack                                                |

| HABSADD     | Halfword absolute and add                                               |

Table 5.11 DIAG instructions

### 5.4. Debug Special Function Unit

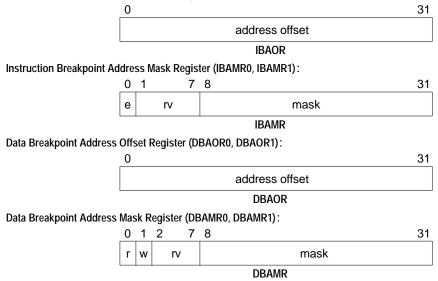

The debug special function unit is an optional, architected SFU which provides hardware assistance for software debugging using breakpoints. The debug SFU is currently provided in the W90210F CPU core. The debug SFU supports two sets of registers for both data breakpoints and instruction breakpoints.

For the instruction debug trap, the trapping address is stored in the interruption instruction address offset queue (IIAOQ). For the data debug trap, the trapping address is stored in the interruption offset register (IOR).

The e bit in each IBAMR determines whether this instruction breakpoint is enabled. If the e bit is 1, any attempt to execute an instruction (including nullified instructions) at an address matching the corresponding IBAOR will cause an instruction debug trap. If the e bit is 0, that instruction breakpoint is disabled.

Instruction Breakpoint Address Offset Register (IBAOR0, IBAOR1):

Figure 5.12 Debug SFU registers

The r and w bits in each DBAMR determine the type of access this data breakpoint is enabled for. If the r bit is 1, any non-nullified load or semaphore instruction to an address matching the corresponding DBAOR will cause a data debug trap. If the w bit is 1, any non-nullified store or semaphore instruction or cache purge operation to an address matching the corresponding DBAOR will cause a data debug trap. If the r and w bits are both 0, the data breakpoint is disabled.

For the control of the debug SFU, three bits are added to the PSW register.

Debug Trap Enable Bit (G): Bit 25 of the PSW is defined as the G-bit- the debug trap enable bit. When the G-bit is 1, the data debug trap and instruction debug trap are enabled; when 0, the traps are disabled. The G-bit is set to 0 on interruptions.

Data Debug Trap disable Bit (Y): Bit 0 of the PSW is defined as the Y-bit. The Y-bit is set to 0 after the execution of each instruction, except for RFI and RFIR instructions which may set it to 1. When 1, data debug traps are disabled.

Instruction Debug Trap disable Bit (Z): Bit 1 of the PSW is defined as the Z-bit. The Z-bit is set to 0 after the execution of each instruction, except for RFI and RFIR instructions which may set it to 1. When 1, instruction debug traps are disabled.

In addition, CCR bits 16- 23 are used as enable/disable bits for SFUs 0- 7. The debug SFU will use bit 17. When bit 17 is enabled, the SFU #1 instructions will operate normally, but when disabled, all SFU #1 instructions will take an assist emulation trap.

Two new exceptions are added to the architecture- one for instruction debugging and one for data debugging. Instruction Debug Trap (30): Interruption #30 is now defined as the instruction debug trap. This trap belongs to group 3.

Data Debug Trap (31): Interruption #31 is defined as the data debug trap. This trap belongs to group3. Following instructions are added for the debug SFU.

| Mnemonic | Description                                              | Operation        |

|----------|----------------------------------------------------------|------------------|

| MTDBAO   | Move to data breakpoint address offset register          | DBAOR[t]\(-GR[r] |

| MFDBAO   | Move from data breakpoint address offset register        | GR[t]←DBAOR[r]   |

| MTDBAM   | Move to data breakpoint address mask register            | DBAMR[t]←GR[r]   |

| MFDBAM   | Move from data breakpoint address mask register          | GR[t]←DBAMR[r]   |

| MTIBAO   | Move to instruction breakpoint address offset register   | IBAOR[t]←GR[r]   |

| MFIBAO   | Move from instruction breakpoint address offset register | GR[t]←IBAOR[r]   |

| MTIBAM   | Move to instruction breakpoint address mask register     | IBAMR[t]←GR[r]   |

| MFIBAM   | Move from instruction breakpoint address mask register   | GR[t]←IBAMR[r]   |

| DEBUGID  | Debug SFU identify                                       | GR[t]←id number  |

Table 5.13 Debug SFU instructions

### 5.5 Addressing and access control

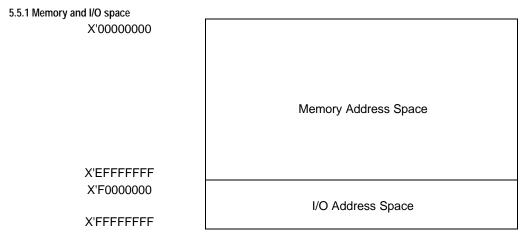

The W90210F implements real mode addressing. The total addressable space for the W90210F is 4 GB. Objects in the memory and I/O system are addressed using 32-bit absolute addresses. An absolute pointer is a 32-bit unsigned integer whose value is the address of the lowest addressed byte of the operand it designates. The address mapping is same as that specified by the PA-RISC architecture.

Figure 5.16 Memory and I/O addresses

Figure 5.16 shows the memory and I/O address space allocation.

Total memory address space available is (4 GB-256 MB). Total addressable I/O space is 256 MB.

Program address for I/O: Fxxxxxxx

W90210F CPU core output address: 0xxxxxxx

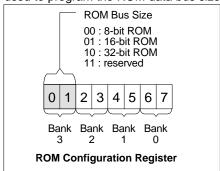

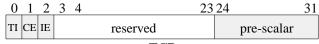

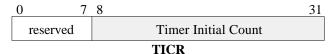

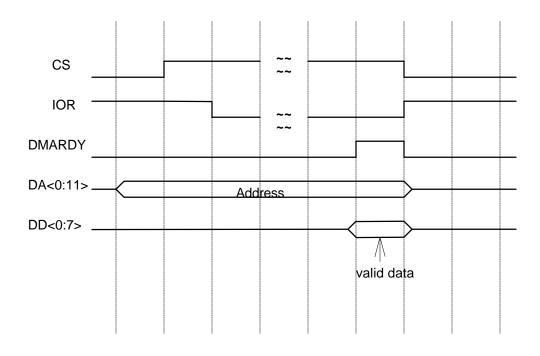

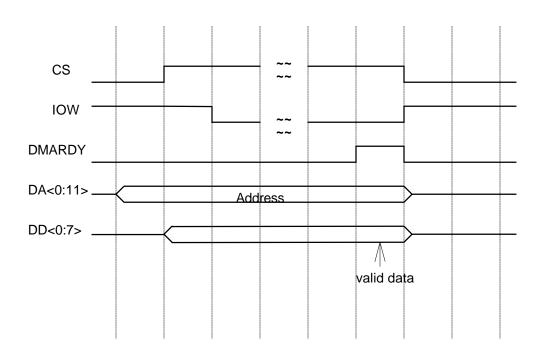

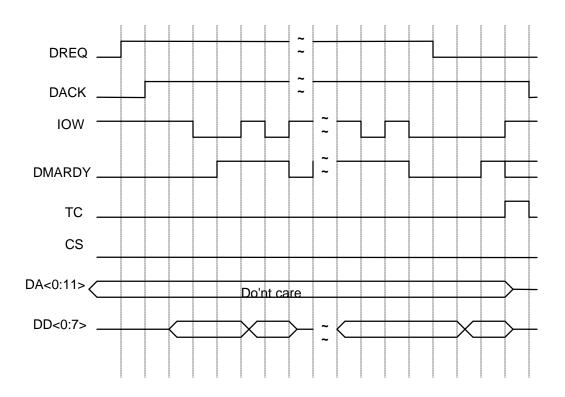

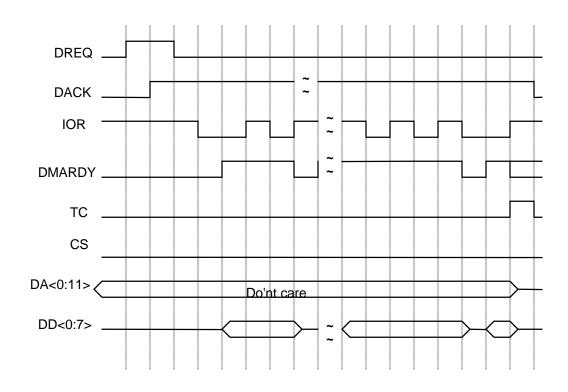

#### 5.5.2 RESET addresses