# QUAD TRAKKING™ POWER SUPPLY MANAGER WITH 1% UV/OV THRESHOLD ACCURACY

## **FEATURES & APPLICATIONS**

- 1% OV and UV Threshold Accuracy

- Programmable Softstart, Tracking and Voltage Monitoring Functions

- Controls 4 Independent Supplies Down to 0.9V Programmable Bus-Side and Card-Side UV and OV Thresholds

- Guarantees Differential Supply Tracking

- Operates From Any One of Four Supply Voltages down to 2.7V

- Four independent RST#s, two IRQ#s, CROWBAR and Circuit breaker functions

- I<sup>2</sup>C 2-Wire Serial Bus Interface for Programming, Power On/Off and Operational Status

- 256X8 Nonvolatile EEPROM Memory Array

#### **Applications**

- Power Supply Management

- Telecom/Datacom Motherboards/Servers

- Mezzanine Line Cards

- Compact PCI<sup>™</sup> Hot Swap Control

- Network Processors, DSPs, ASICs

## INTRODUCTION

The SMT4004A trakker<sup>tm</sup> is a fully integrated programmable voltage manager IC, providing precision accuracy ( $\pm 1\%$ ) supervisory functions and tracking control for up to four independent power supplies. The four internal managers perform the following functions: monitor source (bus-side) voltages for under-voltage and over-voltage conditions, monitor back end (card-side) voltages for under-voltage conditions, ensure voltages to the card-side track within specified parametric limits, and provide status information to a host processor.

The SMT4004A incorporates nonvolatile programmable circuits for setting all monitored thresholds for each manager. Individual functions are also programmable allowing Interrupts or Reset conditions to be generated by many combinations of events. Also included are nonvolatile fault status registers and a 2K-bit (256 byte) nonvolatile memory.

User programming of configuration and control values is simplified with the interface adapter (SMX3200) and Windows GUI software obtainable from Summit Microelectronics.

1

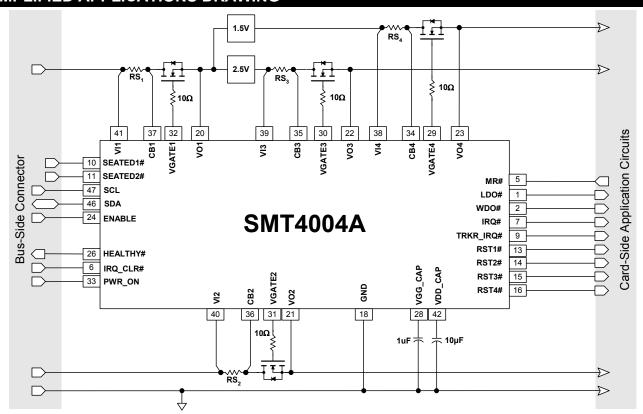

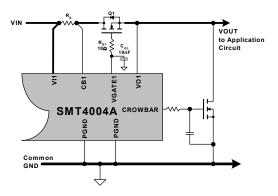

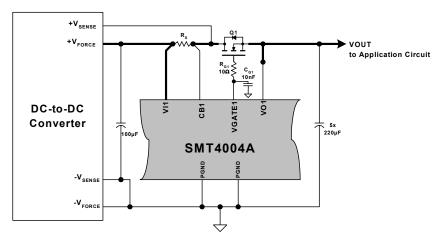

# SIMPLIFIED APPLICATIONS DRAWING

Note: This is an applications example only. Some pins, components and values are not shown.

© Summit Microelectronics, Inc. 2003 • 300 Orchard City Drive, #131 • Campbell CA 95008 • Phone 408 378-6461 • FAX 408 378-6586 • www.summitmicro.com

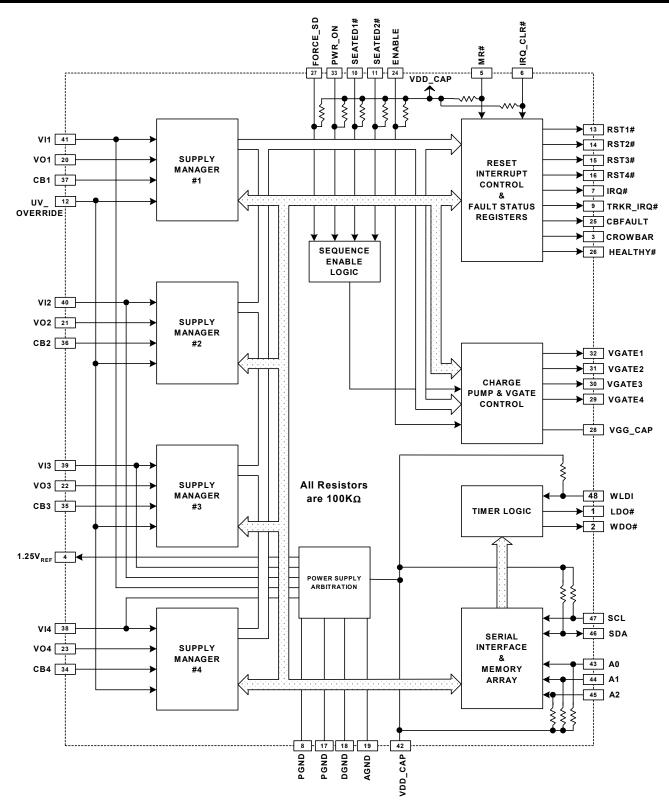

# **DETAILED DEVICE DESCRIPTION**

#### **SUPPLY MANAGERS**

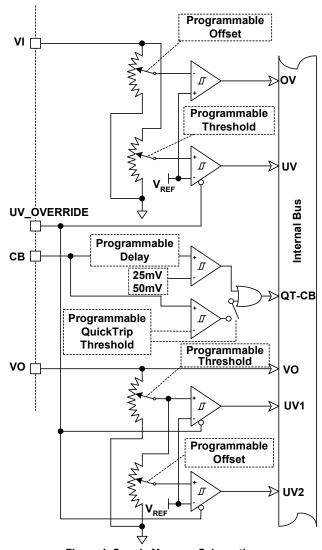

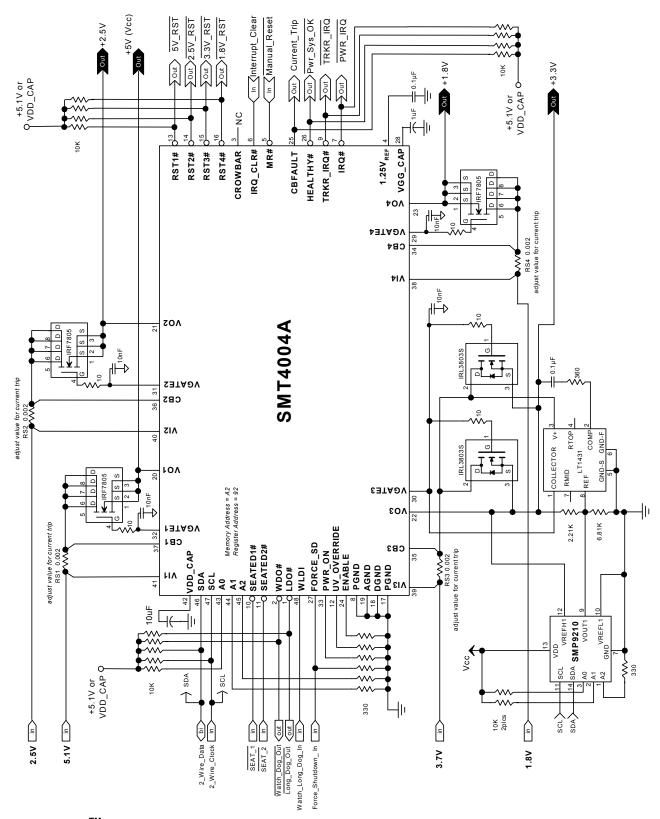

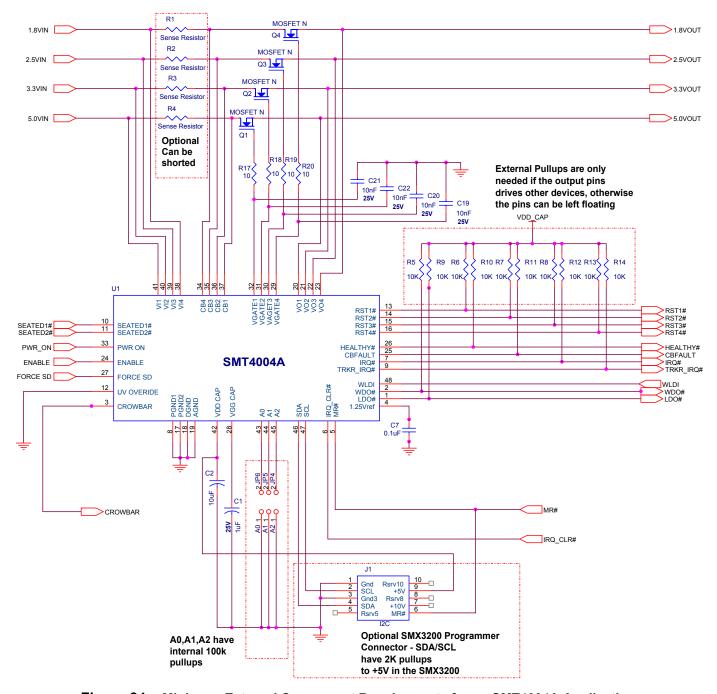

The SMT4004A has four distinct programmable power supply managers and associated circuitry (see Figure 7). The managers are individually programmable and can operate independently or together with the other managers. Each manager monitors the bus and cardside voltages and current for that supply (Figure 1). The VI pin is the bus-side input that connects to two comparators to monitor under-voltage (UV) and overvoltage conditions (OV). The threshold for the UV detector is programmable in 20mV increments, from 0.9V to 6.0V. The OV detector is programmable in 4% increments of the UV settings, from 120% to 244% of the UV settings. The OV threshold is an offset from the UV sensor and the offset varies as the UV threshold: if UV is set to 0.9V then OV can be set from 1.08 to 2.2V.

The OV setting is related to the UV setting according to the formula:

$$OV = UV X [(0.04 \times DecVal) + 1.2]$$

Where: OV = Bus-side Over-voltage setting, UV = Bus-side Under-voltage setting, and DecVal = Decimal value of OV Register contents.

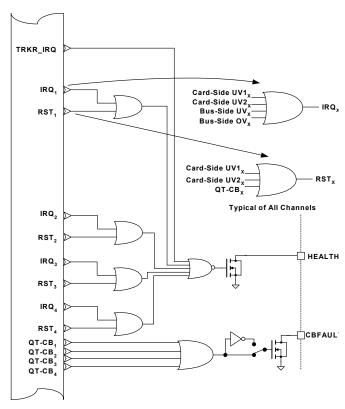

If the VI input is below the UV threshold the manager generates a UV fault status on the internal bus. If the VI input is above the OV threshold the manager generates an OV fault status on the internal bus. The UV and OV status information can be selected to generate an IRQ# output. Refer to Figure 3 for an illustration of the IRQ# function and the relation of the UV and OV status of the four managers.

The VO pin is the card-side input that connects to two comparators to monitor two under-voltage threshold conditions. The threshold for the first under-voltage monitor (UV1) is programmable in 20mV increments, from 0.9V to 6.0V. If the VO input is below the UV1 threshold the manager generates an UV1 fault status on the internal bus.

The threshold for the second under-voltage monitor can be set equal to the UV1 threshold or to one of 31 values less than UV1. The UV2 setting is related to the UV1 setting according to the formula:

UV2 = UV1 X [1-(0.01 X DecVal)]

Where: UV1 = Card-side primary Under-voltage setting, UV2 = Card-side secondary Under-voltage setting, and DecVal = Decimal value of UV2 Register contents (last 5 LSBs).

If the VO input is below the UV2 threshold the manager generates an UV2 fault status on the internal bus. Generally the first threshold, UV1, is used to provide a warning that the supply is deteriorating while the second threshold, UV2, is set lower to indicate the supply is out of the operating range. The UV1 and UV2 status outputs from the manager can be programmed to generate a Reset or an Interrupt.

Figure 1. Supply Manager Schematic.

The UV\_OVERRIDE input is used to mask undervoltage conditions. When asserted (high) all undervoltage conditions are ignored. This function is used either during system test or when performing voltage margin tests. During normal operation this pin must be connected to ground.

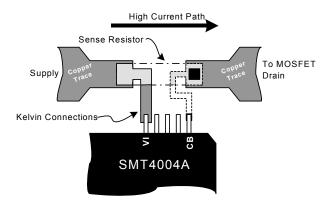

CB is the circuit breaker input. A series resistor placed between VI and CB causes the circuit breaker to trip when the voltage across the resistor exceeds the programmed value of 25mV or 50mV ( $V_{CB}$ ). A programmable filter is provided to allow voltage drops greater than  $V_{CB}$  for selected delays of 25µs, 50µs, 100µs or 200µs. If the filter time is exceeded an overcurrent condition (QT-CB) is generated from the manager.

The CB pin is also connected to the QuickTrip comparator. It is used in conjunction with the circuit breaker function or may be disabled. When enabled, a voltage across the series resistor exceeding the QuickTrip threshold ( $V_{\rm QT}$ ) instantly generates a QT-CB signal from the manager.  $V_{\rm QT}$  can be set to different levels depending on the CB selection. See  $V_{\rm QT}$  page 13.

The QT-OC output from the manager can generate a RST# (Figure 2), an IRQ#, (Figure 3) or an internal force shutdown (FSD) and crowbar output (Figure 5).

#### **DEVICE POWER SUPPLY**

The VI inputs also provide the operating supply voltage for the SMT4004A. Internally they are diode-ORed, so the highest potential VI input becomes the VDD supply. Refer to the functional Block Diagram on page 8.

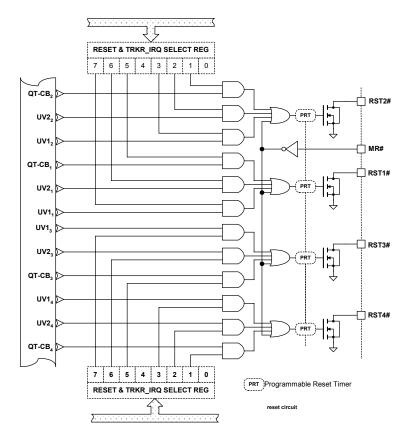

#### RESET CIRCUIT

The SMT4004A has four active-low, open-drain Reset pins (RST1# - RST4#). All RST# outputs are asserted once power is applied; remaining asserted for  $t_{\text{PRTO}}$  (programmable reset timeout period, Figure 10) after all Reset generating conditions are removed.

Individual RST# outputs can be programmed to become active from three manager status conditions: UV1, UV2 or QT-CB. The RST# output remains active for  $t_{\text{PRTO}}$  after the fault condition is removed (Figure 2). Asserting the Manual Reset input (MR# low) forces all RST# outputs low. The RST# outputs remain low while MR# is low, returning high  $t_{\text{PRTO}}$  seconds after MR# is de-asserted.

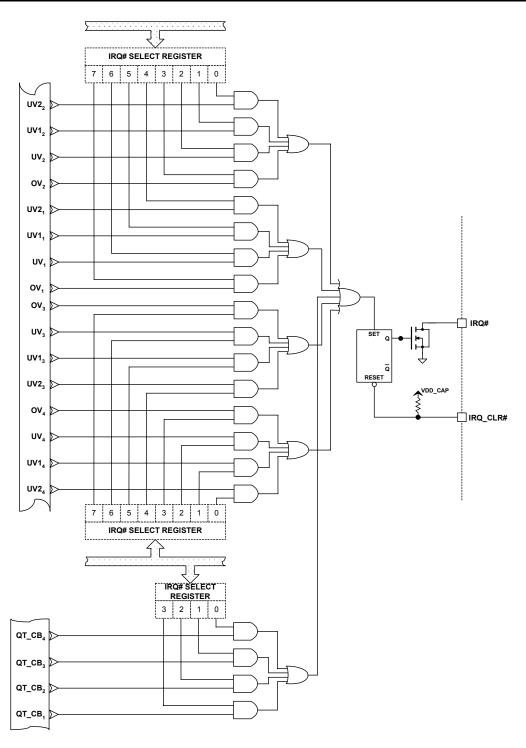

#### INTERRUPT (IRQ#) CIRCUIT

The SMT4004A has an active-low open-drain IRQ# output. The sources for triggering an interrupt are selected from the UV, OV, UV1 and UV2 status outputs of each manager. When asserted, IRQ# is latched and can only be cleared by a high to low transition on the IRQ CLR# pin (Figure 3).

Figure 2. Programmable and hard-wired sources for generating resets.

Figure 3. Interrupt sources from the SMT4004A supply managers.

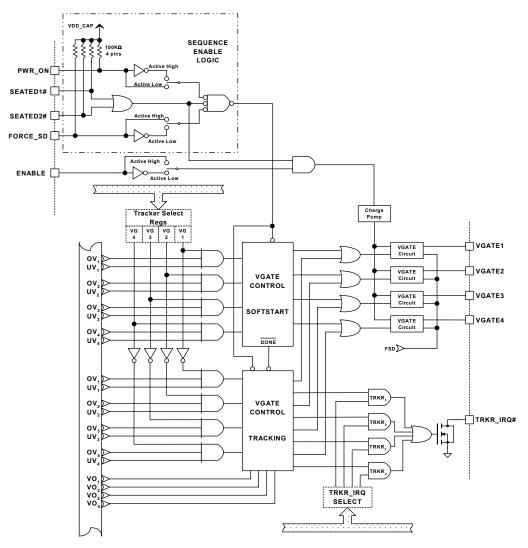

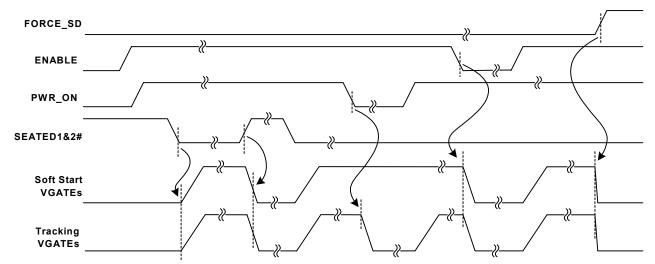

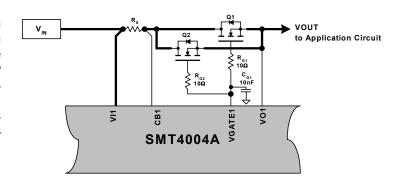

#### **CHARGE PUMP AND VGATE CONTROL**

The VGATE outputs control the gate voltages of external N-channel MOSFETs. Each MOSFET separates the bus and card-side voltages. The VGATE outputs control the card-side slew rates during the power-on/-off interval. The VGATEs are turned on when their controlling inputs either meet softstart conditions or when tracking conditions are met so the MOSFET card-side voltages track. The manager inputs (Figure 1) and the control inputs (Figure 4) control the VGATE outputs.

Certain conditions must be met for the VGATE outputs to become active. The conditions are defined by the sequence enable logic, the manager inputs and the user selected function (softstart or track) for each VGATE output.

The VGATE control blocks (Figure 4) are the logic functions controlling the VGATE outputs. All inputs to these blocks are used to enable the VGATE outputs to drive the external MOSFETs.

The ENABLE input only affects the charge pump (VGG\_CAP voltage). Its active state is programmable and must be true to turn-on the charge pump. The charge pump provides the high-side drive voltage to the VGATE pins.

The PWR\_ON and FORCE\_SD inputs active states are programmable. PWR\_ON, SEATED1# and SEATED2# must be true and FORCE\_SD false to enable a power-on sequence.

Figure 4. Charge Pump and VGATE Control

If both softstart and tracking are enabled, the softstart VGATE outputs must be fully on (VGATE = VGG\_CAP) before the tracking VGATEs are enabled.

The VO inputs are monitored and compared by the tracking logic to control the VGATEs of the tracked voltages. They are also used by the VGATE tracking control logic to generate a TRKR\_IRQ# output if a differential of >300mV between any tracked VO input occurs during the tracking interval.

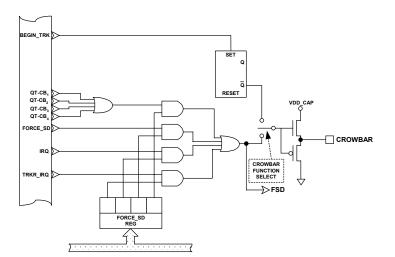

#### FORCE SHUTDOWN AND CROWBAR

The VGATE outputs can be rapidly shutdown by asserting the FORCE\_SD input or when an internally generated force shutdown (FSD) occurs.

Internal sources that generate a force shutdown are programmable and are: a TRKR\_IRQ#, a general IRQ# or an over-current condition (QT-CB) (Figure 5).

#### **HEALTHY# AND CBFAULT**

The SMT4004A has two status output pins, HEALTHY# and CBFAULT (Figure 6). HEALTHY# is an active-low open-drain output that is asserted when all bus and card-side conditions are within the programmed settings, *i.e.*, there must be no bus or card-side fault conditions (programmed RST#s, IRQ#s, or TRKR\_IRQ#s) from the bus-side UV, OV and card-side UV1, UV2 and QT-CB outputs from the managers. If no RST#s, IRQ#s, or TRKR\_IRQ#s are enabled, HEALTHY# will stay asserted even if fault conditions exist. HEALTHY# is an instantaneous indication of the status of the RST#s, IRQ#, and TRKR\_IRQ# signals, and is derived from the unlatched versions of these signals. The CBFAULT is programmable as an active high or active low output.

Figure 5. Force Shutdown (FSD) and CROWBAR circuitry.

It is asserted when an over-current condition (QT-CB) occurs (Figure 6).

Figure 6. HEALTHY# and CBFAULT circuitry. FAULT STATUS REGISTERS

The SMT4004A has three nonvolatile fault status registers. When an IRQ# is generated the cause of the interrupt is recorded in the fault register. The fault source is indicated as a '1' in the assigned bit location (Table 1). The fault status registers are overwritten each time an IRQ# is generated. The fault status registers are always available for reading except for when a nonvolatile write is in progress. Overwriting (clearing) the fault condition is dependent upon the device configuration with regard to the programmable 'active writing state' of the MR# input. Clearing the fault status registers is not necessary as the last fault condition overwrites any information previously stored. If clearing the registers is desired, it is accomplished by forcing a write to those registers while no fault conditions exist.

For prototyping purposes, the Windows GUI (described in the Serial Interface section) has an option to clear the fault status registers.

Fault recording is disabled when the PWR\_ON input is de-asserted.

| Fault Status Register Address 1D |                 |     |     |                 |                 |                 |                 |

|----------------------------------|-----------------|-----|-----|-----------------|-----------------|-----------------|-----------------|

| 7                                | 6               | 5   | 4   | 3               | 2               | 1               | 0               |

| UV₁                              | UV <sub>2</sub> | UV₃ | UV₄ | 0V <sub>1</sub> | 0V <sub>2</sub> | 0V <sub>3</sub> | 0V <sub>4</sub> |

| Fault Status Register Address 1E |                  |       |     |       |                  |      |      |

|----------------------------------|------------------|-------|-----|-------|------------------|------|------|

| 7                                | 6                | 5     | 4   | 3     | 2                | 1    | 0    |

| UV1,                             | UV1 <sub>2</sub> | 1۸۱ ، | ۱۸۸ | ¹0N5¹ | UV2 <sub>2</sub> | UV23 | UV2, |

| Fault Status Register Address 1F |                   |       |       |        |        |        |        |

|----------------------------------|-------------------|-------|-------|--------|--------|--------|--------|

| 7                                | 6                 | 5     | 4     | 3      | 2      | 1      | 0      |

| TRKR,                            | TRKR <sub>2</sub> | TRKR3 | TRKR4 | QT-CB, | QT-CB2 | QT-CB3 | QT-CB4 |

Table 1. Fault Status register bit allocation

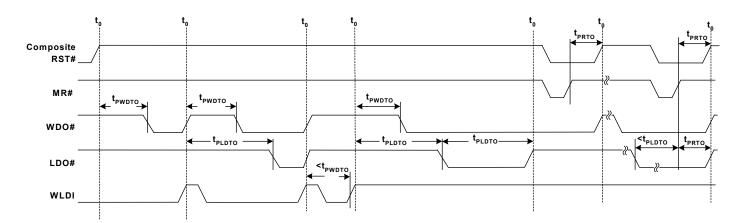

#### **WATCHDOG AND LONGDOG TIMERS**

The SMT4004A's internal timer triggers the activation of the LDO# and WDO# outputs. LDO# and WDO# are active-low open-drain outputs that can be wire-ORed with other open-drain signals.

During a power-on sequence the timers are disabled until all four Resets are released. At this time both timers, if enabled, begin clocking at  $t_0$ . If either times out, it asserts its respective output. The timers work in tandem, so any low to high transition on the WLDI input Resets both timers to  $t_0$ .

The longdog timer must be programmed to timeout sometime after the watchdog timer. The WDO# could then be wire-ORed with the IRQ# output to provide an

alert that action needs to be taken. The LDO# output could be wire-ORed with a system RST# signal to indicate a shutdown condition exists.

Both timers can be programmed off, facilitating system debug. This feature can also be used to allow an operating system to boot-up and configure itself without Interrupts or Resets.

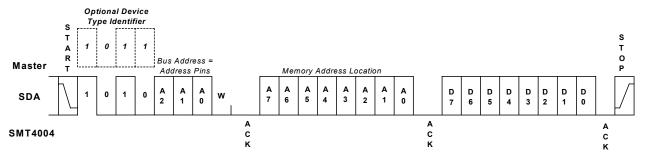

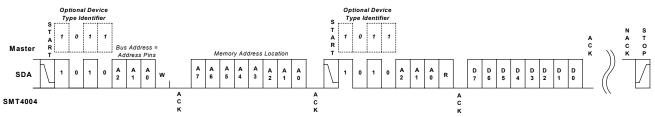

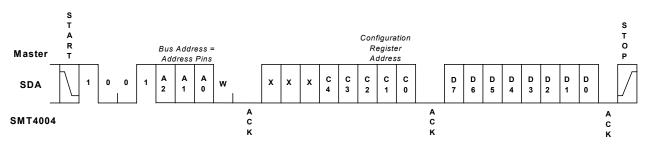

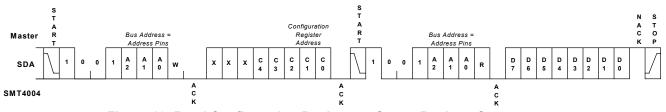

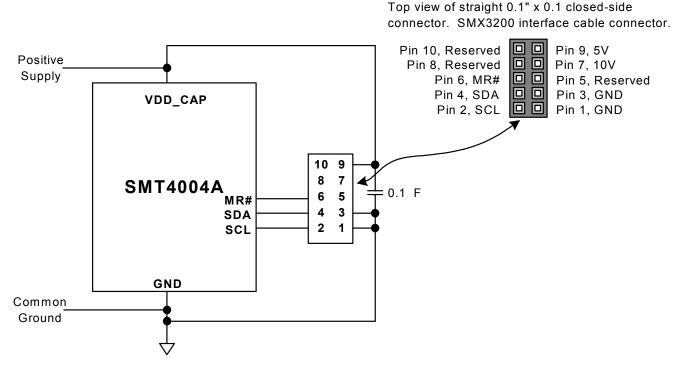

# SERIAL INTERFACE AND GENERAL PURPOSE EEPROM MEMORY ARRAY

The SMT4004A uses the industry standard I<sup>2</sup>C 2-wire serial data interface. This interface provides access to the configuration registers, the nonvolatile fault registers and a 2K-bit (256 byte) nonvolatile memory. The interface has three address inputs (A0, A1, and A2) allowing up to eight devices on the same bus. This allows multiple devices on the same board or multiple boards in a system to be controlled with two signals: SDA and SCL.

The configuration and nonvolatile fault registers share the same device type identifier,  $1001_{\text{BIN}}$ , which is distinct from the 2K-memory device type identifier, optionally  $1010_{\text{BIN}}$  or  $1011_{\text{BIN}}$ . The separation of address space allows full utilization of the EEPROM memory array. The memory is functionally identical to the industry standard 24C02. However, the last 48-bytes in the memory array are reserved for test purposes.

The memory array can be read with MR# low. The memory array cannot be written when the part is in reset whether from MR# being low or from any other reset source. The configuration and fault registers may be read regardless of the state of MR#. A user option selects the active state of the MR# input for writing to the configuration and fault registers.

Device configuration utilizing the Windows based SMT4004A graphical user interface (GUI) is highly recommended. The software is available from the Summit website (www.summitmicro.com). Using the GUI in conjunction with this datasheet and Application Note 22 simplifies the process of device prototyping and the interaction of the various functional blocks. A programming Dongle (SMX3200) is available from Summit to communicate with the SMT4004A. The Dongle connects directly to the parallel port of a PC and programs the device through a cable using the I<sup>2</sup>C bus protocol.

# INTERNAL BLOCK DIAGRAM

Figure 7. SMT4004A Internal Block Diagram.

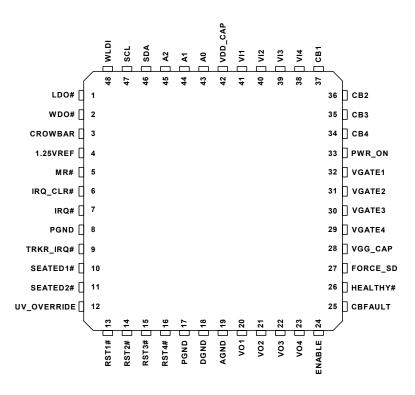

# **PIN DESCRIPTIONS**

| O O P        | LDO# WDO# CROWBAR      | The longdog timer output is an active low open-drain output. It is driven low when the longdog timer has timed out.  The watchdog timer output is an active low open-drain output. It is driven low when the watchdog timer has timed out.  CROWBAR is an active high totem pole output. It is a programmable output; it can act as a CROWBAR output or as an Early-Voltage-Drive (EVD) output. As a CROWBAR it generates a short duration (≈20µs) positive pulse generally used to trigger an external SCR. The sources for initiating the |

|--------------|------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|              |                        | when the watchdog timer has timed out.  CROWBAR is an active high totem pole output. It is a programmable output; it can act as a CROWBAR output or as an Early-Voltage-Drive (EVD) output. As a CROWBAR it generates a short duration (≈20µs) positive pulse                                                                                                                                                                                                                                                                               |

| OP           | CROWBAR                | it can act as a CROWBAR output or as an Early-Voltage-Drive (EVD) output.<br>As a CROWBAR it generates a short duration (≈20µs) positive pulse                                                                                                                                                                                                                                                                                                                                                                                              |

|              |                        | pulse are user selectable and are illustrated in Figure 5. As an EVD output, the pin is held high until the SMT4004A begins tracking, allowing an external MOSFET to discharge any residual voltages on the card-side power rails.                                                                                                                                                                                                                                                                                                          |

| PWR<br>(out) | 1.25V <sub>REF</sub>   | The $1.25V_{REF}$ pin provides a $1.25V$ reference output voltage. It requires a $0.1\mu F$ bypass capacitor to AGND (pin 19).                                                                                                                                                                                                                                                                                                                                                                                                              |

| I            | MR#                    | The MR# (manual Reset) pin is an active low input. When MR# is driven low, the RST1# through RST4# pins are driven low and stay low while MR# is asserted. After MR# returns high, the Reset outputs remain low for $t_{\text{PRTO}}$ . Asserting MR# also resets the watchdog and longdog timers to $t_0$ after the expiration of $t_{\text{PRTO}}$ . The MR# pin is internally pulled-up to VDD_CAP with a $100 \text{K}\Omega$ resistor.                                                                                                 |

| ı            | IRQ_CLR#               | The IRQ_CLR# pin is an active low input. A low on IRQ_CLR# clears any active IRQ#. As long as IRQ_CLR# is held low, IRQ#s are blocked. The IRQ_CLR# pin is internally pulled-up to VDD_CAP with a $100$ K $\Omega$ resistor.                                                                                                                                                                                                                                                                                                                |

| 0            | IRQ#                   | The IRQ# is an active low open-drain output. It is driven low when one or more of its programmable triggers are active. The programmable trigger sources are illustrated in Figure 3.                                                                                                                                                                                                                                                                                                                                                       |

| PWR          | PGND                   | PGND is the ground for the power portion of the internal circuitry. It is internally tied to pin 17. Both pins must be tied to system ground.                                                                                                                                                                                                                                                                                                                                                                                               |

| 0            | TRKR_IRQ#              | TRKR_IRQ# is an active low open-drain output. It is driven low when one or more of its programmable triggers are active. The programmable trigger sources are tracking errors detected by the managers and are illustrated in Figure 4.                                                                                                                                                                                                                                                                                                     |

| ı            | SEATED1#               | The SEATED# inputs are effectively enable inputs. Both must be low for the power-on sequence to proceed. In applications utilizing staggered pin                                                                                                                                                                                                                                                                                                                                                                                            |

| ı            | SEATED2#               | lengths the SEATED# inputs should be tied to the short pins. Internally these pins are pulled-up to VDD_CAP with $100 \text{K}\Omega$ resistors.                                                                                                                                                                                                                                                                                                                                                                                            |

| I            | UV_OVERRIDE            | The UV_OVERRIDE pin is an active high input. When asserted, the UV comparators are disabled (Figure 1). Internally this pin is pulled-up to VDD_CAP with a $100 \text{K}\Omega$ resistor. This pin must be low for normal operation.                                                                                                                                                                                                                                                                                                        |

|              | (out)  I  O  PWR  O  I | I MR#  I IRQ_CLR#  O IRQ#  PWR PGND  O TRKR_IRQ#  I SEATED1#                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

# PIN DESCRIPTIONS (CONTINUED)

| Pin<br>Number | Pin<br>Type    | Pin Name | Description                                                                                                                                                                                                                                                         |  |  |  |  |

|---------------|----------------|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 13            | 0              | RST1#    | The RST# outputs are active low open-drain outputs. The supply manager                                                                                                                                                                                              |  |  |  |  |

| 14            | 0              | RST2#    | trigger source for each Reset output is individually programmable and is illustrated in Figure 2. Each output remains low until the fault is removed and                                                                                                            |  |  |  |  |

| 15            | 0              | RST3#    | t <sub>PRTO</sub> has expired. All Reset outputs are driven low when the MR# input is asserted; remaining low while MR# is asserted, and for t <sub>PRTO</sub> after MR# is                                                                                         |  |  |  |  |

| 16            | 0              | RST4#    | released.                                                                                                                                                                                                                                                           |  |  |  |  |

| 17            | PWR            | PGND     | PGND is the ground for the power portion of the internal circuitry. It is internally tied to pin 8. Both pins must be tied to system ground.                                                                                                                        |  |  |  |  |

| 18            | PWR            | DGND     | DGND is the ground for the digital portion of the internal circuitry. It must be tied to system ground.                                                                                                                                                             |  |  |  |  |

| 19            | PWR            | AGND     | AGND is the ground for the analog portion of the internal circuitry. It must be tied to system ground.                                                                                                                                                              |  |  |  |  |

| 20            | 1              | VO1      |                                                                                                                                                                                                                                                                     |  |  |  |  |

| 21            | I              | VO2      | The VO inputs are used to monitor the card-side voltages for the individual                                                                                                                                                                                         |  |  |  |  |

| 22            | I              | VO3      | managers.                                                                                                                                                                                                                                                           |  |  |  |  |

| 23            | I              | VO4      |                                                                                                                                                                                                                                                                     |  |  |  |  |

| 24            | l <sup>P</sup> | ENABLE   | ENABLE is an input with a programmable active true state. When the input is true the charge pump that supplies the high side drive voltage for the VGATE outputs is turned on. The ENABLE input is internally tied to VDD_CAP with a $100 \text{K}\Omega$ resistor. |  |  |  |  |

| 25            | O <sup>P</sup> | CBFAULT  | CBFAULT is an output with a programmable true state. CBFAULT is asserted when there is an over-current condition (QT-CB).                                                                                                                                           |  |  |  |  |

| 26            | 0              | HEALTHY# | HEALTHY# is an unlatched active-low open-drain output. It is asserted when all four managers report no bus-side over-voltages (OV), under-voltages (UV) or card-side under-voltages (UV1 or UV2) or over-current (QT-CB) conditions. See Figure 6.                  |  |  |  |  |

| 27            | <u>P</u>       | FORCE_SD | FORCE_SD is an input with a programmable active true state. When the input is true the VGATE outputs are immediately turned off and clamped to ground. The FORCE_SD input is internally tied to VDD_CAP with a $100 \text{K}\Omega$ resistor.                       |  |  |  |  |

| 28            | PWR            | VGG_CAP  | VGG_CAP is a charge storage connection for the SMT4004A internal charge pump. A $1\mu F$ capacitor rated above 16V is recommended for most applications.                                                                                                            |  |  |  |  |

| 29            | 0              | VGATE4   | The VOATE culturate are used to control the time are of the send side as the                                                                                                                                                                                        |  |  |  |  |

| 30            | 0              | VGATE3   | The VGATE outputs are used to control the turn-on of the card-side voltages by providing a high side voltage to a power MOSFET. The fully on output                                                                                                                 |  |  |  |  |

| 31            | 0              | VGATE2   | voltage is 14.5V.                                                                                                                                                                                                                                                   |  |  |  |  |

| 32            | 0              | VGATE1   | Vollage is 14.5V.                                                                                                                                                                                                                                                   |  |  |  |  |

32 | O | VGATE1 |

Note: Endicates the pin's function or the active state of the pin is programmable.

# PIN DESCRIPTIONS (CONTINUED)

| Pin<br>Number | Pin<br>Type | Pin Name  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |  |

|---------------|-------------|-----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| 33            | I           | PWR_ON    | PWR_ON is an input with a programmable active true state. It must be true for the SMT4004A to begin turning on the VGATE outputs. The PWR_ON input is internally tied to VDD_CAP with a $100 \mathrm{K}\Omega$ resistor. Once the power-on operation is complete, de-asserting the PWR_ON input forces the tracked channels to track down. The channels programmed for softstart are unaffected and their respective VGATE outputs remain active. |  |  |  |  |

| 34            | 1           | CB4       | ·                                                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |

| 35            | I           | CB3       | CB1 through CB4 are inputs monitoring a voltage drop across an external                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |  |

| 36            |             |           | sense resistor placed between the respective VI and CB inputs.                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |

| 37            | I           | CB1       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 38            | I/PWR       | VI4       |                                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 39            | I/PWR       | VI3       | The VI inputs provide two functions. They are primarily the bus-side (unswitched) voltage monitoring inputs for the individual supply managers.                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 40            | I/PWR       | VI2       | Additionally, they are internally diode-ORed to provide the SMT4004A's VDD CAP supply.                                                                                                                                                                                                                                                                                                                                                            |  |  |  |  |

| 41            | I/PWR       | VI1       | VDD_0/W ddppiy.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |

| 42            | PWR         | VDD_CAP   | VDD_CAP is a charge storage connection to the SMT4004A's internal power supply. For most applications this pin is tied to a 10µF capacitor to ground.                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 43            | 1           | Α0        | The address pins are biased either to VDD_CAP or GND and provide a                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |

| 44            | I           | <b>A1</b> | mechanism for assigning a unique I <sup>2</sup> C serial bus address to the SMT4004A.                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |

| 45            | I           | A2        | These pins are internally pulled-up to VDD_CAP with 100K $\Omega$ resistors.                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |

| 46            | I/O         | SDA       | SDA is the bidirectional serial data pin. This pin is internally pulled-up to VDD_CAP with 100K $\Omega$ resistor. SDA is configured as an open-drain output and requires a pull-up resistor to the highest VDD of the I <sup>2</sup> C system for proper operation.                                                                                                                                                                              |  |  |  |  |

| 47            | I           | SCL       | SCL is the serial clock input, used for clocking data into or out of the SMT4004A. This pin is internally pulled-up to VDD_CAP with 100K $\Omega$ resistor. SCL is configured as an open-drain output and requires a pull-up resistor to the highest VDD of the I $^2$ C system for proper operation.                                                                                                                                             |  |  |  |  |

| 48            | I           | WLDI      | WLDI is an input. A low-to-high transition on this pin resets both the watchdog and longdog timers to $t_0$ . If the WLDI input is held high, WDO# is disabled while the LDO# output remains active. The WLDI input is internally tied to VDD_CAP through a $100 \text{K}\Omega$ resistor.                                                                                                                                                        |  |  |  |  |

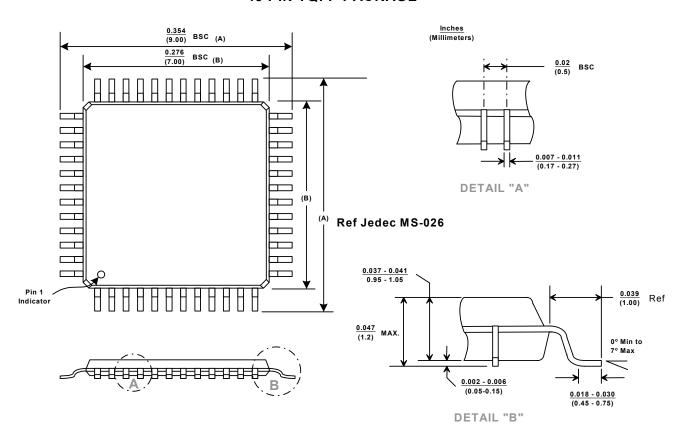

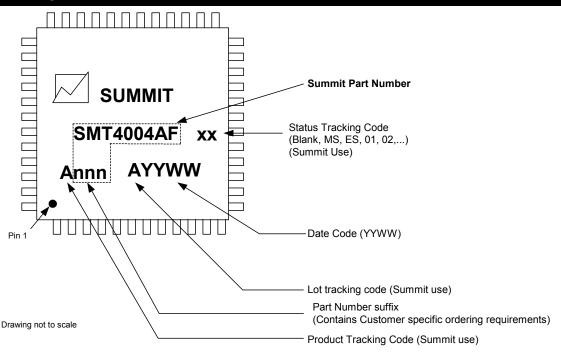

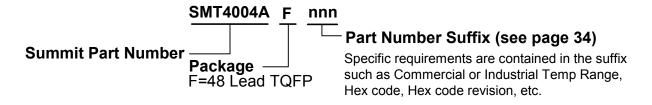

## PACKAGE AND PIN CONFIGURATION

#### 48 Lead TQFP

## **ABSOLUTE MAXIMUM RATINGS**

| Temperature Under Bias55°C to +125°C    |

|-----------------------------------------|

| Storage Temperature65°C to +150°C       |

| Terminal Voltage with Respect to GND:   |

| VI & VO Inputs                          |

| VGATE, VGG_CAP Outputs16V               |

| All Others                              |

| Output Short Circuit Current 100mA      |

| Lead Solder Temperature (10 secs) 300°C |

| Junction Temperature 150°C              |

| ESD Rating per JEDEC 2000V              |

| Latch-Up testing per JEDEC ± 100mA      |

Stresses listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions outside those listed in the operational sections of the specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability. Devices are ESD sensitive. Handling precautions are recommended.

## **RECOMMENDED OPERATING CONDITIONS**

| Temperature Range (Industrial)40°C to +85°C            |

|--------------------------------------------------------|

| (Commercial) –5°C to +70°C                             |

| Supply Voltage 2.7V to 6.0V <sup>1/</sup>              |

| Package Thermal Resistance (θ JA)                      |

| 48 Lead TQFP 80°C/W                                    |

| Moisture Classification Level 1 (MSL 1) per J-STD- 020 |

Notes: 1/ For reliable operation the VDD\_CAP node voltage must be equal to or greater than 2.7V (voltage level measured on pin 42).

#### **RELIABILITY CHARACTERISTICS**

| Data Retention | 100 Years     |

|----------------|---------------|

| Endurance 1    | 00,000 Cycles |

Note: Accuracy data is stored in pages 13-15 of the EEPROM memory array. Erasure of this data will render the SMT4004A GUI unusable. Loss of this data will not alter preset UV/OV trip points.

# **SMT4004A**

## DC OPERATING CHARACTERISTICS

(Over recommended operating conditions, unless otherwise noted. All voltages are relative to GND.)

| Symbol                 | Parameter                                         | Condition                                                     | ıs         | Min.                     | Тур.                | Max                      | Unit |

|------------------------|---------------------------------------------------|---------------------------------------------------------------|------------|--------------------------|---------------------|--------------------------|------|

| V <sub>SUPPLY</sub>    | Power Supply Voltage                              | Device sup<br>provided by<br>highest VIX                      |            | 2.7                      |                     | 6.0                      | V    |

| vx                     | Monitoring Voltage<br>VI1-VI4, VO1-VO4            | Note <u>1</u> /                                               |            | 0                        |                     | 6.54                     | V    |

| I <sub>DD</sub>        | Power Supply Current                              | VGATE Ou<br>enabled, w<br>memory ar                           |            |                          |                     | 5                        | mA   |

| PVIT <sub>UV</sub>     | Programmable VI<br>Threshold for UV condition     | See explar<br>page 2                                          |            | 0.9                      |                     | 6.0                      | V    |

| PVIT <sub>ov</sub>     | Programmable VI<br>Threshold for OV condition     | See explanation on                                            |            | 1.08                     |                     | 6.6                      | ٧    |

| PVIT <sub>HYS</sub>    | OV/UV trip hysteresis                             |                                                               |            |                          | 10                  |                          | mV   |

| PVIT <sub>UVACC</sub>  | Programmable UV<br>Threshold Accuracy             | Note <u>3</u> /                                               |            | 0.99xPVIT <sub>UV</sub>  | PVIT <sub>UV</sub>  | 1.01xPVIT <sub>UV</sub>  | V    |

| PVITOVACC              | Programmable OV<br>Threshold Accuracy             | Note <u>3</u> /                                               |            | 0.99xPVIT <sub>OV</sub>  | PVIT <sub>OV</sub>  | 1.01xPVIT <sub>OV</sub>  | ٧    |

| PVOT <sub>UV1</sub>    | Programmable VO<br>Threshold for UV1<br>condition | See explanation on page 2                                     |            | 0.9                      |                     | 6.0                      | V    |

| PVOT <sub>UV2</sub>    | Programmable VO<br>Threshold for UV2<br>condition | Note 3/  See explanation on page 2  See explanation on page 2 |            | 0.69xPVOT <sub>UV1</sub> |                     | PVOT <sub>UV1</sub>      | V    |

| PVOT <sub>UV1ACC</sub> | Programmable UV1<br>Threshold Accuracy            |                                                               |            | 0.99xPVOT <sub>UV1</sub> | PVOT <sub>UV1</sub> | 1.01xPVOT <sub>UV1</sub> | V    |

| PVOT <sub>UV2ACC</sub> | Programmable UV2<br>Threshold Accuracy            |                                                               |            | 0.95xPVOT <sub>UV2</sub> | PVOT <sub>UV2</sub> | 1.05xPVOT <sub>UV2</sub> | ٧    |

| V                      | Programmable circuit                              | CB Trip Po                                                    | int = 25mV | 19                       | 25                  | 31                       | mV   |

| V <sub>CB</sub>        | breaker trip voltage                              | CB Trip Po                                                    | int = 50mV | 37                       | 50                  | 62                       | mV   |

|                        |                                                   | CB=25mV                                                       | QT=55mV    | 40                       | 55                  | 70                       | mV   |

|                        |                                                   | CB=50mV                                                       | QT=80mV    | 60                       | 80                  | 100                      | mV   |

| $V_{QT}$               | Programmable Quick Trip                           | CB=25mV                                                       | QT=85mV    | 65                       | 85                  | 105                      | mV   |

| - <b>Q</b> I           | Threshold Voltage                                 | CB=50mV                                                       | QT=110mV   | 80                       | 110                 | 140                      | mV   |

|                        |                                                   | CB=25mV                                                       | QT=135mV   | 100                      | 135                 | 170                      | mV   |

|                        |                                                   | CB=50mV                                                       | QT=160mV   | 120                      | 160                 | 200                      | mV   |

Notes:

1/ VX is the entire operating range of the VIX and VOX input pins. Any of these inputs can be at ground potential.

Does not include external load on VDD\_CAP. Any external pull-up resistors tied to VDD\_CAP will increase I<sub>DD</sub>. Maximum allowable external current sourced from VDD\_CAP is 1mA with VDD\_CAP=10µF.

<sup>3/ 1%</sup> accuracy can be achieved for either bus-side UV or bus-side OV, but not both. This is due to the relationship between OV and UV settings noted on page 2 of this data sheet. However, a 1% accuracy is achieved when monitoring bus-side OV and card-side UV1. To obtain this accuracy, OV is set to the minimum setting (decimal value = 0) and adjusted with the UV setting to reach the desired 1% OV trip point. Accuracy data is stored in pages 13-15 of the EEPROM memory array. Erasure of this data will render the SMT4004A GUI unusable. Loss of this data will not alter preset UV/OV trip points.

# **SMT4004A**

# DC OPERATING CHARACTERISTICS (CONTINUED)

(Over recommended operating conditions, unless otherwise noted. All voltages are relative to GND.)

| Symbol                 | Parameter                                      | Conditions                                           | Min.        | Тур. | Max                       | Unit |

|------------------------|------------------------------------------------|------------------------------------------------------|-------------|------|---------------------------|------|

| V <sub>VGATE</sub>     | VGATE drive output                             | ON ( I <sub>VGATE</sub> = 4µA)<br>- Note <u>4</u> /  | 12          |      | 16                        | ٧    |

| VGATE                  | VGATE drive output                             | OFF (I <sub>VGATE</sub> = -8mA)<br>- Note <u>4</u> / | 0           |      | 0.4                       | >    |

| L                      | Total VGATE output drive                       | All VGATEs forced to 10V - Note 4/                   | 10          |      |                           | μΑ   |

| I <sub>VGATE</sub>     | current                                        | All VGATEs forced to 1V - Note 4/                    | 30          |      |                           | μΑ   |

|                        |                                                | <b>SR</b> <sub>VOX</sub> = 100V/s                    | 60          | 100  | 140                       | V/s  |

| SR <sub>vox</sub>      | Tracking VOX Slew Rate                         | <b>SR</b> <sub>VOX</sub> = 250V/s                    | 150         | 250  | 350                       | V/s  |

| SKVOX                  | Tracking VOX Siew Nate                         | <b>SR</b> <sub>VOX</sub> = 500V/s                    | 400         | 500  | 600                       | V/s  |

|                        |                                                | <b>SR</b> <sub>VOX</sub> = 1000V/s                   | 800         | 1000 | 1200                      | V/s  |

| V <sub>TRKR</sub>      | Tracking Differential Voltage                  | Differential between Tracking VOX pins - Note 5/     |             | 100  | 250                       | mV   |

| V <sub>TRKR_IRQ#</sub> | Tracking Differential Voltage Causes TRKR_IRQ# | Differential between<br>Tracking VOX pins            |             | 300  |                           | mV   |

| V <sub>REF</sub>       | 1.25VREF Output Voltage                        | $R_{LOAD} = 2K\Omega$ to gnd                         | 1.23        | 1.25 | 1.27                      | V    |

|                        | Innut High Voltogo                             | VDD_CAP = 2.7V to<br>4.5V                            | 0.9xVDD_CAP |      | 6.0                       | V    |

| V <sub>IH</sub>        | Input High Voltage                             | VDD_CAP = 4.5V to 6.0V                               | 0.7xVDD_CAP |      | 6.0                       | V    |

| V                      | Input Low Voltage                              | VDD_CAP = 2.7V to<br>4.5V                            | -0.1        |      | 0.1xVDD_CAP               | V    |

| V <sub>IL</sub>        | Input Low Voltage                              | VDD_CAP = 4.5V to 6.0V                               | -0.1        |      | 250<br>1.27<br>6.0<br>6.0 | V    |

| V <sub>OL</sub>        | Output Low Voltage                             | Open-drain Outputs, I <sub>OL</sub> = -2mA           | 0           |      | 0.4                       | V    |

| V <sub>CSWFZ</sub>     | Card-Side Wait-For-Zero<br>Threshold           | Note <u>6</u> /                                      | 0.5         |      | 1.2                       | ٧    |

| R <sub>Pull-Up</sub>   | Input Pull-Up Resistors                        | See Pin Descriptions                                 | 50          | 100  | 165                       | kΩ   |

| V <sub>CROW</sub>      | CROWBAR Output Voltage                         | $R_{LOAD}$ =10k $\Omega$ to gnd                      | VDD_CAP-0.5 |      | VDD_CAP                   | V    |

Notes:

<sup>&</sup>lt;u>4</u>/ 5/

$I_{VGATE}$  is the sum of all VGATE output currents. The SMT4004A adjusts the VGATE outputs to control the differential of the VOX outputs to within 100mV nominally. External influences may increase the differential until the VGATE outputs adjust to minimize the differential.

Guaranteed by Design.

# **SMT4004A**

# **AC OPERATING CHARACTERISTICS**

(Over recommended operating conditions, unless otherwise noted. All voltages are relative to GND.)

| Symbol                  | Description                                                  | Conditions                         | Min. | Тур.               | Max.                                 | Unit |

|-------------------------|--------------------------------------------------------------|------------------------------------|------|--------------------|--------------------------------------|------|

|                         |                                                              | CB <sub>DELAY</sub> = 25µs         | 20   | 25                 | 40                                   | μs   |

| CB <sub>DELAY</sub>     | Programmable Circuit Breaker Filter                          | CB <sub>DELAY</sub> = 50µs         | 40   | 50                 | 80                                   | μs   |

| CDDELAY                 | Trogrammable Circuit breaker Filter                          | CB <sub>DELAY</sub> = 100µs        | 80   | 100                | 140                                  | μs   |

|                         |                                                              | CB <sub>DELAY</sub> = 200µs        | 160  | 200                | 40<br>80                             | μs   |

|                         |                                                              | t <sub>PWDTO</sub> = 400ms         |      |                    |                                      |      |

| t <sub>PWDTO</sub>      | Programmable Watchdog Timer                                  | t <sub>PWDTO</sub> = 800ms         | -25  | t <sub>PWDTO</sub> | +25                                  | %    |

| PWDTO                   | Time-Out Period                                              | t <sub>PWDTO</sub> = 1600ms        |      | PWDTO              | . 20                                 | 70   |

|                         |                                                              | t <sub>PWDTO</sub> = 3200ms        |      |                    | 40<br>80<br>140<br>280<br>+25<br>+25 |      |

|                         |                                                              | t <sub>PLDTO</sub> = 800ms         |      |                    |                                      |      |

| t <sub>PLDTO</sub>      | Programmable Longdog Timer Time-                             | t <sub>PLDTO</sub> = 1600ms        | -25  | t <sub>PLDTO</sub> | +25                                  | %    |

| PLDIO                   | Out Period                                                   | t <sub>PLDTO</sub> = 3200ms        |      | PLDTO              | 80<br>140<br>280<br>+25<br>+25       | 70   |

|                         |                                                              | t <sub>PLDTO</sub> = 6400ms        |      |                    |                                      |      |

|                         |                                                              | $t_{PRTO} = 25 ms$                 |      |                    |                                      |      |

| toore                   | Programmable Reset Time-Out                                  | $t_{PRTO}$ = 50ms                  | -25  | t <sub>PRTO</sub>  |                                      | %    |

| t <sub>PRTO</sub>       | Period                                                       | t <sub>PRTO</sub> = 100ms          |      |                    |                                      |      |

|                         |                                                              | t <sub>PRTO</sub> = 200ms          |      |                    |                                      |      |

| t <sub>CROW</sub>       | CROWBAR output pulse width                                   | SCR Mode, $R_{LOAD}$ =10k $\Omega$ | 6    | 10                 | 15                                   | μs   |

| t <sub>DFIRQ</sub>      | Delay from fault detection to IRQ#                           |                                    |      | 1                  |                                      | μs   |

| t <sub>DFRST</sub>      | Delay from fault detection to RST#                           |                                    |      | 1                  |                                      | μs   |

| t <sub>DFHEALTHY#</sub> | Delay from fault detection to HEALTHY#                       |                                    |      | 1                  |                                      | μs   |

| t <sub>DTKRIRQ</sub>    | Delay from tracking fault detection to TRKR IRQ#             |                                    |      | 1                  |                                      | μs   |

| t <sub>DFCR</sub>       | Delay from fault detection to CROWBAR                        |                                    |      | 1                  |                                      | μs   |

| t <sub>DMRRST</sub>     | Delay from assertion of MR# to RST# Active                   |                                    |      | 100                |                                      | ns   |

| t <sub>DVIVG</sub>      | Delay from VIX valid to VGATEX activated                     | VGG_CAP=14V                        | 0    |                    |                                      | μs   |

| t <sub>DFSVG</sub>      | Delay from assertion of FORCE_SD to VGATE clamped to ground. |                                    |      | 10                 |                                      | μs   |

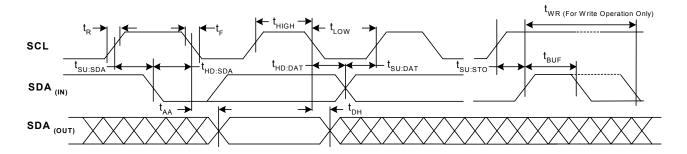

# I<sup>2</sup>C 2-WIRE SERIAL INTERFACE AC OPERATING CHARACTERISTICS - 100kHz

(Over recommended operating conditions, unless otherwise noted. All voltages are relative to GND.)

| Symbol              | Description                | Conditions                        | Min | Typ | Max  | Units |  |

|---------------------|----------------------------|-----------------------------------|-----|-----|------|-------|--|

| f <sub>SCL</sub>    | SCL Clock Frequency        |                                   | 0   |     | 100  | KHz   |  |

| t <sub>LOW</sub>    | Clock Low Period           |                                   | 4.7 |     |      | μS    |  |

| t <sub>HIGH</sub>   | Clock High Period          |                                   | 4.0 |     |      | μS    |  |

| t <sub>BUF</sub>    | Bus Free Time              | Before New Transmission Note 1/   | 4.7 |     |      | μS    |  |

| t <sub>SU:STA</sub> | Start Condition Setup Time |                                   | 4.7 |     |      | μS    |  |

| t <sub>HD:STA</sub> | Start Condition Hold Time  |                                   | 4.0 |     |      | μS    |  |

| t <sub>SU:STO</sub> | Stop Condition Setup Time  |                                   | 4.7 |     |      | μS    |  |

| t <sub>AA</sub>     | Clock Edge to Data Valid   | SCL low to valid SDA (cycle n)    | 0.2 |     | 3.5  | μS    |  |

| t <sub>DH</sub>     | Data Output Hold Time      | SCL low (cycle n+1) to SDA change | 0.2 |     |      | μS    |  |

| t <sub>R</sub>      | SCL and SDA Rise Time      | Note <u>1</u> /                   |     |     | 1000 | ns    |  |

| t <sub>F</sub>      | SCL and SDA Fall Time      | Note <u>1</u> /                   |     |     | 300  | ns    |  |

| t <sub>SU:DAT</sub> | Data In Setup Time         |                                   | 250 |     |      | ns    |  |

| t <sub>HD:DAT</sub> | Data In Hold Time          |                                   | 0   |     |      | ns    |  |

| TI                  | Noise Filter SCL and SDA   | Noise suppression                 |     | 100 |      | ns    |  |

| $t_{WR}$            | Write Cycle Time           |                                   |     |     | 5    | ms    |  |

Note: 1/ - Guaranteed by Design.

# **TIMING DIAGRAMS**

Figure 8 . Basic I<sup>2</sup>C Serial Interface Timing

# TIMING DIAGRAMS (CONTINUED)

Figure 9. De-asserting the VGATE Outputs with the Enabling Inputs

Figure 10. Relation of LDO# and WDO# with WLDI, RST# and MR#

# **APPLICATIONS INFORMATION**

#### **APPLICATIONS EXAMPLE**

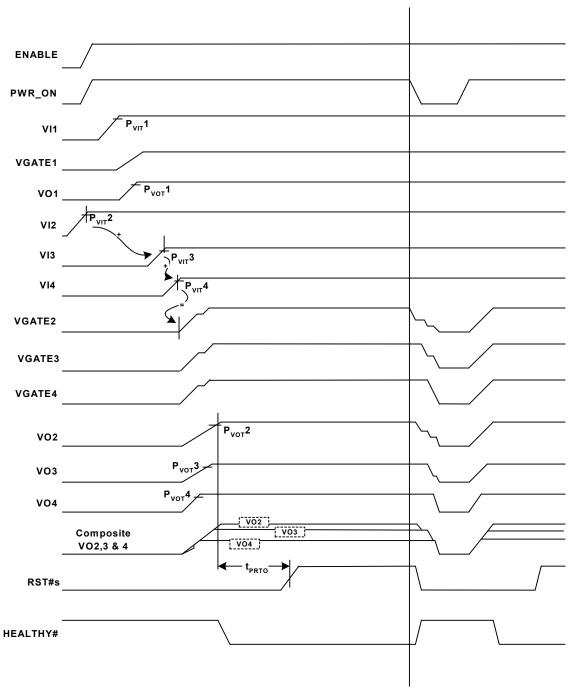

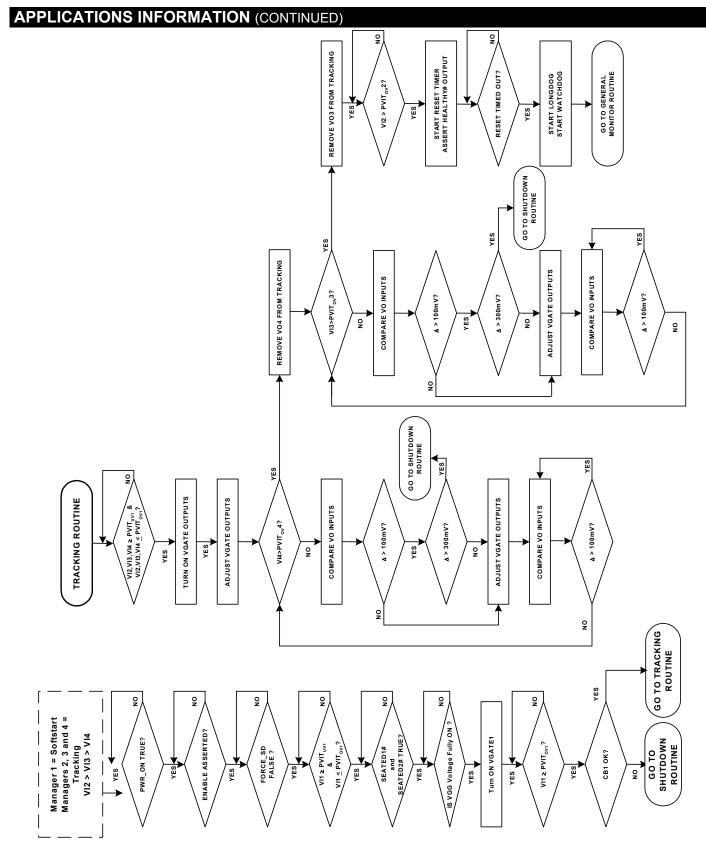

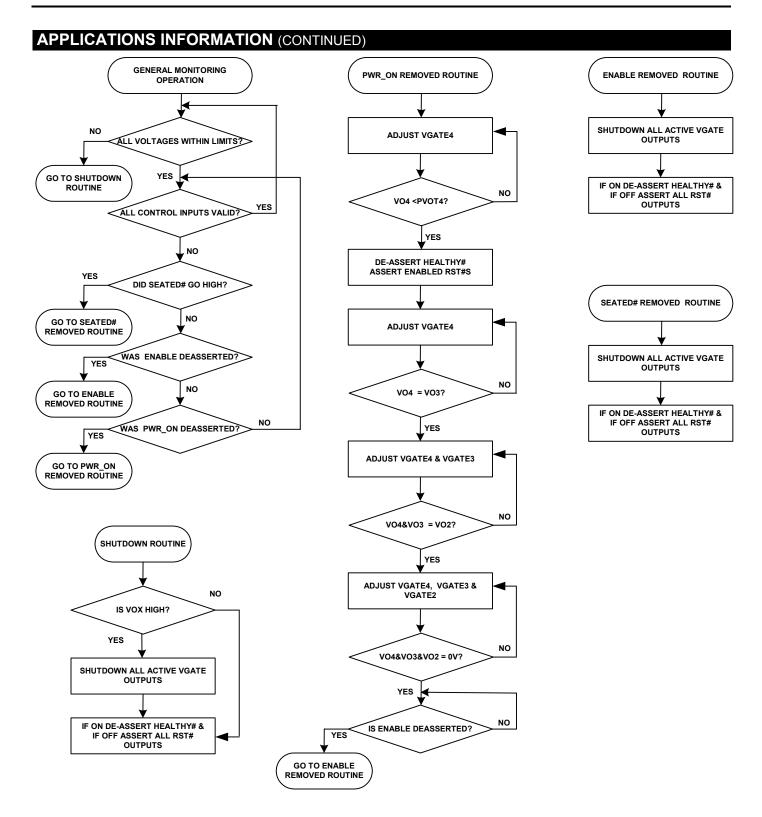

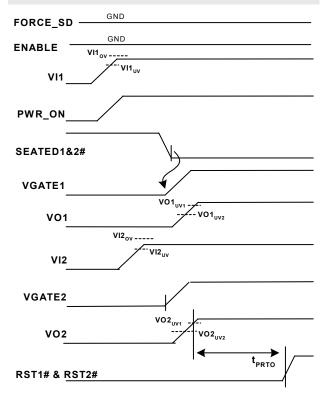

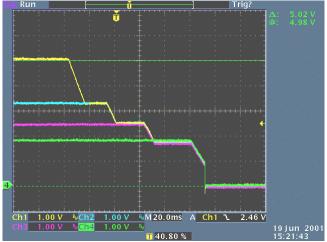

The timing diagram in Figure 11 illustrates a full power-on and power-off sequence and the relationship between many of the signals. This is based on the simplified applications diagram on Page 1. Manager 1 is programmed to softstart. Its supply feeds two power supplies that are monitored by managers 3 and 4 that, along with manager 2, are programmed for tracking. The flow chart in Figures 12A and 12B are a further illustration of the same application.

Figure 11 – Timing of Events During Power-On and Power-Off sequences.

Figure 12A - Power-On Sequence of Events

Figure 12B - Power-Off Sequence of Events

#### SOFTSTART VS TRACKING

As a power supply manager the SMT4004A separates two power domains; the bus-side, or source power supplies, and the card-side that contains the application circuitry. Its primary tasks are to monitor the voltages and control the switching of the bus-side voltages to the card-side circuits. The switching is accomplished by providing a high-side drive output on the VGATE pins. The VGATE output is applied to the gates of the power MOSFET.

#### **Softstart**

The supply managers can act as either tracking managers or as softstart managers. Individual managers turn on their VGATE outputs once all enabling conditions for that class of manager (softstart or tracking) are met. If a manager is set to soft start, its VGATE output ramps at a programmable constant slew rate until it reaches its maximum value. This operation is commonly used when a voltage (e.g., 5V) is first switched into a DC-to-DC converter or group of LDOs. These outputs may then be tracked to the card-side logic.

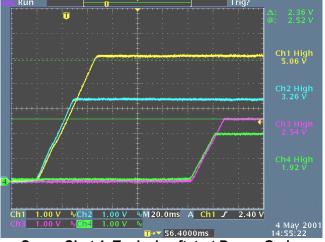

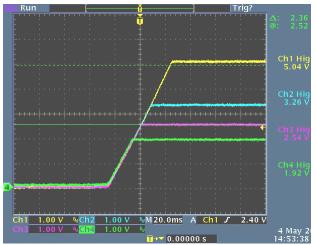

Scope Shot 1. Typical softstart Power-On by twomanagers and tracking by two managers.

## **Tracking**

When a manager is programmed for tracking all enabling conditions for that class of manager (tracking) must be met before the VGATE outputs are turned on. The enabling conditions also include all softstart managers having their VGATE outputs fully on with no existing fault conditions for the softstart managers.

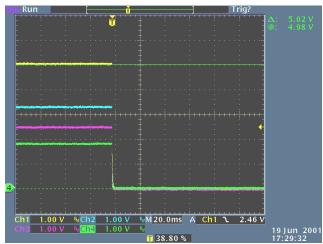

During tracking the card-side voltages are monitored to minimize the differential voltage between each tracked voltage until they reach their respective undervoltage thresholds (UV1). In tracking mode the ramp rates are constant but can stop and wait. That is, if, during the tracking interval, there is any difference between the VO inputs, the VGATE outputs will stop and wait for the slow channel to catch up.

Scope Shot 2. Power-On with all four managers set to track.

#### **POWER-ON**

#### **Initial Conditions**

At least one of the VI pins must be equal to or greater than 2.85V before the power-on operation can proceed. For reliable operation the VDD\_CAP node voltage must be equal to or greater than 2.7V (voltage level measured on pin 42). This requires that at least one of the VI inputs needs to be at or above 2.85V for proper device operation. There is internal arbitration circuitry which chooses the highest VIx to power the SMT4004A and causes an internal voltage drop from VIx to VDD CAP.

Both SEATED# inputs must be low. The SEATED# inputs are generally used with staggered-pin applications where the connector for the application card has two or three levels of pin lengths. This allows 'early-power' to be applied to the SMT4004A so it can begin to monitor bus side supplies as they come up, and also a method to indicate the application board is fully seated and ready for operation. Removal of a powered board is first recognized by the SEATED# pins going high, causing power-off of the board by shutting down the charge-pump, not ensuring a track

down. In this application the SEATED# pins are routed to the board's short pins and grounded when the board is fully inserted. The SEATED# pins can be tied to card insertion switches or they actively driven and used as device enable inputs.

FORCE\_SD can be programmed as a true high or true low input. When asserted, the VGATE outputs are turned off and clamped to ground. This input must be false for power-on to proceed. This pin is internally pulled up to the VDD\_CAP node with a  $100 \mathrm{K}\Omega$  resistor.

The PWR\_ON input can be programmed as a true high or true low input. It must be true for both soft start and tracking managers to turn on their VGATE outputs. If the SMT4004A has already activated the VGATE outputs and PWR\_ON is turned off, only the VGATE outputs for the tracking managers are turned off. VGATE outputs programmed for soft start remain active.

An I<sup>2</sup>C power-on function is available. This allows the tracking power-on/off operations to be initiated by the 2-wire serial interface.

If the SMT4004A is configured for I<sup>2</sup>C power-on then the PWR\_ON pin must be in its true state.

The ENABLE input can be programmed to a true high or true low input. The ENABLE input activates the high-side driver charge pump and must be true for the VGATE outputs to be able to drive the gates of the external MOSFETs.

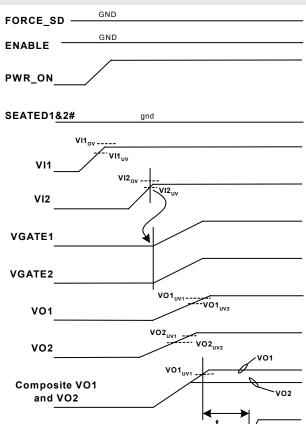

Managers programmed for soft start enable their VGATE outputs once all softstarted VI inputs are within their programmed threshold limits (UV and OV) (Figure 13). Managers programmed for tracking enable their VGATE output once softstarting is successful and all tracking manager's VI inputs are within their programmed threshold limits (Figure 14).

#### **POWER-ON OPTIONS**

#### **Bus-side Over-voltage**

If OV detection is selected and is programmed to be a trigger source for IRQ#, and if IRQ# is a trigger source for force shutdown (FSD), the user has several options as to how the part reacts to an OV. Different options can be chosen for how the SMT4004A will respond during the time periods during power-on, after power-on has completed, or when normal monitoring is underway. OV detection must not be enabled on disabled manager channels.

Assumptions: managers 1 & 2 are softstart, managers 3 & 4 are tracking and are not shown; Staggered pin application; ENABLE true low and FORCE\_SD true high, both tied to ground; PWR\_ON active high, tied to +5V thru pull up; only RST1# and RST2# enabled.

Figure 13. Typical Soft Start Sequence

If an OV occurs after softstart has completed and before tracking has begun, the SMT4004A can be programmed to ignore the OV. A case where this would be selected might be as illustrated in the Simplified Applications drawing on Page 1. Assume the +5V softstarts as planned and the LDO's are energized. The LDOs might cause a temporary OV condition before full regulation on the 1.5V or 2.5V supplies occurs.

If the ignore option is selected the following are true:

- 1. Only managers with OV detection are affected.

- If OV occurs during softstart, the VGATE outputs are turned off and remain off until the OV condition is cleared.

- If tracking has started and OV is detected, a FORCE SD is initiated.

Assumptions: managers 1 and 2 are tracking managers; Managers 3 & 4 are turned off; FORCE\_SD is active high and ENABLE is active low, both tied to ground; PWR\_ON is active high tied to VDD thru a pull-up resistor; the SEATED# inputs are tied to ground.

Figure 14 - Typical tracking sequence of operation.

#### **Card-side Voltage**

**RST1# & RST2#**

When tracking is selected the SMT4004A monitors the VO inputs prior to initiating the tracking function. The SMT4004A will not start tracking until the VO inputs are below 0.5V (**V**<sub>CSWFZ</sub>). However, some systems may partially charge one or more of the power busses if a softstart voltage has energized some of the application circuitry. If the charge is excessive (>**V**<sub>CSWFZ</sub>), tracking will not start. The SMT4004A has two options that can be selected to accommodate this situation.

The "Don't-Wait-For-Zero" (DWFZ) option can be enabled. As the name implies the SMT4004A will not monitor the VO inputs and tracking starts once all UV, OV and enabling inputs are valid. NOTE: If the starting VO potentials are too high, tracking of low voltage supplies may not meet some system specifications.

2. The CROWBAR pin is normally configured to output a short positive pulse to trigger an SCR. Optionally it can be configured as a normally active high output during the power-on phase prior to tracking. Configured as such, it can be used to drive the gate of an N-channel MOSFET to actively discharge any 'early voltages.' Once tracking is initiated, the CROWBAR output goes low allowing the card-side voltages to turn-on. Refer to Figure 15 for a schematic illustration.

NOTE: This feature can be used independently or in conjunction with the DWFZ option.

Figure 15 - Example implementation of the 'Early Drive Function.'

# **Tracking Failure Options**

During tracking differentials greater than 300mV between VO inputs can be reported through the assertion of the TRKR\_IRQ# output. Any tracking manager detecting a failure can generate an interrupt, and any tracking manager can be assigned to track but not generate an interrupt.

If a manager is assigned to track, and a tracking error is detected, the SMT4004A can be programmed to take one of the following actions.

- Ignore the condition and proceed with the power-on operation.

- Shutdown all supplies and generate a TRKR IRQ#.

- Generate a TRKR\_IRQ# and proceed with the power-on operation.

#### **POWER-OFF**

Power-off of the application circuit is affected by turning off the VGATE outputs. This can be done by de-asserting one of the enabling signals or the detection of a fault condition. When the SMT4004A

Scope Shot 3. Power-Off caused by de-assertion of PWR\_ON ( all managers selected for tracking).

receives a power-off command, whether it is from the PWR\_ON pin, an I<sup>2</sup>C command, or from the latching of a fault, there will be a delay of approximately VI<sub>MAX</sub>/Tracking Slew Rate (where VI<sub>MAX</sub> is the VI with the highest voltage level) before the first tracked VGATE begins to discharge.

## **Enabling Inputs**

If the PWR\_ON input is de-asserted tracking managers will 'track down' their voltages. The softstart managers are unaffected and their VGATE outputs remain active. If either or both SEATED# inputs are de-asserted the SMT4004A immediately powers-off the VGATE outputs.

If the FORCE\_SD input is asserted the managers immediately shut off the VGATE drivers by clamping these outputs to ground (Scope Shot 4).

If the ENABLE input is de-asserted, the VGATE outputs are shut off. Refer to Figure 9 for an illustration of de-asserting the various enabling inputs.

Scope Shot 4. Power-Off of all managers using the FORCE SD pin.

#### SOFTWARE POWER-ON/POWER-OFF

The SMT4004A has an option allowing a commanded power-on and power-off via the  $I^2C$  serial interface of tracked channels. If the device is configured for this option, the PWR\_ON pin must be in the true state. Once all enabling conditions are met and all voltages are within their thresholds the SMT4004A can be tracked-up by writing to register 16. Once the application circuit is tracked-up a subsequent write to register 17 initiates a track down. Refer to the applications circuits and descriptions for a system level description.

#### **RESET OPERATION**

Once power is applied to the SMT4004A the four RST# outputs are driven low. Because they are meant to be used by the application circuitry, the RST# outputs remain low until all Reset trigger sources (for any manager's UV1, UV2 or QT-CB output) are removed. The RST# outputs remain low for the duration of the programmable reset time-out period ( $t_{\text{PRTO}}$ ) after the triggers are cleared.

After the circuitry is 'powered-on' and the SMT4004A is in the steady-state monitoring mode, the RST# outputs remain high unless one of the enabled fault conditions is detected by a manager. When this occurs only the RST# output affected by that manager is asserted. All RST# outputs that have gone low to indicate a problem on their corresponding channel will remain low until all reset conditions have been removed and  $t_{\text{PRTO}}$  has expired.

All four RST# outputs are driven low when the MR# input is taken low. They continue to assert their outputs after MR# returns high for t<sub>PRTO</sub> seconds.

# INTERRUPTS, FORCE SHUTDOWN AND CROWBAR

The SMT4004A has two interrupt outputs: IRQ# and TRKR\_IRQ#. The CROWBAR output is configurable to operate in conjunction with the IRQ# outputs.

The IRQ# output has a large number of programmable sources for latching its output. Any combination of supply manager fault condition outputs (UV, OV, UV1, UV2 and QT-CB) can be enabled as a trigger for the IRQ# latched output. Once triggered the IRQ# output is latched and remains asserted even if the fault condition is removed. IRQ# can only be cleared by asserting the IRQ\_CLR# input.

IRQ# can also trigger a force shutdown (FSD) and/or a CROWBAR pulse. Refer to Figure 3 and the graphical user interface (GUI) for the SMT4004A.

During the power on sequence of the SMT4004A the IRQ# output is disabled for the IRQ# hold-off time period. This time period begins when the PWR\_EN and ENABLE are active. Once the IRQ# hold-off time period expires any programmed IRQ condition will trigger the IRQ# output. The IRQ# hold-off time period precedes the Reset timeout period. If the reset conditions are removed before the end of the IRQ# hold-off time period the reset timeout period will begin after the IRQ# hold-off timer has timed out. The hold off can be extended from the end of the Reset timeout period for 0ms, 200ms, 400ms, 800ms or 1600ms. This allows the application circuit and all of the supplies time to stabilize after the initial power-on.

The VGATE control circuitry monitors VO inputs for those managers selected for tracking. If a VO input is found to not be tracking, or deviates from the other voltages by more than 300mV, the control circuitry generates a tracker error. If that output is ANDed with an enable bit it forces the TRKR\_IRQ# output low. No other fault conditions can generate a TRKR\_IRQ#. TRKR\_IRQ# can trigger an internal force shutdown and/or a CROWBAR pulse like the IRQ# output.

If the fault latch feature is enabled the fault condition is captured. The fault sources are a forced shutdown, CROWBAR, or IRQ#. When a fault is detected a volatile latch is set to keep the SMT4004A from being powered-up again until IRQ CLR# is toggled.

The CROWBAR pin is designed to deliver an active high pulse to an external SCR to shutdown the cardside voltages as quickly as possible. A CROWBAR pulse can be triggered by one of seven inputs: a QT-CB fault, an IRQ#, a TRKR IRQ# and/or assertion of the FORCE SD input. These trigger sources are optional and any combination can be selected. Note: because an over-current condition is potentially catastrophic, each manager has a unique source input to the CROWBAR logic even though they are included in the trigger sources for an IRQ#. This allows less harmful fault triggers to be used as inputs for the IRQ# without generating a CROWBAR. There is also an option to change the CROWBAR pin output from an SCR pulse to a voltage level to discharge Card-side early voltages prior to tracking (see Figure 15).

#### WATCHDOG AND LONGDOG TIMERS

The SMT4004A has two timers that generate independent outputs: the WDO#, or watchdog timer output, and the LDO#, or longdog timer output. Both timers use the same clock circuitry. However, the time out period for each timers is independently programmable. When the timer has timed out for either the watchdog or the longdog, their respective outputs are driven low. The timers are Reset to  $t_0$  by a low-to-high transition on the WLDI input.

Note: If WLDI is held high the WDO# output is disabled and the LDO# transitions low after its programmed time out period  $t_{\text{PLDTO}}$ . It remains low for  $t_{\text{PLDTO}}$  returning high for  $t_{\text{PLDTO}}$  seconds, and repeating the pulse output until the next low-to-high transition on the WLDI input.