# **AN221E02 Datasheet**

# **Entry Level, Dynamically Reconfigurable FPAA With Enhanced I/O**

www.anadigm.com

#### Disclaimer

Anadigm reserves the right to make any changes without further notice to any products herein. Anadigm makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Anadigm assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including with out limitation consequential or incidental damages. "Typical" parameters can and do vary in different applications. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. Anadigm does not in this document convey any license under its patent rights nor the rights of others. Anadigm software and associated products cannot be used except strictly in accordance with an Anadigm software license. The terms of the appropriate Anadigm software license shall prevail over the above terms to the extent of any inconsistency.

© Anadigm<sup>®</sup> Ltd. 2003 © Anadigm<sup>®</sup>, Inc. 2003 All Rights Reserved.

#### PRODUCT AND ARCHITECTURE OVERVIEW

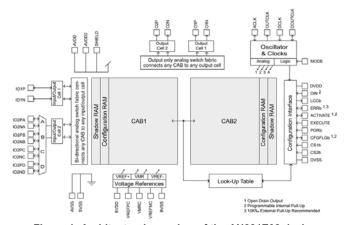

The AN221E02 device is a low-cost, entry-level version of the Anadigmvortex FPAA. The device consists of a two fully Configurable Analog Blocks (CABs), surrounded by a fabric of programmable interconnect resources. Each device has two configurable I/Os and two dedicated outputs – which allows for maximum flexibility to the system designer.

# These devices can be configured both in the static and in the dynamic mode.

Using the on-chip LUT, these devices also accommodate nonlinear functions such as sensor response linearization and arbitrary waveform synthesis. In addition, the AN221E04 devices allow designers to implement an integrated 8-bit analog-to-digital converter on the FPAA, eliminating the potential need for an external converter.

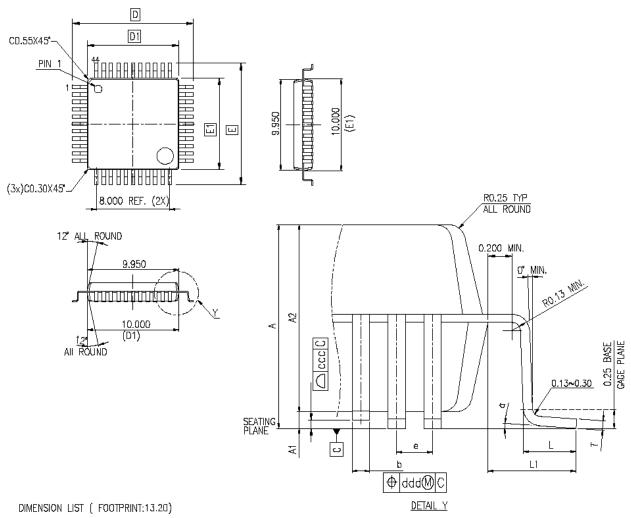

Packaged in a standard 44-pin TQFP package, these devices maintain pin compatibility with the larger FPAA devices (i.e. the AN221E04); allowing designers the ability to migrate up the density curve

Figure 1: Architectural overview of the AN221E02 device

With dynamic reconfigurability, the functionality of the AN221E02 can be reconfigured in-system by the designer or on-the-fly by a microprocessor. A single AN221E02 can thus be programmed to implement multiple analog functions and/or to adapt on-the-fly to maintain precision operation despite system degradation and aging.

#### **PRODUCT FEATURES**

- Two CABs, Two configurable I/O, two dedicated outputs

- Static and Dynamic reconfiguration

- 256 Byte Look-Up Table (LUT) for linearization and arbitrary signal generation

- 8-bit SAR analog-to-digital converter

- Fully differential architecture

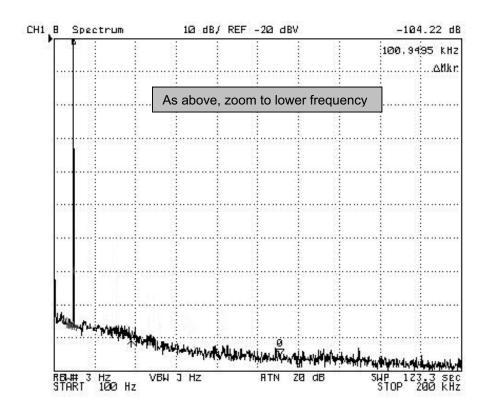

- SNR Broadband 80dB

- SNR Narrowband (audio) 100dB

- Total Harmonic Distortion (THD): 80dB

- Fully differential I/O buffering with options for single ended to differential conversion

- · Low input offset through chopper stabilized amplifiers

- DC offset <100μV</li>

- 4:1 Input multiplexer

- Typical Signal Bandwidth: DC-2MHz (Bandwidth is CAM dependent)

- Package: 44-pin QFP (10x10x2mm)

- Lead pitch 0.8mm

- Supply voltage: 5V

## **ORDERING CODES**

AN221D04-EVAL

AN221E02-QFPSP Dynamically reconfigurable FPAA

Sample Pack

AN221E02-QFPTY Dynamically reconfigurable FPAA

Tray (96 pcs)

AN221E02-QFPTR Dynamically reconfigurable FPAA

Tape and Reel (1000 pcs) Anadigmvortex Evaluation Kit

Anadigmvortex Evaluation Kit

#### **APPLICATIONS**

- Intelligent sensor modules

- Tunable filters

- Programmable analog front-end to DSPs

- Self-calibrating systems

- Compensation for aging of system components

- Dynamic recalibration of remote systems

- Ultra-low frequency signal conditioning

- · Custom analog signal processing

[For more detailed information on the features of the AN221E02 device, please refer to the Anadigmvortex Silicon User Manual coming soon.]

# **ELECTRICAL CHARACTERISTICS**

## **Absolute Maximum Ratings**

| Parameter                        | Symbol                  | Min     | Тур | Max         | Unit | Comment                                                      |

|----------------------------------|-------------------------|---------|-----|-------------|------|--------------------------------------------------------------|

| DC Power Supplies                | AVDD(2)<br>BVDD<br>DVDD | -0.5    | -   | 5.5 V       | ٧    | AVSS, BVSS, DVSS and SVSS all held to 0.0 V <sup>a</sup>     |

| xVDD to xVDD Offset              |                         | -0.5    |     | 0.5         | V    | Ideally all supplies should be at the same voltage           |

| Package Power Dissipation        | Pmax 25°C<br>Pmax 85°C  | 1       | -   | 1.8<br>0.73 | W    | Still air, No heatsink, 4 layer board, 44 pins. θja = 55°C/W |

| Analog and Digital Input Voltage | Vinmax                  | Vss-0.5 | -   | Vdd+0.5     | V    |                                                              |

| Ambient Operating Temperature    | Тор                     | -40     | -   | 85          | ŷ    |                                                              |

| Storage Temperature              | Tstg                    | -65     |     | 150         | ပွ   |                                                              |

<sup>&</sup>lt;sup>a</sup> Absolute Maximum DC Power Supply Rating - The failure mode is non-catastrophic for Vdd of up to 7 volts, but will cause reduced operating life time. The additional stress caused by higher local electric fields within the CMOS circuitry may induce metal migration, oxide leakage and other time/quality related issues.

## **Recommended Operating Conditions**

| Parameter             | Symbol                  | Min     | Тур  | Max     | Unit | Comment                                   |

|-----------------------|-------------------------|---------|------|---------|------|-------------------------------------------|

| DC Power Supplies     | AVDD(2)<br>BVDD<br>DVDD | 4.75    | 5.00 | 5.25    | V    | AVSS, BVSS, DVSS and SVSS all held to 0 V |

| Analog Input Voltage. | Vina                    | VMR-1.9 | -    | VMR+1.9 | V    | VMR is 2.0 volts above AVSS               |

| Digital Input Voltage | Vind                    | 0       | -    | DVDD    | V    |                                           |

| Junction Temp         | Tj                      | -40     | -    | 125     | °C   | Assume a package θja = 55°C/W b           |

b In order to calculate the junction temperature you must first empirically determine the current draw (total ldd) for the design. Once the current consumption established then the following formula can be used; Tj = Ta + ldd x Vdd x 55 °C/W, where Ta is the ambient temperature. The worst case θja of 55 °C/W assumes no air flow and no additional heatsink of any type.

## General Digital I/O Characteristics (Vdd = 5v +/- 10%, -40 to 85 deg.C)

| Parameter             | Symbol  | Min | Тур   | Max  | Unit    | Comment                            |

|-----------------------|---------|-----|-------|------|---------|------------------------------------|

| Input Voltage Low     | Vih     | 0   | -     | 30   | -       | % of DVDD                          |

| Input Voltage High    | Vil     | 70  | -     | 100  | -       | % of DVDD                          |

| Output Voltage Low    | Vol     | 0   | -     | 20   | -       | % of DVDD                          |

| Output Voltage High   | Voh     | 80  | -     | 100  | -       | % of DVDD                          |

| Input Leakage Current | lil     | -   | -     | ±1.0 | μΑ      | All pins except DCLK               |

| Input Leakage Current | lil     | _   | ±12.0 | _    | μA      | DCLK if a crystal is connected and |

|                       | III     | -   | 112.0 | _    | μΛ      | the on-chip oscillator is used     |

| Max. Capacitive Load  | Cmax    | _   | _     | 10   | pF      | The maximum load for a digital     |

|                       | Ciliax  | _   |       | 10   | ρι      | output is 10 pF // 10 Kohm         |

| Min. Resistive Load   | Rmin    | 10  | _     | _    | Kohm    | The maximum load for a digital     |

|                       | IXIIIII | 10  | _     | _    | ROIIII  | output is 10 pF // 10 Kohm         |

| DCLK Frequency        | Fmax    |     |       | 40   | MHz     | For MODE = 1, Max DCLK is          |

|                       | 1 IIIax | -   | -     | 40   | IVII IZ | 16 MHz                             |

| ACLK Frequency        | Fmax    |     |       | 40   | MHz     | Divide down to <8 MHz prior to use |

|                       | i illax | _   | -     | 40   | IVITIZ  | as a CAB clock                     |

| Clock Duty Cycle      | -       | 45  | -     | 55   | %       | All clocks                         |

# Detailed Digital I/O Interface Characteristics: Vdd = 5.0volts **LCCb**

| Parameter            | Symbol  | Min | Тур | Max | Unit | Comment                       |

|----------------------|---------|-----|-----|-----|------|-------------------------------|

| Output Voltage Low   | Vol     | Vss | -   | 150 | mV   | Load 20pF//50Kohm to Vss      |

| Output Voltage High  | Voh     | 4.5 | -   | Vdd | V    | Load 20pF//50Kohm to Vss      |

| Max. Capacitive Load | Cmax    | -   | -   | 20  | pF   | Maximum load 20 pF // 50 Kohm |

| Min. Resistive Load  | Rmin    | 50  | -   | -   | Kohm | Maximum load 20 pF // 50 Kohm |

| Current Sink         | Isnkmax | -   | -   | 15  | mA   | LCCb pin shorted to Vdd       |

| Current Source       | Isrcmax | -   | -   | 4   | mA   | LCCb pin shorted to Vss       |

# **CFGFLG, ACTIVATE**

| Parameter                 | Symbol     | Min | Тур | Max | Unit | Comment                                                    |

|---------------------------|------------|-----|-----|-----|------|------------------------------------------------------------|

| Input Voltage Low         | Vil        | 0   |     | 30  | %    | % of DVDD                                                  |

| Input Voltage High        | Vih        | 70  |     | 100 | %    | % of DVDD                                                  |

| Output Voltage Low        | Vol        | Vss | -   | 85  | mV   | Pin load =<br>Internal pullup + 20pF//50K to Vss           |

| Output Voltage High       | Voh        | 4.5 | -   | Vdd | V    | Pin load =<br>Internal pullup + 20pF//50K to Vss           |

| Output Voltage Low        | Vol        | Vss | -   | 200 | mV   | Pin Load =<br>External 5K ohm pullup +<br>20pF//50K to Vss |

| Output Voltage High       | Voh        | 4.5 | -   | Vdd | V    | Pin Load =<br>External 5Kohm pullup +<br>20pF//50K to Vss  |

| Max. Capacitive Load      | Cmax       | -   | -   | 50  | pF   | Maximum load 50 pF // 50 Kohm                              |

| Min. Resistive Load       | Rmin       | 50  | -   | -   | Kohm | Maximum load 50 pF // 50 Kohm                              |

| Current Sink              | Isnkmax    | -   | -   | 2.5 | mA   | Pin shorted to Vdd                                         |

| Current Source            | Isrcmax    | -   | -   | 200 | μΑ   | Pin shorted to Vss                                         |

| External Resistive Pullup | Rpullupext | 5   | 7.5 | 10  | Kohm | Use only if internal pullup is deselected                  |

### **ERRb**

| Parameter                 | Symbol     | Min | Тур | Max | Unit | Comment                       |

|---------------------------|------------|-----|-----|-----|------|-------------------------------|

| Input Voltage Low         | Vil        | 0   |     | 30  | %    | % of DVDD                     |

| Input Voltage High        | Vih        | 70  |     | 100 | %    | % of DVDD                     |

| Output Voltage Low        | Vol        | Vss | -   | 50  | mV   |                               |

| Output Voltage High       | Voh        | 4.9 | -   | Vdd | V    |                               |

| Max. Capacitive Load      | Cmax       | -   | -   | 50  | pF   | Maximum load 50 pF // 50 Kohm |

| Min. Resistive Load       | Rmin       | 50  | -   | -   | Kohm | Maximum load 50 pF // 50 Kohm |

| Current Sink              | Isnkmax    | -   | -   | 10  | mA   |                               |

| Current Source            | Isrcmax    | -   | -   | 0   | μA   |                               |

| External Resistive Pullup | Rpullupext | 10  | 10  | 10  | Kohm |                               |

# DCLK,Mode,DIN,EXECUTE,PORb,CS1b,CS2b

| Parameter          | Symbol | Min | Тур | Max | Unit | Comment   |

|--------------------|--------|-----|-----|-----|------|-----------|

| Input Voltage Low  | Vil    | 0   | -   | 30  | %    | % of DVDD |

| Input Voltage High | Vih    | 70  | -   | 100 | %    | % of DVDD |

# OUTCLK/SPIMEM,DOUTCLK

| Parameter            | Symbol  | Min | Тур | Max | Unit | Comment                       |

|----------------------|---------|-----|-----|-----|------|-------------------------------|

| Output Voltage Low   | Vol     | 0   | -   | 20  | %    | % of DVDD                     |

| Output Voltage High  | Voh     | 80  | -   | 100 | %    | % of DVDD                     |

| Max. Capacitive Load | Cmax    | ı   | -   | 50  | pF   | Maximum load 50 pF // 50 Kohm |

| Min. Resistive Load  | Rmin    | 10  | -   | 1   | Kohm | Maximum load 50 pF // 50 Kohm |

| Current Sink         | Isnkmax | 1   | -   | 17  | mA   |                               |

| Current Source       | Isrcmax | -   | -   | 4   | mA   |                               |

## **ACLK/SPIP**

| Parameter            | Symbol  | Min | Тур | Max | Unit | Comment                       |

|----------------------|---------|-----|-----|-----|------|-------------------------------|

| Input Voltage Low    | Vil     | 0   | -   | 30  | %    | % of DVDD                     |

| Input Voltage High   | Vih     | 70  | -   | 100 | %    | % of DVDD                     |

| Output Voltage Low   | Vol     | 0   | -   | 20  | %    | % of DVDD                     |

| Output Voltage High  | Voh     | 80  | -   | 100 | %    | % of DVDD                     |

| Max. Capacitive Load | Cmax    | -   | -   | 50  | pF   | Maximum load 50 pF // 50 Kohm |

| Min. Resistive Load  | Rmin    | 10  | -   | -   | Kohm | Maximum load 50 pF // 50 Kohm |

| Current Sink         | Isnkmax | -   | -   | 15  | mA   |                               |

| Current Source       | Isrcmax | _   | -   | 4   | mA   |                               |

# **Analog Inputs General**

| Parameter                                      | Symbol   | Min | Тур | Max    | Unit | Comment                                                                                                                                                                  |

|------------------------------------------------|----------|-----|-----|--------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Precision Input Range <sup>c</sup>        | Vina     | 0.5 | -   | 3.5    | V    | VMR +/- 1.5v                                                                                                                                                             |

| Standard precision Input Range d               | Vina     | 0.1 | -   | 3.9    | V    | VMR +/- 1.9v                                                                                                                                                             |

| High Precision Differential Input <sup>c</sup> | Vdiffina | 0   | -   | +/-3.0 | V    | Common mode voltage = 2 V                                                                                                                                                |

| Standard Precision Differential Input d        | Vdiffina | 0   | -   | +/-3.8 | V    | Common mode voltage = 2 V                                                                                                                                                |

| Common Mode<br>Input Range                     | Vcm      | 1.8 | 2.0 | 2.2    | V    |                                                                                                                                                                          |

| Input Offset                                   | Vos      | 1   | 5   | 15     | mV   | Non-chopper stabilized input                                                                                                                                             |

| Input Frequency                                | Fain     | 0   | <2  | 8      | MHz  | Max value is clock, CAM and input stage dependant. Input frequency is limited to approx <2MHz due to CAM signal processing which is based on sampled data architectures. |

# Input Differential Amplifier ON and Filter OFF

| Parameter                                          | Symbol           | Min    | Тур        | Max     | Unit      | Comment                                                                                                                                       |

|----------------------------------------------------|------------------|--------|------------|---------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| Input Range                                        | Vina<br>Vdiffina | See ar | nalog inpu | t above |           | Usable input range will be reduced by the effective gain setting                                                                              |

| Gain Setting                                       | Ginamp           | 16     | -          | 128     |           |                                                                                                                                               |

| Gain Accuracy                                      |                  | -      | 1.0        | 2.5     | %         |                                                                                                                                               |

| Gain Drift (Temperature, Supply Voltage zand Time) | Dist             | -      | -          | 1.0     | %         |                                                                                                                                               |

| Equivalent Input Offset Voltage                    | Vos              | -      | 3          | 12      | mV        | Non-chopper stabilized input When the input amplifier and filter are used in combination Vos contribution comes only from the input amplifier |

| Offset Voltage Temperature Coefficient             | Voffsettc        | -      | 1          | 10      | μV/°C     | from -40°C to 125°C                                                                                                                           |

| Input Frequency <sup>c</sup>                       | Fain             | 0      | -          | 2       | MHz       |                                                                                                                                               |

| Input Frequency d                                  | Fain             | 0      | <2         | 8       | MHz       |                                                                                                                                               |

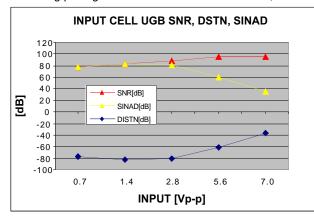

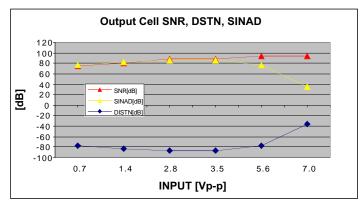

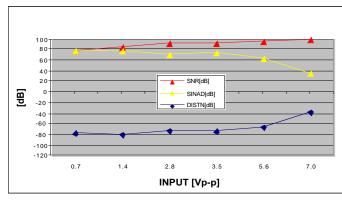

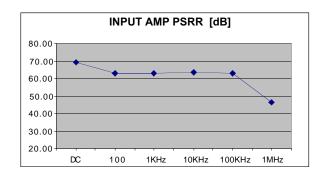

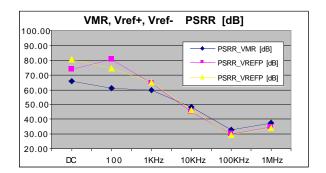

| Power Supply Rejection Ratio                       | PSRR             | 65     | -          | -       | dB        | d.c. Amp Gain =16<br>a.c. See graphs page 18                                                                                                  |

| Common Mode Rejection Ratio                        | CMRR             | -      | 67         | -       | dB        |                                                                                                                                               |

| Large Signal Harmonic Distortion                   | Dist             | -      | -65        | -       | dB        | 0.4v p-p Differential input at 660Hz<br>Gain setting = 16                                                                                     |

| Input Resistance                                   | Rin              | 10     |            | -       | Mohm      |                                                                                                                                               |

| Input Capacitance                                  | Cin              | -      |            | 5.0     | pF        |                                                                                                                                               |

| Input Referred Noise Figure                        | NF               | -      | 0.1        | -       | μV/sqrtHz | Input cell Gain = 16 Applies to audio frequency range (400Hz to 30KHz). See graphical data on page 18                                         |

| Signal-to Noise Ratio and Distortion               | SINAD            | -      | 75         | -       | dB        | Input signal = 285 mV p-p diff,<br>audio frequency range<br>See graphical data on page 18                                                     |

| Spurious Free Dynamic Range                        | SFDR             | -      | 73         | -       | dB        | Input signal = 100 mV p-p diff<br>See graphical data on page 18                                                                               |

<sup>&</sup>lt;sup>c.</sup> High precision operating range provides optimal linearity and dynamic range.

<sup>d.</sup> Standard precision operating range provides maximum dynamic range and reduced linearity.

<sup>&</sup>lt;sup>c.</sup> High precision operating range provides optimal linearity and dynamic range.

<sup>d.</sup> Standard precision operating range provides maximum dynamic range and reduced linearity.

# Input Differential Chopper Amplifier on and Filter OFF

| Parameter                                          | Symbol           | Min       | Тур                    | Max   | Unit      | Comment                                                                                                                                                                        |

|----------------------------------------------------|------------------|-----------|------------------------|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Range                                        | Vina<br>Vdiffina | See ana   | See analog input above |       |           | Usable input range will be reduced by the effective gain setting                                                                                                               |

| Gain Setting                                       | Ginamp           | 16        | -                      | 128   |           |                                                                                                                                                                                |

| Gain Accuracy                                      |                  | -         | 1.0                    | 2.5   | %         |                                                                                                                                                                                |

| Gain Drift, (Temperature, Supply Voltage and Time) |                  | -         | -                      | 1.0   | %         |                                                                                                                                                                                |

| Chopper Frequency Clock Range                      | Fch              | Fc/260100 | -                      | >250  | KHz       | Fc = master clock frequency<br>Set Fch as slow as possible<br>Fch > 250KHz will result in some<br>signal attenuation                                                           |

| Equivalent Input Offset Voltage                    | Vos              | -         | <100                   | 200   | μV        | Chopper stabilized amplifier The maximum value of 200µV is guaranteed by production test This is a tester limitation                                                           |

| Offset Voltage Temperature Coefficient             | Voffsettc        | -         | 0.5                    | 2.0   | μV/°C     | from -40°C to 125°C                                                                                                                                                            |

| Power Supply Rejection Ratio                       | PSRR             | 65        | -                      | -     | dB        | d.c.<br>a.c. See graphs on page 18                                                                                                                                             |

| Common Mode Rejection Ratio                        | CMRR             | -         | 102                    | -     | dB        |                                                                                                                                                                                |

| Large Signal Harmonic Distortion                   | Dist             | -         | -40                    | -     | dB        | 0.4v p-p Differential input at<br>660Hz<br>Gain setting = 16                                                                                                                   |

| Input Frequency                                    | Fain             | 0         | Fch/20                 | Fch/2 | KHz       | Fch=Chopper clock frequency The chopper frequency and input frequency should be chosen such that subsequent low pass filtering can remove the chopper stage frequency elements |

| Input Resistance                                   | Rin              | 10        |                        | -     | Mohm      | Input to filter or chopper                                                                                                                                                     |

| Input Capacitance                                  | Cin              | -         |                        | 5.0   | pF        |                                                                                                                                                                                |

| Input Referred Noise Figure                        | NF               | -         | 0.09                   | -     | μV/sqrtHz | Input cell Gain = 16 Applies to Audio frequency range Chopper clock Fch = 250KHz See graphical data on page 18                                                                 |

| Signal-to Noise Ratio and Distortion               | SINAD            | -         | 75                     | -     | dB        | Input signal = 285 mV p-p<br>differential,<br>Audio frequency range<br>See graphical data on page 18                                                                           |

| Spurious Free Dynamic Range                        | SFDR             | -         | 74                     | -     | dB        | Input signal =100 mV p-p<br>differential<br>See graphical data on page 18                                                                                                      |

# Input Differential Amplifier OFF and Filter ON

| Parameter                                 | Symbol           | Min   | Тур         | Max   | Unit  | Comment                                                                                                                                                              |

|-------------------------------------------|------------------|-------|-------------|-------|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Range                               | Vina<br>Vdiffina | See a | nalog input | above |       |                                                                                                                                                                      |

| Equivalent Input Offset                   | Vos              | -     | 8           | 32    | mV    | Non-chopper stabilized input,<br>Filter corner frequency =470KHz                                                                                                     |

| Offset Voltage Temperature<br>Coefficient | Voffsettc        | -     | 0.05        | 1.0"  | mV/°C | from -40°C to 125°C I. measured at filter corner=470Khz II. maximum at Filter corner=76KHz                                                                           |

| Input Frequency                           | Fain             | -     | -           | -     | MHz   | Input filter frequency will define the maximum frequency Input filter is recommended to be >30x higher than the max input frequency, for 80dB distortion performance |

| Common Mode Rejection Ration                                 | CMRR        | -  | 60   | -   | dB        |                                                                                                     |

|--------------------------------------------------------------|-------------|----|------|-----|-----------|-----------------------------------------------------------------------------------------------------|

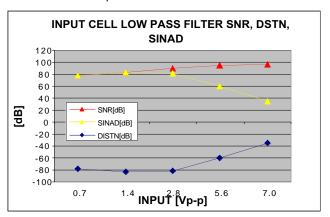

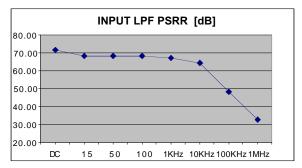

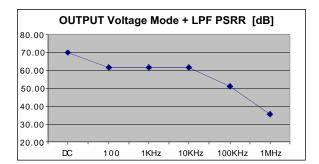

| Power Supply Rejection Ratio                                 | PSRR        | 68 | ı    | -   | dB        | d.c.<br>a.c. See graphical data on page 19                                                          |

| Large Signal Harmonic Distortion                             | Dist        | -  | -82  | -   | dB        | 4v p-p Differential input at 660Hz<br>Filter corner frequency 470KHz                                |

| Input Low Pass Filter (Anti-Alias) Corner Frequency Settings | Ffiltcorner | 76 | -    | 470 | KHz       |                                                                                                     |

| Input Resistance                                             | Rin         | 10 | -    | -   | Mohm      | Input to filter or chopper                                                                          |

| Input Capacitance                                            | Cin         | -  |      | 5.0 | pF        |                                                                                                     |

| Input Referred Noise Figure                                  | NF          | -  | 0.17 | -   | μV/sqrtHz | Input cell filter corner Fc = 470KHz Applies to Audio frequency range See graphical data on page 18 |

| Signal-To Noise Ratio and Distortion                         | SINAD       | -  | 84   | -   | dB        | Input signal = 1400 mV p-p diff,<br>Audio frequency range<br>See graphical data on page 18          |

| Spurious Free Dynamic Range                                  | SFDR        | -  | 90   | -   | dB        | Input signal =1400 mV p-p differential See graphical data on page 18                                |

# Input Differential Voltage Mode, Amplifier OFF, Filter OFF and Unity Gain Stage ON

| Parameter                              | Symbol           | Min    | Тур       | Max     | Unit      | Comment                                                                                    |

|----------------------------------------|------------------|--------|-----------|---------|-----------|--------------------------------------------------------------------------------------------|

| Input Range                            | Vina<br>Vdiffina | See an | alog inpu | t above | V         |                                                                                            |

| Equivalent Input Offset                | Vos              | -      | 5         | 15      | mV        | Non-chopper stabilized input                                                               |

| Offset Voltage Temperature Coefficient | Voffsettc        | -      | 20        | 50      | μV/°C     | from -40°C to 125°C                                                                        |

| Input Frequency                        | Fain             | -      | -         | 1.0     | MHz       | Gain Bandwidth limited by input impedance                                                  |

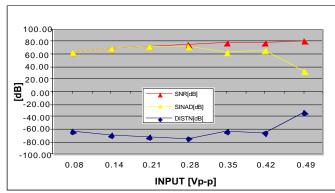

| Power Supply Rejection Ratio           | PSRR             | 60     | -         | -       | dB        | d.c.<br>a.c. See graphs on page 18                                                         |

| Common Mode Rejection Ratio            | CMRR             | -      | 60        | -       | dB        |                                                                                            |

| Large Signal Harmonic Distortion       | Dist             | -      | -80       | -       | dB        | 4v p-p Differential input at 660Hz                                                         |

| Large Signal Harmonic Distortion       | Dist             | -      | -80       | -       | dB        | 3v p-p single ended signal at 660Hz                                                        |

| Input Resistance                       | Rin              | -      | 126       | -       | Kohm      | Input to unity gain stage                                                                  |

| Input Capacitance                      | Cin              | -      | 2.0       | 5.0     | pF        |                                                                                            |

| Input Referred Noise Figure            | NF               | -      | 0.16      | -       | μV/sqrtHz | Applies to Audio frequency range<br>See graphical data on page 18                          |

| Signal-To Noise Ratio and Distortion   | SINAD            | -      | 84        | -       | dB        | Input signal = 1400 mV p-p diff,<br>Audio frequency range<br>See graphical data on page 18 |

| Spurious Free Dynamic Range            | SFDR             | -      | 90        | -       | dB        | Input signal =1400 mV p-p differential See graphical data on page 18                       |

# Input Differential Voltage Mode, Amplifier OFF, Filter OFF and Unity Gain Stage OFF

| Parameter                              | Symbol           | Min    | Тур                    | Max | Unit  | Comment                                                                                                                                                 |

|----------------------------------------|------------------|--------|------------------------|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Range                            | Vina<br>Vdiffina | See an | See analog input above |     | V     |                                                                                                                                                         |

| Equivalent Input Offset                | Vos              | N/A    | N/A                    | N/A | mV    | See CAM Op Amp                                                                                                                                          |

| Offset Voltage Temperature Coefficient | Voffsettc        | N/A    | N/A                    | N/A | μV/°C | See CAM Op Amp.<br>from -40°C to 125°C                                                                                                                  |

| Input Frequency                        | Fain             | -      | -                      | 8   | MHz   | Dependant upon CAM                                                                                                                                      |

| Power Supply Rejection Ratio           | PSRR             | N/A    | N/A                    | N/A | dB    | See CAM Op Amp                                                                                                                                          |

| Large Signal Harmonic Distortion       | Dist             | -      | -85                    | -   | dB    | See CAM Op Amp                                                                                                                                          |

| Input Resistance                       | Rin              | -      | -                      | -   | Mohm  | Input to CAM directly (Input cell<br>bypass mode). This variable is<br>influenced by CAB capacitor size,<br>CAB clock frequency and CAB<br>architecture |

| Input Capacitance                      | Cin              | -      | -                      | -   | pF    | Input to CAM directly (Input cell bypass mode) This variable is influenced by CAB capacitor size, CAB clock frequency and CAB architecture              |

## **Analog Outputs**

(See "Output Cell" section in the AN120E04/AN220E04 user manual for more details)

| Parameter                                           | Symbol    | Min | Тур | Max    | Unit | Comment                   |

|-----------------------------------------------------|-----------|-----|-----|--------|------|---------------------------|

| High Precision Output Range <sup>c</sup>            | Vouta     | 0.5 | -   | 3.5    | V    | VMR +/- 1.5v              |

| Standard Precision Output Range <sup>d</sup>        | Vouta     | 0.1 | -   | 3.9    | V    | VMR +/- 1.9v              |

| High Precision Differential Output °                | Vdiffouta | -   | -   | +/-3.0 | V    | Common mode voltage = 2 V |

| Standard precision Differential Output <sup>d</sup> | Vdiffouta | -   | -   | +/-3.8 | V    | Common mode voltage = 2 V |

| Common Mode<br>Voltage                              | Vcm       | 1.9 | 2.0 | 2.1    | V    |                           |

# Output Voltage Mode and Filter ON, Corner Frequency 470KHz

| Parameter                                                    | Symbol           | Min     | Тур        | Max   | Unit      | Comment                                                                                                                                                               |

|--------------------------------------------------------------|------------------|---------|------------|-------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Input Range                                                  | Vina<br>Vdiffina | See ana | alog input | above | V         |                                                                                                                                                                       |

| Equivalent Input Offset                                      | Vos              | -       | 5          | 15    | mV        |                                                                                                                                                                       |

| Offset Voltage Temperature<br>Coefficient                    | Voffsettc        |         | 0.05       | 1.0 " | mV/°C     | from -40°C to 125°C I measured at filter corner: 470Khz II maximum at filter corner: 76KHz                                                                            |

| Output Frequency                                             | Faout            | ı       | -          | -     | MHz       | Output filter frequency will define the maximum frequency Input filter is recommended to be >30x higher then the max input frequency, for good distortion performance |

| Power Supply Rejection Ratio                                 | PSRR             | 60      | -          | -     | dB        | d.c.<br>a.c. See graphical data on page 19                                                                                                                            |

| Large Signal Harmonic Distortion                             | Dist             | -       | -82        | -     | dB        | 4v p-p Differential input at 660Hz<br>Filter corner frequency 470KHz                                                                                                  |

| Input Low Pass Filter (Anti-Alias) Corner Frequency Settings | Ffiltcorner      | 76      | -          | 470   | KHz       |                                                                                                                                                                       |

| Output Load <sup>c e</sup>                                   | Rload            | 0.1     | -          | -     | Mohm      |                                                                                                                                                                       |

| Output Load <sup>c e</sup>                                   | Cload            | -       | -          | 50    | pF        |                                                                                                                                                                       |

| Output Load <sup>d e</sup>                                   | Rload            | 1       | 10         | -     | Kohm      | Additional loading causes internal voltage drops across output stage and series resistances The output stage has a small signal output impedance of approx 100hm      |

| Output Load <sup>d e</sup>                                   | Cload            | -       | -          | 100   | pF        |                                                                                                                                                                       |

| Common Mode Rejection Ratio                                  | CMRR             | -       | 56         | -     | dB        |                                                                                                                                                                       |

| Input Referred Noise Figure                                  | NF               | -       | 0.22       | -     | μV/sqrtHz | Output filter corner fc = 470KHz Applies to Audio frequency range See graphical data on page 18                                                                       |

| Signal-To Noise Ratio and Distortion                         | SINAD            | -       | 82         |       | dB        | Input signal = 1400 mV p-p diff,<br>Audio frequency range<br>See graphical data on page 18                                                                            |

| Spurious Free Dynamic Range                                  | SFDR             | -       | 90         | -     | dB        | Input signal =1400 mV p-p diff<br>See graphical data on page 18                                                                                                       |

<sup>&</sup>lt;sup>c</sup>. High precision operating range provides optimal linearity and dynamic range.

<sup>°.</sup> High precision operating range provides optimal linearity and dynamic range. d. Standard precision operating range provides maximum dynamic range and reduced linearity.

d. Standard precision operating range provides maximum dynamic range and reduced linearity.

e. The maximum load for an analog output is 50 pF // 100 Kohms. This load maybe with respect to analog ground VMR or AVSS.

**Output Voltage Mode and Filter Off (Bypass Mode)**

| Parameter                              | Symbol           | Min                    | Тур | Max | Unit  | Comment                                                                                                                               |

|----------------------------------------|------------------|------------------------|-----|-----|-------|---------------------------------------------------------------------------------------------------------------------------------------|

| Input Range                            | Vina<br>Vdiffina | See analog input above |     |     | V     |                                                                                                                                       |

| Equivalent Input Offset                | Vos              | N/A                    | N/A | N/A | mV    | See CAM Op Amp                                                                                                                        |

| Offset Voltage Temperature Coefficient | Voffsettc        | N/A                    | N/A | N/A | mV/°C | See CAM Op Amp                                                                                                                        |

| Output Frequency ce                    | Faout            | -                      | -   | 4   | MHz   |                                                                                                                                       |

| Output Frequency df                    | Faout            | -                      | -   | 8   | MHz   | The realizable output frequency is limited to approx <2MHz due to CAM signal processing which is based on sampled data architectures. |

| Power Supply Rejection Ratio           | PSRR             | N/A                    | N/A | N/A | dB    | See CAM Op Amp                                                                                                                        |

| Large Signal Harmonic Distortion       | Dist             | -                      | -85 | -   | dB    |                                                                                                                                       |

| Output Load                            | Rload            | N/A                    | N/A | N/A | Mohm  | See CAM Op Amp                                                                                                                        |

| Output Load                            | Cload            | N/A                    | N/A | N/A | pF    | See CAM Op Amp                                                                                                                        |

- <sup>c</sup>. High precision operating range provides optimal linearity and dynamic range.

- d. Standard precision operating range provides maximum dynamic range and reduced linearity.

- . The maximum load for an analog output is 50 pF // 100 Kohms. This load maybe with respect to analog ground VMR or AVSS.

- f. The maximum load for an analog output is 100 pF // 100 Kohms. This load must be differential and with respect to analog ground(VMR).

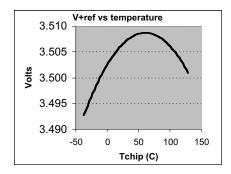

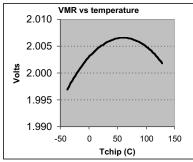

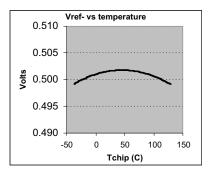

## VMR (Voltage Mid Rail) and VREF (Reference Voltage) Ratings

| Parameter                                               | Symbol  | Min   | Тур   | Max   | Unit | Comment                                                      |

|---------------------------------------------------------|---------|-------|-------|-------|------|--------------------------------------------------------------|

| VMR Output Voltage                                      | Vvmr    | 1.925 | 2.01  | 2.075 | V    | At 25°C, Vdd=5.00 volts                                      |

| VREF+ Output Voltage                                    | Vref+   | 3.4   | 3.51  | 3.6   | V    | At 25°C, Vdd=5.00 volts                                      |

| VREF- Output Voltage                                    | Vref-   | 0.45  | 0.505 | 0.55  | V    | At 25°C, Vdd=5.00 volts                                      |

| Output Voltage Deviation VREF+, VMR, VREF-              | Vrefout | -     | 0.5   | 1     | %    | Over process and supply voltage corners                      |

| Voltage Temperature<br>Coefficient<br>VREF+, VMR, VREF- | Vreftc  | -     | -     | -     | -    | See typical graphical data below -40°C to 125°C <sup>f</sup> |

| Power Supply Rejection Ratio, VMR                       | PSSR    | 60    | -     | -     | dB   |                                                              |

| Power Supply Rejection Ratio<br>Vref+ and Vref-         | PSSR    | 75    | -     | -     | dB   |                                                              |

| Start Up Time                                           | Tstart  | -     | -     | 1     | ms   | Assuming recommended capacitors                              |

# CAB (Configurable Analog Block) Differential Operational Amplifier

| Parameter                                              | Symbol    | Min | Тур  | Max    | Unit      | Comment                                                                                                                                                          |

|--------------------------------------------------------|-----------|-----|------|--------|-----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| High Precision Input/Output<br>Range <sup>c</sup>      | Vinouta   | 0.5 | -    | 3.5    | V         | VMR +/- 1.5v                                                                                                                                                     |

| Standard Precision Input/Output Range <sup>d</sup>     | Vinouta   | 0.1 | -    | 3.9    | V         | VMR +/-1.9v                                                                                                                                                      |

| High Precision. Differential Input/Output <sup>c</sup> | Vdiffioa  | -   | -    | +/-3.0 | V         | Common mode voltage = 2 V                                                                                                                                        |

| Standard Precision Differential Input/Output d         | Vdiffioa  | -   | -    | +/-3.8 | V         | Common mode voltage = 2 V                                                                                                                                        |

| Common Mode Input Voltage<br>Range <sup>d</sup>        | Vcm       | 0   | 2.0  | 4      | V         |                                                                                                                                                                  |

| Common Mode Output Voltage<br>Range                    | Vcm       | 1.9 | 2.0  | 2.1    | V         |                                                                                                                                                                  |

| Equivalent Input Voltage Offset.                       | Voffset   | 0.1 | 5    | 15     | mV        | Some CAMs (Configurable<br>Analog Modules) can inherently<br>compensate                                                                                          |

| Offset Voltage Temperature<br>Coefficient              | Voffsettc | -   | 1    | 10     | μV/°C     | from -40°C to 125°C some<br>CAMs (Configurable Analog<br>Modules) can inherently<br>compensate                                                                   |

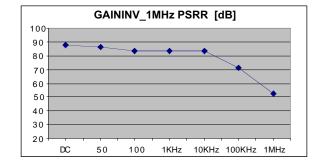

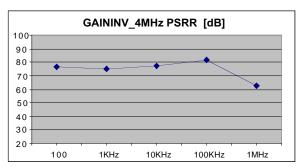

| Power Supply Rejection Ratio                           | PSSR      | -   | 80   | -      | dB        | Variation between CAMs is expected because of variations in architecture                                                                                         |

| Common Mode Rejection Ratio                            | CMRR      | -   | 77   | -      | dB        | Example 1 GainInv CAM CAM clock = 1MHz CAM parameter settings Gain = 1                                                                                           |

| Common Mode Rejection Ratio                            | CMRR      | -   | 60   | -      | dB        | Example 2 Filterbiquad Setting = Low pass filter CAM clock = 1MHz CAM parameter settings Gain = 1, Corner frequency = 50KHz Quality Factor = 0.707               |

| Differential Slew Rate, Internal                       | Slew      | -   | 50   | -      | V/µsec    | Applicable when the OpAmp load is internal to the FPAA                                                                                                           |

| Differential Slew Rate, External                       | Slew      | -   | 10   | -      | V/µsec    | Applicable when the OpAmp driving signal out of the FPAA package                                                                                                 |

| Unity Gain Bandwidth,<br>Full Power Mode.              | UGB       | -   | 50   | -      | MHz       | Applicable when sourcing and loading the OpAmp with a load internal to the FPAA                                                                                  |

| Input Impedance, Internal                              | Rin       | 10  | -    | -      | Mohm      |                                                                                                                                                                  |

| Output Impedance, Internal                             | Rout      | -   | -    | -      | Ohms      | The OpAmp output is designed to drive all internal nodes, these are dominantly capacitive loads                                                                  |

| Output Impedance, External                             | Rout      | -   | -    | -      | Ohms      | Output to an FPAA output pin<br>(ouput cell bypass mode). This<br>variable is influenced by CAB<br>capacitor size, CAB clock<br>frequency and CAB architecture   |

| Output Load, External <sup>c e</sup>                   | Rload     | 0.1 | -    | -      | Mohm      |                                                                                                                                                                  |

| Output Load, External ce                               | Cload     | -   | -    | 50     | pF        |                                                                                                                                                                  |

| Output Load, External <sup>d e f</sup>                 | Rload     | 1   | 10   | -      | Kohm      | Additional loading causes internal voltage drops across output stage and series resistances The output stage has a small signal output impedance of approx 10ohm |

| Output Load, External <sup>d e f</sup>                 | Cload     | -   | -    | 50     | pF        |                                                                                                                                                                  |

| Noise Figure <sup>9</sup>                              | Noise     | -   | 0.13 | -      | μV/sqrtHz | Example1 GainInv CAM<br>CAM clock = 1MHz<br>Gain = 1                                                                                                             |

| Signal-To Noise Ratio and Distortion <sup>g</sup> | SINAD | - | 80 | - | dB | Input signal=1400 mV p-p<br>differential<br>Audio frequency range<br>Example. GainInv CAM<br>CAM clock = 1MHz<br>Gain = 1  |

|---------------------------------------------------|-------|---|----|---|----|----------------------------------------------------------------------------------------------------------------------------|

| Spurious Free Dynamic Range <sup>9</sup>          | SFDR  | - | 92 | - | dB | Input signal=1400 mV p-p<br>differential,<br>Audio frequency range<br>Example. GainInv CAM<br>CAM clock = 1MHz<br>Gain = 1 |

- <sup>c</sup>. High precision operating range provides optimal linearity and dynamic range.

- d. Standard precision operating range provides maximum dynamic range and reduced linearity.

- °. The maximum load for an analog output is 50 pF || 100 Kohms. This load may be with respect to analog ground VMR or AVSS.

- 1. Using the FPAA with CAB Op Amp's driving directly off-chip, requires care, full characterization of the performance of each application circuit by the circuit designer is necessary.

- This specification parameter can only be characterized when a circuit topology is configured onto the CAB differential amplifier architecture.

The figure provided here is an representative on the performance of one specific CAM, as specified in the comments.

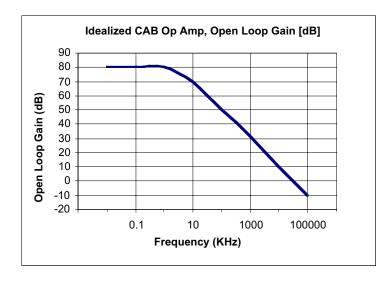

The idealized open loop gain plot is provided for information only. This information is associated with the FPAA in full power mode of operation. The FPAA operation amplifier open loop gain cannot be observed nor used when associated with external connections to the device. Internal reprogrammable routing impedances and switched capacitor circuit architecture using this operational amplifier limit the effective usable bandwidth of a circuit realized in the FPAA to less than 2MHz.

# CAB (Configurable Analog Block) Differential Comparator

| Parameter                                                  | Symbol    | Min     | Тур      | Max     | Unit  | Comment                                                              |

|------------------------------------------------------------|-----------|---------|----------|---------|-------|----------------------------------------------------------------------|

| Input Range, Internal                                      | Vina      | 0.1     | -        | 3.9     | V     |                                                                      |

| Input Range, External                                      | Vina      | 0.0     | -        | Vdd     | V     |                                                                      |

| Differential Input, Internal                               | Vdiffina  | -       | -        | +/-3.8  | V     | Common mode voltage = 2 V                                            |

| Differential Input, External                               | Vdiffina  | +/- 0.0 | -        | +/- Vdd | V     | -                                                                    |

| Common Mode Output Voltage<br>Range, Internal <sup>c</sup> | Vcm       | 1.9     | 2.0      | 2.1     | V     |                                                                      |

| Common Mode Input Voltage<br>Range, External <sup>c</sup>  | Vcm       | 0       | 2.0      | 4       | V     |                                                                      |

| Common Mode Input Voltage, External <sup>d</sup>           | Vcm       | 0       | -        | 5       | V     | The comparator will function correctly                               |

| Differential Output                                        | Voutdiff  | -       | -        | +/-5    | V     |                                                                      |

| Single Pin Output (Ox1P)                                   | Vout      | 0       | -        | 5       | V     |                                                                      |

| Input Voltage Offset                                       | Voffcomp  | -       | 2        | 10      | mV    | Zero hysterisis                                                      |

| Offset Voltage Temperature Coefficient                     | Voffsettc | -       | 1        | 10      | μV/°C | from -40°C to 125°C,<br>Zero Hysterisis                              |

| Setup Time, Internal                                       | Tsetint   | -       | -        | 125     | nsec  |                                                                      |

| Setup Time, External                                       | Tsetext   | -       | -        | 500     | nsec  |                                                                      |

| Delay Time                                                 | Tdelay    | _Td+25  | -        | 1_Td+25 | nsec  | Td = 1/Fc Fc = master clock frequency                                |

| Output Load                                                | Rload     | 10      | -        | -       | Kohm  | Applies if comparator drive off chip with output cell in bypass mode |

| Output Load                                                | Cload     | -       | -        | 50      | pF    | Applies if comparator drive off chip with output cell in bypass mode |

| Differential Variable Reference Voltage Settings           | CompVref  | 0       | -        | +/-4.0  | V     |                                                                      |

| Differential Hysteresis                                    | Hysta1    | -       | Voffcomp | -       | mV    | Hysteresis setting = zero                                            |

| Differential Hysteresis                                    | Hysta2    | -       | 20       | -       | mV    | Hysteresis setting = 10mV                                            |

| Differential Hysteresis                                    | Hysta3    | -       | 40       | -       | mV    | Hysteresis setting = 20mV                                            |

| Differential Hysteresis                                    | Hysta4    | -       | 80       | -       | mV    | Hysteresis setting = 40mV                                            |

| Hysteresis Setting Accuracy                                | Hystb     | -       | 25       | -       | %     | -                                                                    |

| Hysteresis Temperature<br>Coefficient                      | Hysttc1   | -       | 5        | -       | μV/°C | Hysteresis setting = zero                                            |

| Hysteresis Temperature<br>Coefficient                      | Hysttc2   | -       | 50       | -       | μV/°C | Hysteresis setting = 10mV                                            |

| Hysteresis Temperature<br>Coefficient                      | Hysttc3   | -       | 100      | -       | μV/°C | Hysteresis setting = 20mV                                            |

| Hysteresis Temperature Coefficient                         | Hysttc4   | -       | 200      | -       | μV/°C | Hysteresis setting = 40mV                                            |

<sup>°.</sup> High precision operating range provides optimal linearity and dynamic range.

d. Standard precision operating range provides maximum dynamic range and reduced linearity.

#### **ESD Characteristics**

| Pin Type              | Human<br>Body<br>Model | Machine<br>Model | Charged<br>Device<br>Model |

|-----------------------|------------------------|------------------|----------------------------|

| Digital Inputs        | 4000V                  | 250V             | 4kV                        |

| Digital Outputs       | 4000V                  | 250V             | 4kV                        |

| Digital Bidirectional | 4000V                  | 250V             | 4kV                        |

| Digital Open Drain    | 4000V                  | 250V             | 4kV                        |

| Analog Inputs         | 2000V                  | 200V             | 4kV                        |

| Analog Outputs        | 1500V                  | 100V             | 4kV                        |

| Reference Voltages    | 1500V                  | 100V             | 4kV                        |

The AN221E02 is an ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000V readily accumulate on the human body and test equipment and can discharge without detection. Although the AN221E02 device features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

### Power Consumption - Low Power Mode

| Parameter                                    | Symbol | Min | Тур | Max | Unit  | Comment                 |

|----------------------------------------------|--------|-----|-----|-----|-------|-------------------------|

| Minimum Power <sup>1a</sup>                  | ldd    | -   | 0.2 | -   | mA    | Vdd=5.00 volts, Tj=25°C |

| Low Power Nominal 50%<br>Power <sup>1b</sup> | ldd    | -   | 25  | 30  | mA    | Vdd=5.00 volts, Tj=25°C |

| Low Power Maximum Power <sup>1c</sup>        | ldd    | -   | 42  | 47  | mA    | Vdd=5.00 volts, Tj=25°C |

| Temperature Coefficient                      | -      | -   | -2  | -10 | μΑ/°C |                         |

<sup>&</sup>lt;sup>1a</sup>. External clock, all analog function disabled, memory active.

#### **Power Consumption – Full Power Mode**

| Parameter                                       | Symbol | Min | Тур | Max | Unit | Comment                 |

|-------------------------------------------------|--------|-----|-----|-----|------|-------------------------|

| Full Power Mode Minimum Power <sup>2a</sup>     | ldd    | ı   | 1.5 | -   | mA   | Vdd=5.00 volts, Tj=25°C |

| Full Power Mode Nominal 50% Power <sup>2b</sup> | ldd    | ı   | 80  | 90  | mA   | Vdd=5.00 volts, Tj=25°C |

| Full Power Mode Maximum Power <sup>2c</sup>     | ldd    | -   | 150 | 160 | mA   | Vdd=5.00 volts, Tj=25°C |

<sup>&</sup>lt;sup>2a</sup>. AN220E04 Crystal Oscillator, all analog functions disabled, memory active.

FPAA active elements – Two core op-amps (low power mode), one comparator, one input (bypass mode), one output filter and differential to single-ended converter (low power mode).

FPAA active elements – Four core op-amps (low power mode), two comparators (one using SAR), two inputs (bypass mode), two output filters and two differential to single-ended converters (low power mode).

<sup>&</sup>lt;sup>2b</sup>. FPAA active elements – Two core op-amps, one comparator, one input filter and chopper amplifier, one output filter and differential to single-ended converter.

<sup>&</sup>lt;sup>2c</sup>. FPAA active elements – Four core op-amps, two comparators (one using SAR), two Input filters and two chopper amplifiers, two output filters and two differential to single-ended converters.

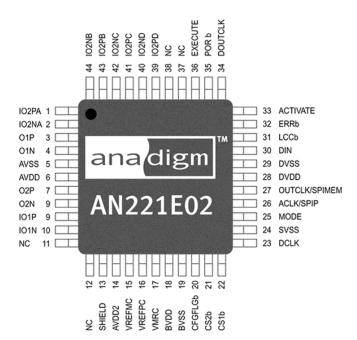

# **PINOUT**

| Pin<br>Numb<br>er | Pin<br>Name       | Pin<br>Type                | Comments                                                                                                                                                                                                                                |

|-------------------|-------------------|----------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                 | I2PA              | Analog IN+                 |                                                                                                                                                                                                                                         |

| 2                 | I2NA              | Analog IN-                 |                                                                                                                                                                                                                                         |

| 3                 | O1P               | Analog OUT+                |                                                                                                                                                                                                                                         |

| 4                 | O1N               | Analog OUT-                |                                                                                                                                                                                                                                         |

| 5                 | AVSS              | Analog Vss                 |                                                                                                                                                                                                                                         |

| 6                 | AVDD              | Analog Vdd                 |                                                                                                                                                                                                                                         |

| 7                 | O2P               | Analog OUT Analog OUT      |                                                                                                                                                                                                                                         |

| 9                 | O2N<br>I1P        | Analog UU1 Analog IN+      |                                                                                                                                                                                                                                         |

| 10                | I1N               | Analog IN+                 |                                                                                                                                                                                                                                         |

| 11                | NC                | Analog IN-                 | Not Connected                                                                                                                                                                                                                           |

| 12                | NC                |                            | Not Connected                                                                                                                                                                                                                           |

| 13                | SHIELD            | Analog Vdd                 | Low noise Vdd bias for capacitor array n-wells                                                                                                                                                                                          |

| 14                | AVDD2             | Analog Vdd                 | Analog power                                                                                                                                                                                                                            |

| 15                | VREFMC            | Vref                       | Attach filter capacitor for VREF-                                                                                                                                                                                                       |

| 16                | VREFPC            | Vref                       | Attach filter capacitor for VREF+                                                                                                                                                                                                       |

| 17                | VMRC              | Vref                       | Attach filter capacitor for VMR (Voltage Main Reference)                                                                                                                                                                                |

| 18                | BVDD              | Analog Vdd                 | Analog power for bandgap Vref Generators                                                                                                                                                                                                |

| 19                | BVSS              | Analog Vss                 | Analog ground for bandgap Vref Generators                                                                                                                                                                                               |

| 20                | CFGFLGb           | Digital IN                 | In multi-device systems 0, Ignore incoming data (unless currently addressed) 1, Pay attention to incoming data (watching for address)                                                                                                   |

| 21                | CS2b              | Digital OUT  Digital IN    | O, Device is being configured     Z, Device is not being configured (if internal pullup is selected)     O, Chip is selected                                                                                                            |

| 22                | CS1b              | Digital IN                 | 1, Chip is not selected     0, Allow configuration to proceed                                                                                                                                                                           |

| 22                | CSTD              | (during config) Digital IN | 1, Hold off configuration Passes read-back data through to LCC_B pin                                                                                                                                                                    |

|                   |                   | (after config)_            |                                                                                                                                                                                                                                         |

| 23                | DCLK              | Digital IN                 |                                                                                                                                                                                                                                         |

| 24                | SVSS              | Digital Vss                | Digital ground - substrate tie                                                                                                                                                                                                          |

| 25                | MODE              | Digital IN                 | 0, Synchronous serial interface 1, SPI EPROM Interface                                                                                                                                                                                  |

| 26                | ACLK / SPIP       | Digital IN                 | MODE = 0, analog clock < 40 MHz                                                                                                                                                                                                         |

| 27                | OUTCLK /          | Digital OUT Digital OUT    | MODE = 1, SPI EPROM or serial EPROM clock  During power-up, sources SPI EPROM initialization command string                                                                                                                             |

| 27                | SPIMEM            | Digital OUT                | After power-up, sources any of the four internal analog clocks                                                                                                                                                                          |

| 28                | DVDD              | Digital Vdd                | After power-up, sources any of the four internal arialog clocks                                                                                                                                                                         |

| 29                | DVSS              | Digital Vss                |                                                                                                                                                                                                                                         |

| 30                | DIN               | Digital IN                 | Serial configuration data input                                                                                                                                                                                                         |

| 31                | LCCb              | Digital OUT                | 1, Local configuration is needed. Once configuration is completed, it is a registered version of CS1b or if the device is addressed for read, it serves as serial data out port                                                         |

| 32                | ERRb              | Digital IN (monitored OUT) | 0, Initiate reset 1, No action                                                                                                                                                                                                          |

|                   |                   | Digital OUT                | 0, Error condition Z, No error condition (external pullup required)                                                                                                                                                                     |