# AC '97 SoundMAX® Codec

AD1985

#### **AC'97 2.3 COMPLIANT FEATURES**

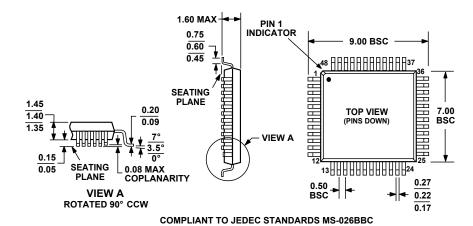

48-lead LQFP package

6 DAC channels for 5.1 Surround

Greater than 90 dB dynamic range

20-bit resolution on all DACs

S/PDIF Output

Integrated stereo headphone amplifiers

Variable rate audio

Double rate audio (fs = 96 kHz)

Line-level mono phone input

High quality CD mixer input

Selectable MIC input with preamp

AUX and Line In stereo inputs

External amplifier power down (EAPD)

Power management modes

Jack sensing and peripheral enumeration/identification

#### **ENHANCED FEATURES**

Integrated parametric equalizer (EQ)

Stereo microphone with preamplifiers

Integrated PLL for system clocking

Variable sample rate 7 kHz to 96 kHz

7 kHz to 48 kHz in 1 Hz increments

96 kHz for double rate audio

Software enabled outputs for jack sharing

Advanced jack sense with auto topology switching Software enabled  $V_{\text{REFOUT}}$  for microphones and external power amp

Auto down-mix and channel spreading

Microphone to mono output

Stereo microphone analog passthrough to outputs

Built-in stereo microphone and Center/LFE pin sharing

Selectable Center/LFE tip/ring swapping to support various

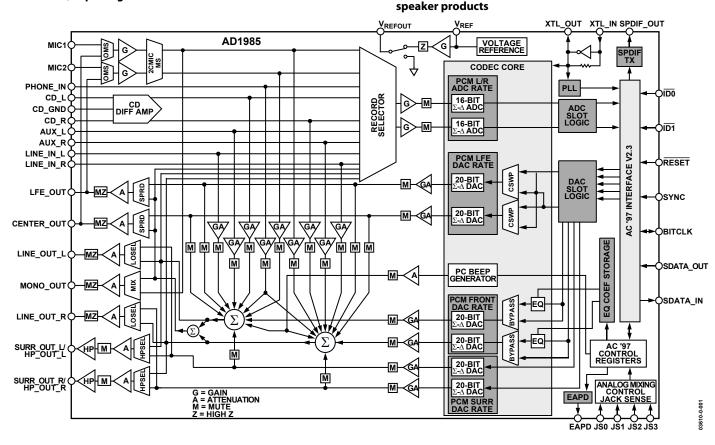

Figure 1. Functional Block Diagram

Rev. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective companies.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 www.analog.com

Fax: 781.326.8703 © 2003 Analog Devices, Inc. All rights reserved.

# **TABLE OF CONTENTS**

| Detailed Functional Block Diagram               |  |

|-------------------------------------------------|--|

| AD1985—Specifications                           |  |

| Absolute Maximum Ratings                        |  |

| Pin Configuration And Functional Descriptions10 |  |

| Pin Descriptions   | 10 |

|--------------------|----|

| Outline Dimensions | 47 |

| Ordering Guide     | 47 |

### **REVISION HISTORY**

Revision 0: Initial Version

## **DETAILED FUNCTIONAL BLOCK DIAGRAM**

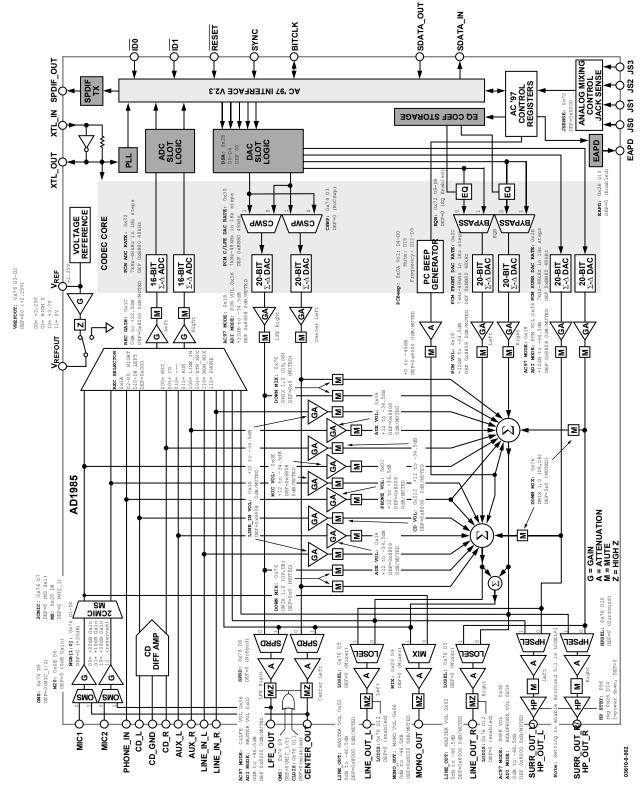

Figure 2. Detailed Functional Block Diagram

# AD1985—SPECIFICATIONS

### **Test Conditions unless Otherwise Noted**

| Parameter                          | Value/Condition                     | Unit    |  |  |

|------------------------------------|-------------------------------------|---------|--|--|

| Temperature                        | 25                                  | °C      |  |  |

| Digital Supply (DV <sub>DD</sub> ) | 3.3                                 | V       |  |  |

| Analog Supply (AV <sub>DD</sub> )  | 5.0                                 | V       |  |  |

| Sample Rate (fs)                   | 48                                  | kHz     |  |  |

| Input Sine Wave Signal             | 1,008                               | Hz      |  |  |

| Analog Output Pass-Band            | 20 to 20,000                        | Hz      |  |  |

|                                    | Calibrated                          |         |  |  |

|                                    | Output –3 dB relative to full scale |         |  |  |

| DAC Test Conditions                | 10 kΩ output load: line             |         |  |  |

| DAC Test Conditions                | 32 Ω output load: headphon          |         |  |  |

|                                    | 2 kΩ output load: center            | and LFE |  |  |

|                                    | 47.5 kΩ output load: moi            | 10      |  |  |

|                                    | Calibrated                          |         |  |  |

| ADC Test Conditions                | 0 dB PGA gain                       |         |  |  |

|                                    | Input –3 dB relative to full scale  |         |  |  |

| Clock                              | 24.576 MHz                          |         |  |  |

### **ANALOG INPUT**

| Parameter                      | Min | Тур   | Max | Unit  |

|--------------------------------|-----|-------|-----|-------|

| INPUT VOLTAGE                  |     |       |     |       |

| LINE_IN, CD, AUX, PHONE_IN     |     | 1     |     | V rms |

|                                |     | 2.83  |     | V p-p |

| MIC_IN with +30 dB Preamp      |     | 0.032 |     | V rms |

|                                |     | 0.089 |     | V p-p |

| MIC_IN with +20 dB Preamp      |     | 0.1   |     | V rms |

|                                |     | 0.283 |     | V p-p |

| MIC_IN with +10 dB Preamp      |     | 0.316 |     | V rms |

|                                |     | 0.894 |     | V p-p |

| MIC_IN with 0 dB Preamp        |     | 1     |     | V rms |

|                                |     | 2.83  |     | V p-p |

| Input Impedance <sup>1</sup>   |     | 20    |     | kΩ    |

| Input Capacitance <sup>1</sup> |     | 5     | 7.5 | pF    |

<sup>&</sup>lt;sup>1</sup>Guaranteed, not tested.

### **MASTER VOLUME**

| Parameter                                                 | Min | Тур  | Max | Unit |

|-----------------------------------------------------------|-----|------|-----|------|

| Step Size (Line Out, Mono Out, Surround Out, Center, LFE) |     | 1.5  |     | dB   |

| Output Attenuation Range (0 dB to -46.5 dB)               |     | 46.5 |     | dB   |

| Mute Attenuation of 0 dB Fundamental <sup>1</sup>         | 80  |      |     | dB   |

<sup>&</sup>lt;sup>1</sup>Guaranteed, not tested.

### PROGRAMMABLE GAIN AMPLIFIER—ADC

| Parameter                    | Min Typ | Max | Unit |

|------------------------------|---------|-----|------|

| Step Size (0 dB to +22.5 dB) | 1.5     |     | dB   |

| PGA Gain Range Span          | 22.5    |     | dB   |

### ANALOG MIXER—INPUT GAIN/AMPLIFIERS/ATTENUATORS

| Parameter                                          | Min | Тур  | Max | Unit |

|----------------------------------------------------|-----|------|-----|------|

| Signal-to-Noise Ratio (SNR)                        |     |      |     |      |

| CD to LINE_OUT                                     |     | 90   |     | dB   |

| LINE, AUX, PHONE, to LINE_OUT                      |     | 85   |     | dB   |

| MIC1 or MIC2 to LINE_OUT                           |     | 80   |     | dB   |

| Step Size: All Mixer Inputs, except PC Beep        |     | 1.5  |     | dB   |

| Input Gain/Attenuation Range (+12 dB to -34.5 dB): |     |      |     |      |

| All Mixer Inputs                                   |     | 46.5 |     | dB   |

### **DIGITAL DECIMATION AND INTERPOLATION FILTERS**<sup>1</sup>

| Parameter                            | Min              | Тур               | Max              | Unit |

|--------------------------------------|------------------|-------------------|------------------|------|

| Pass Band                            | 0                |                   | $0.4 \times F_S$ | Hz   |

| Pass-Band Ripple                     |                  |                   | ±0.09            | dB   |

| Transition Band                      | $0.4 \times F_S$ |                   | $0.6 \times F_s$ | Hz   |

| Stop Band                            | $0.6 \times F_S$ |                   | ∞                | Hz   |

| Stop-Band Rejection                  | -74              |                   |                  | dB   |

| Group Delay                          |                  | 16/F <sub>s</sub> |                  | S    |

| Group Delay Variation over Pass Band |                  | 0                 |                  | μs   |

#### **ANALOG-TO-DIGITAL CONVERTERS**

| Parameter                                                             | Min | Тур        | Max  | Unit |

|-----------------------------------------------------------------------|-----|------------|------|------|

| Resolution                                                            |     | 16         |      | Bits |

| Total Harmonic Distortion (THD)                                       |     | -85        |      | dB   |

| Dynamic Range (–60 dB in THD+N; Referenced to Full-Scale; A-Weighted) |     | 84         |      | dB   |

| Signal-to-Intermodulation Distortion <sup>1</sup> (CCIF Method)       |     | 85         |      | dB   |

| ADC Crosstalk <sup>1</sup>                                            |     |            |      |      |

| Line Inputs                                                           |     | -85        |      | dB   |

| (Input L, Ground R, Read R; Input R, Ground L Read L)                 |     |            |      |      |

| LINE_IN to Other                                                      |     | <b>-95</b> |      | dB   |

| Gain Error (Full-Scale Span Relative to Nominal Input Voltage)        |     |            | ±10  | %    |

| Interchannel Gain Mismatch (Difference of Gain Errors)                |     |            | ±0.5 | dB   |

| ADC Offset Error <sup>1</sup>                                         |     |            | ±5   | mV   |

### **DIGITAL-TO-ANALOG CONVERTERS**

| Parameter                                                                                         | Min Typ | Max  | Unit |

|---------------------------------------------------------------------------------------------------|---------|------|------|

| Resolution                                                                                        | 20      |      | Bits |

| Total Harmonic Distortion (THD); LINE_OUT, C/LFE                                                  | -90     |      | dB   |

| Total Harmonic Distortion (THD); HP_OUT                                                           | -75     |      | dB   |

| Dynamic Range (–60 dB in THD+N; Referenced to Full-Scale; A-Weighted)                             | 90      |      | dB   |

| Signal-to-Intermodulation Distortion <sup>1</sup> (CCIF Method)                                   | 100     |      | dB   |

| Gain Error (Output Full-Scale Voltage Relative to Nominal Output Full-Scale Voltage) <sup>2</sup> | ±10     |      | %    |

| Interchannel Gain Mismatch (Difference of Gain Errors)                                            |         | ±0.7 | dB   |

| DAC Crosstalk <sup>1</sup>                                                                        |         |      |      |

| (Input L, Zero R, Read R_OUT; Input R, Zero L, Read L_OUT                                         | -100    | )    | dB   |

| Total Out-of-Band Energy (Measured from $0.6 \times f_S$ to $100 \text{ kHz})^1$                  | -85     |      | dB   |

<sup>&</sup>lt;sup>1</sup>Guaranteed, not tested. <sup>2</sup>C/LFE specified with 10 kΩ load.

#### **ANALOG OUTPUT**

| Parameter                                                  | Min | Тур  | Max  | Unit  |

|------------------------------------------------------------|-----|------|------|-------|

| Full-Scale Output Voltage: LINE OUT, MONO OUT, CENTER, LFE |     | 1    |      | V rms |

|                                                            |     | 2.83 |      | V p-p |

| Output Impedance <sup>1</sup>                              |     | 300  | 500  | Ω     |

| External Load Impedance <sup>1</sup>                       | 2   | 10   |      | kΩ    |

| Output Capacitance <sup>1</sup>                            |     | 15   |      | pF    |

| External Load Capacitance                                  |     |      | 1000 | pF    |

| Full-Scale Output Voltage: HP_OUT                          |     | 1    |      | V rms |

|                                                            |     | 2.83 |      | V p-p |

| External Load Capacitance <sup>1</sup>                     |     |      | 1000 | pF    |

| External Load Impedance <sup>1</sup>                       | 32  |      |      | Ω     |

| $V_{REF}$                                                  | 2.1 | 2.25 | 2.4  | V     |

| $V_{REFOUT}$ (VREFH, VREFD = 00 in Reg 0x76)               |     | 2.25 |      | V     |

| V <sub>REFOUT</sub> (VREFH, VREFD = 10)                    |     | 3.70 |      | V     |

| V <sub>REFOUT</sub> (VREFH, VREFD = 11)                    |     | 0.0  |      | V     |

| V <sub>REFOUT</sub> Current Drive                          |     |      | 5    | mA    |

| Mute Click (Muted Output Unmuted Mid-Scale DAC Output)     |     | ±5   |      | mV    |

Note: Setting V<sub>REFOUT</sub> to 0 V reduces crosstalk when Center/LFE is sharing the MIC jack. The Center-LFE crosstalk should be better than -60 dB at 100 Hz when sharing with a stereo microphone application circuit.

### **STATIC DIGITAL SPECIFICATIONS**

| Parameter                                                       | Min                   | Тур | Max                   | Unit |

|-----------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| DIGITAL INPUTS/OUTPUTS                                          |                       |     |                       |      |

| High Level Input Voltage (V <sub>IH</sub> )                     | $0.65 \times DV_{DD}$ |     |                       | V    |

| Low Level Input Voltage (V <sub>IL</sub> )                      |                       |     | $0.35 \times DV_{DD}$ | V    |

| High Level Output Voltage ( $V_{OH}$ ), $I_{OH} = 2 \text{ mA}$ | $0.9 \times DV_{DD}$  |     |                       | V    |

| Low Level Output Voltage ( $V_{OL}$ ), $I_{OL} = 2 \text{ mA}$  |                       |     | $0.1 \times DV_{DD}$  | V    |

| Input Leakage Current                                           | -10                   |     | +10                   | μΑ   |

| Output Leakage Current                                          | -10                   |     | +10                   | μΑ   |

| Input/Output Pin Capacitance                                    |                       |     | 7.5                   | pF   |

### **POWER SUPPLY**

| Parameter                                                       | Min  | Тур | Max  | Unit |

|-----------------------------------------------------------------|------|-----|------|------|

| Power Supply Range—Analog (AV <sub>DD</sub> )                   | 4.5  |     | 5.5  | V    |

| Power Supply Range—Digital (DV <sub>DD</sub> )                  | 2.97 |     | 3.63 | V    |

| Power Dissipation—5 V/3.3 V                                     |      | 465 |      | mW   |

| Power Supply Rejection (100 mV p-p Signal @ 1 kHz) <sup>1</sup> |      | 40  |      | dB   |

### **POWER-DOWN STATES**<sup>2</sup>

| Parameter              | PR[K:I] <sup>3</sup> | PR[6:0] <sup>3</sup> | DV <sub>DD</sub> (3.3 V) Ty | p AV <sub>DD</sub> (5 V) Typ | Unit |

|------------------------|----------------------|----------------------|-----------------------------|------------------------------|------|

| Full Power-Up          | 000                  | 000 0000             | 55.5                        | 56.0                         | mA   |

| ADC                    | 000                  | 000 0001             | 47.4                        | 49.9                         | mA   |

| FRONT DAC              | 000                  | 000 0010             | 49.5                        | 47.9                         | mA   |

| CENTER DAC             | 001                  | 000 0000             | 55.5                        | 56.0                         | mA   |

| SURROUND DAC           | 010                  | 000 0000             | 49.0                        | 47.5                         | mA   |

| LFE DAC                | 100                  | 000 0000             | 55.1                        | 56.0                         | mA   |

| ADC + ALL DACs         | 111                  | 000 0011             | 15.8                        | 24.2                         | mA   |

| Mixer                  | 000                  | 000 0100             | 55.5                        | 34.3                         | mA   |

| ADC + Mixer            | 000                  | 000 0101             | 47.4                        | 27.4                         | mA   |

| ALL DACs + Mixer       | 111                  | 000 0110             | 34.1                        | 10.0                         | mA   |

| ADC + ALL DACs + Mixer | 111                  | 000 0111             | 14.3                        | 2.5                          | mA   |

| Standby                | 111                  | 011 1111             | 0.114                       | 0.004                        | mA   |

| Headphone Standby      | 000                  | 100 0000             | 55.5                        | 48.3                         | mA   |

¹Guaranteed, not tested.

²Currents measured with V<sub>REFOUT</sub> unloaded.

³PR bits are controlled in Registers 0x2A and 0x26.

### **CLOCK SPECIFICATIONS**

| Parameter                                             | Min | Тур      | Max | Unit |

|-------------------------------------------------------|-----|----------|-----|------|

| Input Clock Frequency (XTAL Mode or Clock Oscillator) |     | 24.576   |     | MHz  |

| Input Clock Frequency (Reference Clock Mode)          |     | 14.31818 |     | MHz  |

| Input Clock Frequency (USB Clock Mode)                |     | 48.000   |     | MHz  |

| Recommended Clock Duty Cycle                          | 40  | 50       | 60  | %    |

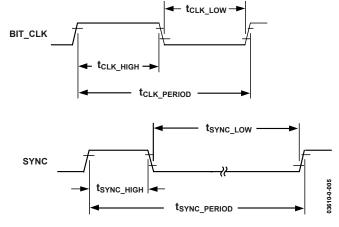

### **TIMING PARAMETERS**

(Guaranteed over Operating Temperature Range.)

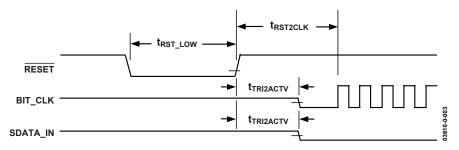

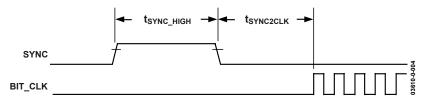

| Parameter                                                    | Symbol                  | Min   | Тур    | Max  | Unit |

|--------------------------------------------------------------|-------------------------|-------|--------|------|------|

| RESET Active Low Pulsewidth                                  | t <sub>RST_LOW</sub>    |       | 1.0    |      | μs   |

| RESET Inactive to SDATA_IN or BIT_CLK Active Delay           | t <sub>RST2CLK</sub>    | 162.8 |        |      | ns   |

| SYNC Active High Pulsewidth                                  | t <sub>SYNC_HIGH</sub>  |       | 1.3    |      | μs   |

| SYNC Low Pulsewidth                                          | t <sub>SYNC_LOW</sub>   |       | 19.5   |      | μs   |

| SYNC Inactive to BIT_CLK Startup Delay                       | t <sub>SYNC2CLK</sub>   | 162.8 |        |      | ns   |

| BIT_CLK Frequency                                            |                         |       | 12.288 |      | MHz  |

| BIT_CLK Period                                               | t <sub>CLK_PERIOD</sub> |       | 81.4   |      | ns   |

| BIT_CLK Output Jitter <sup>1,2</sup>                         |                         |       | 750    | 2000 | ps   |

| BIT_CLK High Pulsewidth                                      | t <sub>CLK_HIGH</sub>   | 33    | 42     | 48   | ns   |

| BIT_CLK Low Pulsewidth                                       | t <sub>CLK_LOW</sub>    | 33    | 38     | 48   | ns   |

| SYNC Frequency                                               |                         |       | 48.0   |      | kHz  |

| SYNC Period                                                  | tsync_period            |       | 20.8   |      | μs   |

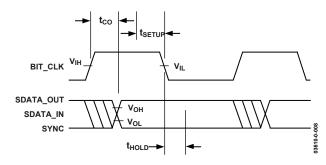

| Setup to Falling Edge of BIT_CLK                             | t <sub>SETUP</sub>      | 10    | 2.5    |      | ns   |

| Hold from Falling Edge of BIT_CLK                            | t <sub>HOLD</sub>       | 5     |        |      | ns   |

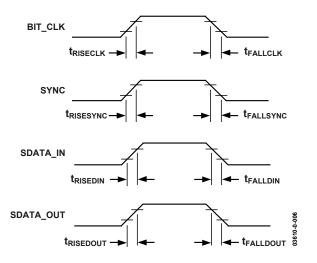

| BIT_CLK Rise Time                                            | t <sub>RISECLK</sub>    | 2     | 4      | 6    | ns   |

| BIT_CLK Fall Time                                            | <b>t</b> FALLCLK        | 2     | 4      | 6    | ns   |

| SYNC Rise Time                                               | t <sub>RISESYNC</sub>   | 2     | 4      | 6    | ns   |

| SYNC Fall Time                                               | <b>t</b> FALLSYNC       | 2     | 4      | 6    | ns   |

| SDATA_IN Rise Time                                           | t <sub>RISEDIN</sub>    | 2     | 4      | 6    | ns   |

| SDATA_IN Fall Time                                           | t <sub>FALLDIN</sub>    | 2     | 4      | 6    | ns   |

| SDATA_OUT Rise Time                                          | t <sub>RISEDOUT</sub>   | 2     | 4      | 6    | ns   |

| SDATA_OUT Fall Time                                          | <b>t</b> FALLDOUT       | 2     | 4      | 6    | ns   |

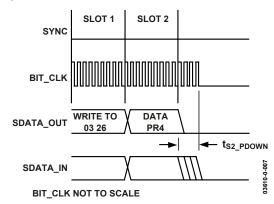

| End of Slot 2 to BIT_CLK, SDATA_IN Low                       | t <sub>S2_PDOWN</sub>   | 0     |        | 1.0  | μs   |

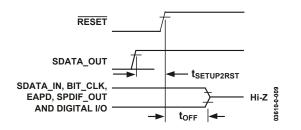

| Setup to Trailing Edge of RESET (Applies to SYNC, SDATA_OUT) | t <sub>SETUP2RST</sub>  | 15.0  |        |      | ns   |

| Rising Edge of RESET to High-Z Delay                         | t <sub>OFF</sub>        |       |        | 25.0 | ns   |

| Propagation Delay                                            |                         |       |        | 15   | ns   |

| RESET Rise Time                                              |                         |       |        | 50   | ns   |

| Output Valid Delay from Rising Edge of BIT_CLK to SDI Valid  | tco                     |       |        | 15   | ns   |

| RESET Inactive to BIT_CLK Startup Delay                      | t <sub>TRI2ACTV</sub>   |       |        | 25   | ns   |

NOTES

<sup>&</sup>lt;sup>1</sup>Guaranteed but not tested.

$<sup>{}^2\!</sup>Output\,jitter\,directly\,dependent\,on\,crystal\,input\,jitter; max\,specified\,for\,noncrystal\,operation.$

Figure 3. Cold Reset Timing (Codec is Supplying the Bit\_CLK Signal)

Figure 4. Warm Reset Timing

Figure 5. Clock Timing

Figure 6. Signal Rise and Fall Times

Figure 7. AC Link Low Power Mode Timing

Figure 8. AC Link Low Power Mode Timing

Figure 9. ATE Test Mode

## **ABSOLUTE MAXIMUM RATINGS**

| Parameter                           | Min  | Max             | Unit |

|-------------------------------------|------|-----------------|------|

| Power Supplies                      |      |                 |      |

| Digital (DV <sub>DD</sub> )         | -0.3 | +3.6            | V    |

| Analog (AV <sub>DD</sub> )          | -0.3 | +6.0            | ٧    |

| Input Current (Except Supply Pins)  |      | ±10.0           | mA   |

| Analog Input Voltage (Signal Pins)  | -0.3 | $AV_{DD} + 0.3$ | ٧    |

| Digital Input Voltage (Signal Pins) | -0.3 | $DV_{DD} + 0.3$ | ٧    |

| Ambient Temperature (Operating)     | 0    | 70              | °C   |

| Storage Temperature                 | -65  | +150            | °C   |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other condition s above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ENVIRONMENTAL CONDITIONS**

**Ambient Temperature Rating**

$T_{\text{CASE}} = Case \; Temperature \; in \; ^{\circ}C$

PD = Power Dissipation in W

$\theta_{JA}$  = Thermal Resistance (Junction-to-Ambient)

$\theta_{\text{JC}}$  = Thermal Resistance (Junction-to-Case)

#### **Thermal Resistance**

| Package Type | $\theta$ JA | θις      |

|--------------|-------------|----------|

| LQFP         | 50.1°C/W    | 17.8°C/W |

All measurements per EIA/JESD51 with 2S2P test board per EIA/JESD51-7.

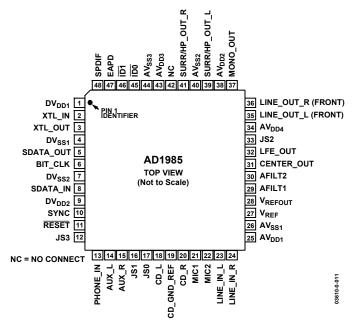

## PIN CONFIGURATION AND FUNCTIONAL DESCRIPTIONS

Figure 10. 48-Lead LQFP Pin Configuration

Circuit Layout Note: In normal operation, Surround and Line Out are swapped to provide headphone drive on line outputs. Therefore Pins 35, 36 become the Surround L/R outputs and Pins 39, 41 become the Line Out (Front) L/R outputs with headphone drive.

### **Pin Descriptions**

### **DIGITAL I/O**

| Pin Name  | Pin Number | I/O | Description                                                                                |

|-----------|------------|-----|--------------------------------------------------------------------------------------------|

| XTL_IN    | 2          | I   | Crystal Input (24.576 MHz) or External Clock In (24.576 MHz, 14.31818 MHz, or 48.000 MHz). |

| XTL_OUT   | 3          | 0   | Crystal Output.                                                                            |

| SDATA_OUT | 5          | I   | AC Link Serial Data Output. AD1985 input stream.                                           |

| BIT_CLK   | 6          | O/I | AC Link Bit Clock. 12.288 MHz serial data clock. (Input pin, for secondary mode only.)     |

| SDATA_IN  | 8          | 0   | AC Link Serial Data Input. AD1985 output stream.                                           |

| SYNC      | 10         | I   | AC Link Frame Sync.                                                                        |

| RESET     | 11         | I   | AC Link Reset. AD1985 master hardware reset.                                               |

| SPDIF     | 48         | 0   | SPDIF Output.                                                                              |

#### CHIP SELECTS/CLOCK STRAPPING

| Pin Name | Pin Number | I/O | Description                                                                                            |

|----------|------------|-----|--------------------------------------------------------------------------------------------------------|

| ĪD0      | 45         | 1   | Chip Select Input 0 (Active Low). This pin can also be used as the chain input from a secondary codec. |

| ĪD1      | 46         | I   | Chip Select Input 1 (Active Low).                                                                      |

### **JACK SENSE/EAPD**

| Pin Name | Pin<br>Number | Туре | Description         |

|----------|---------------|------|---------------------|

| EAPD     | 47            | 0    | EAPD Output.        |

| JS0      | 17            | 1    | JACK SENSE 0 Input. |

| JS1      | 16            | 1    | JACK SENSE 1 Input. |

| JS2      | 33            | 1    | JACK SENSE 2 Input. |

| JS3      | 12            | 1    | JACK SENSE 3 Input. |

### **ANALOG I/O**

| Pin Name            | Pin<br>Number | I/O | Description                                                                                    |

|---------------------|---------------|-----|------------------------------------------------------------------------------------------------|

| PHONE_IN            | 13            | ı   | Monaural Line-Level Input.                                                                     |

| _<br>AUX_L          | 14            | 1   | Auxiliary Input, Left Channel.                                                                 |

| _<br>AUX_R          | 15            | 1   | Auxiliary Input, Right Channel.                                                                |

| CD_L                | 18            | 1   | CD Audio Left Channel.                                                                         |

| CD_GND_REF          | 19            | 1   | CD Audio Analog Ground Reference for Differential CD Input.                                    |

| CD_R                | 20            | 1   | CD Audio Right Channel.                                                                        |

| MIC1                | 21            | 1   | Microphone 1 Input.                                                                            |

| MIC2                | 22            | 1   | Microphone 2 Input.                                                                            |

| LINE_IN_L           | 23            | 1   | Line In Left Channel.                                                                          |

| LINE_IN_R           | 24            | 1   | Line In Right Channel.                                                                         |

| CENTER_OUT          | 31            | I/O | Center Channel Output or Input to Recorder (depending on OMS bit in Reg 0x74).                 |

| LFE_OUT             | 32            | I/O | Low Frequency Enhanced Output or Input to Recorder (depending on OMS bit in Reg 0x74).         |

| LINE_OUT_L/SURR_L   | 35            | 0   | Line Out (Front) Left Channel or Surround Left Channel (depending on LOSEL bit in Reg 0x76).   |

| LINE_OUT_R/SURR_R   | 36            | 0   | Line Out (Front) Right Channel or Surround Right Channel (depending on LOSEL bit in Reg 0x76). |

| MONO_OUT            | 37            | 0   | Monaural Output to Telephony Subsystem Speakerphone.                                           |

| SURR_OUT_L/HP_OUT_L | 39            | 0   | Surround or Front Headphone Left Channel Output (depending on HPSEL bit in Reg 0x76).          |

| SURR_OUT_R/HP_OUT_R | 41            | 0   | Surround or Front Headphone Right Channel Output (depending on HPSEL bit in Reg 0x76).         |

## FILTER/REFERENCE

| Pin Name         | Pin    | I/O | Description                                       |

|------------------|--------|-----|---------------------------------------------------|

|                  | Number |     |                                                   |

| V <sub>REF</sub> | 27     | 0   | Voltage Reference Filter.                         |

| $V_{REFOUT}$     | 28     | 0   | Voltage Reference Output (Intended for Mic Bias). |

| AFILT1           | 29     | 0   | Antialiasing Filter Capacitor—ADC Right Channel.  |

| AFLIT2           | 30     | 0   | Antialiasing Filter Capacitor—ADC Left Channel.   |

## **POWER AND GROUND SIGNALS**

| Pin Name          | Pin Number | Type | Description                      |

|-------------------|------------|------|----------------------------------|

| DV <sub>DD1</sub> | 1          | I    | Digital V <sub>DD</sub> : 3.3 V. |

| $DV_{SS1}$        | 4          | I    | Digital Ground.                  |

| $DV_{SS2}$        | 7          | I    | Digital Ground.                  |

| $DV_{DD2}$        | 9          | I    | Digital V <sub>DD</sub> : 3.3 V. |

| $AV_{DD1}$        | 25         | I    | Analog V <sub>DD</sub> : 5.0 V.  |

| $AV_{SS1}$        | 26         | I    | Analog Ground.                   |

| $AV_{DD4}$        | 34         | I    | Analog V <sub>DD</sub> : 5.0 V.  |

| $AV_{DD2}$        | 38         | I    | Analog V <sub>DD</sub> : 5.0 V.  |

| $AV_{SS2}$        | 40         | I    | Analog Ground.                   |

| $AV_DD3$          | 43         | I    | Analog V <sub>DD</sub> : 5.0 V.  |

| $AV_{SS3}$        | 44         | I    | Analog Ground.                   |

## **NO CONNECTS**

| Pin Name | Pin Number | Type | Description |

|----------|------------|------|-------------|

| NC       | 42         | N/A  | No Connect. |

### **Indexed Control Registers**

| 0x00<br>0x02<br>0x04 | Reset                 |             |            |            |           | D11       | D10       | D9         | D8         | D7         | D6         | D5        | D4        | D3        | D2        | D1         | D0         | Default |

|----------------------|-----------------------|-------------|------------|------------|-----------|-----------|-----------|------------|------------|------------|------------|-----------|-----------|-----------|-----------|------------|------------|---------|

|                      | neset                 | Х           | SE4        | SE3        | SE2       | SE1       | SE0       | ID9        | ID8        | ID7        | ID6        | ID5       | ID4       | ID3       | ID2       | ID1        | ID0        | 0x0090  |

| 0x04                 | Master Volume         | MM          | Х          | Х          | LMV4      | LMV3      | LMV2      | LMV1       | LMV0       | MMRM*      | Х          | Х         | RMV4      | RMV3      | RMV2      | RMV1       | RMV0       | 0x8000  |

| 0/10 .               | Headphones Volume     | НРМ         | Х          | Х          | LHV4      | LHV3      | LHV2      | LHV1       | LHV0       | HPRM*      | Х          | Х         | RHV4      | RHV3      | RHV2      | RHV1       | RHV0       | 0x8000  |

| 0x06                 | Mono Volume           | MVM         | Х          | Х          | Х         | Х         | Х         | Χ          | Х          | Х          | Х          | Х         | MV4       | MV2       | MV2       | MV1        | MV0        | 0x8000  |

| 0x0A                 | PC Beep               | PCBM        | Х          | Х          | PCBF7     | PCBF6     | PCBF5     | PCBF4      | PCBF3      | PCBF2      | PCBD1      | PCBF0     | PCBV3     | PCBV2     | PCBV1     | PCBV0      | Х          | 0x8000  |

| 0x0C                 | Phone Volume          | РНМ         | Х          | Х          | Х         | Х         | Х         | Χ          | Х          | Х          | Х          | Х         | PHV4      | PHV3      | PHV2      | PHV1       | PHV0       | 0x8008  |

| 0x0E                 | Mic Volume            | MCM         | Х          | Х          | Х         | Х         | Х         | Х          | Х          | Х          | M20        | Х         | MCV4      | MCV3      | MCV2      | MCV1       | MCV0       | 0x8008  |

| 0x10                 | Line In Volume        | LM          | Х          | Х          | LLV4      | LLV3      | LLV2      | LLV1       | LLV0       | LVRM*      | Х          | Х         | RLV4      | RLV3      | RLV2      | RLV1       | RLV0       | 0x8808  |

| 0x12                 | CD Volume             | CM          | Х          | Х          | LCV4      | LCV3      | LCV2      | LCV1       | LCV0       | CDRM*      | Х          | Х         | RCV4      | RCV3      | RCV2      | RCV1       | RCV0       | 0x8808  |

| 0x16                 | AUX Volume            | AM          | Х          | Х          | LAV4      | LAV3      | LAV2      | LAV1       | LAV0       | AVRM*      | Х          | Х         | RAV4      | RAV3      | RAV2      | RAV1       | RAV0       | 0x8808  |

| 0x18                 | PCM Out Vol           | ОМ          | Х          | Х          | LOV4      | LOV3      | LOV2      | LOV1       | LOV0       | OMRM*      | х          | Х         | ROV4      | ROV3      | ROV2      | ROV1       | ROV0       | 0x8808  |

| 0x1A                 | Record Select         | х           | х          | Х          | Х         | Х         | LS2       | LS1        | LS0        | Х          | х          | х         | х         | Х         | RS2       | RS1        | RS0        | 0x0000  |

| 0x1C                 | Record Gain           | IM          | Х          | Х          | Х         | LIV3      | LIV2      | LIV1       | LIV0       | IMRM*      | Х          | Х         | Х         | RIV3      | RIV2      | RIV1       | RIV0       | 0x8000  |

| 0x20                 | General Purpose       | х           | х          | Х          | Х         | DRSS1     | DRSS0     | MIX        | MS         | LPBK       | Х          | Х         | Х         | Х         | Х         | Х          | х          | 0x0000  |

| 0x24                 | Audio Int. and Paging | 14          | 13         | 12         | l1        | 10        | Х         | Х          | Х          | Х          | Х          | Х         | Х         | PG3       | PG2       | PG1        | PG0        | 0xXXXx  |

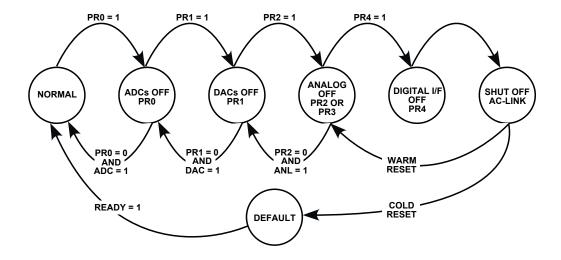

| 0x26                 | Power-Down Ctrl/Stat  | EAPD        | PR6        | PR5        | PR4       | PR3       | PR2       | PR1        | PR0        | Х          | Х          | Х         | Х         | REF       | ANL       | DAC        | ADC        | N/A     |

| 0x28                 | Extended Audio ID     | AID1        | AID0       | Х          | Х         | REV1      | REV0      | AMAP       | AIDLDAC    | AIDSDAC    | AIDCDAC    | DSA1      | DSA0      | Х         | AIDSPDF   | AIDDRA     | AIDVRA     | 0xXBC7  |

| 0x2A                 | Ext'd Audio Stat/Ctrl | VFORCE      | Х          | PRK        | PRJ       | PRI       | SPCV      | Х          | ASCLDAC    | ASCSDAC    | ASCCDAC    | SPSA1     | SPSA0     | Х         | ASCSPDF   | ASCDRA     | ASCVRA     | 0xXXXX  |

| 0x2C                 | PCM Front DAC Rate    | SRF15       | SRF14      | SRF13      | SRF12     | SRF11     | SRF10     | SRF9       | SRF8       | SRF7       | SRF6       | SRF5      | SRF4      | SRF3      | SRF2      | SRF1       | SRF0       | 0xBB80  |

| 0x2E                 | PCM Surr DAC Rate     | SRS15       | SRS14      | SRS13      | SRS12     | SRS11     | SRS10     | SRS9       | SRS8       | SRS7       | SRS6       | SRS5      | SRS4      | SRS3      | SRS2      | SRS1       | SRS0       | 0xBB80  |

| 0x30                 | PCM LFE/C DAC Rate    | SRCL15      | SRCL14     | SRCL13     | SRCL12    | SRCL11    | SRCL10    | SRCL9      | SRCL8      | SRCL7      | SRCL6      | SRCL5     | SRCL4     | SRCL3     | SRCL2     | SRCL1      | SRCL0      | 0xBB80  |

| 0x32                 | PCM L/R ADC Rate      | SRA15       | SRA14      | SRA13      | SRA12     | SRA11     | SRA10     | SRA9       | SRA8       | SRA7       | SRA6       | SRA5      | SRA4      | SRA3      | SRA2      | SRA1       | SRA0       | 0xBB80  |

| 0x36                 | Center/LFE volume     | LFEM        | Х          | Х          | LFE4      | LFE3      | LFE2      | LFE1       | LFE0       | CNTM       | Х          | Х         | CNT4      | CNT3      | CNT2      | CNT1       | CNT0       | 0x8080  |

| 0x38                 | Surround Volume       | LSM         | Х          | Х          | LSR4      | LSR3      | LSR2      | LSR1       | LSR0       | RSM        | Х          | Х         | RSR4      | RSR3      | RSR2      | RSR1       | RSR0       | 0x8080  |

| 0x3A                 | SPDIF Control         | V           | Х          | SPSR1      | SPSR0     | L         | CC6       | CC5        | CC4        | CC3        | CC2        | CC1       | CC0       | PRE       | COPY      | AUD        | PRO        | 0x2000  |

| 0x60                 | EQ Control            | EQM         | Х          | Х          | X         | Х         | Х         | Х          | Х          | SYM        | CHS        | BCA5      | BCA4      | BCA3      | BCA2      | BCA1       | BCA0       | 0x8080  |

| 0x62                 | EO Data               | CFD15       | CFD14      | CFD13      | CFD12     | CFD11     | CFD10     | CFD9       | CFD8       | CFD7       | CFD6       | CFD5      | CFD4      | CFD3      | CFD2      | CFD1       | CFD0       | 0x0000  |

| 0x70                 | J Sense/General       | Х           | Х          | Х          | Х         | Х         | X         | Х          | Х          | MMDIS      | JS2SEL     | Х         | Х         | Х         | Х         | Х          | х          | N/A     |

| 0x72                 | J Sense/Audio/Status  | JS1<br>SPRD | JS1<br>DMX | JS0<br>DMX | JS<br>MT2 | JS<br>MT1 | JS<br>MT0 | JS1<br>EQB | JS0<br>EQB | JS1<br>TMR | JS0<br>TMR | JS1<br>MD | JS0<br>MD | JS1<br>ST | JS0<br>ST | JS1<br>INT | JS0<br>INT | N/A     |

| 0x74                 | Serial Configuration  | SLOT16      | REGM2      | REGM1      | REGM0     | REGM3     | DRF       | OMS        | CHEN       | SPOVR      | LBKS1      | LBKS0     | INTS      | CSWP      | SPAL      | SPDZ       | SPLNK      | 0x1001  |

| 0x76                 | Misc Control Bits     | DACZ        | AC97NC     | MSPLT      | LODIS     | CLDIS     | HPSEL     | DMIX1      | DMIX0      | SPRD       | 2CMIC      | LOSEL     | SRU       | VREFH     | VREFD     | MBG1       | MBG0       | 0x0000  |

| 0x78                 | Advanced Jack Sense   | Х           | Х          | Х          | Χ         | Х         | Х         | Х          | Х          | JS3 TMR    | JS2 TMR    | JS3 MD    | JS2 MD    | JS3 ST    | JS2 ST    | JS3 INT    | JS2 INT    | N/A     |

| 0x7C                 | Vendor ID1            | VIDF7       | VIDF6      | VIDF5      | VIDF4     | VIDF3     | VIDF2     | VIDF1      | VIDF0      | VIDS7      | VIDS6      | VIDS5     | VIDS4     | VIDS3     | VIDS2     | VIDS1      | VIDS0      | 0x4144  |

| 0x7E                 | Vendor ID2            | VIDT7       | VIDT6      | VIDT5      | VIDT4     | VIDT3     | VIDT2     | VIDT1      | VIDT0      | VIDREV7    | VIDREV6    | VIDREV5   | VIDREV4   | VIDREV3   | VIDREV2   | VIDREV1    | VIDREV0    | 0x5375  |

| 0x60<br>pg. 1        | CODEC Class/Rev       | х           | х          | х          | CL4       | CL3       | CL2       | CL1        | CL0        | RV7        | RV6        | RV5       | RV4       | RV3       | RV2       | RV1        | RV0        | N/A     |

| 0x62<br>pg. 1        | PCI SVID              | PVI15       | PVI14      | PVI13      | PVI12     | PVI11     | PVI10     | PVI9       | PVI8       | PVI7       | PVI6       | PVI5      | PVI4      | PVI3      | PVI2      | PVI1       | PVI0       | N/A     |

| 0x64<br>pg. 1        | PCI SID               | PI15        | PI14       | PI13       | PI12      | PI11      | PI10      | PI9        | PI8        | PI7        | PI6        | PI5       | PI4       | PI3       | PI2       | PI1        | PI0        | N/A     |

| 0x66<br>pg. 1        | Function Select       | х           | х          | х          | х         | х         | х         | х          | х          | Х          | х          | х         | FC3       | FC2       | FC1       | FC0        | T/R        | 0x0000  |

| 0x68<br>pg. 1        | Function Information  | G4          | G3         | G2         | G1        | G0        | INV       | DL4        | DL3        | DL2        | DL1        | DL0       | IV        | Х         | Х         | Х          | FIP        | N/A     |

| 0x6A<br>pg. 1        | Sense Register        | ST2         | ST1        | ST0        | S4        | S3        | S2        | S1         | S0         | OR1        | OR0        | SR5       | SR4       | SR3       | SR2       | SR1        | SR0        | N/A     |

Odd register addresses are aliased to the next lower even address.

Registers not shown and bits containing an X are assumed to be reserved.

Reserved registers should not be written. Zeros should be written to reserved bits.

\*For AC '97 compatibility, these RM bits must be enabled before they can have any effect.

### Reset (Index 0x00)

| Reg Num | Name  | D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0  | Default |

|---------|-------|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|-----|---------|

| 0x00    | Reset | X   | SE4 | SE3 | SE2 | SE1 | SE0 | ID9 | ID8 | ID7 | ID6 | ID5 | ID4 | ID3 | ID2 | ID1 | ID0 | 0x0090  |

Note: Writing any value to this register performs a register reset, which causes all registers (except Register 0x74) to revert to their default values. Register 0x74 will only reset bits CSWP (D3), LBKS[1:0] (D[6:5]), and OMS (D9). The REGM and serial configuration bits are reset only by an external hardware reset. Reading this register returns the ID code of the part and a code for the type of 3D stereo enhancement.

ID[9:0] Identify Capability: The ID decodes the capabilities of AD1985 based on the following:

| Bit = 1 | Function                          | AD1985 |

|---------|-----------------------------------|--------|

| ID0     | Dedicated Mic PCM In Channel      | 0      |

| ID1     | Reserved (per AC '97, 2.3)        | 0      |

| ID2     | Bass and Treble Control           | 0      |

| ID3     | Simulated Stereo (Mono to Stereo) | 0      |

| ID4     | Headphone Out Support             | 1      |

| ID5     | Loudness (Bass Boost) Support     | 0      |

| ID6     | 18-Bit DAC Resolution             | 0      |

| ID7     | 20-Bit DAC Resolution             | 1      |

| ID8     | 18-Bit ADC Resolution             | 0      |

| ID9     | 20-Bit ADC Resolution             | 0      |

SE[4:0] Stereo Enhancement. The AD1985 does not provide hardware 3D stereo enhancement (all bits are 0).

#### Master Volume Register (Index 0x02)

| Reg Num | Name          | D15 | D14 | D13 | D12  | D11  | D10  | D9   | D8   | D7    | D6 | D5 | D4   | D3   | D2   | D1   | D0   | Default |

|---------|---------------|-----|-----|-----|------|------|------|------|------|-------|----|----|------|------|------|------|------|---------|

| 0x02    | Master Volume | MM  | Χ   | Χ   | LMV4 | LMV3 | LMV2 | LMV1 | LMV0 | MMRM* | Χ  | Χ  | RMV4 | RMV3 | RMV2 | RMV1 | RMV0 | 0x8000  |

<sup>\*</sup>For AC '97 compatibility, Bit D7 (MMRM) is available only by setting the MSPLT bit in Register 0x76. The MSPLT bit enables separate mute bits for the left and right channels.

This register controls the LINE\_OUT volume controls and mute bit. Each volume subregister contains five bits, generating 32 volume levels with increments of 1.5 dB each.

Because AC '97 defines 6-bit volume registers, to maintain compatibility, whenever the D5 or D13 bit is set to 1, its respective lower five volume bits are automatically set to 1 by the codec logic. On readback, all lower five bits will read 1s whenever these bits are set to 1.

Note that depending on the state of the AC97NC bit in Register 0x76, this register has the following additional functionality:

For AC97NC = 0, the register controls the LINE\_OUT output attenuators only.

For AC97NC = 1, the register controls the LINE\_OUT, center, and LFE output attenuators.

| RMV[5:0] | Right Master Volume Control. The least significant bit represents 1.5 dB. This register controls the output from 0 dB to a maximum attenuation of 46.5 dB.                                                    |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MMRM     | Right Channel Mute. Once enabled by the MSPLT bit in Register 0x76, this bit mutes the right channel separately from the MM bit. Otherwise this bit will always read 0 and will have no effect when set to 1. |

| LMV[5:0] | Left Master Volume Control. The least significant bit represents 1.5 dB. This register controls the output from 0 dB to a maximum attenuation of 46.5 dB.                                                     |

| MM       | Master Volume Mute. When this bit is set to 1, all channels are muted, unless the MSPLT bit in Register 0x76 is set to 1, in which case this mute bit will only affect the left channels.                     |

#### **Volume Settings for Master and Headphone**

| -         |                                                         | Control Bits                                     |          |                             |     |         |          |                              |  |  |  |  |  |  |

|-----------|---------------------------------------------------------|--------------------------------------------------|----------|-----------------------------|-----|---------|----------|------------------------------|--|--|--|--|--|--|

| Reg. 0x76 |                                                         | Master Volume (0x02) and Headphone Volume (0x04) |          |                             |     |         |          |                              |  |  |  |  |  |  |

|           | Left Channel Volume D[13:8] Right Channel Volume D[5:0] |                                                  |          |                             |     |         |          |                              |  |  |  |  |  |  |

| MSPLT*    | D15                                                     | WRITE                                            | READBACK | Function                    | D7* | WRITE   | READBACK | Function                     |  |  |  |  |  |  |

| 0         | 0                                                       | 00 0000                                          | 00 0000  | 0 dB Gain                   | Х   | 00 0000 | 00 0000  | 0 dB Gain                    |  |  |  |  |  |  |

| 0         | 0                                                       | 00 1111                                          | 00 1111  | –22.5 dB Gain               | Х   | 00 1111 | 00 1111  | –22.5 dB Gain                |  |  |  |  |  |  |

| 0         | 0                                                       | 01 1111                                          | 01 1111  | –46.5 dB Gain               | Х   | 01 1111 | 01 1111  | -46.5 dB Gain                |  |  |  |  |  |  |

| 0         | 0                                                       | 1x xxxx                                          | 01 1111  | –46.5 dB Gain               | Х   | 1x xxxx | 01 1111  | –46.5 dB Gain                |  |  |  |  |  |  |

| 0         | 1                                                       | XX XXXX                                          | xx xxxx  | –∞ dB Gain, Muted           | Х   | XX XXXX | XX XXXX  | –∞ dB Gain, Muted            |  |  |  |  |  |  |

| 1         | 0                                                       | 1x xxxx                                          | 01 1111  | –46.5 dB Gain               | 1   | xx xxxx | xx xxxx  | –∞ dB Gain, Only Right Muted |  |  |  |  |  |  |

| 1         | 1                                                       | XX XXXX                                          | xx xxxx  | –∞ dB Gain, Only Left Muted | 0   | 1x xxxx | 01 1111  | –46.5 dB Gain                |  |  |  |  |  |  |

| 1         | 1                                                       | xx xxxx                                          | xx xxxx  | –∞ dB Gain, Left Muted      | 1   | xx xxxx | xx xxxx  | –∞ dB Gain, Right Muted      |  |  |  |  |  |  |

<sup>\*</sup>For AC '97 compatibility, Bit D7 is available only by setting the MSPLT bit, Register 0x76. The MSPLT bit enables separate mute bits for the left and right channels. If MSPLT is not set, Bit D7 has no effect.

Note: x in the above table is a wild card, meaning the value has no effect.

#### Headphone Volume Register (Index 0x04)

| Reg Num | Name              | D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7    | D6 | D5 | D4  | D3  | D2  | D1  | D0  | Default |

|---------|-------------------|-----|-----|-----|-----|-----|-----|-----|-----|-------|----|----|-----|-----|-----|-----|-----|---------|

| 0x04    | Headphones Volume | HPM | Χ   | Χ   | LHV | LHV | LHV | LHV | LHV | HPRM* | Χ  | Χ  | RHV | RHV | RHV | RHV | RHV | 0x8000  |

|         |                   |     |     |     | 4   | 3   | 2   | 1   | 0   |       |    |    | 4   | 3   | 2   | 1   | 0   |         |

<sup>\*</sup>For AC '97 compatibility, Bit D7 (HPRM) is available only by setting the MSPLT bit in Register 0x76. The MSPLT bit enables separate mute bits for the left and right channels

This register controls the headphone volume controls for both stereo channels and mute bit. Each volume subregister contains five bits, generating 32 volume levels with increments of 1.5 dB each. Because AC '97 defines 6-bit volume registers, to maintain compatibility, whenever the D5 or D13 bit is set to 1, its respective lower five volume bits are automatically set to 1 by the codec logic. On readback, all lower five bits will read 1s whenever these bits are set to 1. See Volume Settings for Master and Headphone table, above.

Note that depending on the state of the AC97NC bit in Register 0x76, this register has the following additional functionality:

For AC97NC = 0, the register has no control over the SURR\_OUT/HP\_OUT outputs (see Register 0x38).

For AC97NC = 1, the register controls the SURR\_OUT/HP\_OUT output attenuators.

| RHV[5:0] | Right Headphone Volume Control. The least significant bit represents 1.5 dB. This register controls the output from 0 dB to a maximum attenuation of 46.5 dB.                                                    |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HPRM     | Right Channel Mute. Once enabled by the MSPLT bit in Register 0x76, this bit mutes the right channel separately from the HPM bit. Otherwise this bit will always read 0 and will have no effect when set to 1.   |

| LHV[5:0] | Left Headphone Volume Control. The least significant bit represents 1.5 dB. This register controls the output from 0 dB to a maximum attenuation of 46.5 dB.                                                     |

| НРМ      | Headphones Volume Mute. When this bit is set to 1, both the left and right channels are muted, unless the MSPLT bit in Register 0x76 is set to 1, in which case this mute bit will only affect the left channel. |

### Mono Volume (Index 0x06)

| Reg Num | Name        | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4  | D3  | D2  | D1  | D0  | Default |

|---------|-------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|-----|-----|-----|-----|-----|---------|

| 0x06    | Mono Volume | MVM | Χ   | Χ   | Χ   | Χ   | Χ   | Χ  | Χ  | Χ  | Χ  | Χ  | MV4 | MV3 | MV2 | MV1 | MV0 | 0x8000  |

This register controls the Mono output volume and mute bit. The volume register contains five bits, generating 32 volume levels with increments of 1.5 dB each. Because AC '97 defines 6-bit volume registers, to maintain compatibility, whenever the

D5 bit is set to 1, its respective lower five volume bits are automatically set to 1 by the codec logic. On readback, all lower five bits will read 1s whenever this bit is set to 1.

| MV[5:0] | Mono Volume Control. The least significant bit represents 1.5 dB. This register controls the output from 0 dB to a maximum attenuation of 46.5 dB. |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| MVM     | Mono Volume Mute. When this bit is set to 1, the channel is muted.                                                                                 |

### **Volume Settings for Mono**

|     | Control Bits D |          |                   |

|-----|----------------|----------|-------------------|

| D15 | WRITE          | READBACK | Function          |

| 0   | 0 0000         | 0 0000   | 0 dB Gain         |

| 0   | 0 1111         | 0 1111   | –22.5 dB Gain     |

| 0   | 1 1111         | 1 1111   | –46.5 dB Gain     |

| 1   | x xxxx         | x xxxx   | –∞ dB Gain, Muted |

Note: x in the above table is a wild card, meaning the value has no effect.

### PC Beep Register (Index 0x0A)

| Reg  | Name           | D15  | D14 | D13 | D12   | D11   | D10   | D9    | D8    | D7     | D6    | D5    | D4    | D3    | D2    | D1    | D0 | Default |

|------|----------------|------|-----|-----|-------|-------|-------|-------|-------|--------|-------|-------|-------|-------|-------|-------|----|---------|

| 0x0A | PC Beep Volume | PCBM | Χ   | Χ   | PCBF7 | PCBF6 | PCBF5 | PCBF4 | PCBF3 | PCB F2 | PCBF1 | PCBF0 | PCBV3 | PCBV2 | PCBV1 | PCBV0 | Χ  | 0x8000  |

This register controls the level and frequency for the digital PC beep generated by the codec.

| PV3-PV0     | Controls the volume of the generated signal. Each step corresponds to approximately 3 dB of attenuation. The MSB of the register is the mute bit. When this bit is set to 1, the level for the signal is set at −∞ dB.                                                                                                                                                           |

|-------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PCBF7-PCBF0 | These bits are writeable, and the codec-digital PCBEEP generation is supported. The beep frequency generated is the result of dividing the 48 kHz clock by 4 times the number specified in PCBF[7:0], allowing tones from 47 Hz to 12 kHz. A value of 0x00 in Bits PCBF[7:0] disables internal PC beep generation. The PV bits control the volume level of the generated signal. |

The register default value is 0x8000, which corresponds to  $0~\mathrm{dB}$  attenuation with mute on.

| PCBM | PV3-PV0 | Function          |

|------|---------|-------------------|

| 0    | 0000    | 0 dB Attenuation  |

| 0    | 1111    | 45 dB Attenuation |

| 1    | XXXX    | ∞ dB Attenuation  |

| PCBF | Frequency of PC Beep |

|------|----------------------|

| 0x00 | PC Beep Disabled     |

| 0x01 | 12 kHz               |

| 0x0C | 1 kHz                |

| 0xFF | 47 Hz                |

### Phone\_in Volume (Index 0x0C)

| Reg Num | Name            | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6 | D5 | D4   | D3   | D2   | D1   | D0   | Default |

|---------|-----------------|-----|-----|-----|-----|-----|-----|----|----|----|----|----|------|------|------|------|------|---------|

| 0x0C    | Phone_in Volume | PHM | Χ   | Χ   | Χ   | Χ   | Χ   | Χ  | Χ  | Χ  | Χ  | Χ  | PHV4 | PHV3 | PHV2 | PHV1 | PHV0 | 0x8008  |

| PHV[4:0] | Phone Volume. Allows setting the Phone Volume gain/attenuator to one of 32 levels. The LSB represents 1.5 dB, and the gain range is +12 dB to -34.5 dB. The default value is 0 dB, with mute bit enabled. |

|----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PHM      | Phone Mute. When this bit is set to 1, the Phone channel is muted.                                                                                                                                        |

### **Volume Settings for Phone and MIC**

|     | Control Bit<br>Phone (0x0 | s D[4:0]<br>C) and MIC (0x0E) |                   |

|-----|---------------------------|-------------------------------|-------------------|

| D15 | WRITE                     | READBACK                      | Function          |

| 0   | 0 0000                    | 0 0000                        | 12 dB Gain        |

| 0   | 0 1000                    | 0 1000                        | 0 dB Gain         |

| 0   | 1 1111                    | 1 1111                        | –34.5 dB Gain     |

| 1   | x xxxx                    | x xxxx                        | –∞ dB Gain, Muted |

Note: x in the above table is a wild card, meaning the value has no effect.

### Microphone Volume (Index 0x0E)

| Reg Num | Name       | D15 | D14 | D13 | D12 | D11 | D10 | D9 | D8 | D7 | D6  | D5 | D4   | D3   | D2   | D1   | D0   | Default |

|---------|------------|-----|-----|-----|-----|-----|-----|----|----|----|-----|----|------|------|------|------|------|---------|

| 0x0E    | Mic Volume | MCM | Χ   | Χ   | Χ   | Χ   | Χ   | Χ  | Χ  | Χ  | M20 | Χ  | MCV4 | MCV3 | MCV2 | MCV1 | MCV0 | 0x8008  |

This register controls the volume, gain boost, and mute for the gain/attenuators on both the left (MIC1) and right (MIC2) paths to the mixer. There is no separate control for left and right on

this path. The signal paths must be identical, hence the single control for both.

| MCV[4:0] | MIC Volume. Allows setting the MIC volume gain/attenuator to one of 32 levels. The LSB represents 1.5 dB, and the gain range is $+12$ dB to $-34.5$ dB. The default value is 0 dB, with mute enabled.                        |

|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| M20      | MIC Gain Boost. This bit allows setting additional MIC gain to increase the microphone sensitivity.                                                                                                                          |

|          | The nominal gain boost by default is +20 dB, however Bits D0 and D1 (MBG[1:0]) on the Miscellaneous Control Bits Register (0x76), allow changing the gain boost to +10 dB or +30 dB if necessary.  0 = Disabled; Gain = 0 dB |

|          | 1 = Enabled; Default Gain = +20 dB (see Register 0x76, Bits D0, D1)                                                                                                                                                          |

| MCM      | MIC Mute. When this bit is set to 1, both channels are muted.                                                                                                                                                                |

### Line In Volume (Index 0x10)

| Reg Num | Name           | D15 | D14 | D13 | D12  | D11  | D10  | D9   | D8   | D7    | D6 | D5 | D4   | D3   | D2   | D1   | D0   | Default |

|---------|----------------|-----|-----|-----|------|------|------|------|------|-------|----|----|------|------|------|------|------|---------|

| 0x10    | Line In Volume | LM  | Χ   | Χ   | LLV4 | LLV3 | LLV2 | LLV1 | LLV0 | LVRM* | Χ  | Χ  | RLV4 | RLV3 | RLV2 | RLV1 | RLV0 | 0x8808  |

<sup>\*</sup>For AC '97 compatibility, Bit D7 (LVRM) is available only by setting the MSPLT bit in Register 0x76. The MSPLT bit enables separate mute bits for the left and right channels.

| RLV[4:0] | Right Line In Volume. Allows setting the line in right channel gain/attenuator to one of 32 levels. The LSB represents 1.5 dB, and the gain range is +12 dB to -34.5 dB. The default value is 0 dB, mute enabled. |

|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| LVRM     | Right Channel Mute. Once enabled by the MSPLT bit in Register 0x76, this bit mutes the right channel separately from the LM bit. Otherwise this bit will always read 0 and will have no effect when set to 1.     |

| LLV[4:0] | Line In Volume Left. Allows setting the line in left channel gain/attenuator to one of 32 levels. The LSB represents 1.5 dB, and the gain range is +12 dB to -34.5 dB. The default value is 0 dB, mute enabled.   |

| LM       | Line In Mute. When this bit is set to 1, both the left and right channels are muted, unless the MSPLT bit in Register 0x76 is set to 1, in which case this mute bit will affect only the left channel.            |

### Volume Settings for Line In, CD Volume, AUX, and PCM Out

|           |                                                           |                                                         |          | Cont                        | rol Bits |        |          |                              |  |  |  |  |  |  |

|-----------|-----------------------------------------------------------|---------------------------------------------------------|----------|-----------------------------|----------|--------|----------|------------------------------|--|--|--|--|--|--|

| Reg. 0x76 | Line In (0x10), CD (0x12), AUX (0x16), and PCM Out (0x18) |                                                         |          |                             |          |        |          |                              |  |  |  |  |  |  |

|           |                                                           | Left Channel Volume D[12:8] Right Channel Volume D[4:0] |          |                             |          |        |          |                              |  |  |  |  |  |  |

| MSPLT*    | D15                                                       | WRITE                                                   | READBACK | Function                    | D7*      | WRITE  | READBACK | Function                     |  |  |  |  |  |  |

| 0         | 0                                                         | 0 0000                                                  | 0 0000   | 12 dB Gain                  | Х        | 0 0000 | 0 0000   | 12 dB Gain                   |  |  |  |  |  |  |

| 0         | 0                                                         | 0 1000                                                  | 0 1000   | 0 dB Gain                   | Х        | 0 1000 | 0 1000   | 0 dB Gain                    |  |  |  |  |  |  |

| 0         | 0                                                         | 1 1111                                                  | 1 1111   | -34.5 dB Gain               | Х        | 1 1111 | 1 1111   | -34.5 dB Gain                |  |  |  |  |  |  |

| 0         | 1                                                         | x xxxx                                                  | x xxxx   | –∞ dB Gain, Muted           | Х        | x xxxx | x xxxx   | –∞ dB Gain, Muted            |  |  |  |  |  |  |

| 1         | 0                                                         | 1 1111                                                  | 1 1111   | -34.5 dB Gain               | 1        | x xxxx | x xxxx   | –∞ dB Gain, Only Right Muted |  |  |  |  |  |  |

| 1         | 1                                                         | x xxxx                                                  | x xxxx   | –∞ dB Gain, Only Left Muted | 0        | 1 1111 | 1 1111   | –34.5 dB Gain                |  |  |  |  |  |  |

| 1         | 1                                                         | x xxxx                                                  | x xxxx   | –∞ dB Gain, Left Muted      | 1        | x xxxx | x xxxx   | –∞ dB Gain, Right Muted      |  |  |  |  |  |  |

<sup>\*</sup>For AC '97 compatibility, Bit D7 is available only by setting the MSPLT bit, Register 0x76. The MSPLT bit enables separate mute bits for the left and right channels. If MSPLT is not set, RM bit has no effect.

Note: x in the above table is a wild card, meaning the value has no effect.

### CD Volume (Index 0x12)

| Reg Num | Name      | D15 | D14 | D13 | D12  | D11  | D10  | D9   | D8   | D7    | D6 | D5 | D4   | D3   | D2   | D1   | D0   | Default |

|---------|-----------|-----|-----|-----|------|------|------|------|------|-------|----|----|------|------|------|------|------|---------|

| 0x12    | CD Volume | CM  | Χ   | Χ   | LCV4 | LCV3 | LCV2 | LCV1 | LCV0 | CDRM* | Χ  | Χ  | RCV4 | RCV3 | RCV2 | RCV1 | RCV0 | 0x8808  |

<sup>\*</sup>For AC97 compatibility, Bit D7 (CDRM) is available only by setting the MSPLT bit in Register 0x76. The MSPLT bit enables separate mute bits for the left and right channels. See the Volume Settings for Line In, CD Volume, AUX, and PCM Out table, above.

| RCV[4:0] | Right CD Volume. Allows setting the CD right channel gain/attenuator to one of 32 levels. The LSB represents 1.5 dB, and the gain range is +12 dB to -34.5 dB. The default value is 0 dB, mute enabled.       |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CDRM     | Right Channel Mute. Once enabled by the MSPLT bit in Register 0x76, this bit mutes the right channel separately from the CM bit. Otherwise this bit will always read 0 and will have no effect when set to 1. |

| LCV[4:0] | Left CD Volume. Allows setting the CD left channel gain/attenuator to one of 32 levels. The LSB represents 1.5 dB, and the gain range is +12 dB to -34.5 dB. The default value is 0 dB, mute enabled.         |

| CM       | CD Volume Mute. When this bit is set to 1, both the left and right channels are muted, unless the MSPLT bit in Register 0x76 is set to 1, in which case this mute bit will only affect the left channel.      |

#### **AUX In Volume (Index 0x16)**

| Reg Num | Name       | D15 | D14 | D13 | D12  | D11  | D10  | D9   | D8   | D7    | D6 | D5 | D4   | D3   | D2   | D1   | D0   | Default |

|---------|------------|-----|-----|-----|------|------|------|------|------|-------|----|----|------|------|------|------|------|---------|

| 0x16    | AUX Volume | AVM | Χ   | Χ   | LAV4 | LAV3 | LAV2 | LAV1 | LAV0 | AVRM* | Χ  | Χ  | RAV4 | RAV3 | RAV2 | RAV1 | RAV0 | 0x8808  |

<sup>\*</sup>For AC '97 compatibility, Bit D7 (AVRM) is available only by setting the MSPLT bit in Register 0x76. The MSPLT bit enables separate mute bits for the left and right channels. See the Volume Settings for Line In, CD Volume, AUX, and PCM Out table, above.

| RAV[4:0] | Right AUX Volume. Allows setting the AUX right channel gain/attenuator to one of 32 levels. The LSB represents 1.5 dB, and the gain range is $+12$ dB to $-34.5$ dB. The default value is 0 dB, mute enabled.  |

|----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| AVRM     | Right Channel Mute: Once enabled by the MSPLT bit in Register 0x76, this bit mutes the right channel separately from the AVM bit. Otherwise this bit will always read 0 and will have no effect when set to 1. |

| LAV[4:0] | Left AUX Volume. Allows setting the AUX left channel gain/attenuator to one of 32 levels. The LSB represents 1.5 dB, and the gain range is +12 dB to -34.5 dB. The default value is 0 dB, mute enabled.        |

| AVM      | AUX Volume Mute. When this bit is set to 1, both the left and right channels are muted, unless the MSPLT bit in Register 0x76 is set to 1, in which case this mute bit will only affect the left channel.      |

#### PCM Out Volume (Index 0x18)

| Reg Num | Name        | D15 | D14 | D13 | D12  | D11  | D10  | D9   | D8   | D7    | D6 | D5 | D4   | D3   | D2   | D1   | D0   | Default |

|---------|-------------|-----|-----|-----|------|------|------|------|------|-------|----|----|------|------|------|------|------|---------|

| 0x18    | PCM Out Vol | OM  | Χ   | Χ   | LOV4 | LOV3 | LOV2 | LOV1 | LOV0 | OMRM* | Χ  | Χ  | ROV4 | ROV3 | ROV2 | ROV1 | ROV0 | 0x8808  |

\*For AC '97 compatibility, Bit D7 (OMRM) is available only by setting the MSPLT bit in Register 0x76. The MSPLT bit enables separate mute bits for the left and right channels. See the Volume Settings for Line In, CD Volume, AUX, and PCM Out table, above.

Note that depending on the state of the AC97NC bit in Register 0x76, this register has the following additional functionality:

For AC97NC = 0, the register also controls the Surround, Center, and LFE DAC Gain/Attenuators.

For AC97NC = 1, the register controls the PCM Out Volume only.

| ROV[4:0] | Right PCM Out Volume. Allows setting the PCM right channel gain/attenuator to one of 32 levels. The LSB represents 1.5 dB, and the gain range is +12 dB to -34.5 dB. The default value is 0 dB, mute enabled. |

|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OMRM     | Right Channel Mute. Once enabled by the MSPLT bit in Register 0x76, this bit mutes the right channel separately from the OM bit. Otherwise this bit will always read 0 and will have no effect when set to 1. |

| LOV[4:0] | Left PCM Out Volume. Allows setting the PCM left channel gain/attenuator to one of 32 levels. The LSB represents 1.5 dB, and the gain range is +12 dB to -34.5 dB. The default value is 0 dB, mute enabled.   |

| OM       | PCM Out Volume Mute. When this bit is set to 1, both the left and right channels are muted, unless the MSPLT bit in Register 0x76 is set to 1, in which case this mute bit will only affect the left channel. |

### Record Select Control Register (Index 0x1A)

| Reg Num | Name          | D15 | D14 | D13 | D12 | D11 | D10 | D9  | D8  | D7 | D6 | D5 | D4 | D3 | D2  | D1  | D0  | Default |

|---------|---------------|-----|-----|-----|-----|-----|-----|-----|-----|----|----|----|----|----|-----|-----|-----|---------|

| 0x1A    | Record Select | Χ   | Χ   | Χ   | Χ   | Χ   | LS2 | LS1 | LS0 | Χ  | Χ  | Χ  | Χ  | Χ  | RS2 | RS1 | RS0 | 0x0000  |

This register is used to select the record source, independently for the right and left channels.

For single MIC recording see MS bit (Register 0x20) for MIC1 and MIC2 input selection.

For dual MIC recording see 2CMIC bit (Register 0x76) to enable simultaneous recording into L/R channels.

The default value is 0x0000, which corresponds to MIC input for both channels.

| RS[2:0] | Right Record Select: See table below. |

|---------|---------------------------------------|

| LS[2:0] | Left Record Select: See table below.  |

| LS[2:0] | Left Re         | cord Sele  | ct  |                 |  |  |  |  |  |  |  |

|---------|-----------------|------------|-----|-----------------|--|--|--|--|--|--|--|

|         | OMS             | 2CMIC      | MS  |                 |  |  |  |  |  |  |  |

|         | 0               | 0          | 0   | MIC 1 (mono)    |  |  |  |  |  |  |  |

|         | 0               | 0          | 1   | MIC 2 (mono)    |  |  |  |  |  |  |  |

|         | 0               | 1          | 0   | MIC 1 (stereo)  |  |  |  |  |  |  |  |

| 0       | 0               | 1          | 1   | MIC 2 (stereo)  |  |  |  |  |  |  |  |

|         | 1               | 0          | 0   | CENTER (mono)   |  |  |  |  |  |  |  |

|         | 1               | 0          | 1   | LFE (mono)      |  |  |  |  |  |  |  |

|         | 1               | 1          | 0   | CENTER (stereo) |  |  |  |  |  |  |  |

|         | 1               | 1          | 1   | LFE (stereo)    |  |  |  |  |  |  |  |

| 1       | CD_IN           | (left)     |     |                 |  |  |  |  |  |  |  |

| 2       | muted           |            |     |                 |  |  |  |  |  |  |  |

| 3       | AUX_II          |            |     |                 |  |  |  |  |  |  |  |

| 4       | LINE_I          |            |     |                 |  |  |  |  |  |  |  |

| 5       | Stereo          | Mix (left) |     |                 |  |  |  |  |  |  |  |

| 6       |                 | Mix (mon   |     |                 |  |  |  |  |  |  |  |

| 7       | PHONE_IN (mono) |            |     |                 |  |  |  |  |  |  |  |

| RS[2:0] |                 | Record Sel |     | <del>,</del>    |  |  |  |  |  |  |  |

|         | OMS             | 2CMIC      | MS  |                 |  |  |  |  |  |  |  |

|         | 0               | 0          | 0   | MIC 1 (mono)    |  |  |  |  |  |  |  |

|         | 0               | 0          | 1   | MIC 2 (mono)    |  |  |  |  |  |  |  |

|         | 0               | 1          | 0   | MIC 2 (stereo)  |  |  |  |  |  |  |  |

| 0       | 0               | 1          | 1   | MIC 1 (stereo)  |  |  |  |  |  |  |  |

|         | 1               | 0          | 0   | CENTER (mono)   |  |  |  |  |  |  |  |

|         | 1               | 0          | 1   | LFE (mono)      |  |  |  |  |  |  |  |

|         | 1               | 1          | 0   | LFE (stereo)    |  |  |  |  |  |  |  |

|         | 1               | 1          | 1   | CENTER (stereo) |  |  |  |  |  |  |  |

| 1       | CD_IN           |            |     |                 |  |  |  |  |  |  |  |

| 2       | muted           |            |     |                 |  |  |  |  |  |  |  |

| 3       | AUX_IN (right)  |            |     |                 |  |  |  |  |  |  |  |

| 4       |                 | N (right)  |     |                 |  |  |  |  |  |  |  |

| 5       |                 | Mix (righ  |     |                 |  |  |  |  |  |  |  |

| 6       |                 | Mix (mon   |     |                 |  |  |  |  |  |  |  |

| 7       | PHONI           | E_IN (mon  | 10) |                 |  |  |  |  |  |  |  |

## Record Gain (Index 0x1C)

| Reg Num | Name        | D15 | D14 | D13 | D12 | D11  | D10  | D9   | D8   | D7    | D6 | D5 | D4 | D3   | D2   | D1   | D0   | Default |

|---------|-------------|-----|-----|-----|-----|------|------|------|------|-------|----|----|----|------|------|------|------|---------|

| 0x1C    | Record Gain | IM  | Χ   | Χ   | Χ   | LIV3 | LIV2 | LIV1 | LIV0 | IMRM* | Χ  | Χ  | Χ  | RIV3 | RIV2 | RIV1 | RIV0 | 0x8000  |

<sup>\*</sup>For AC '97 compatibility, Bit D7 (IMRM) is available only by setting the MSPLT bit in Register 0x76. The MSPLT bit enables separate mute bits for the left and right channels.

| RIV[3:0] | Right Input Mixer Gain Control. Each LSB represents 1.5 dB and the gain range is 0 dB to +22.5 dB.                                                                                                            |