# MODIO™ SoundComm®\* Host Signal Processing Codec

AD1821

**FEATURES**

General

Compatible with Microsoft® PC 97 Logo Requirements Supports Applications Written for Windows® 95, Windows 3.1, Windows NT, SoundBlaster® Pro, AdLib®/OPL3®

ISA Plug and Play Compatible Operation from +5 V Supply Power Management Modes 100-Lead PQFP Package

Modem

V.34bis (14.4 kbps up to 33.6 kbps) 56k Software Upgradable

V.32/32bis, V.23, V.22/22bis, V.21, Bell 103 and Bell 212

Modem Protocols: V.8 and Automode

V.42/42bis MNP 5 Data Compression and V.43 MNP 2-4 Error Correction Virtual COM Port 460.8 kbps and 16550 UART Hayes AT Command Set

Fax

Group 3, Class 1 Support V.17 (14.4 kbps), V.29 (9600/7200 bps), V.27/V.27ter Hayes AT Command Set TIES Escape Sequence

Voice/Telephony AT#V Commands Unimodem V TAPI-Compliant Voice/Fax/Modem Distinction Ring Detection

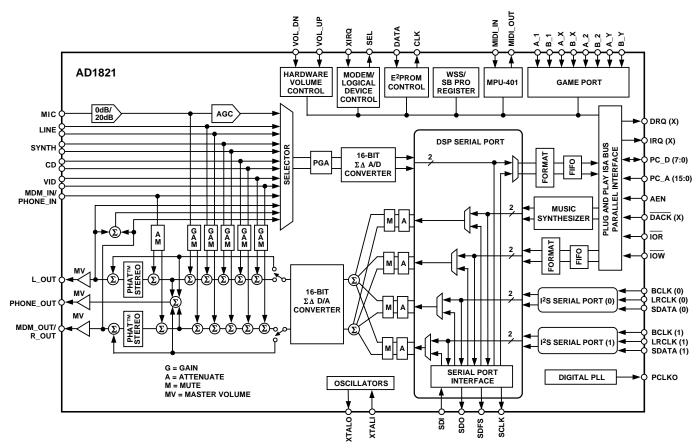

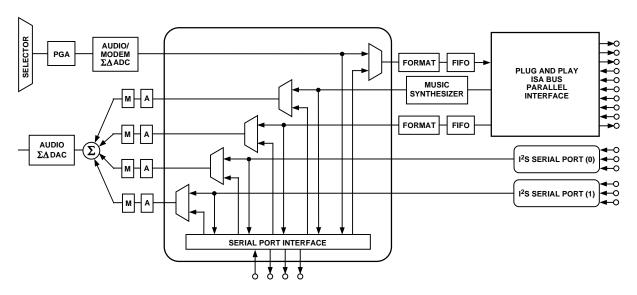

#### FUNCTIONAL BLOCK DIAGRAM

<sup>\*</sup>SoundComm is a registered trademark of Analog Devices, Inc.

All other trademarks are the property of their respective holders.

#### REV. 0

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 617/329-4700 World Wide Web Site: http://www.analog.com Fax: 617/326-8703 © Analog Devices, Inc., 1997

<sup>\*</sup>Phat is a trademark of Analog Devices, Inc.

On/Off Hook Control

Call Progress Monitor

DTMF Detection and Generation

Auto Dial

Call Forwarding and Conferencing

VOX (Voice Detection)

ADPCM (32 kpbs Voice Compression)

Caller ID

Full-Duplex Speakerphone

Handset Record and Playback

Handset On/Off Detection

DSVD Software Upgradeable

Stereo Audio 16-Bit ∑∆ Codec

V.34 Class Modem Analog Front End

Full-Duplex Capture and Playback Operation at

Different Sample Rates

Internal 3D Circuit—Phat™\* Stereo Phase Expander

Integrated OPL3-Compatible Music Synthesizer

Software and Hardware Volume Control

FEATURES ..... 1

#### PRODUCT OVERVIEW

The AD1821 MODIO™ (Modem over Audio) SoundComm® HSP (Host Signal Processing) Codec is a single-chip audio and communications subsystem for personal computers. The AD1821 solution includes the AD1821 mixed-signal controller IC controller IC and MODIO™ host signal processing software drivers. The AD1821 maintains full legacy compatibility with applications written for SoundBlaster Pro and AdLib, while servicing Microsoft PC 97 application requirements. The AD1821 includes an internal OPL3 compatible music synthesizer, Phat™ Stereo circuitry for phase expanding the analog stereo output, an MPU-401 UART joystick interface with built-in timer, a DSP serial port and two I2S Serial ports. The MODIO™ drivers utilize CPU resources to implement high speed fax, data, voice (with Echo Cancellation) communications and maintain audio compatibility. The drivers enable simultaneous execution of communications and audio with data flowing through the AD1821, and provide a graceful degradation of modem performance as the host CPU load changes. The AD1821 on-chip Plug and Play routine provides configuration services for all integrated logical devices.

#### TABLE OF CONTENTS

| PRODUCT OVERVIEW 1                                     | Functional Block Diagram .                 |

|--------------------------------------------------------|--------------------------------------------|

| SPECIFICATIONS                                         | Figure 1. PIO Read Cycle .                 |

| PIN CONFIGURATION                                      | Figure 2. PIO Write Cycle                  |

| PIN FUNCTION DESCRIPTIONS                              | Figure 3. DMA Read Cycle                   |

| HOST INTERFACE                                         | Figure 4. DMA Write Cycle                  |

|                                                        | Figure 5. Codec Transfers                  |

| REFERENCES                                             | Figure 6. DSP Port Timing                  |

| SERIAL INTERFACES                                      | Figure 7. I <sup>2</sup> S Serial Port Tir |

| ISA INTERFACE                                          | Figure 8. Reset Pulse Width                |

| AD1821 Chip Registers                                  | Figure 9. Serial Interface Ri              |

| AD1821 Plug and Play Device Configuration Registers 21 | Figure 10. Serial Interface I              |

| Sound System Direct Registers                          | Figure 11. Serial Interface I              |

| Sound System Indirect Registers                        | Figure 12. DSP Serial Inter                |

| SB Pro; AdLib Registers                                | Figure 13. DSP Serial Inter                |

| MIDI and MPU-401 Registers                             | Frame Rate)                                |

| Game Port Register                                     | Figure 14. DSP Serial Port                 |

| APPENDIX A                                             | Figure 15. Codec Transfers                 |

| AD1821JS AND AD1821JS-M                                | Figure 16. AD1821 Frequen                  |

| AD1821JS PLUG AND PLAY INTERNAL ROM 39                 | Tables                                     |

| AD1821JS-M PLUG AND PLAY INTERNAL ROM 40               | Table I. DSP Port Time Slo                 |

|                                                        | Table II. Chip Register Dia                |

| APPENDIX B                                             | Table III. Logical Devices a               |

| PLUG AND PLAY KEY AND "ALTERNATE KEY"                  | Play Device Drivers                        |

| SEQUENCES 41                                           | Table IV. Logical Device C                 |

| PROGRAMMING EXTERNAL EEPROMS 42                        | Table V. Sound System Dir                  |

| REFERENCE DESIGNS AND DEVICE DRIVERS 42                | Table VI. Codec Transfers                  |

| OUTLINE DIMENSIONS                                     | Table VII. Indirect Register               |

|                                                        | Table VIII. Sound System I                 |

|                                                        | Table IX. SoundBlaster Pro                 |

|                                                        | Table X. AdLib ISA Bus Re                  |

| Figures                                                        |

|----------------------------------------------------------------|

| Functional Block Diagram 1                                     |

| Figure 1. PIO Read Cycle 6                                     |

| Figure 2. PIO Write Cycle                                      |

| Figure 3. DMA Read Cycle                                       |

| Figure 4. DMA Write Cycle 7                                    |

| Figure 5. Codec Transfers 7                                    |

| Figure 6. DSP Port Timing                                      |

| Figure 7. I <sup>2</sup> S Serial Port Timing 7                |

| Figure 8. Reset Pulse Width 7                                  |

| Figure 9. Serial Interface Right-Justified Mode 16             |

| Figure 10. Serial Interface I <sup>2</sup> S-Justified Mode 16 |

| Figure 11. Serial Interface Left-Justified Mode 16             |

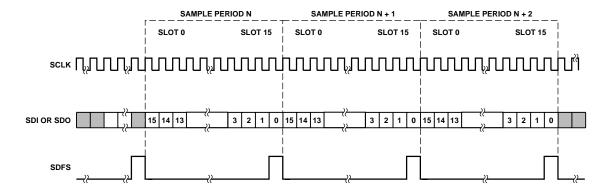

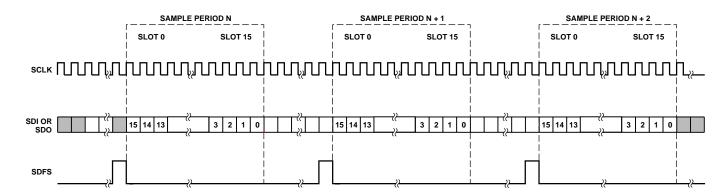

| Figure 12. DSP Serial Interface (Default Frame Rate) 19        |

| Figure 13. DSP Serial Interface (User Programmed               |

| Frame Rate)                                                    |

| Figure 14. DSP Serial Port                                     |

| Figure 15. Codec Transfers                                     |

| Figure 16. AD1821 Frequency Response Plots 43                  |

| Tables                                                         |

| Table I. DSP Port Time Slot Map                                |

| Table II. Chip Register Diagram                                |

| Table III. Logical Devices and Compatible Plug and             |

| Play Device Drivers                                            |

| Table IV. Logical Device Configuration                         |

| Table V. Sound System Direct Registers                         |

| Table VI. Codec Transfers                                      |

| Table VII. Indirect Register Map and Reset/Default States . 29 |

| Table VIII. Sound System Indirect Registers 30                 |

| Table IX. SoundBlaster Pro ISA Bus Registers                   |

| Table X. AdLib ISA Bus Registers                               |

| Table XI. MIDI ISA Bus Registers                               |

| Table XII. Game Port ISA Bus Registers 38                      |

-2- REV. 0

# **SPECIFICATIONS**

| STANDARD TEST CONDITIONS U<br>OTHERWISE NOTED | J <b>NLESS</b> |                      | DAC Test Conditions 0 dB Attenuation                                            |

|-----------------------------------------------|----------------|----------------------|---------------------------------------------------------------------------------|

| Temperature                                   | 25             | $^{\circ}\mathrm{C}$ | Input Full Scale                                                                |

| Digital Supply (V <sub>DD</sub> )             | 5.0            | V                    | 16-Bit Linear Mode                                                              |

| Analog Supply (V <sub>CC</sub> )              | 5.0            | V                    | 100 kΩ Output Load                                                              |

| Sample Rate (F <sub>S</sub> )                 | 48             | kHz                  | Mute Off                                                                        |

| Input Signal Frequency                        | 1008           | Hz                   | Measured at Line Output                                                         |

| Audio Output Passband                         | 20 Hz to       | 20 kHz               | ADC Test Conditions                                                             |

| $V_{\mathrm{IH}}$                             | 5.0            | V                    | 0 dB Gain                                                                       |

| $ m V_{IL}$                                   | 0              | V                    | Input -4 dB Relative to Full Scale<br>Line Input Selected<br>16-Bit Linear Mode |

#### **ANALOG INPUT**

| Parameter                                                    | Min | Тур   | Max | Units |

|--------------------------------------------------------------|-----|-------|-----|-------|

| Full-Scale Input Voltage (RMS Values Assume Sine Wave Input) |     |       |     |       |

| PHONE_IN, LINE, SYNTH, CD, VID, MDM_IN                       |     | 1     |     | V rms |

|                                                              |     | 2.83  |     | V p-p |

| MIC with $+20 \text{ dB Gain (MGE} = 1)$                     |     | 0.1   |     | V rms |

|                                                              |     | 0.283 |     | V p-p |

| MIC with 0 dB Gain (MGE = $0$ )                              |     | 1     |     | V rms |

|                                                              |     | 2.83  |     | V p-p |

| Input Impedance*                                             |     | 17    |     | kΩ    |

| Input Capacitance*                                           |     | 15    |     | pF    |

#### PROGRAMMABLE GAIN AMPLIFIER—ADC

| Parameter                   | Min | Тур  | Max | Units |

|-----------------------------|-----|------|-----|-------|

| Step Size (0 dB to 22.5 dB) |     |      |     |       |

| (All Steps Tested)          |     | 1.5  |     | dB    |

| PGA Gain Range Span         |     | 22.5 |     | dB    |

# $\textbf{CD, LINE, MICROPHONE, MODEM, SYNTHESIZER, AND VIDEO INPUT ANALOG GAIN/AMPLIFIERS, ATTENUATORS/MUTE \\$

| Parameter                                                       | Min | Тур  | Max | Units |

|-----------------------------------------------------------------|-----|------|-----|-------|

| CD, LINE, MIC, SYNTH, VID, MDM_IN Step Size: (All Steps Tested) |     |      |     | lp.   |

| +12 dB to -34.5 dB                                              |     | 1.5  |     | dB    |

| Input Gain/Attenuation Range                                    |     | 46.5 |     | dB    |

| PHONE_IN                                                        |     |      |     |       |

| Step Size 0 dB to -45 dB: (All Steps Tested)                    |     | 3.0  |     | dB    |

| Input Gain/Attenuation Range                                    |     | 45   |     | dB    |

REV. 0 -3-

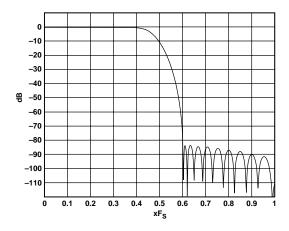

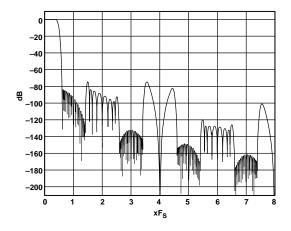

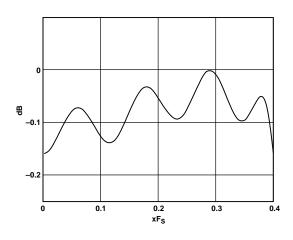

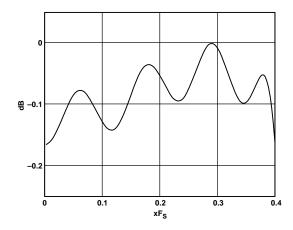

## DIGITAL DECIMATION AND INTERPOLATION FILTERS\*

| Parameter                           | Min              | Тур | Max              | Units |

|-------------------------------------|------------------|-----|------------------|-------|

| Audio Passband                      | 0                |     | $0.4 \times F_S$ | Hz    |

| Audio Passband Ripple               |                  |     | $\pm 0.09$       | dB    |

| Audio Transition Band               | $0.4 \times F_S$ |     | $0.6 \times F_S$ | Hz    |

| Audio Stopband                      | $0.6 \times F_S$ |     | ∞                | Hz    |

| Audio Stopband Rejection            | 82               |     |                  | dB    |

| Audio Group Delay                   |                  |     | $12/F_S$         | sec   |

| Group Delay Variation Over Passband |                  |     | 0.0              | μs    |

## ANALOG-TO-DIGITAL CONVERTERS

| Parameter                                                          | Min | Тур   | Max      | Units |

|--------------------------------------------------------------------|-----|-------|----------|-------|

| Resolution                                                         |     | 16    |          | Bits  |

| Signal-to-Noise Ratio (SNR) (A-Weighted, Referenced to Full Scale) |     | -82   | -80      | dB    |

| Total Harmonic Distortion (THD) (Referenced to Full Scale)         |     | 0.011 | 0.015    | %     |

|                                                                    |     | -79   | -76.5    | dB    |

| Audio Dynamic Range (-60 dB Input THD+N Referenced to              |     |       |          |       |

| Full-Scale, A-Weighted)                                            | 79  | 82    |          | dB    |

| Audio THD+N (Referenced to Full-Scale)                             |     |       | 0.019    | %     |

| , ,                                                                |     | -76   | -74.5    | dB    |

| Signal-to-Intermodulation Distortion* (CCIF Method)                |     | 82    |          | dB    |

| ADC Crosstalk*                                                     |     |       |          |       |

| Line Inputs (Input L, Ground R, Read R; Input R, Ground L, Read L) |     | -95   | -80      | dB    |

| Line to MIC (Input LINE, Ground and Select MIC, Read ADC)          |     | -95   | -80      | dB    |

| Line to SYNTH                                                      |     | -95   | -80      | dB    |

| Line to CD                                                         |     | -95   | -80      | dB    |

| Line to VID                                                        |     | -95   | -80      | dB    |

| Gain Error (Full-Scale Span Relative to Nominal Input Voltage)     |     |       | $\pm 10$ | %     |

| Interchannel Gain Mismatch (Difference of Gain Errors)             |     |       | ±1       | dB    |

| ADC Offset Error                                                   | -22 |       | +15      | mV    |

## **DIGITAL-TO-ANALOG CONVERTERS**

| Parameter                                                            | Min | Тур   | Max       | Units |

|----------------------------------------------------------------------|-----|-------|-----------|-------|

| Resolution                                                           |     | 16    |           | Bits  |

| Signal-to-Noise Ratio (SNR) (A-Weighted)                             |     | -83   | -79       | dB    |

| Total Harmonic Distortion (THD)                                      |     | 0.006 | 0.009     | %     |

|                                                                      |     | -85   | -80.5     | dB    |

| Audio Dynamic Range (-60 dB Input THD+N Referenced to                |     |       |           |       |

| Full Scale, A-Weighted)                                              | 79  | 82    |           | dB    |

| Audio THD+N (Referenced to Full Scale)                               |     | 0.013 | 0.017     | %     |

|                                                                      |     | -78   | -75.5     | dB    |

| Signal-to-Intermodulation Distortion* (CCIF Method)                  |     | 95    |           | dB    |

| Gain Error (Full-Scale Span Relative to Nominal Input Voltage)       |     |       | $\pm 10$  | %     |

| Interchannel Gain Mismatch (Difference of Gain Errors)               |     |       | $\pm 0.5$ | dB    |

| DAC Crosstalk* (Input L, Zero R, Measure R_OUT;                      |     |       |           |       |

| Input R, Zero L, Measure L_OUT)                                      |     |       | -80       | dB    |

| Total Out-of-Band Energy (Measured from $0.6 \times F_S$ to 100 kHz  |     |       |           |       |

| at L_OUT and R_OUT)*                                                 |     |       | -45       | dB    |

| Audible Out-of-Band Energy (Measured from $0.6 \times F_S$ to 20 kHz |     |       |           |       |

| at L_OUT and R_OUT)*                                                 |     |       | -75       | dB    |

## MASTER VOLUME ATTENUATORS (L\_OUT AND R\_OUT, PHONE\_OUT)

| Parameter                                      | Min | Тур  | Max | Units |

|------------------------------------------------|-----|------|-----|-------|

| Master Volume Step Size (0 dB to -43.5 dB)     |     | 1.5  |     | dB    |

| Master Volume Step Size (-43.5 dB to -46.5 dB) |     | 1.5  |     | dB    |

| Master Volume Output Attenuation Range Span    |     | 46.5 |     | dB    |

| Mute Attenuation of 0 dB Fundamental*          | 80  |      |     | dB    |

-4-

REV. 0

## **DIGITAL MIX ATTENUATORS\***

| Parameter                                                         | Min | Тур   | Max | Units |

|-------------------------------------------------------------------|-----|-------|-----|-------|

| Step Size: I <sup>2</sup> S (0), I <sup>2</sup> S (1), Music, ISA |     | 1.505 |     | dB    |

| Digital Mix Attenuation Range Span                                |     | 94.8  |     | dB    |

## ANALOG OUTPUT

| Parameter                                               | Min  | Тур     | Max  | Units |

|---------------------------------------------------------|------|---------|------|-------|

| Full-Scale Output Voltage (at L_OUT, R_OUT, PHONE_OUT ) |      | 2.8     |      | V p-p |

| Output Impedance*                                       |      |         | 570  | Ω     |

| External Load Impedance*                                | 10   |         |      | kΩ    |

| Output Capacitance*                                     |      | 15      |      | pF    |

| External Load Capacitance                               |      |         | 100  | pF    |

| $V_{ m REFX}*$                                          | 2.10 | 2.25    | 2.40 | V     |

| V <sub>REFX</sub> Current Drive*                        |      | 100     |      | μΑ    |

| V <sub>REFX</sub> Output Impedance*                     |      | 6.5     |      | kΩ    |

| Mute Click (Muted Analog Mixers), Muted Output Minus    |      |         |      |       |

| Unmuted Output at 0 dB                                  |      | $\pm 5$ |      | mV    |

## **SYSTEM SPECIFICATIONS\***

| Parameter                                              | Min | Тур | Max | Units   |

|--------------------------------------------------------|-----|-----|-----|---------|

| System Frequency Response Ripple (Line In to Line Out) |     |     | 1.0 | dB      |

| Differential Nonlinearity                              |     |     | ±1  | LSB     |

| Phase Linearity Deviation                              |     |     | 5   | Degrees |

#### STATIC DIGITAL SPECIFICATIONS

| Parameter                                                                 | Min | Тур | Max | Units |

|---------------------------------------------------------------------------|-----|-----|-----|-------|

| High Level Input Voltage (V <sub>IH</sub> )                               | 2   |     |     | V     |

| XTALI                                                                     | 2.4 |     |     | V     |

| Low Level Input Voltage (V <sub>IL</sub> )                                |     |     | 0.8 | V     |

| High Level Output Voltage ( $V_{OH}$ ), $I_{OH} = 8 \text{ mA}^{\dagger}$ | 2.4 |     |     | V     |

| Low Level Output Voltage ( $V_{OL}$ ), $I_{OL} = 8 \text{ mA}$            |     |     | 0.4 | V     |

| Input Leakage Current                                                     | -10 |     | +10 | μΑ    |

| Output Leakage Current                                                    | -10 |     | +10 | μA    |

## **POWER SUPPLY**

| Parameter                                                           | Min  | Тур | Max  | Units |

|---------------------------------------------------------------------|------|-----|------|-------|

| Power Supply Range—Analog                                           | 4.75 |     | 5.25 | V     |

| Power Supply Range—Digital                                          | 4.75 |     | 5.25 | V     |

| Power Supply Current                                                |      |     | 221  | mA    |

| Power Dissipation                                                   |      |     | 1105 | mW    |

| Analog Supply Current                                               |      |     | 51   | mA    |

| Digital Supply Current                                              |      |     | 170  | mA    |

| Analog Power Supply Current—Power-Down                              |      |     | 2    | mA    |

| Digital Power Supply Current—Power-Down                             |      |     | 24   | mA    |

| Analog Power Supply Current—RESET                                   |      |     | 0.2  | mA    |

| Digital Power Supply Current—RESET                                  |      |     | 10   | mA    |

| Power Supply Rejection (100 mV p-p Signal @ 1 kHz)* (At Both Analog |      |     |      |       |

| and Digital Supply Pins, Both ADCs and DACs)                        |      | 40  |      | dB    |

## **CLOCK SPECIFICATIONS\***

| Parameter                                                                             | Min | Тур      | Max       | Units          |

|---------------------------------------------------------------------------------------|-----|----------|-----------|----------------|

| Input Clock Frequency<br>Recommended Clock Duty Cycle<br>Power-Up Initialization Time | 25  | 33<br>50 | 75<br>500 | MHz<br>%<br>ms |

REV. 0 -5-

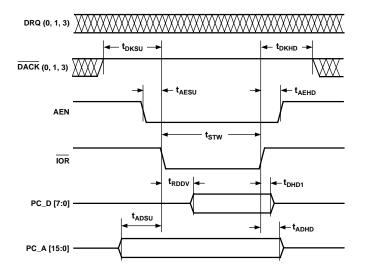

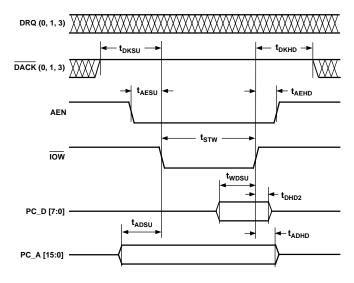

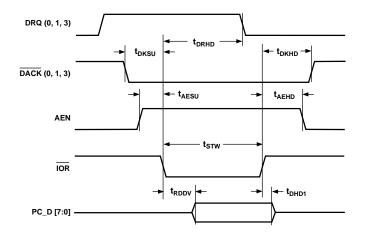

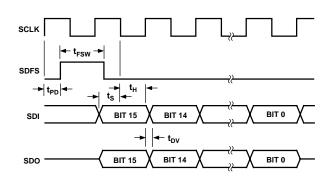

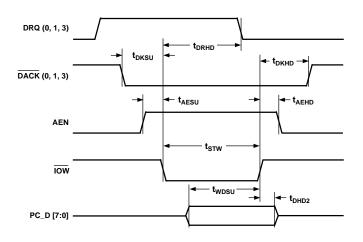

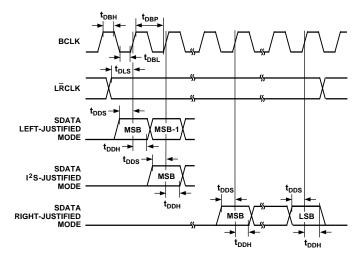

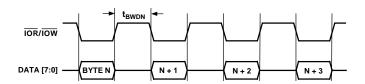

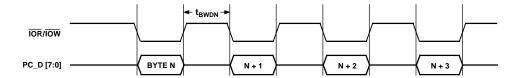

TIMING PARAMETERS (Guaranteed Over Operating Temperature Range)

| Parameter                                | Symbol            | Min | Тур | Max | Units |

|------------------------------------------|-------------------|-----|-----|-----|-------|

| IOW/IOR Strobe Width                     | $t_{ m STW}$      | 100 |     |     | ns    |

| IOW/IOR Rising to IOW/IOR Falling        | $t_{BWDN}$        | 80  |     |     | ns    |

| Write Data Setup to IOW Rising           | $t_{ m WDSU}$     | 10  |     |     | ns    |

| IOW Falling to Valid Read Data           | $t_{ m RDDV}$     |     |     | 40  | ns    |

| AEN Setup to IOW/IOR Falling             | t <sub>AESU</sub> | 10  |     |     | ns    |

| AEN Hold from IOW/IOR Rising             | t <sub>AEHD</sub> | 0   |     |     | ns    |

| Adr Setup to IOW/IOR Falling             | t <sub>ADSU</sub> | 10  |     |     | ns    |

| Adr Hold from IOW/IOR Rising             | t <sub>ADHD</sub> | 0   |     |     | ns    |

| DACK Rising to IOW/IOR Falling           | t <sub>DKSU</sub> | 20  |     |     | ns    |

| Data Hold from IOR Rising                | t <sub>DHD1</sub> |     |     | 2   | ns    |

| Data Hold from IOW Rising                | t <sub>DHD2</sub> | 15  |     |     | ns    |

| DRQ Hold from IOW/IOR Falling            | t <sub>DRHD</sub> |     |     | 25  | ns    |

| DACK Hold from IOW/IOR Rising            | t <sub>DKHD</sub> | 10  |     |     | ns    |

| Data [SDI] Input Setup Time to SCLK*     | $t_{\mathrm{S}}$  | 15  |     |     | ns    |

| Data [SDI] Input Hold Time from SCLK*    | t <sub>H</sub>    | 10  |     |     | ns    |

| Frame Sync [SDFS] HI Pulse Width*        | $t_{ m FSW}$      |     | 80  |     | ns    |

| Clock [SCLK] to Frame Sync [SDFS]        |                   |     |     |     |       |

| Propagation Delay*                       | $t_{\rm PD}$      |     |     | 15  | ns    |

| Clock [SCLK] to Output Data [SDO] Valid* | $t_{DV}$          |     |     | 15  | ns    |

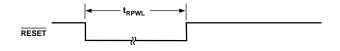

| RESET Pulse Width                        | $t_{ m RPWL}$     | 100 |     |     | ns    |

| BCLK HI Pulse Width                      | t <sub>DBH</sub>  | 25  |     |     | ns    |

| BCLK LO Pulse Width                      | t <sub>DBL</sub>  | 25  |     |     | ns    |

| BCLK Period                              | t <sub>DBP</sub>  | 50  |     |     | ns    |

| LRCLK Setup                              | $t_{ m DLS}$      | 5   |     |     | ns    |

| SDATA Setup                              | $t_{ m DDS}$      | 5   |     |     | ns    |

| SDATA Hold                               | t <sub>DDH</sub>  | 5   |     |     | ns    |

### NOTES

Specifications subject to change without notice.

Figure 1. PIO Read Cycle

Figure 2. PIO Write Cycle

<sup>\*</sup>Guaranteed, not tested.

$<sup>\</sup>dagger$ (All ISA pins MIDI\_OUT IOL = 24 mA. Refer to pin description for individual output drive levels.

Figure 3. DMA Read Cycle

Figure 6. DSP Port Timing

Figure 4. DMA Write Cycle

Figure 7. I<sup>2</sup>S Serial Port Timing

Figure 5. Codec Transfers

Figure 8. Reset Pulse Width

REV. 0 -7-

#### ABSOLUTE MAXIMUM RATINGS\*

| Parameter                           | Min  | Max                | Units |

|-------------------------------------|------|--------------------|-------|

| Power Supplies                      |      |                    |       |

| Digital $(V_{DD})$                  | -0.3 | 6.0                | V     |

| Analog (V <sub>CC</sub> )           | -0.3 | 6.0                | V     |

| Input Current (Except Supply Pins)  |      | $\pm 10.0$         | mA    |

| Analog Input Voltage (Signal Pins)  | -0.3 | $V_{CC} + 0.3$     | V     |

| Digital Input Voltage (Signal Pins) | -0.3 | $V_{\rm DD} + 0.3$ | V     |

| Ambient Temperature (Operating)     | 0    | +70                | °C    |

| Storage Temperature                 | -65  | +150               | °C    |

<sup>\*</sup>Stresses greater than those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ENVIRONMENTAL CONDITIONS**

Ambient Temperature Rating:

$\begin{array}{ll} T_{AMB} &= T_{CASE} - (PD \times \theta_{CA}) \\ T_{CASE} &= Case \ Temperature \ in \ ^{\circ}C \\ PD &= Power \ Dissipation \ in \ W \end{array}$

$\begin{array}{ll} \theta_{CA} & = Thermal \; Resistance \; (Case-to-Ambient) \\ \theta_{JA} & = Thermal \; Resistance \; (Junction-to-Ambient) \\ \theta_{IC} & = Thermal \; Resistance \; (Junction-to-Case) \end{array}$

| Package | $\theta_{ m JA}$ | $\theta_{ m JC}$ | $\theta_{CA}$ |  |

|---------|------------------|------------------|---------------|--|

| PQFP    | 77°C/W           | 7°C/W            | 70°C/W        |  |

#### **ORDERING GUIDE**

| Model      | Temperature  | Package       | Function    | Package |

|------------|--------------|---------------|-------------|---------|

|            | Range        | Description   | Description | Option* |

| AD1821JS   | 0°C to +70°C | 100-Lead PQFP | Audio/Modem | S-100   |

| AD1821JS-M | 0°C to +70°C | 100-Lead PQFP | Modem       | S-100   |

<sup>\*</sup>S = Plastic Quad Flatpack.

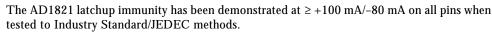

#### CAUTION\_

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD1821 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

\_8\_ REV. 0

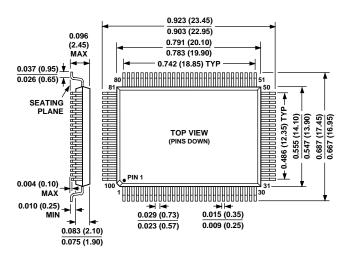

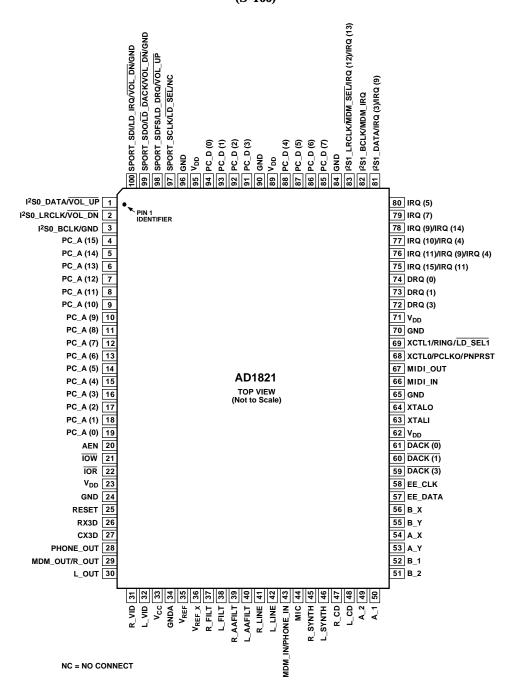

## PIN CONFIGURATION 100-Lead PQFP (S-100)

REV. 0 \_9\_

## PIN FUNCTION DESCRIPTIONS

**Analog Signals**

| Pin Name            | PQFP | I/O | Description                                                                                                                                                                                                                                                                                                                                                                                         |

|---------------------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| MIC                 | 44   | I   | Microphone Input. The MIC input may be either line-level or -20 dB from line-level (the difference being made up through a software controlled 20 dB gain block). The mono MIC input may be sent to the left and right channel of the ADC for conversion, or gained/attenuated from +12 dB to -34.5 dB in 1.5 dB steps and then summed with left and right line OUT before the Master Volume stage. |

| L_LINE              | 42   | I   | Left Line-Level Input. The left line-level input may be: sent to the left channel of the ADC; gained/attenuated from +12 dB to -34.5 dB in 1.5 dB steps and then summed with left line OUT.                                                                                                                                                                                                         |

| R_LINE              | 41   | I   | Right Line-Level Input. The right line-level input may be: sent to the right channel of the ADC; gained/attenuated from +12 dB to -34.5 dB in 1.5 dB steps and then summed with right line OUT.                                                                                                                                                                                                     |

| L_SYNTH             | 46   | I   | Left Synthesizer Input. The left MIDI upgrade line-level input may be: sent to the left channel of the ADC; gained/attenuated from +12 dB to -34.5 dB in 1.5 dB steps and then summed with left line OUT.                                                                                                                                                                                           |

| R_SYNTH             | 45   | I   | Right Synthesizer Input. The right MIDI upgrade line-level input may be: sent to the right channel of the ADC; gained/attenuated from +12 dB to -34.5 dB in 1.5 dB steps and then summed with right line OUT.                                                                                                                                                                                       |

| L_CD                | 48   | I   | Left CD Line-Level Input. The left CD line-level input may be: sent to the left channel of the ADC; gained/attenuated from +12 dB to -34.5 dB in 1.5 dB steps and then summed with left line OUT.                                                                                                                                                                                                   |

| R_CD                | 47   | I   | Right CD Line-Level Input. The right CD line-level input may be: sent to the right channel of the ADC; gained/attenuated from +12 dB to -34.5 dB in 1.5 dB steps and then summed with right line OUT.                                                                                                                                                                                               |

| L_VID               | 32   | I   | Left Video Input. The left audio track for a video line-level input may be: sent to the left channel of the ADC; gained/attenuated from +12 dB to -34.5 dB in 1.5 dB steps and then summed with left line OUT.                                                                                                                                                                                      |

| R_VID               | 31   | I   | Right Video Input. The right audio track for a video line-level input may be: sent to the right channel of the ADC; gained/attenuated from +12 dB to -34.5 dB in 1.5 dB steps and then summed with right line OUT.                                                                                                                                                                                  |

| L_OUT               | 30   | О   | Left Output. Left channel line-level post-mixed output. The final stage passes through the Master Volume block and may be attenuated 0 dB to -45 dB in 1.5 dB steps.                                                                                                                                                                                                                                |

| MDM_OUT/<br>R_OUT   | 29   | 0   | Modem Output/Right Output. Right channel line-level post-mixed output. The final stage passes through the Master Volume block and may be attenuated 0 dB to -45 dB in 1.5 dB steps.                                                                                                                                                                                                                 |

| MDM_IN/<br>PHONE_IN | 43   | I   | Modem Input/Phone Input. Line-level input from a DAA/modem chipset.                                                                                                                                                                                                                                                                                                                                 |

| PHONE_OUT           | 28   | 0   | Phone Output. Line-level output from a DAA/modem chipset.                                                                                                                                                                                                                                                                                                                                           |

| RX3D                | 26   | О   | Phat™* Stereo Phase Expander filter network, resistor pin.                                                                                                                                                                                                                                                                                                                                          |

| CX3D                | 27   | I   | Phat™* Stereo Phase Expander filter network, capacitor pin.                                                                                                                                                                                                                                                                                                                                         |

## Parallel Interface (All Outputs are 24 mA Drivers)

| Pin Name   | PQFP         | I/O          | Description                                                                                                                                                                                                          |

|------------|--------------|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PC_D[7:0]  | 85-88, 91-94 | 83-86, 89-92 | I/O Bidirectional ISA Bus PC Data, 24 mA drive. Connects the AD1821 to the low byte data on the bus.                                                                                                                 |

| IRQ(x)*    | 75–81, 83    | 0            | Host Interrupt Request, 24 mA drive. IRQ (3)/IRQ (9), IRQ(5), IRQ(7), IRQ(9)/IRQ (14), IRQ(10)/IRQ(4), IRQ(11)/IRQ (9)/IRQ (4), IRQ(12)/IRQ(13), IRQ(15)/IRQ (11). Active HI signals indicating a pending interrupt. |

| DRQ(x)     | 72-74        | О            | DMA Request, 24 mA drive. DRQ(0), DRQ(1), DRQ(3). Active HI signals indicating a request for DMA bus operation.                                                                                                      |

| PC_A[15:0] | 4–19         | I            | ISA Bus PC Address. Connects the AD1821 to the ISA bus address lines.                                                                                                                                                |

| AEN        | 20           | I            | Address Enable. Low signal indicates a PIO transfer.                                                                                                                                                                 |

| DACK (x)   | 59-61        | I            | DMA Acknowledge. DACK(0), DACK(1), DACK(3). Active LO signal indicating that a DMA operation can begin.                                                                                                              |

| ĪOR        | 22           | I            | I/O Read. Active LO signal indicates a read operation.                                                                                                                                                               |

| ĪOW        | 21           | I            | I/O Write. Active HI signal indicates a write operation.                                                                                                                                                             |

| RESET      | 25           | I            | Reset. Active HI.                                                                                                                                                                                                    |

#### **Game Port**

| Pin Name | PQFP | I/O | Description             |

|----------|------|-----|-------------------------|

| A_1      | 50   | I   | Game Port A, Button #1. |

| A_2      | 49   | I   | Game Port A, Button #2. |

| A_X      | 54   | I   | Game Port A, X-Axis.    |

| A_Y      | 53   | I   | Game Port A, Y-Axis.    |

| B_1      | 52   | I   | Game Port B, Button #1. |

| B_2      | 51   | I   | Game Port B, Button #2. |

| B_X      | 56   | I   | Game Port B, X-Axis.    |

| B_Y      | 55   | I   | Game Port B, Y-Axis.    |

## MIDI Interface Signal (24 mA Drivers)

| Pin Name | PQFP | I/O | Description                                                                            |

|----------|------|-----|----------------------------------------------------------------------------------------|

| MIDI_IN  | 66   | I   | RXD MIDI Input. This pin is typically connected to Pin 15 of the game port connector.  |

| MIDI_OUT | 67   | О   | TXD MIDI Output. This pin is typically connected to Pin 12 of the game port connector. |

REV. 0 -11-

## Muxed Serial Ports (8 mA Drivers)

| Pin Name                   | PQFP | I/O | Description                                    |

|----------------------------|------|-----|------------------------------------------------|

| I <sup>2</sup> S(0)_BCLK*  | 3    | I   | I <sup>2</sup> S (0) Bit Clock.                |

| I <sup>2</sup> S(0)_LRCLK* | 2    | I   | I <sup>2</sup> S (0) Left/Right Clock.         |

| $I^2S(0)_DATA^*$           | 1    | I   | I <sup>2</sup> S (0) Serial Data Input.        |

| I <sup>2</sup> S(1)_BCLK*  | 82   | I   | I <sup>2</sup> S (1) Bit Clock.                |

| I <sup>2</sup> S(1)_LRCLK* | 83   | I   | I <sup>2</sup> S (1) Left/Right Clock.         |

| $I^2S(1)_DATA^*$           | 81   | I   | I <sup>2</sup> S (1) Serial Data Input.        |

| SPORT_SDI*                 | 100  | I   | Serial Port Digital Serial Input.              |

| SPORT_SCLK*                | 97   | О   | Serial Port Serial Clock.                      |

| SPORT_SDFS*                | 98   | О   | Serial Port Serial Data Frame Synchronization. |

| SPORT_SDO*                 | 99   | О   | Serial Port Serial Data Output.                |

## **Miscellaneous Analog Pins**

| Pin Name                        | PQFP | I/O | Description                                                                                                                                                           |  |

|---------------------------------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| $\overline{V_{	ext{REF}_{-}X}}$ | 36   | О   | Voltage Reference. Nominal 2.25 volt reference available for dc-coupling and level-shifting. $V_{\text{REF\_X}}$ should not be used to sink or source signal current. |  |

| $V_{ m REF}$                    | 35   | I   | Voltage Reference Filter. Voltage reference filter point for external bypassing only.                                                                                 |  |

| L_FILT                          | 38   | I   | Left Channel Filter. Requires a 1.0 $\mu F$ to analog ground for proper operation.                                                                                    |  |

| R_FILT                          | 37   | I   | Right Channel Filter. Requires a 1.0 $\mu F$ to analog ground for proper operation.                                                                                   |  |

| L_AAFILT                        | 40   | I   | Left Channel Antialias Filter. This pin requires a 270 pF NPO capacitor to analog ground for proper operation.                                                        |  |

| R_AAFILT                        | 39   | I   | Right Channel Antialias Filter. This pin requires a 270 pF NPO capacitor to analog ground for proper operation.                                                       |  |

## **Crystal Pin**

| Pin Name | PQFP | I/O | Description                                                                                                                                                                                                                                                                                                                |  |

|----------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| XTALO    | 64   | 0   | 33 MHz Crystal Output. If no Crystal is present leave XTALO unconnected.                                                                                                                                                                                                                                                   |  |

| XTALI    | 63   | I   | 33 MHz Clock. When using a crystal as a clock source, the crystal should be connected between the XTALI and XTALO pins. Clock input may be driven into XTALI in place of a crystal. When using an external clock, $V_{\rm IH}$ must be 2.4 V rather than the $V_{\rm IH}$ of 2.0 V specified for all other digital inputs. |  |

## **External Logical Devices**

| Pin Name         | PQFP | I/O | Description                |

|------------------|------|-----|----------------------------|

| LD_IRQ*          | 100  | I   | Logical Device IRQ.        |

| LD_DACK*         | 99   | 0   | Logical Device DACK.       |

| LD_DRQ*          | 98   | I   | Logical Device DRQ.        |

| TD_SEL*          | 97   | О   | Logical Device Select.     |

| MDM_SEL*         | 83   | О   | Modem Chip Set Select.     |

| MDM_IRQ*         | 82   | I   | Modem Chip Set IRQ.        |

| <u>LD_SEL1</u> ∗ | 69   | 0   | Logical Device (1) Select. |

| PNPRST*          | 68   | 0   | Plug and Play Reset.       |

-12- REV. 0

#### **Hardware Volume Pins**

| Pin Name | PQFP       | I/O | Description                                                                                                                                                                                                                                                                                                                                                          |

|----------|------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VOL_DN*  | 2, 99, 100 | I   | Master Volume Down. Modifies output level on pins L_OUT and R_OUT. Contains a 10 k $\Omega$ internal pull-up resistor. When asserted LO, decreases Master Volume by 1.5 dB/sec. Must be asserted at least 25 ms to be recognized. When asserted simultaneously with VOL_UP, output is muted. Output level modification reflected in indirect register 0 $\times$ 29. |

| VOL_UP*  | 1, 98      | I   | Master Volume Up. Modifies output level on pins L_OUT and R_OUT. Contains a 10 k $\Omega$ internal pull-up resistor. When asserted LO, increases Master Volume by 1.5 dB/sec. Must be asserted at least 25 ms to be recognized. When asserted simultaneously with VOL_UP, output is muted. Output level modification reflected in indirect register 0 × 29.          |

## **Control Pins**

| Pin Name | PQFP | I/O | Description                                                                                                                                                                                                                                                                                                    |  |

|----------|------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| XCTL0*   | 68   | 0   | External Control 0. The state of this pin (TTL HI or LO) is reflected in codec indexed register. This pin is an open drain driver.                                                                                                                                                                             |  |

| PCLKO*   | 68   | О   | Programmable Clock Output. This pin can be programmed to generate an output clock equal to $F_S$ , $8 \times F_S$ , $16 \times F_S$ , $32 \times F_S$ , $64 \times F_S$ , $128 \times F_S$ or $256 \times F_S$ . MPEG decoders typically require a master clock of $256 \times F_S$ for audio synchronization. |  |

| XCTL1*   | 69   | О   | External Control 1. The state of this pin (TTL HI or LO) is reflected in codec indexed register. Open drain, 8 mA active 0.5 mA pull-up resistor.                                                                                                                                                              |  |

| RING*    | 69   | I   | Ring Indicator. Used to accept the ring indicator flag from the DAA.                                                                                                                                                                                                                                           |  |

## **Power Supplies**

| Pin Name            | PQFP                                        | I/O | Description                    |

|---------------------|---------------------------------------------|-----|--------------------------------|

| $\overline{V_{CC}}$ | 33                                          | I   | Analog Supply Voltage (+5 V).  |

| GNDA                | 34                                          | I   | Analog Ground.                 |

| $V_{DD}$            | 23, 62, 71,<br>89, 95                       | I   | Digital Supply Voltage (+5 V). |

| GND                 | 3*, 24, 65,<br>70, 84, 90,<br>96, 99*, 100* | I   | Digital Ground.                |

## **Optional EEPROM Pins**

| Pin Name | PQFP | I/O | Description   |

|----------|------|-----|---------------|

| EE_CLK   | 58   | О   | EEPROM Clock. |

| EE_DATA  | 57   | I   | EEPROM Data.  |

<sup>\*</sup>The position of this pin location/function is dependent on the EEPROM data.

REV. 0 -13-

#### **HOST INTERFACE**

The AD1821 contains all necessary ISA bus interface logic onchip. This logic includes address decoding for all onboard resources, control and signal interpretation, DMA selection and control logic, IRQ selection and control logic, and all interface configuration logic.

The AD1821 supports a Type "F" DMA request/grant architecture for transferring data with the ISA bus through the 8-bit interface. The AD1821 also supports DACK preemption. Programmed I/O (PIO) mode is also supported for control register accesses and for applications lacking DMA control. The AD1821 includes dual DMA count registers for full-duplex operation enabling simultaneous capture and playback on separate DMA channels.

#### **Codec Functional Description**

The AD1821's full-duplex stereo codec supports business audio and multimedia applications. The codec includes stereo audio converters, complete on-chip filtering, MPC Level-2 and Level-3 compliant analog mixing, programmable gain and attenuation, a variable sample rate converter, extensive digital mixing and FIFOs buffering the Plug and Play ISA bus interface. When using MODIO modem software, PHONE\_IN and R\_OUT channels are used to support modem and telephony features.

#### **Analog Inputs**

The codec contains a stereo pair of  $\Sigma\Delta$  analog-to-digital converters (ADC). Inputs to the ADC can be selected from the following analog signals: mono (PHONE\_IN), mono microphone (MIC), stereo line (LINE), external stereo synthesizer (SYNTH), stereo CD ROM (CD), stereo audio from a video source (VID) and post-mixed stereo or mono line output (OUT).

#### Analog Mixing

PHONE\_IN, MIC, LINE, SYNTH, CD and VID can be mixed in the analog domain with the stereo line OUT from the  $\Sigma\Delta$  digital-to-analog converters (DAC). Each channel of the stereo analog inputs can be independently gained or attenuated from +12 dB to -34.5 dB in 1.5 dB steps, except for PHONE\_IN, which has a range of 0 dB to -45 dB steps. The summing path for the mono inputs (MIC, and PHONE\_IN to line OUT) duplicates mono channel data on both the left and right line OUT, which can also be gained or attenuated from +12 dB to -34.5 dB in 1.5 dB steps for MIC, and +0 dB to -45.5 dB in 3 dB steps for PHONE\_IN. The left and right mono summing signals are always identical being equally gained or attenuated.

#### Analog-to-Digital Datapath

The selector sends left and right channel information to the programmable gain amplifier (PGA). The PGA following the selector allows independent gain for each channel entering the ADC from 0 dB to 22.5 dB in 1.5 dB steps.

For supporting time correlated I/O echo cancellation, the ADC is capable of sampling microphone data on the left channel and the mono summation of left and right OUT on the right channel.

The codec can operate in either a global stereo mode or a global mono mode with left channel inputs appearing at both channels of the 16-bit  $\Sigma\Delta$  converters. Data can be sampled at the programmed sampling frequency (from 4 kHz to 55.2 kHz with 1 Hz resolution).

#### **Digital Mixing & Sample Rates**

The audio ADC sample rate and the audio DAC sample rates

are completely independent. The AD1821 includes a variable sample rate converter that lets the codec instantaneously change and process sample rates from 4 kHz to 55.2 kHz with a resolution of 1 Hz. The in-band integrated noise and distortion artifacts introduced by rate conversions are below -90 dB.

Up to four channels of digital data can be summed together and presented to the stereo DAC for conversion. Each digital channel pair can contain information encoded at a different sample rate. For example, 8 kHz .wav data received from the ISA interface, 48 kHz MPEG audio data received from I<sup>2</sup>S(0), digital 44.1 kHz CD data received from I<sup>2</sup>S(1) and internally generated 22.05 kHz music data may be summed together and converted by the DACs.

#### Digital-to-Analog Datapath

The internally generated music synthesizer data, PCM data received from the ISA interface, data received from the I $^2$ S(0) port and data received from the I $^2$ S(1) port, and the DSP serial port passes through an attenuation mute stage. The attenuator allows independent control over each digital channel, which can be attenuated from 0 dB to -94.5 dB in 1.5 dB steps before being summed together and passed to the DAC, or the channel may be muted entirely.

#### **Analog Outputs**

The analog output of the DAC can be summed with any of the analog input signals. The summed analog signal enters the Master Volume stage where each channel L\_OUT, R\_OUT and PHONE\_OUT may be attenuated from 0 dB to -46.5 dB in 1.5 dB steps or muted.

## Digital Data Types

The codec can process 16-bit twos-complement PCM linear digital data, 8-bit unsigned magnitude PCM linear data and 8-bit  $\mu$ -law or A-law companded digital data as specified in the control registers. The AD1821 also supports ADPCM encoded in the Creative SoundBlaster ADPCM formats.

#### **Host-Based Echo Cancellation Support**

The AD1821 supports time correlated I/O data format by presenting MIC data on the left channel of the ADC and the mono summation of left and right OUT on the right channel. The ADC sample rates are independent of the DAC sample rate allowing the AD1821 to support ADC time correlated I/O data at 8 kHz and DAC data at any other sample rate in the range of 4 kHz to 55.2 kHz simultaneously.

#### **Telephony Support**

The AD1821 contains a PHONE\_IN input and a PHONE\_OUT output. These pins are supplied so the AD1821 may be connected to a modem chip set, a telephone handset or down-line phone.

#### WSS and SoundBlaster Compatibility

Windows Sound System software audio compatibility is built into the AD1821.

SoundBlaster emulation is provided through the SoundBlaster register set and the internal music synthesizer. SoundBlaster Pro version 2.01 functions are supported, including record and Creative SoundBlaster ADPCM.

Virtually all applications developed for SoundBlaster, Windows Sound System, AdLib and MIDI MPU-401 platforms run on the AD1821 SoundComm® Controller. Follow the same development process for the controller as you would for these other devices.

As the AD1821 contains SoundBlaster (compatible) and Windows Sound System logical devices. You may find the following related development kits useful when developing AD1821 applications.

Developer Kit for SoundBlaster Series, 2nd ed. © 1993, Creative Labs, Inc., 1901 McCarthy Blvd., Milpitas, CA 95035 Microsoft Windows Sound System Driver Development Kit (CD), Version 2.0, © 1993, Microsoft Corp., One Microsoft Way, Redmond, WA 98052

The following reference texts can serve as additional sources of information on developing applications that run on the AD1821.

- S. De Furia & J. Scacciaferro, The MIDI Implementation Book, (© 1986, Third Earth, Pompton Lake)

- C. Petzold, Programming Windows: the Microsoft guide to writing applications for Windows 3.1, 3rd. ed., (© 1992, Microsoft Press. Redmond)

- K. Pohlmann, Principles of Digital Audio, (© 1989, Sams, **Indianapolis**)

- A. Stolz, The SoundBlaster Book, (© 1993, Abacaus, Grand Rapids)

- J. Strawn, Digital Audio Engineering, An Anthology, (© 1985, Kaufmann, Los Altos)

Yamamoto, MIDI Guidebook, 4th. ed., (© 1987, 1989, Roland Corp.)

#### **Multimedia PC Capabilities**

The AD1821 is MPC-2 and MPC-3 compliant. This compliance is achieved through the AD1821's flexible mixer and the embedded chip resources.

#### Music Synthesis

The AD1821 includes an embedded music synthesizer that emulates industry standard OPL3 FM synthesizer chips and delivers 20 voice polyphony. The internal synthesizer generates digital music data at 22.05 kHz and is summed into the DACs digital data stream prior to conversion. To sum synthesizer data with the ADC output, the ADC must be programmed for a 22.05 kHz sample rate.

The synthesizer is a hardware implementation of Eusynth-1+ code that was developed by Euphonics, a research and development company that specializes in audio processing and electronic music synthesis.

#### Wavetable MIDI Inputs

The AD1821 has a dedicated analog input for receiving an analog wavetable synthesizer output. Alternatively, a wavetable synthesizer's I<sup>2</sup>S formatted digital output can be directly connected to one of the AD1821's I2S serial ports. Digital wavetable data from the AD1821's I<sup>2</sup>S port may be summed with other digital data streams being handled by the AD1821 and then sent to the 16-bit  $\Sigma\Delta$  DAC.

The primary interface for communicating MIDI data to and from the host PC is the compatible MPU-401 interface that operates in UART mode. The MPU-401 interface has two

built-in FIFOs: a 64 byte receive FIFO and a 16 byte transmit FIFO.

#### Game Port

An IBM-compatible game port interface is provided on chip. The game port supports up to two joysticks via a 15-pin D-sub connector. Joystick registers supporting the Microsoft Direct Input standard are included as part of the register map. The AD1821 may be programmed to automatically sample the game port and save the value in the Joystick Position Data Register. When enabled, this feature saves up to 10% CPU MIPS by off-loading the host from constantly polling the joystick port.

#### **Volume Control**

The registers that control the Master Volume output stage are accessible through the parallel port. Master Volume output can also be controlled through a 2-pin hardware interface. One pin is used to increase the gain, the other pin attenuates the output and both pins together entirely mute the output. Once muted, any further activity of these pins will unmute the AD1821's output.

#### **Plug and Play Configuration**

The AD1821 is fully Plug and Play configurable. For motherboard applications, the built-in Plug and Play protocol can be disabled with a software key providing a back door for the BIOS to configure the AD1821's logical devices. For information on the Plug and Play mode configuration process, see the Plug and Play ISA Specification Version 1.0a (May 5, 1994). All the AD1821's logical devices comply with Plug and Play resource definitions described in the specification.

The AD1821 may alternatively be configured using an optional Plug and Play Resource ROM. When the EEPROM is present, some additional AD1821 muxed-pin features become available. For example, pins that control an external modem logical device are muxed with the DSP serial port. Some of these pin option combinations are mutually exclusive (see Appendix A for more information).

#### REFERENCES

The AD1821 also complies with the following related specifications; they can be used as an additional reference to AD1821 operations beyond the material in this data sheet.

Plug and Play ISA Specification, Version 1.0a, © 1993, 1994, Intel Corp. & Microsoft Corp., One Microsoft Way, Redmond, WA 98052

Multimedia PC Level 2 Specification, © 1993, Multimedia PC Marketing Council, 1730 M St. NW, Suite 707, Washington, DC 20036

MIDI 1.0 Detailed Specification & Standard MIDI Files 1.0, © 1994, MIDI Manufacturers Association, PO Box 3173 La Habra, CA 90632-3173

Recommendation G.711-Pulse Code Modulation (PCM) Of Voice Frequencies (µ-Law & A-Law Companding), The International Telegraph and Telephone Consultative Committee IX Plenary Assembly Blue Book, Volume III - Fascicle III.4, General Aspects Of Digital Transmission Systems; Terminal Equipment's, Recommendations G.700 - G.795, (Geneva, 1988), ISBN 92-61-03341-5

IMA Digital Audio Doc-Pac (IMA-ADPCM), © 1992, Interactive Multimedia Association, 48 Maryland Avenue, Suite 202, Annapolis, MD 21401-8011

#### SERIAL INTERFACES

#### I<sup>2</sup>S Serial Ports

The two I<sup>2</sup>S serial ports on the AD1821 accept serial data in the following formats: Right-Justified, I<sup>2</sup>S-Justified and Left-Justified.

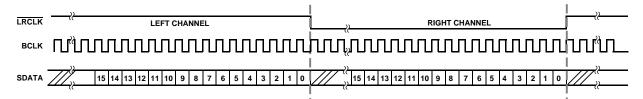

Figure 9 shows the right-justified mode. LRCLK is HI for the left channel and LO for the right channel. Data is valid on the rising edge of the BCLK. The MSB is delayed 16-bit clock periods from an LRCLK transition, so that when there are 64 BCLK periods per LRCLK period, the LSB of the data will be right-justified to the next LRCLK transition.

Figure 9. Serial Interface Right-Justified Mode

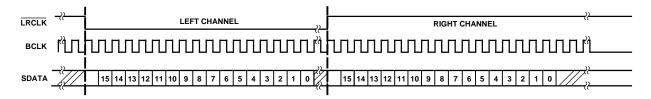

Figure 10 shows the I<sup>2</sup>S-justified mode. LRCLK is LO for the left channel and HI for the right channel. Data is valid on the rising edge of BCLK. The MSB is left-justified to an LRCLK transition, but with a single BCLK period delay.

Figure 10. Serial Interface I<sup>2</sup>S-Justified Mode

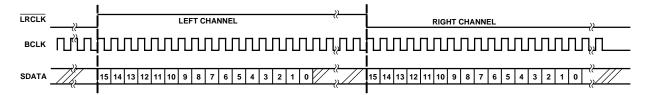

Figure 11 shows the left-justified mode. LRCLK is HI for the left channel and LO for the right channel. Data is valid on the rising edge of BCLK. The MSB is left-justified to an LRCLK transition, with no MSB delay.

Figure 11. Serial Interface Left-Justified Mode

#### **Bidirectional DSP Serial Interface**

The AD1821 SoundComm® Controller transmits and receives both data and control/status information through its DSP serial interface port (SPORT). The AD1821 is always the bus master and supplies the frame sync and the serial clock. The AD1821 has four pins assigned to the SPORT: SDI, SDO, SDFS, and SCLK. The SPORT has two operating modes: monitor and intercept. The SPORT always monitors the various data streams being processed by the AD1821. In intercept mode, any of the digital data streams can be manipulated by the DSP before reaching the final ADC or DAC stages.

The SDI and SDO pins handle the serial data input and output of the AD1821. Communication in and out of the AD1821 requires that bits of data be transmitted after a rising edge of SCLK and sampled on the falling edge of SCLK. The SCLK frequency is always 11 MHz (or 1/3 or XTALI).

DSP Serial Port Interface time slots are mapped as shown in Table I.

**Table I. DSP Port Time Slot Map**

| Time Slot | SDI Pin                                           | SDO Pin                                                                |

|-----------|---------------------------------------------------|------------------------------------------------------------------------|

| 0         | Control Word Input                                | Status Word Output                                                     |

| 1         | Control Register Data Input                       | Control Register Data Output                                           |

| 2         | * SS/SB ADC Right Input (to ISA)                  | SS/SB ADC Right Output (from Codec)                                    |

| 3         | * SS/SB ADC Left Input (to ISA)                   | SS/SB ADC Left Output (from Codec)                                     |

| 4         | * SS/SB DAC Right Input (to Codec)                | SS/SB DAC Right Output (from ISA)                                      |

| 5         | * SS/SB DAC Left Input (to Codec)                 | SS/SB DAC Left Output (from ISA)                                       |

| 6         | * FM DAC Right Input (to Codec)                   | FM DAC Right Output (from FM Synth Block)                              |

| 7         | * FM DAC Left Input (to Codec)                    | FM DAC Left Output (from FM Synth Block)                               |

| 8         | * I <sup>2</sup> S (1) DAC Right Input (to Codec) | I <sup>2</sup> S (1) DAC Right Output (from I <sup>2</sup> S Port [1]) |

| 9         | * I <sup>2</sup> S (1) DAC Left Input (to Codec)  | I <sup>2</sup> S (1) DAC Left Output (from I <sup>2</sup> S Port [1])  |

| 10        | * I <sup>2</sup> S (0) DAC Right Input (to Codec) | I <sup>2</sup> S (0) DAC Right Output (from I <sup>2</sup> S Port [0]) |

| 11        | * I <sup>2</sup> S (0) DAC Left Input (to Codec)  | I <sup>2</sup> S (0) DAC Left Output (from I <sup>2</sup> S Port [0])  |

<sup>\*</sup>This data is ignored by the AD1821 unless the channel pair is in intercept mode (see below).

At start-up (after pin reset), there are exactly 12 time slots per frame. The frame rate will be 57,291 and 2/3 Hz ( $11\,MHz$  sclk/ (16 bits  $\times$  12 slots)). Interfacing with an Analog Devices 21xx family DSP can be achieved by putting the ADSP-21xx in 24 slot per frame mode, where the first 12 and second 12 slots in the ADSP-21xx frame are identical.

The frame rate can be changed from its default by a write to the DFS(2:0) bits in register 33. Rate choices are: Maximum (57,291 and 2/3 Hz default), SS capture rate, SS playback rate, FM rate,  $I^2S$  Port (1) rate, or  $I^2S$  Port (0) rate. When the frame rate is less than 57,261 and 2/3 Hz, extra SCLK periods are added to fill up the time. The number of SCLK periods added will vary somewhat from frame to frame.

To control the sample data flow of each channel through the DSP Port, valid input, valid output and request bits are located in the control and status words. If the specified channel sample rate is equal to the frame rate, these bits may be ignored since they will always be set to "1".

By default, the DSP serial port allows only codec sample data I/O to be monitored. Intercept modes must be enabled to make substitutions in sample data flow to and from the codec. There are five bits in SS register 33, which enable intercept mode for SS capture, SS playback, FM playback,  $I^2S$  Port (1) playback and  $I^2S$  Port (0) playback.

#### **Control Word Input (Slot 0 SDI)**

| 15    | 14  | 13  | 12    | 11      | 10   | 9     | 8     |

|-------|-----|-----|-------|---------|------|-------|-------|

| FCLR  | RES | RES | SSCVI | SSPVI   | FMVI | IS1VI | IS0VI |

| 7     | 6   | 5   | 4     | 3       | 2    | 1     | 0     |

| ALIVE | R/W |     |       | IA[5:0] |      |       |       |

| IA [5:0] | Indirect Register Address. Sound System Indirect Register Address defines the address of indirect registers shown | l |

|----------|-------------------------------------------------------------------------------------------------------------------|---|

|          | in Table VI.                                                                                                      |   |

| R/W | Read/Write request. Either a read from or a write to an SS indirect register occurs every frame. Setting this bit ini- |

|-----|------------------------------------------------------------------------------------------------------------------------|

|     | tiates an SS indirect register read while clearing this bit initiates an SS indirect register write.                   |

| ALIVE | DSP port alive bit. When set, this bit indicates to the power-down timer that the DSP port is active. When cleared, |

|-------|---------------------------------------------------------------------------------------------------------------------|

|       |                                                                                                                     |

this bit indicates that the DSP port is inactive.

ISOVI I<sup>2</sup>S Port 0 Substitution Data Input Valid Flag. This bit is ignored if: (1) Intercept mode is not enabled for the I<sup>2</sup>S port 0 channel pair, or (2) The AD1821 did not request data from the I<sup>2</sup>S port 0 channel pair in the previous frame. Otherwise, setting this bit indicates that slots 10 and 11 contain valid right and left I<sup>2</sup>S Port 0 substitution

data. When this bit is cleared, data in slots 10 and 11 is ignored.

I<sup>2</sup>S Port 1 Substitution Data Input Valid Flag. This bit is ignored if: (1) Intercept mode is not enabled for I<sup>2</sup>S port 1 channel pair or (2) The AD1821 did not request data from the I<sup>2</sup>S port channel pair in the previous frame. Otherwise, setting this bit indicates that Slots 8 and 9 contain valid right and left I<sup>2</sup>S Port 1 substitution data. When this bit is cleared, data in slots 8 and 9 is ignored.

FM Synthesis Substitution Data Input Valid Flag. This bit is ignored if: (1) Intercept mode is not enabled for the FM synthesis channel pair or (2) The AD1821 did not request data from the FM synthesis channel pair in the previous frame (see the FMRQ Bit 9 in the status word output). Otherwise, setting this bit to 1 indicates that slots 6 and 7 contain valid right and left FM synthesis channel substitution data. When this bit is reset to 0, data in slots 6 and 7 is ignored.

REV. 0 -17-

IS1VI

**FMVI**

SS = Sound System Mode

SB = SoundBlaster Mode

**SSPVI**

SS/SB Playback Substitution Data Input Valid Flag. This bit is ignored if: (1) Intercept mode is not enabled for SS/SB playback or (2) The AD1821 did not request data for SS/SB playback in the previous frame (see the SSPRQ bit in the Status Word Output). Otherwise, setting this bit indicates that Slots 4 and 5 contain valid right and left SS/SB playback substitution data. If in "capture rate equal to playback rate" mode, setting this bit also indicates that valid capture substitution data is being sent to the AD1821. If not in modem mode, right and left channel capture substitution data is accepted in Slots 2 and 3 respectively. If in modem mode, only mono capture substitution data is accepted in slots 2 and 3. When this bit is cleared, data in all slots controlled by this bit, as defined above, is ignored.

SSCVI

SS/SB Capture Substitution Data Input Valid Flag. This bit is ignored if: (1) Intercept mode is not enabled for SS/SB capture or (2) The AD1821 did not request data for SS/SB capture in the previous frame (see the SSCRQ bit in the Status Word Output). Otherwise, setting this bit indicates that valid SS/SB capture substitution data is being sent to the AD1821. If not in modem mode, or DSP port or ISA bus based, right and left channel capture data is accepted in Slots 2 and 3 respectively. If in modem mode, only mono capture substitution data is accepted in Slot 3, because Slot 2, which is mapped to the right capture channel, is being used for modem. This mono data will, however, be sent to both left and right ISA SS/SB capture channels. When this bit is cleared, data in Slots 3 and 2 is ignored.

RES

Reserved: To ensure future compatibility write "0" to all reserved bits.

**FCLR**

MB0

MB1

IS1V1

DSP Port Clear Status Flag. When this bit is set, (write 1), the PNPR and PDN flag bits in the status word (Bits 15 and 14 of slots 0 SDO) are cleared. When this bit is cleared, (writing a 0), it has no effect on PNPR and PDN and preserves them in the previous states.

#### **Status Word Output (Slot 0 SDO)**

| 15  | 14   | 13  | 12    | 11    | 10   | 9     | 8     |

|-----|------|-----|-------|-------|------|-------|-------|

| PDN | PNPR | RES | SSCVO | SSPVO | FMVO | IS1VO | IS0VO |

| 7   | 6    | 5   | 4     | 3     | 2    | 1     | 0     |

| MB1 | MB0  | RES | SSCRQ | SSPRQ | FMRQ | IS1RQ | IS0RQ |

ISORQ I<sup>2</sup>S Port (0) Input Request Flag. This bit is set if intercept mode is enabled for I<sup>2</sup>S Port (0) and its four-word stereo input buffer is not full.

IS1RQ I<sup>2</sup>S Port (1) Input Request Flag. This bit is set if intercept mode is enabled for I<sup>2</sup>S Port (1) and its four-word stereo input buffer is not full.

FMRQ FM Synthesis Input Request Flag. This bit is set if intercept mode is enabled for FM synthesis and its four-word stereo input buffer is not full.

SSPRQ SS/SB Capture Input Request Flag. This bit is set if intercept mode is enabled for SS/SB playback and its fourword stereo input buffer is not full.

SSCRQ SS/SB Capture Input Request Flag. This bit is set if intercept mode is enabled for SS/SB capture and its four-word stereo input buffer is not full.

Mailbox 0 Status Flag. This bit is set if the most recent action to SS indirect register 42 (DSP port Mail Box 1) was a write, and is cleared if the most recent action was a read. The status of this bit is also reflected in SS indirect register 33. It may be used as a handshake bit to facilitate communication between a DSP on the DSP port and a host CPU on the ISA bus.

Mailbox 1 Status Flag. This bit is set if the most recent action to SS indirect register 43 (DSP port Mail Box 1) was a write and is cleared if the most recent action was a read. The status of this bit is also reflected in SS indirect register 33. It may be used as a handshake bit to facilitate communication between a DSP on the DSP port and a host CPU on the ISA bus.

ISOVO I<sup>2</sup>S Port 0 Valid Out. This bit is set if Slots 10 and 11 contain valid right and left I<sup>2</sup>S Port 0 data.

I<sup>2</sup>S Port 1 Valid Out. This bit is set if Slots 8 and 9 contain valid right and left I<sup>2</sup>S Port 1 data.

FMVO FM Synthesis Valid Out. This bit is set if Slots 6 and 7 contain valid left and right FM synthesis data.

SSPVO SS/SB Playback Valid Out. This bit is set if Slots 4 and 5 contain valid right and left SS/SB playback data.

SSCVO SS/SB Capture Valid Out. This bit is set if valid SS/SB capture data is being transmitted. If not in a modem mode, Slots 2 and 3 will contain valid right and left SS/SB capture data. If in modem mode, only Slot 3 will contain valid left SS/SB capture data as Slot 2 and the ADC right channel are used by the modem.

-18- REV. 0

**PNPR**

Plug and Play Reset flag. This bit is set by an AD1821 reset (RESETB pin asserted LOW) or by a Plug and Play reset command. This bit is cleared by the assertion of the FCLR bit in the control word. While this bit is set, all attempts to write an SS indirect register via the DSP port will be ignored and fail. This is to ensure that Plug and Play resets are immediately applied to the application running on the DSP, without requiring them to continuously poll the Plug and Play reset status bit. During the frame in which this bit is cleared (by asserting FCLR), an attempt to write an SS indirect register will succeed. If the FCLR bit is continuously asserted, writes to indirect registers via the DSP port will always be enabled. A Plug and Play reset command will set this PNPR bit HIGH during at least one frame.

**PDN**

Power-Down flag. This bit is set by an AD1821 reset (RESETB pin asserted LOW), or by an AD1821 power-down. Before an AD1821 power-down sequence shuts down the DSP port, at least one frame will be sent with this bit set. This bit can be cleared by the assertion of the FCLR (DSP port status clear) bit in the control word, providing the AD1821 is no longer in power-down.