### **General Description**

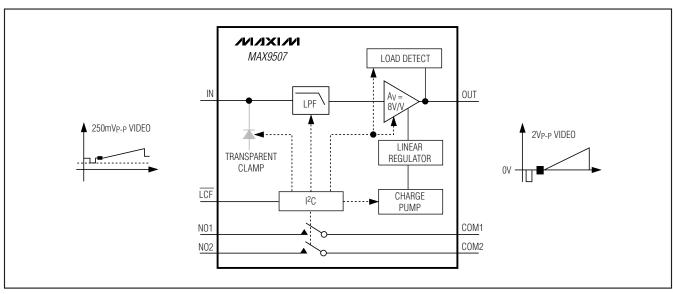

The MAX9507 amplifies and filters standard-definition video signals and only consumes 5.8mW guiescent power and 11.7mW average power. The MAX9507 leverages Maxim's DirectDrive™ technology to generate a clean, internal negative supply. Combining the internal negative power supply with the external positive 1.8V supply, the MAX9507 is able to drive a 2V<sub>P-P</sub> video signal into a  $150\Omega$  load.

The MAX9507 provides an I<sup>2</sup>C interface for easy configuration and access to the load status. The MAX9507 can detect, report, and act upon the change of a video load. This feature helps reduce overall power consumption by allowing the system to turn on the video encoder and driver only when a video load is connected to the MAX9507.

With a high power-supply rejection ratio (47dB at 100kHz), the MAX9507 can be powered directly from a 1.8V digital supply. The two integrated single-pole/single-throw (SPST) analog switches are ideal for routing audio, video, or digital signals.

The input of the MAX9507 can be directly connected to the output of a video DAC. The MAX9507 also features a transparent input sync-tip clamp, allowing AC-coupling of input signals with different DC biases.

The MAX9507 has an internal fixed gain of 8. The input full-scale video signal is nominally 0.25VP-P, and the output full-scale video signal is nominally 2VP-P.

**Features**

- ♦ 1.8V or 2.5V Single-Supply Operation

- ♦ Low Power Consumption (5.8mW Quiescent, 11.7mW Average)

- ♦ Video Load Detection

- ♦ DirectDrive Sets Video Output Black Level Near Ground

- ♦ Dual SPST Analog Switches

- ◆ Transparent Input Sync-Tip Clamp

- ♦ I<sup>2</sup>C Control

**Applications**

Mobile Phones

Portable Media Players (PMP)

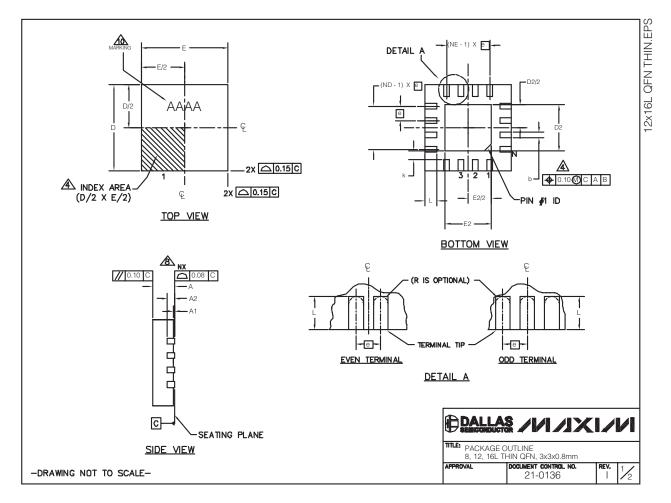

### **Ordering Information**

| PART        | PIN-PACKAGE | PKG CODE | TOP<br>MARK |

|-------------|-------------|----------|-------------|

| MAX9507ATE+ | 16 TQFN-EP* | T1633+4  | AFH         |

**Note:** This device is specified over the -40°C to +125°C operating temperature range.

- +Denotes lead-free package.

- \*EP = Exposed pad.

Pin Configuration appears at end of data sheet.

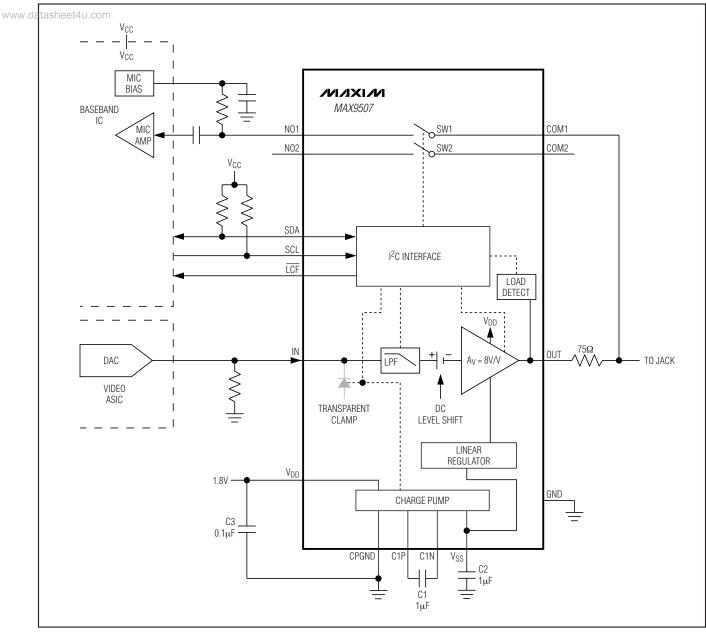

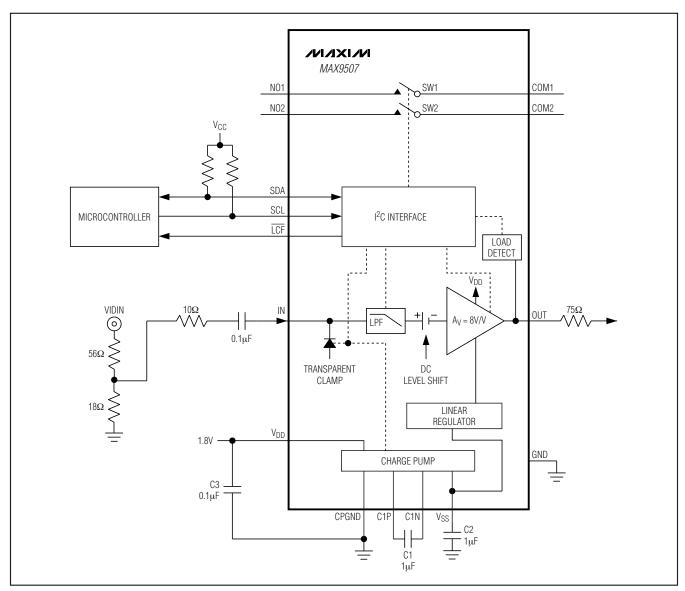

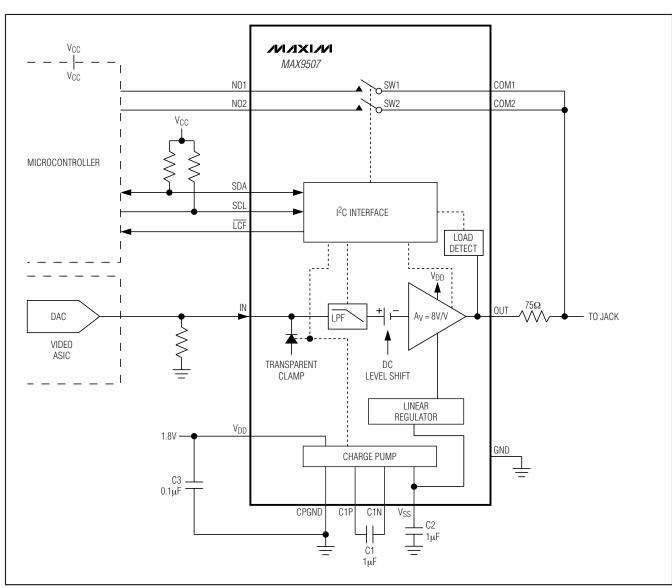

### Block Diagram

### **ABSOLUTE MAXIMUM RATINGS**

| (Voltages with respect to GND.)                                         |

|-------------------------------------------------------------------------|

| V <sub>DD</sub> 0.3V to +3V                                             |

| CPGND0.1V to +0.1V                                                      |

| IN0.3V to (V <sub>DD</sub> + 0.3V)                                      |

| OUT, NO_,                                                               |

| COM(The greater of V <sub>SS</sub> and -1V) to (V <sub>DD</sub> + 0.3V) |

| SDA, SCL, DEV_ADDR, LCF0.3V to +4V                                      |

| C1P0.3V to (V <sub>DD</sub> + 0.3V)                                     |

| C1N(V <sub>SS</sub> - 0.3V) to +0.3V                                    |

| V <sub>SS</sub> 3V to +0.3V                                             |

| Duration of OUT Short Circuit                            |

|----------------------------------------------------------|

| to V <sub>DD</sub> , GND, and V <sub>SS</sub> Continuous |

| Continuous Current                                       |

| IN, SDA, SCL, DEV_ADDR, LCF±20mA                         |

| NO_, COM±100mA                                           |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ )    |

| 16-Pin TQFN (derate 15.6mW/°C above +70°C)1250mW         |

| Operating Temperature Range40°C to +125°C                |

| Junction Temperature+150°C                               |

| Storage Temperature Range65°C to +150°C                  |

| Lead Temperature (soldering, 10s)+300°C                  |

|                                                          |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +1.8V, GND = 0V, OUT has R_L = 150\Omega$  connected to GND, transparent sync-tip clamp enabled,  $C_1 = C_2 = 1\mu F$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                          | SYMBOL           | CONDITIONS                                                                                    |                                                              | MIN   | TYP | MAX   | UNITS             |

|------------------------------------|------------------|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------|-------|-----|-------|-------------------|

| Supply Voltage Range               | $V_{DD}$         | Guaranteed by PSRR                                                                            |                                                              | 1.700 |     | 2.625 | V                 |

| Cumply Current                     | 1                | No load, full operation                                                                       | Filter enabled                                               |       | 3.1 | 5.4   | Λ                 |

| Supply Current                     | IDD              | mode                                                                                          | Filter disabled                                              |       | 2.9 | 5.1   | mA                |

| Sleep-Mode Supply Current          |                  | No load                                                                                       |                                                              |       | 3   |       | μΑ                |

| Shutdown Supply Current            | ISHDN            |                                                                                               |                                                              |       | 0.2 | 10    | μΑ                |

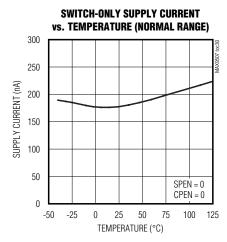

| Switch Only Supply Current         |                  | Shutdown mode                                                                                 |                                                              |       | 0.2 |       |                   |

| Switch-Only Supply Current         |                  | Charge-pump-only mod                                                                          | е                                                            |       | 520 |       | μΑ                |

| Output Load Detect Threshold       |                  | R <sub>L</sub> to GND, V <sub>SYNC-TIP</sub> <                                                | 13mV                                                         | 200   |     |       | Ω                 |

| DC-COUPLED INPUT                   |                  |                                                                                               |                                                              |       |     |       |                   |

|                                    |                  | Guaranteed by output-                                                                         | $1.7 \text{V} \leq \text{V}_{\text{DD}} \leq 2.625 \text{V}$ | 0     |     | 262.5 |                   |

| Input Voltage Range                |                  | voltage swing 2.375                                                                           | 2.375V ≤ V <sub>DD</sub> ≤ 2.625V                            | 0     |     | 325   | mV                |

| Input Current                      | ΙΒ               | IN = 130mV                                                                                    |                                                              |       | 2   | 3.2   | μΑ                |

| Input Resistance                   | R <sub>IN</sub>  | 10mV ≤ IN ≤ 250mV                                                                             |                                                              |       | 280 |       | kΩ                |

| Output Level                       |                  | IN = 80mV                                                                                     |                                                              | -75   | +5  | +75   | mV                |

| AC-COUPLED INPUT                   |                  |                                                                                               |                                                              |       |     |       |                   |

| Sync-Tip Clamp Level               | V <sub>CLP</sub> | $C_{IN} = 0.1 \mu F$                                                                          |                                                              | -8    | 0   | +11   | mV                |

|                                    |                  | Guaranteed by output-                                                                         | $1.7 \text{V} \le \text{V}_{\text{DD}} \le 2.625 \text{V}$   |       |     | 252.5 |                   |

| Input-Voltage Swing                |                  | voltage swing                                                                                 | 2.375V ≤ V <sub>DD</sub> ≤ 2.625V                            |       |     | 325   | mV <sub>P-P</sub> |

| Sync Crush                         |                  | Percentage reduction in sync pulse at output,<br>RSOURCE = $37.5\Omega$ , $C_{IN} = 0.1\mu F$ |                                                              |       | 1.6 |       | %                 |

| Input Clamping Current             |                  | IN = 130mV                                                                                    |                                                              |       | 2   | 3.2   | μΑ                |

| Line-Time Distortion               |                  | C <sub>IN</sub> = 0.1µF                                                                       |                                                              |       | 0.2 |       | %                 |

| Minimum Input Source<br>Resistance |                  |                                                                                               |                                                              |       | 25  |       | Ω                 |

| Output Level                       |                  | IN = 80mV                                                                                     |                                                              | -75   | +5  | +75   | mV                |

\_\_ /N/IXI/W

### www.deELECTRICAL CHARACTERISTICS (continued)

$(V_{DD} = +1.8V, GND = 0V, OUT has R_L = 150\Omega$  connected to GND, transparent sync-tip clamp enabled,  $C_1 = C_2 = 1\mu F$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                    | SYMBOL | CONDITIONS                                                                                      |                                                                        | MIN   | TYP  | MAX   | UNITS             |  |

|------------------------------|--------|-------------------------------------------------------------------------------------------------|------------------------------------------------------------------------|-------|------|-------|-------------------|--|

| DC CHARACTERISTICS           |        |                                                                                                 |                                                                        |       |      |       |                   |  |

| DC Voltage Gain              | Ay     | Guaranteed by output-voltage swing (Note 2)                                                     |                                                                        | 7.84  | 8    | 8.16  | V/V               |  |

|                              |        |                                                                                                 | 0V ≤ V <sub>IN</sub> ≤ 262.5mV,<br>DC-coupled input                    | 2.058 | 2.1  | 2.142 |                   |  |

| Output-Voltage Swing         |        | 1.7V ≤ V <sub>DD</sub> ≤ 2.625V                                                                 | 0V ≤ V <sub>IN</sub> ≤<br>252.5mV <sub>P-P</sub> ,<br>AC-coupled input | 1.979 | 2.02 | 2.061 | V <sub>P-</sub> P |  |

|                              |        | $2.375V \le V_{DD} \le 2.625V$                                                                  | 0V ≤ V <sub>IN</sub> ≤ 325mV                                           | 2.548 | 2.6  | 2.652 |                   |  |

| Power-Supply Rejection Ratio | PSRR   | 1.7V ≤ V <sub>DD</sub> ≤ 2.625V, m<br>load resistors                                            | neasured between 75Ω                                                   | 46    | 60   |       | dB                |  |

| Shutdown Input Resistance    |        | $0V \le IN \le V_{DD}$                                                                          |                                                                        |       | 2.8  |       | МΩ                |  |

| Output Resistance            | Rout   | OUT = 0V, -5mA ≤ I <sub>LOA</sub>                                                               | D ≤ +5mA                                                               |       | 0.1  |       | Ω                 |  |

| Shutdown Output Resistance   |        | $0V \le OUT \le V_{DD}$                                                                         |                                                                        |       | 32   |       | МΩ                |  |

| Shutdown OUT Leakage Current |        |                                                                                                 |                                                                        |       |      | 1     | μΑ                |  |

| Output Short-Circuit Current |        | Sourcing                                                                                        |                                                                        |       | 82   |       | m ^               |  |

| Output Short-Circuit Current |        | Sinking                                                                                         |                                                                        | 32    |      |       | mA                |  |

| AC CHARACTERISTICS (FILTER   | 3      |                                                                                                 |                                                                        |       |      |       |                   |  |

|                              |        |                                                                                                 | ±1dB passband                                                          |       | 7.5  |       | MHz               |  |

| Standard-Definition          |        | OUT = 2V <sub>P-P</sub> ,<br>reference frequency is                                             | f = 5.5MHz                                                             |       | 0    |       |                   |  |

| Reconstruction Filter        |        | 100kHz                                                                                          | f = 9.3MHz                                                             |       | -3   |       | dB                |  |

|                              |        |                                                                                                 | f = 27MHz                                                              |       | -49  |       |                   |  |

| Differential Cain            | DC     | f = 3.58MHz                                                                                     |                                                                        |       | 0.63 |       | 0/                |  |

| Differential Gain            | DG     | f = 4.43MHz                                                                                     |                                                                        |       | 0.93 |       | %                 |  |

| Differential Dhace           | DP     | f = 3.58MHz                                                                                     |                                                                        |       | 0.50 |       | Daguaga           |  |

| Differential Phase           | DP     | f = 4.43MHz                                                                                     |                                                                        |       | 0.63 |       | Degrees           |  |

| 2T Pulse-to-Bar K Rating     |        | 2T = 200ns, bar time is 2.5% and the ending 2. ignored                                          |                                                                        |       | 0.1  |       | K%                |  |

| 2T Pulse Response            |        | 2T = 200ns                                                                                      |                                                                        |       | 0.3  |       | K%                |  |

| 2T Bar Response              |        | 2T = 200ns, bar time is 18µs, the beginning 2.5% and the ending 2.5% of the bar time is ignored |                                                                        |       | 0.2  |       | K%                |  |

| Nonlinearity                 |        | 5-step staircase                                                                                |                                                                        |       | 0.1  |       | %                 |  |

| Group-Delay Distortion       |        | 100kHz ≤ f ≤ 5MHz, OUT = 2V <sub>P-P</sub>                                                      |                                                                        |       | 21   |       | ns                |  |

| Peak Signal to RMS Noise     |        | 100kHz ≤ f ≤ 5MHz                                                                               |                                                                        |       | 65   |       | dB                |  |

| Power-Supply Rejection Ratio | PSRR   | f = 100kHz, 100mV <sub>P-P</sub>                                                                |                                                                        |       | 47   |       | dB                |  |

| Output Impedance             |        |                                                                                                 |                                                                        | 7.5   |      | Ω     |                   |  |

| Shutdown OUT-to-IN Isolation |        | f < 5.5MHz                                                                                      |                                                                        |       | 102  |       | dB                |  |

| Shutdown IN-to-OUT Isolation |        | f < 5.5MHz                                                                                      |                                                                        |       | 98   |       | dB                |  |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD}=+1.8V, GND=0V, OUT has R_L=150\Omega$  connected to GND, transparent sync-tip clamp enabled,  $C_1=C_2=1\mu F, T_A=T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A=+25^{\circ}C$ .) (Note 1)

| PARAMETER                                  | SYMBOL                 | С                                                                                                                             | ONDITIONS                                                                                                                 | MIN  | TYP     | MAX  | UNITS   |

|--------------------------------------------|------------------------|-------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|------|---------|------|---------|

| AC CHARACTERISTICS (FILTE                  | R                      |                                                                                                                               |                                                                                                                           |      |         |      |         |

| Small-Signal -3dB Bandwidth                |                        | OUT = 100mV <sub>P-P</sub>                                                                                                    |                                                                                                                           |      | 40.7    |      | MHz     |

| Large-Signal -3dB Bandwidth                |                        | OUT = 2V <sub>P-P</sub>                                                                                                       |                                                                                                                           |      | 9.8     |      | MHz     |

| Small-Signal 1dB Flatness                  |                        | OUT = 100mV <sub>P-P</sub>                                                                                                    |                                                                                                                           |      | 32.8    |      | MHz     |

| Large-Signal 1dB Flatness                  |                        | OUT = 2V <sub>P-P</sub>                                                                                                       |                                                                                                                           |      | 7.2     |      | MHz     |

| Slew Rate                                  |                        | OUT = 2V step                                                                                                                 |                                                                                                                           |      | 35      |      | V/µs    |

| Settling Time to 0.1%                      |                        | OUT = 2V step                                                                                                                 |                                                                                                                           |      | 230     |      | ns      |

| Differential Onio                          | DO                     | f = 3.58MHz                                                                                                                   |                                                                                                                           |      | 0.63    |      | 0/      |

| Differential Gain                          | DG                     | f = 4.43MHz                                                                                                                   |                                                                                                                           |      | 0.94    |      | %       |

| Differential Disco-                        | DD                     | f = 3.58MHz                                                                                                                   |                                                                                                                           |      | 0.50    |      | D       |

| Differential Phase                         | DP                     | f = 4.43MHz                                                                                                                   |                                                                                                                           |      | 0.64    |      | Degrees |

| 2T Pulse-to-Bar K Rating                   |                        |                                                                                                                               | ime is 18µs, the beginning<br>ling 2.5% of the bar time is                                                                |      | 0.1     |      | К%      |

| 2T Pulse Response                          |                        | 2T = 200ns                                                                                                                    |                                                                                                                           |      | 0.2     |      | Κ%      |

| 2T Bar Response                            |                        |                                                                                                                               | 2T = 200ns, bar time is 18µs, the beginning 2.5% and the ending 2.5% of the bar time is ignored                           |      |         |      | K%      |

| Nonlinearity                               |                        | 5-step staircase                                                                                                              |                                                                                                                           |      | 0.1     |      | %       |

| Group-Delay Distortion                     |                        | 100kHz ≤ f ≤ 5MH                                                                                                              | $dz$ , OUT = $2V_{P-P}$                                                                                                   |      | 15      |      | ns      |

| Peak Signal to RMS Noise                   |                        | 100kHz ≤ f ≤ 5MH                                                                                                              | łz                                                                                                                        |      | 69      |      | dB      |

| Power-Supply Rejection Ratio               | PSRR                   | f = 100kHz, 100m                                                                                                              | NP-P                                                                                                                      |      | 42      |      | dB      |

| Output Impedance                           |                        | f = 5MHz, IN = 80mV 7.5                                                                                                       |                                                                                                                           |      |         | Ω    |         |

| Shutdown OUT-to-IN Isolation               |                        | f < 5.5MHz 102                                                                                                                |                                                                                                                           |      | dB      |      |         |

| Shutdown IN-to-OUT Isolation               |                        | f < 5.5MHz                                                                                                                    |                                                                                                                           |      | 98      |      | dB      |

| CHARGE PUMP                                |                        |                                                                                                                               |                                                                                                                           |      |         |      |         |

| Switching Frequency                        |                        |                                                                                                                               |                                                                                                                           | 325  | 625     | 1150 | kHz     |

| ANALOG SWITCHES                            |                        |                                                                                                                               |                                                                                                                           |      |         |      |         |

| On-Resistance (Note 3)                     | Ron                    | ICOM_ = 10mA,                                                                                                                 | Normal range                                                                                                              |      | 1.2 2.2 |      | Ω       |

| On-Hesistance (Note 3)                     | HON                    | V <sub>NO</sub> _ = 0V                                                                                                        | Extended range                                                                                                            |      | 1.2     | 2.2  | 52      |

| On-Resistance Flatness                     |                        |                                                                                                                               | Normal range,<br>V <sub>NO</sub> _ = 0V, 1V, V <sub>DD</sub>                                                              |      | 2.3     |      |         |

| (Notes 3, 4)                               | RFLAT(ON)              | ICOM_ = 10mA                                                                                                                  | Extended range, V <sub>NO</sub> = -0.9V, 0V, +1.2V, V <sub>DD</sub>                                                       |      | 0.3     | 1.1  | Ω       |

| NO_ Off-Leakage Current<br>Normal Range    | INO_(OFF)N             | V <sub>DD</sub> = 2.625V, V <sub>COM</sub> = 0.3V, 2.3V;<br>V <sub>NO</sub> = 2.3V, 0.3V; T <sub>A</sub> = +25°C (Notes 3, 5) |                                                                                                                           | -100 |         | +100 | nA      |

| COM_ On-Leakage Current<br>Normal Range    | ICOM_(ON)N             |                                                                                                                               | V <sub>DD</sub> = 2.625V, V <sub>NO</sub> = high-Z,<br>V <sub>COM</sub> = 0.3V, 2.3V; T <sub>A</sub> = +25°C (Notes 3, 5) |      |         | +100 | nA      |

| NO_ Off-Leakage Current,<br>Extended Range | I <sub>NO_(OFF)E</sub> |                                                                                                                               | OM_ = -0.6V, +2.3V;<br>6V; T <sub>A</sub> = +25°C (Notes 3, 5)                                                            | -100 |         | +100 | nA      |

4 \_\_\_\_\_\_*MIXIM*

### www.da**ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +1.8V, GND = 0V, OUT has R_L = 150\Omega$  connected to GND, transparent sync-tip clamp enabled,  $C_1 = C_2 = 1\mu F$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                  | SYMBOL                            | CONDITION                                                                                                    | MIN                                                                                              | TYP                      | MAX      | UNITS                    |                   |

|--------------------------------------------|-----------------------------------|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--------------------------|----------|--------------------------|-------------------|

| COM_ On-Leakage Current,<br>Extended Range | ICOM_(ON)E                        | $V_{DD} = 2.625V$ , $V_{NO} = high-Z$ , $V_{COM} = -0.6V$ , $+2.3V$ ; $T_A = +25^{\circ}C$ (Notes 3, 5)      |                                                                                                  | -100                     |          | +100                     | nA                |

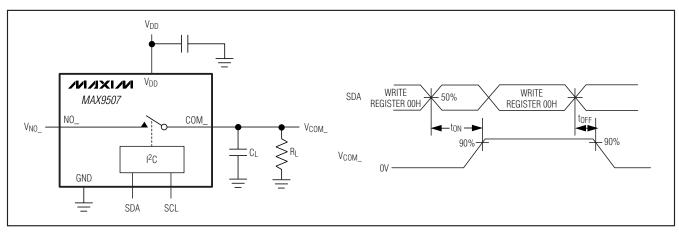

| Turn-On Time                               | toN                               | $V_{NO}$ = 0.9V, $R_L$ = 300 $\Omega$ , $C_l$ Figure 1 (Note 6)                                              | _ = 35pF,                                                                                        |                          | 310      |                          | ns                |

| Turn-Off Time                              | toff                              | $V_{NO}$ = 0.9V, $R_L$ = 300 $\Omega$ , $C_I$ Figure 1 (Note 6)                                              | _ = 35pF,                                                                                        |                          | 372      |                          | ns                |

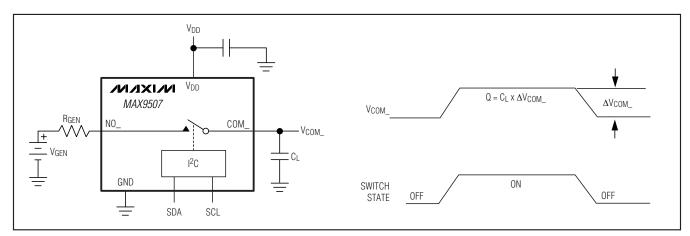

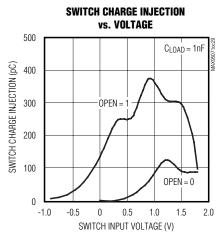

| Charge Injection                           | Q                                 | $V_{GEN} = 0.9V, R_{GEN} = 0\Omega, C$<br>Figure 2                                                           | L = 1nF,                                                                                         |                          | 60       |                          | рС                |

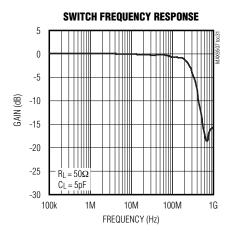

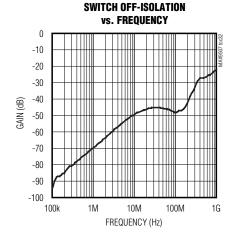

| Off-Isolation                              | VISO                              | $V_{NO}$ = 1 $V_{P-P}$ , $R_L$ = 50 $\Omega$ , $C_L$ = 5pF, Figure 1                                         | f = 10MHz<br>f = 1MHz                                                                            |                          | 49<br>69 |                          | dB                |

| On-Channel -3dB Bandwidth                  | BW                                | V <sub>NO</sub> _ = 0dBm, R <sub>SOURCE</sub> = 5<br>C <sub>L</sub> = 5pF, Figure 1                          | $50\Omega$ , $R_L = 50\Omega$ ,                                                                  |                          | 280      |                          | MHz               |

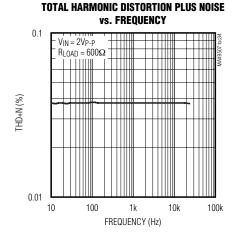

| Total Harmonic Distortion                  | THD                               | $V_{COM} = 1V_{P-P}, R_L = 600\Omega$                                                                        |                                                                                                  |                          | 0.037    |                          | %                 |

| Charge-Pump Noise                          |                                   | Extended range, $R_L = 50\Omega$                                                                             |                                                                                                  |                          | 1.2      |                          | mV <sub>P-P</sub> |

| NO_ Off-Capacitance                        | Coff                              | f = 1MHz                                                                                                     |                                                                                                  |                          | 21       |                          | рF                |

| Switch On-Capacitance                      | Con                               | f = 1MHz                                                                                                     |                                                                                                  |                          | 53       |                          | рF                |

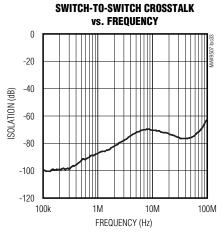

| CROSSTALK                                  |                                   |                                                                                                              |                                                                                                  |                          |          |                          |                   |

| Switch to Switch                           |                                   | Switch 1, 2 closed;<br>V <sub>NO</sub> = 1V <sub>P-P</sub> , R <sub>L</sub> = 50Ω,                           | f = 10MHz                                                                                        |                          | -71      |                          | dB                |

|                                            |                                   | $C_L = 5pF$ , Figure 1                                                                                       | f = 1MHz                                                                                         |                          | -88      |                          |                   |

| NO_ to OUT                                 |                                   | Switch 1, 2 open; video circuitry enabled,                                                                   | f = 10MHz                                                                                        |                          | -44      |                          | dB                |

|                                            |                                   | V <sub>NO</sub> _ = 1V <sub>P-P</sub>                                                                        | f = 1MHz                                                                                         |                          | -78      |                          |                   |

| OUT to NO_                                 |                                   | Switch 1, 2 closed; video cir<br>f = 20kHz, OUT = 2V <sub>P-P</sub> , R <sub>L</sub><br>C <sub>L</sub> = 5pF | •                                                                                                |                          | -94      |                          | dB                |

| IN to COM_                                 |                                   | Switch 1, 2 closed; video cirr<br>f = 20kHz, IN = 0.25V <sub>P-P</sub> , R <sub>I</sub>                      | •                                                                                                |                          | -89      |                          | dB                |

| OUT to COM_                                |                                   |                                                                                                              | Switch 1, 2 closed; video circuitry enabled, $f = 20kHz$ , $OUT = 2V_{P-P}$ , $R_L = 50\Omega$ , |                          | -94      |                          | dB                |

| CMOS DIGITAL INPUTS (SDA,                  | SCL, DEV_ADI                      | DR)                                                                                                          |                                                                                                  |                          |          |                          |                   |

| Input Low Voltage                          | VIL                               |                                                                                                              |                                                                                                  |                          |          | 0.3 x<br>V <sub>DD</sub> | V                 |

| Input High Voltage                         | VIH                               |                                                                                                              |                                                                                                  | 0.7 x<br>V <sub>DD</sub> |          |                          | ٧                 |

| Input Hysteresis                           |                                   |                                                                                                              |                                                                                                  |                          | 275      |                          | mV                |

| Input Leakage Current                      | I <sub>IL</sub> , I <sub>IH</sub> |                                                                                                              |                                                                                                  | -10                      |          | +10                      | μΑ                |

| Input Capacitance                          | CIN                               |                                                                                                              |                                                                                                  |                          | 15       |                          | рF                |

### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +1.8V, GND = 0V, OUT has R_L = 150\Omega$  connected to GND, transparent sync-tip clamp enabled,  $C_1 = C_2 = 1\mu F$ ,  $T_A = T_{MIN}$  to  $T_{MAX}$ , unless otherwise noted. Typical values are at  $T_A = +25^{\circ}C$ .) (Note 1)

| PARAMETER                                       | SYMBOL          | CONDITIONS         |                        | MIN                       | TYP | MAX      | UNITS |

|-------------------------------------------------|-----------------|--------------------|------------------------|---------------------------|-----|----------|-------|

| DIGITAL OUTPUTS (SDA, LCF)                      |                 |                    |                        | ·                         |     |          |       |

|                                                 |                 |                    | V <sub>DD</sub> > 2V   |                           |     | 0.4      |       |

| Output Low Voltage                              | V <sub>OL</sub> | $I_{OL} = 3mA$     | \/== + 0\/             |                           |     | 0.2 x    | V     |

|                                                 |                 |                    | V <sub>DD</sub> < 2V   |                           |     | $V_{DD}$ |       |

| Output High Leakage Current                     | loh             | $V_{OUT} = V_{DD}$ |                        |                           |     | 1        | μΑ    |

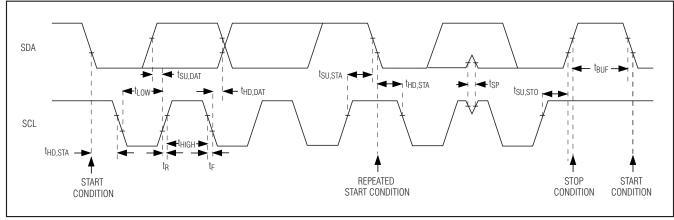

| SERIAL INTERFACE TIMING (Fig                    | ure 3)          |                    |                        |                           |     |          |       |

| Serial Clock Frequency                          | fscl            |                    |                        | 0                         |     | 400      | kHz   |

| Bus Free Time Between STOP and START Conditions | tBUF            |                    |                        | 1.3                       |     |          | μs    |

| Hold Time (Repeated) START Condition            | thd,sta         |                    |                        | 0.6                       |     |          | μs    |

| SCL Pulse-Width Low                             | tLOW            |                    |                        | 1.3                       |     |          | μs    |

| SCL Pulse-Width High                            | thigh           |                    |                        | 0.6                       |     |          | μs    |

| Setup Time for a Repeated START Condition       | tsu,sta         |                    |                        | 0.6                       |     |          | μs    |

| Data Hold Time                                  | thd,dat         |                    |                        | 0                         |     | 900      | ns    |

| Data Setup Time                                 | tsu,dat         |                    |                        | 100                       |     |          | ns    |

| Bus Capacitance                                 | CB              |                    |                        |                           |     | 400      | рF    |

| SDA and SCL Receiving Rise<br>Time              | tR              | (Note 7)           |                        | 20 +<br>0.1C <sub>B</sub> |     | 300      | ns    |

| SDA and SCL Receiving Fall Time                 | tF              | (Note 7)           |                        | 20 +<br>0.1C <sub>B</sub> |     | 300      | ns    |

| SDA Transmitting Fall Time                      | tϝ              | (Note 7)           | V <sub>DD</sub> = 1.7V | 20 +<br>0.1C <sub>B</sub> |     | 250      | ns    |

|                                                 |                 |                    | $V_{DD} = 2.625V$      | 0                         |     | 250      |       |

| Setup Time for STOP Condition                   | tsu,sto         |                    |                        | 0.6                       |     |          | μs    |

| Pulse Width of Suppressed Spike                 | tsp             |                    |                        | 0                         |     | 50       | ns    |

- Note 1: All devices are 100% production tested at  $T_A = +25$ °C. Specifications over temperature are guaranteed by design.

- Note 2: Voltage gain (Ay) is a two-point measurement in which the output-voltage swing is divided by the input-voltage swing.

- **Note 3:** Normal range: charge pump disabled. Extended range: charge pump enabled. In extended range mode, the switch input can swing from -0.9V to Vpp.

- **Note 4:** Flatness is defined as the difference between the maximum and minimum values of on-resistance as measured at the specified voltages.

- Note 5: Not production tested, guaranteed by design.

- Note 6: toN and toFF are measured from the end of the writing of register 0x00 until COM reaches 90% of the output voltage. See Figure 1.

- Note 7: CB is in picofarads.

**Test Circuits/Timing Diagrams**

Figure 1. Analog Switch Test Circuit

Figure 2. Analog Switch Charge Injection

Figure 3. I<sup>2</sup>C Serial-Interface Timing Diagram

www.datasheet4u.com

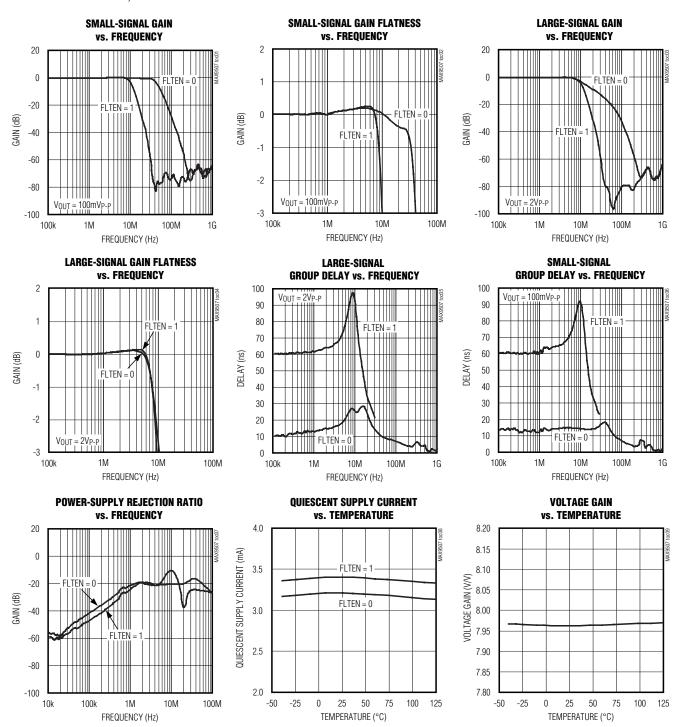

### Typical Operating Characteristics

$(V_{DD} = +1.8V, GND = 0V, mode 2 (Table 6), video output has R_L = 150\Omega$  connected to GND, video filter enabled,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

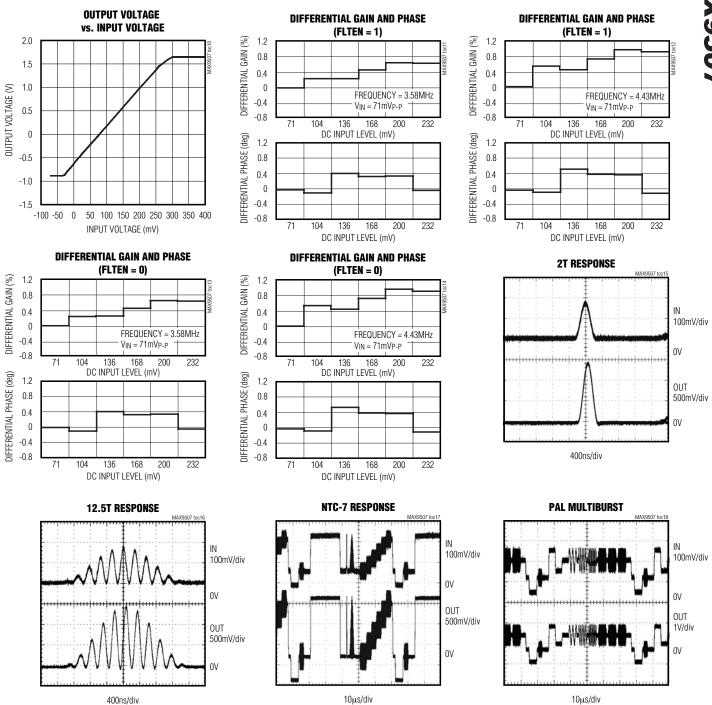

### Typical Operating Characteristics (continued)

$(V_{DD} = +1.8V, GND = 0V, mode 2 (Table 6), video output has R<sub>I</sub> = 150<math>\Omega$  connected to GND, video filter enabled,  $T_A = +25^{\circ}C$ , unless otherwise noted.)

400ns/div

10μs/div

www.datasheet4u.com

10

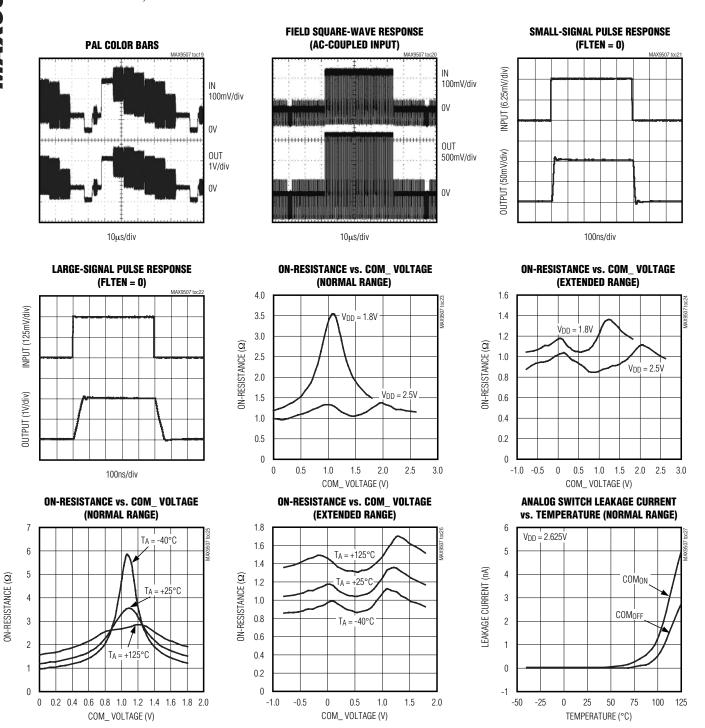

### \_Typical Operating Characteristics (continued)

$(V_{DD} = +1.8V, GND = 0V, mode 2 (Table 6), video output has R_L = 150\Omega connected to GND, video filter enabled, T_A = +25°C, unless otherwise noted.)$

www.datasheet4u.com

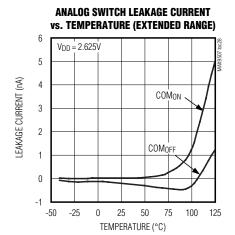

### Typical Operating Characteristics (continued)

$(V_{DD} = +1.8V, GND = 0V, mode 2 (Table 6), video output has R_L = 150\Omega connected to GND, video filter enabled, T_A = +25°C, unless otherwise noted.)$

#### w datasheet/u com

### **Pin Description**

| PIN | NAME            | FUNCTION                                                                                                    |

|-----|-----------------|-------------------------------------------------------------------------------------------------------------|

| 1   | IN              | Video Input                                                                                                 |

| 2   | SDA             | I <sup>2</sup> C-Compatible Serial-Data Input/Output                                                        |

| 3   | SCL             | I <sup>2</sup> C-Compatible Serial-Clock Input                                                              |

| 4   | DEV_ADDR        | I <sup>2</sup> C Device Address Input. Connect DEV_ADDR to GND, V <sub>DD</sub> , SCL, or SDA. See Table 4. |

| 5   | V <sub>DD</sub> | Positive Power Supply. Bypass with a 0.1µF capacitor to GND.                                                |

| 6   | C1P             | Charge-Pump Flying Capacitor Positive Terminal. Connect a 1µF capacitor from C1P to C1N.                    |

| 7   | CPGND           | Charge-Pump Ground                                                                                          |

| 8   | C1N             | Charge-Pump Flying Capacitor Negative Terminal. Connect a 1µF capacitor from C1P to C1N.                    |

| 9   | V <sub>SS</sub> | Charge-Pump Negative Power Supply. Bypass with a 1µF capacitor to GND.                                      |

| 10  | OUT             | Video Output                                                                                                |

| 11  | GND             | Ground                                                                                                      |

| 12  | <u>LCF</u>      | Load Change Flag. Open-drain, active-low signal indicates when a video load change occurs.                  |

| 13  | NO1             | Normally Open Terminal 1                                                                                    |

| 14  | COM1            | Common Terminal 1                                                                                           |

| 15  | COM2            | Common Terminal 2                                                                                           |

| 16  | NO2             | Normally Open Terminal 2                                                                                    |

| _   | EP              | Exposed Pad. EP is internally connected to GND. Connect EP to GND.                                          |

### **Detailed Description**

The MAX9507 represents Maxim's second-generation of DirectDrive video amplifiers that meet the requirements of current and future portable equipment:

- 1.8V Operation: Eliminate the need for 3.3V supply in favor of lower supply voltages.

- Lower Power Consumption: The MAX9507 reduces average power consumption by up to 75% compared to the 3.3V first generation (MAX9503/ MAX9505).

- Internal Fixed Gain of 8: As the supply voltages drop for system chips on deep submicron processes, the video DAC can no longer create a 1V<sub>P-P</sub> signal at its output, and the gain of 2 found in the previous generation of video filter amplifiers is not enough.

- Load Reporting: The MAX9507 senses the presence of a video load. For portable devices, a video load is not connected most of the time, and turning off the video encoder saves power. Another benefit of load reporting is a simpler user interface, eliminating the need to browse through menus to activate the video output. Instead, the equipment will automatically enable this feature.

Dual SPST Analog Switches: The two analog switches are ideal for routing additional audio, video, or digital signals.

DirectDrive technology is necessary for a voltage-mode amplifier to output a 2VP-P video signal from a 1.8V supply. The integrated inverting charge pump creates a negative supply that increases the output range and gives the video amplifier enough headroom to drive a 2VP-P video signal into a  $150\Omega$  load.

#### **DirectDrive**

#### Background

Integrated video filter amplifier circuits operate from a single supply. The positive power supply usually creates video output signals that are level-shifted above ground to keep the signal within the linear range of the output amplifier. For applications where the positive DC level is not acceptable, a series capacitor can be inserted in the output connection in an attempt to eliminate the positive DC level shift. The series capacitor cannot truly level shift a video signal because the average level of the video varies with picture content. The series capacitor biases the video output signal around ground, but the actual level of the video signal can vary significantly depending upon the RC time constant and the picture content.

The series capacitor creates a highpass filter. Since the lowest frequency in video is the frame rate, which can be between 24Hz and 30Hz, the pole of the highpass filter should ideally be an order of magnitude lower in frequency than the frame rate. Therefore, the series capacitor must be very large, typically from 220µF to 3000µF. For space-constrained equipment, the series capacitor is unacceptable. Changing from a single series capacitor to a SAG network that requires two smaller capacitors can only reduce space and cost slightly.

The series capacitor in the usual output connection also prevents damage to the output amplifier if the connector is shorted to a supply or to ground. While the output connection of the MAX9507 does not have a series capacitor, the MAX9507 will not be damaged if the connector is shorted to a supply or to ground (see the *Short-Circuit Protection* section).

### Video Amplifier

If the full-scale video signal from a video DAC is 250mV, the black level of the video signal created by the video DAC is around 75mV. The MAX9507 shifts the black level to near ground at the output so that the active video is above ground and the sync is below ground. The amplifier needs a negative supply for its output stage to remain in its linear region when driving sync below ground.

The MAX9507 has an integrated charge pump and linear regulator to create a low-noise negative supply from the positive supply voltage. The charge pump inverts the positive supply to create a raw negative voltage that is then fed into the linear regulator filtering out the charge-pump noise.

#### Comparison Between DirectDrive Output and AC-Coupled Output

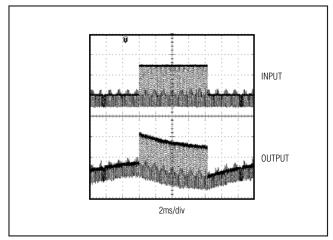

The actual level of the video signal varies less with a DirectDrive output than an AC-coupled output. The average video signal level can change greatly depending upon the picture content. With an AC-coupled output, the average level will change according to the time constant formed by the series capacitor and series resistance (usually 150 $\Omega$ ). For example, Figure 4 shows an AC-coupled video signal alternating between a completely black screen and a completely white screen. Notice the excursion of the video signal as the screen changes.

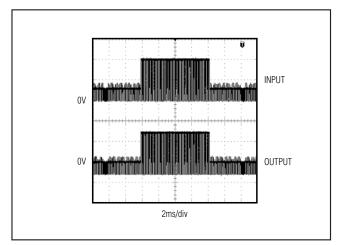

With the DirectDrive amplifier, the black level is held at ground. The video signal is constrained between -0.3V to +0.7V. Figure 5 shows the video signal from a DirectDrive amplifier with the same input signal as the AC-coupled system.

Figure 4. AC-Coupled Output

Figure 5. DirectDrive Output

#### **Video Reconstruction Filter**

The MAX9507 includes an internal five-pole, Butterworth lowpass filter to condition the video signal. The reconstruction filter smoothes the steps and reduces the spikes created whenever the DAC output changes value. In the frequency domain, the steps and spikes cause images of the video signal to appear at multiples of the sampling clock frequency. The reconstruction filter typically has ±1dB passband flatness of 7.3MHz and 48dB attenuation at 27MHz.

#### Transparent Sync-Tip Clamp

The MAX9507 contains an integrated, transparent sync-tip clamp. When using a DC-coupled input, the sync-tip clamp does not affect the input signal, as long as it remains above ground. When using an AC-coupled input, the sync-tip clamp automatically clamps the input signal to ground, preventing it from going lower. A small current of 2µA pulls down on the input to prevent an AC-coupled signal from drifting outside the input range of the device.

Using an AC-coupled input results in some additional variation of the black level at the output. Applying a voltage above ground to the input pin of the device always produces the same output voltage, regardless of whether the input is DC- or AC-coupled. However, since the sync-tip clamp level (VCLP) can vary over a small range, the video black level at the output of the device when using an AC-coupled input can vary by an additional amount equal to the V<sub>CLP</sub> multiplied by the DC voltage gain (Ay).

### **Dual SPST Analog Switches**

The MAX9507 has dual SPST analog switches for routing additional audio, video, digital, and other signals. The switches are selected through the I<sup>2</sup>C interface. SW1EN (register 0x00, bit B6) and SW2EN (register 0x00, bit B7) control the analog switches. See the 12C Registers and Bit Descriptions section. The dual analog switches operate in either normal or extended range. In normal range, the part is in shutdown and the analog switches can handle signals between GND and VDD. In extended range, the charge pump and linear regulator are on and the analog switches can handle signals between -0.9V and Vnn.

#### **Short-Circuit Protection**

The MAX9507 typical operating circuit includes a  $75\Omega$ back-termination resistor that limits short-circuit current if an external short is applied to the video output. The MAX9507 also features internal output short-circuit protection to prevent device damage in prototyping and applications where the amplifier output can be directly shorted.

### **Powering On/Off the MAX9507**

The MAX9507 powers on in a low-power shutdown mode with the analog switches open and the video signal path, charge pump, and load detection circuitry disabled. It is good practice to configure the operating mode of the signal path before enabling it. This may include selecting the sync-tip clamp and video filter. Setting CPEN = 1 (register 0x00, bit B0) enables the charge pump. The charge pump must be fully operational before the signal path will be functional. Setting SPEN = 1 (register 0x00, bit B1) enables the signal path. Both SPEN and CPEN may be set at the same time and internal control circuitry will monitor the charge pump and enable the signal path at the appropriate time.

The analog switches can be turned on or off at any time, regardless of the state of the charge pump or signal path. However, the signal range is limited from GND to V<sub>DD</sub> when the charge pump is disabled.

The MAX9507 can be placed in a low-power shutdown mode by setting SPEN = 0 and CPEN = 0.

#### **Video Load Detection Circuitry**

The MAX9507 contains video load detection circuitry at the video output, enabling efficient power consumption based on the actual presence of a video load. Setting the automatic signal path enable bit, ASPEN = 1 (register 0x01, bit B1) or the automatic charge-pump enable bit, ACPEN = 1 (register 0x01, bit B0) enables the load detection feature. The LOAD bit (register 0x01, bit B7) indicates the load status.

To enable complete, automatic control of the part, set ASPEN = ACPEN = 1 and SPEN = CPEN = 0. In this state, when an output load is connected to the amplifier, the signal path and charge pump fully turn on and stay on until the output load is disconnected. If an output load is not connected to the amplifier, then the signal path and charge pump remain in a low-power sleep mode while continuing to check if a load is connected. Setting SPEN = 1 or CPEN = 1 overrides the corresponding ASPEN or ACPEN bits, enabling the block regardless of the detected video load status.

The LOAD bit indicates the latest video load status. All changes to the video load status are debounced typically 128ms to eliminate false load-detect events.

Setting the load change flag enable bit, LCFEN = 1 (register 0x01, bit B3), and enabling the load detection feature (ASPEN = 1 or ACPEN = 1) enables the open-drain LCF output. LCF asserts low whenever the LOAD bit changes state. It remains low until the LOAD bit (register 0x01) is read. LCF can be used as an interrupt to notify the system that the load status has changed.

MIXIM

#### Sleep Mode

www.datasheet4u.com If a video load is not connected to the amplifier, the MAX9507 remains in a low-power sleep mode. The load-sense circuitry checks for a load eight times per second by connecting an internal  $7.5k\Omega$  pullup resistor to the output for 1ms. If the output is pulled up, no load is present. If the output stays low, a load is connected, and the automatic control circuitry enables the appropriate blocks. When the amplifier is on, it continually checks if the load has been disconnected by detecting if the amplifier is sinking current during a horizontal line time. Therefore, a black-burst signal (or input signal < 13mV) is required to maintain the detected load status. If the load is disconnected, the device returns to the low-power sleep mode.

### **Common Modes of Operation**

| NO. | MODE                                                                                                                                               | ASPEN | ACPEN | SPEN | CPEN |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------------|-------|-------|------|------|

| 1   | Shutdown mode. Switches in normal range. Load-detect function disabled.                                                                            | 0     | 0     | 0    | 0    |

| 2   | Full operation mode. Video, charge pump, and regulator on. Switches in extended range.                                                             | Х     | Х     | 1    | 1    |

| 3   | Charge-pump-only mode. Charge pump and regulator on, video off. Switches in extended range.                                                        | Х     | Х     | 0    | 1    |

| 4   | Sleep mode. Video, charge pump, and regulator automatic. Switches in extended range only when the charge pump is on. Load-detect function enabled. | 1     | 1     | 0    | 0    |

| 5   | Charge pump and regulator on, video automatic. Switches in extended range. Load-detect function enabled.                                           | 1     | 0     | 0    | 1    |

X = Don't care.

### I<sup>2</sup>C Registers and Bit Descriptions

#### **Table 1. Register Map**

| REGISTER<br>ADDRESS | REGISTER             | В7    | В6    | В5 | B4   | В3    | B2 | B1    | В0    | POWER-ON<br>RESET<br>STATE |

|---------------------|----------------------|-------|-------|----|------|-------|----|-------|-------|----------------------------|

| 0x00                | Configuration        | SW2EN | SW1EN | 0  | STEN | FLTEN | 0  | SPEN  | CPEN  | 0x00                       |

| 0x01                | Video Load<br>Detect | LOAD  | 0     | 0  | 0    | LCFEN | 0  | ASPEN | ACPEN | 0x00                       |

### da Table 2 Configuration Register (0x00)

| BIT | NAME  | FUNCTION                                                                                                                                           |

|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| В7  | SW2EN | 1 = Analog switch 2 closed.<br>0 = Analog switch 2 open.                                                                                           |

| В6  | SW1EN | 1 = Analog switch 1 closed.<br>0 = Analog switch 1 open.                                                                                           |

| B4  | STEN  | 1 = Transparent sync-tip clamp enabled, the input can be DC- or AC-coupled. 0 = Transparent sync-tip clamp disabled, the input must be DC-coupled. |

| В3  | FLTEN | 1 = Video filter enabled.<br>0 = Video filter disabled (bypassed).                                                                                 |

| B1  | SPEN  | 1 = Signal path enabled* (SPEN overrides the ASPEN setting).<br>0 = Signal path disabled.                                                          |

| В0  | CPEN  | 1 = Charge pump enabled (CPEN overrides the ACPEN setting). 0 = Charge pump disabled.                                                              |

<sup>\*</sup>Internal control circuitry prevents the signal path from turning on until the charge pump has been enabled and has settled.

### Table 3. Video Load-Detect Register (0x01)

| BIT | NAME  | FUNCTION                                                                                                         |

|-----|-------|------------------------------------------------------------------------------------------------------------------|

| B7  | LOAD* | 1 = Load detected.<br>0 = No load detected.                                                                      |

| В3  | LCFEN | 1 = Changes to the video load will trigger LCF to pull low. 0 = Changes to the video load are not reported.      |

| B1  | ASPEN | 1 = Enable automatic control of the video signal path**. 0 = Disable automatic control of the video signal path. |

| В0  | ACPEN | 1 = Enable automatic control of the charge pump***. 0 = Disable automatic control of the charge pump.            |

<sup>\*</sup>Read-only bit indicating the load status when the video load-detect circuitry is enabled (ASPEN = 1 or ACPEN = 1). When LCFEN = 1, reading this bit will clear the  $\overline{LCF}$  flag.

#### I<sup>2</sup>C Serial Interface

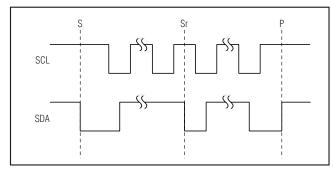

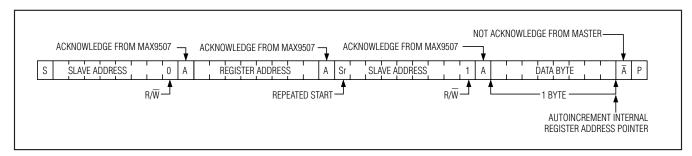

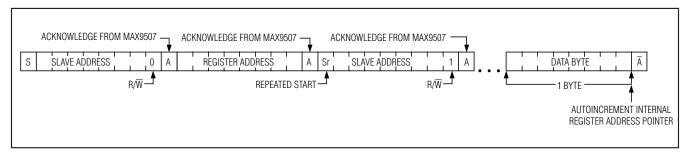

The MAX9507 features an I<sup>2</sup>C/SMBus<sup>TM</sup>-compatible, 2-wire serial interface consisting of a serial-data line (SDA) and a serial-clock line (SCL). SDA and SCL facilitate communication between the MAX9507 and the master at clock rates up to 400kHz. Figure 3 shows the 2-wire interface timing diagram. The master generates SCL and initiates data transfer on the bus. A master device writes data to the MAX9507 by transmitting a START (S) condition, the proper slave address with the R/W bit set to 0, followed by the register address and then the data word. Each transmit sequence is framed by a START (S) and a STOP (P) condition. Each word transmitted to the MAX9507 is 8 bits long and is followed by an acknowledge clock pulse. A master reads from the MAX9507 by

transmitting the slave address with the R/W bit set to 0, the register address of the register to be read, a REPEAT-ED START (Sr) condition, the slave address with the R/W bit set to 1, followed by a series of SCL pulses. The MAX9507 transmits data on SDA in sync with the master-generated SCL pulses. The master acknowledges receipt of each byte of data. Each read sequence is framed by a START or REPEATED START condition, an acknowledge or a not acknowledge, and a STOP condition. SDA operates as both an input and an open-drain output. A pullup resistor, typically greater than  $500\Omega$ , is required on the SDA bus. SCL operates as only an input. A pullup resistor, typically greater than  $500\Omega$ , is required on SCL if there are multiple masters on the bus, or if the master in a single-master system has an open-drain SCL output.

SMBus is a trademark of Intel Corp.

MIXIM

<sup>\*\*</sup>If SPEN = 0, then the signal path will be automatically enabled when a video load is detected and the charge pump has been enabled and has settled.

<sup>\*\*\*</sup> If CPEN = 0, then the charge pump will be automatically enabled when a video load is detected.

Series resistors in line with SDA and SCL are optional. Series resistors protect the digital inputs of the MAX9507 from high-voltage spikes on the bus lines, and minimize crosstalk and undershoot of the bus signals.

#### Bit Transfer

One data bit is transferred during each SCL cycle. The data on SDA must remain stable during the high period of the SCL pulse. Changes in SDA while SCL is high are control signals (see the *START and STOP Conditions* section). SDA and SCL idle high when the I<sup>2</sup>C bus is not busy.

#### START and STOP Conditions

SDA and SCL idle high when the bus is not in use. A master initiates communication by issuing a START condition. A START condition is a high-to-low transition on SDA with SCL high. A STOP condition is a low-to-high transition on SDA while SCL is high (Figure 6). A START condition from the master signals the beginning of a transmission to the MAX9507. The master terminates transmission, and frees the bus, by issuing a STOP condition. The bus remains active if a REPEATED START condition is generated instead of a STOP condition.

### Early STOP Conditions

The MAX9507 recognizes a STOP condition at any point during data transmission except if the STOP condition occurs in the same high pulse as a START condition. For proper operation, do not send a STOP condition during the same SCL high pulse as the START condition.

#### Slave Address

The slave address is defined as the 7 most significant bits (MSBs) followed by the read/write (R/W) bit. Set the R/W bit to 1 to configure the MAX9507 to read mode. Set the R/W bit to 0 to configure the MAX9507 to write mode. The slave address is always the first byte of information sent to the MAX9507 after a START or a REPEATED START condition. The MAX9507 slave address is configurable with DEV\_ADDR. Table 4 shows the possible slave addresses for the MAX9507.

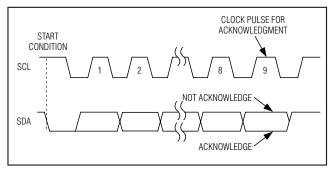

#### Acknowledge

The acknowledge bit (ACK) is a clocked 9th bit that the MAX9507 uses to handshake receipt of each byte of data when in write mode (see Figure 7). The MAX9507 pulls down SDA during the entire master-generated ninth clock pulse if the previous byte is successfully received. Monitoring ACK allows for detection of unsuccessful data transfers. An unsuccessful data transfer occurs if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the bus master may retry communication. The master pulls down SDA during the ninth clock cycle to acknowledge receipt of data when the MAX9507 is in read mode. An acknowledge is sent by the master after each read byte to allow data transfer to continue. A not acknowledge is sent when the master reads the final byte of data from the MAX9507, followed by a STOP condition.

**Table 4. Slave Address**

| DEV_ADDR        | В7 | В6 | В5 | В4 | В3 | B2 | B1 | В0  | WRITE ADDRESS<br>(hex) | READ ADDRESS<br>(hex) |

|-----------------|----|----|----|----|----|----|----|-----|------------------------|-----------------------|

| GND             | 1  | 0  | 0  | 1  | 1  | 0  | 0  | R/W | 0x98                   | 0x99                  |

| V <sub>DD</sub> | 1  | 0  | 0  | 1  | 1  | 0  | 1  | R/W | 0x9A                   | 0x9B                  |

| SCL             | 1  | 0  | 0  | 1  | 1  | 1  | 0  | R/W | 0x9C                   | 0x9D                  |

| SDA             | 1  | 0  | 0  | 1  | 1  | 1  | 1  | R/W | 0x9E                   | 0x9F                  |

Figure 6. START, STOP, and REPEATED START Conditions

Figure 7. Acknowledge

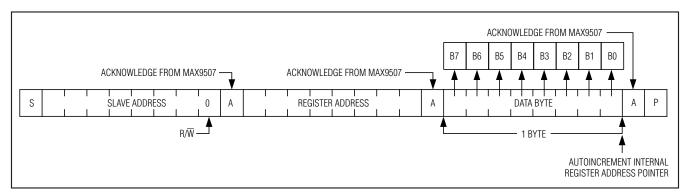

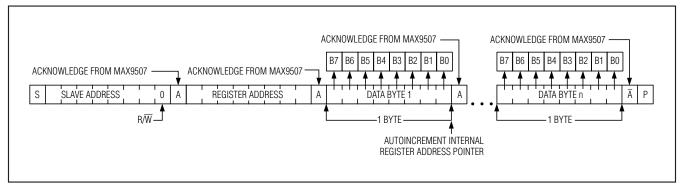

#### Write Data Format

A write to the MAX9507 consists of transmitting a START condition, the slave address with the R/W bit set to 0, one data byte to configure the internal register address pointer, one or more data bytes, and a STOP condition. Figure 8 illustrates the proper frame format for writing one byte of data to the MAX9507. Figure 9 illustrates the frame format for writing n-bytes of data to the MAX9507.

The slave address with the R/W bit set to 0 indicates that the master intends to write data to the MAX9507. The MAX9507 acknowledges receipt of the address byte during the master-generated ninth SCL pulse.

The second byte transmitted from the master configures the MAX9507's internal register address pointer. The pointer tells the MAX9507 where to write the next byte of data. An acknowledge pulse is sent by the MAX9507 upon receipt of the address pointer data.

The third byte sent to the MAX9507 contains the data that will be written to the chosen register. An acknowledge pulse from the MAX9507 signals receipt of the data byte. The address pointer autoincrements to the

next register address after each received data byte. This autoincrement feature allows a master to write to sequential register address locations within one continuous frame. The master signals the end of transmission by issuing a STOP condition.

#### Read Data Format

The master presets the address pointer by first sending the MAX9507's slave address with the R/W bit set to 0 followed by the register address after a START condition. The MAX9507 acknowledges receipt of its slave address and the register address by pulling SDA low during the ninth SCL clock pulse. A REPEATED START condition is then sent followed by the slave address with the R/W bit set to 1. The MAX9507 transmits the contents of the specified register. Transmitted data is valid on the rising edge of the master-generated serial clock (SCL). The address pointer autoincrements after each read data byte. This autoincrement feature allows all registers to be read sequentially within one continuous frame. A STOP condition can be issued after any number of read data bytes. If a STOP condition is issued followed by another read operation, the first

Figure 8. Writing a Byte of Data to the MAX9507

Figure 9. Writing n-Bytes of Data to the MAX9507

data byte to be read will be from the register address location set by the previous transaction and not 0x00, and subsequent reads will autoincrement the address pointer until the next STOP condition. Attempting to read from register addresses higher than 0x01 results in repeated reads from a dummy register containing 0xFF data. The master acknowledges receipt of each read byte during the acknowledge clock pulse. The master must acknowledge all correctly received bytes except the last byte. The final byte must be followed by a not acknowledge from the master and then a STOP condition. Figures 10 and 11 illustrate the frame format for reading data from the MAX9507.

### \_Applications Information

### **Power Consumption**

The quiescent power consumption and average power consumption of the MAX9507 is remarkably low because of 1.8V operation and DirectDrive technology. Quiescent power consumption is defined when the MAX9507 is operating without load. In this case, the MAX9507 consumes about 5.8mW. Average power consumption, which is defined when the MAX9507 drives a 150 $\Omega$  load to ground with a 50% flat field, is about 11.7mW. Table 5 shows the power consumption with different video signals. The supply voltage is 1.8V and OUT drives a 150 $\Omega$  load to ground.

Notice that the two extremes in power consumption occur with a video signal that is all black and a video signal that is all white. The power consumption with 75% color bars and 50% flat field lies in between the extremes.

Figure 10. Reading One Indexed Byte of Data from the MAX9507

Figure 11. Reading n-Bytes of Indexed Data from the MAX9507

### Table 5. MAX9507 Power Consumption with Different Video Signals

| VIDEO SIGNAL     | MAX9507 POWER CONSUMPTION WITH FILTER ENABLED (mW) | MAX9507 POWER CONSUMPTION WITH FILTER DISABLED (mW) |  |  |  |

|------------------|----------------------------------------------------|-----------------------------------------------------|--|--|--|

| All Black Screen | 6.7                                                | 6.2                                                 |  |  |  |

| All White Screen | 18.2                                               | 17.9                                                |  |  |  |

| 75% Color Bars   | 11.6                                               | 11.0                                                |  |  |  |

| 50% Flat Field   | 11.7                                               | 11.3                                                |  |  |  |

### datashee 40.00 index by Control of the Control of t

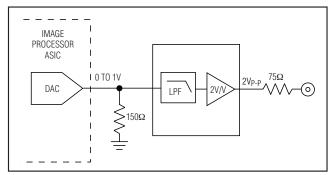

Devices designed to generate 1VP-P video signals at the output of the video DAC can still work with the MAX9507. Most video DACs source current into a ground-referenced resistor, which converts the current into a voltage. Figure 12 shows a video DAC that creates a video signal from 0 to 1V across a 150 $\Omega$  resistor. The following video filter amplifier has a 2V/V gain so that the output is 2VP-P.

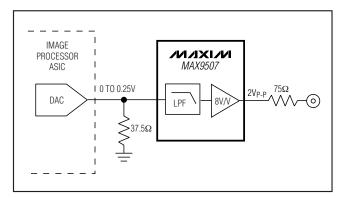

The MAX9507 expects input signals that are 0.25Vp-p nominally. The same video DAC can be made to work with the MAX9507 by scaling down the 150 $\Omega$  resistor to a 37.5 $\Omega$  resistor, as shown in Figure 13. The 37.5 $\Omega$  resistor is one-quarter the size of the 150 $\Omega$  resistor, resulting in a video signal that is one-quarter the amplitude.

Figure 12. Video DAC Generates a 1V<sub>P-P</sub> Signal Across a 150Ω Resistor Connected to Ground

Figure 13. Video DAC Generates a 0.25Vp-p Signal Across a 37.5 $\Omega$  Resistor Connected to Ground

### **Changing Between Video Output and Microphone Input on a Single Connector**

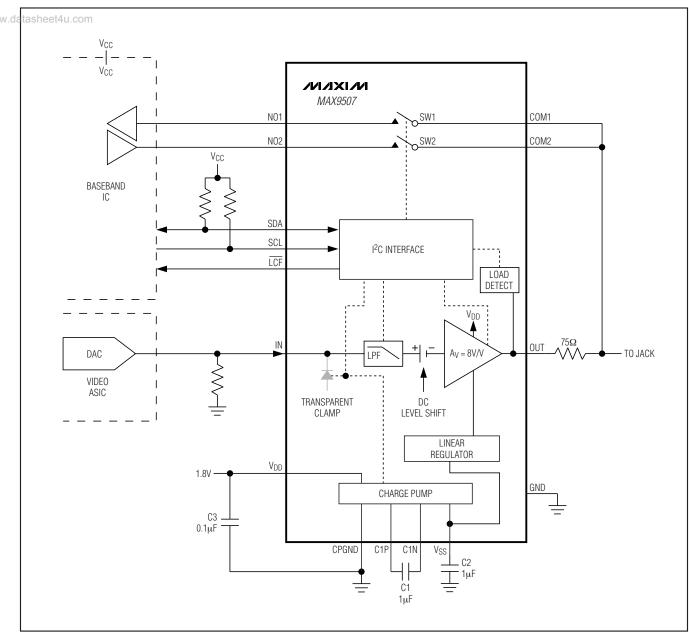

Figure 14 shows how a single pole on a mobile phone jack can be used for transmitting a video signal to a television or receiving the signal from the microphone of a headset. To transmit a video signal, open SW1 and enable the video circuitry. To receive a signal from a microphone, close SW1 and disable the video circuitry.

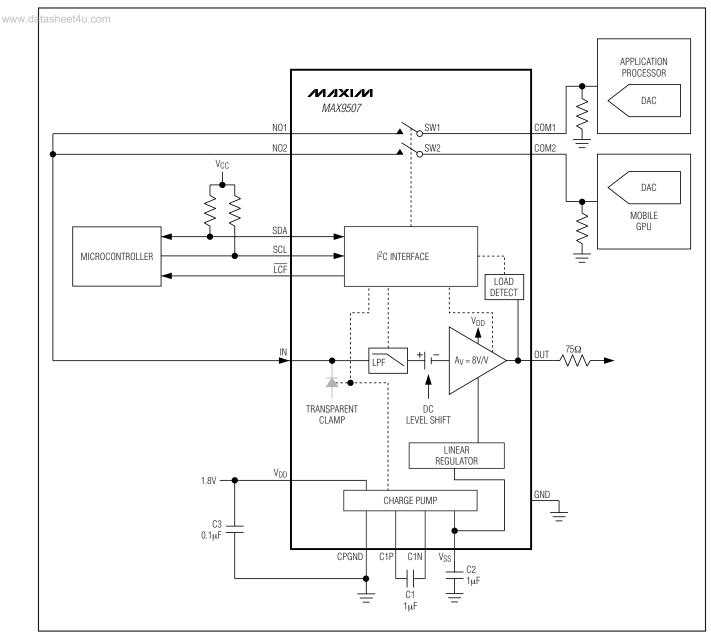

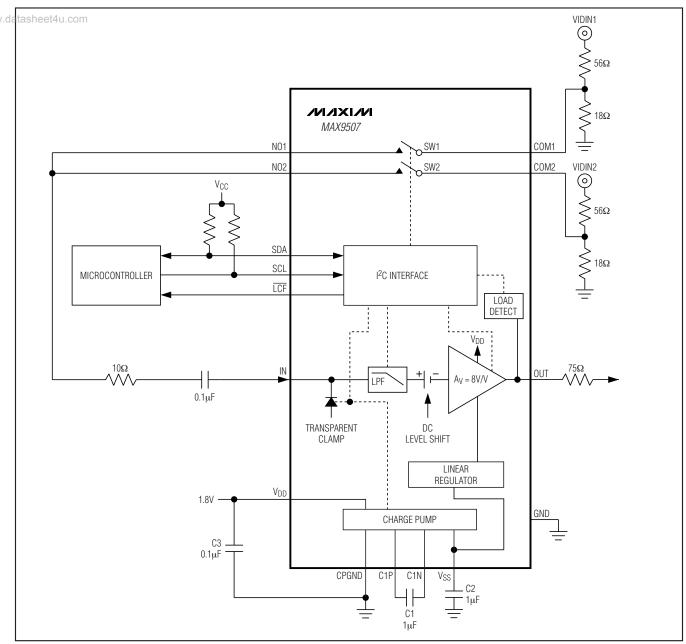

### Switching Between Video and Digital Signals