www.datasheet4u.com

## **General Description**

Applications

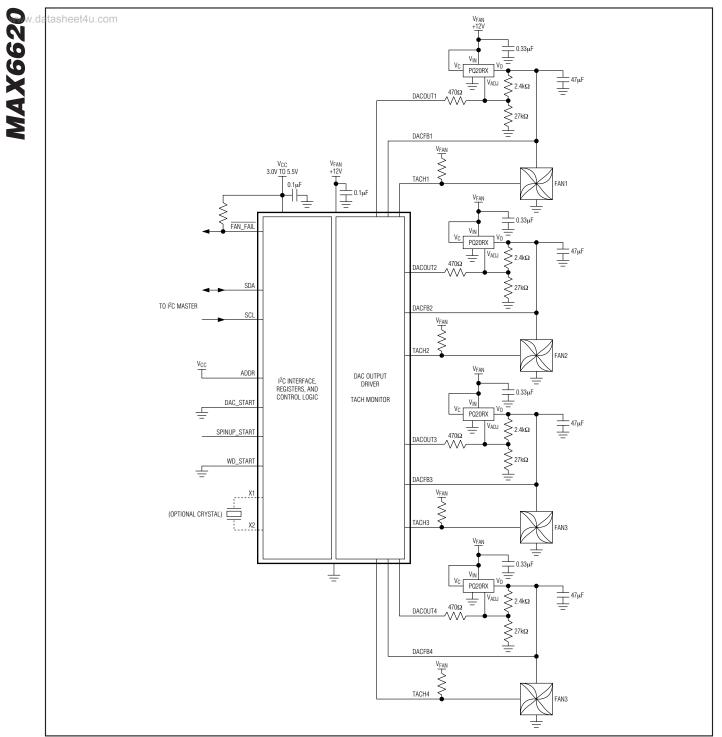

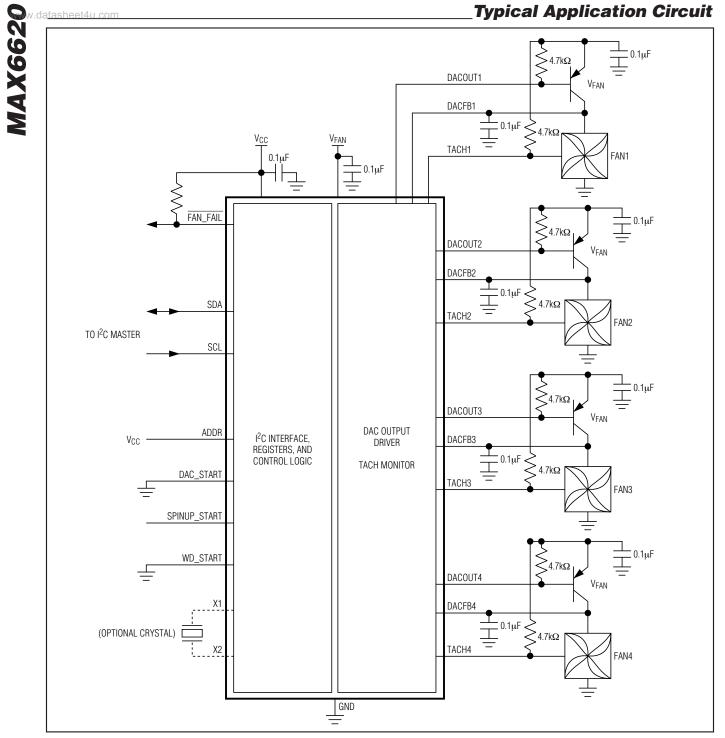

The MAX6620 controls the speeds of up to four fans using four independent linear voltage outputs. The drive voltages for the fans are controlled directly over the I<sup>2</sup>C interface. Each output drives the base of an external bipolar transistor or the gate of a FET in highside drive configuration. Voltage feedback at the fan's power-supply terminal is used to force the correct output voltage.

The MAX6620 offers two methods for fan control. In RPM mode, the MAX6620 monitors four fan tachometer logic outputs for precise ( $\pm$ 1%) control of fan RPM and detection of fan failure. In DAC mode, each fan is driven with a voltage resolution of 9 bits and the tachometer outputs of the fans are monitored for failure.

The DAC\_START input selects the fan power-supply voltage at startup to ensure appropriate fan drive when power is first applied. A watchdog feature turns the fans fully on to protect the system if there are no valid I<sup>2</sup>C communications within a preset timeout period.

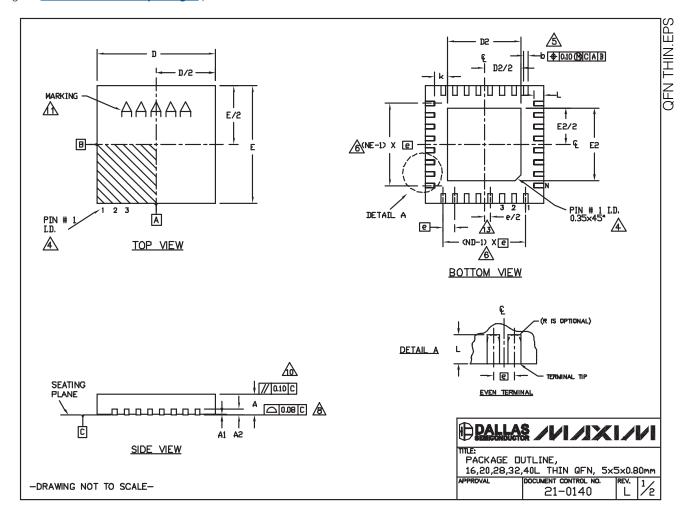

The MAX6620 operates from a 3.0V to 5.5V power supply with low 250 $\mu$ A supply current, and the l<sup>2</sup>C-compatible interface makes it ideal for fan control in a wide range of cooling applications. The MAX6620 is available in a 28-pin TQFN package and operates over the -40°C to +125°C automotive temperature range.

Consumer Products Servers Communications Equipment Storage Equipment \_Features

- Controls Up to Four Independent Fans With Linear (DC) Drive

- Uses Four External Low-Cost Pass Transistors

- 1% Accuracy Precision RPM Control

- Controlled Voltage Rate-Of-Change for Best Acoustics

- I<sup>2</sup>C Bus Interface

- 3.0V to 5.5V Supply Voltage Range

- ♦ 250µA (typ) Operating Supply Current

- ♦ 3µA (typ) Shutdown Supply Current

- Small 5mm x 5mm Footprint

## **Ordering Information**

| PART                          | TEMP RANGE      | PIN-<br>PACKAGE | PKG<br>CODE |  |  |  |  |  |

|-------------------------------|-----------------|-----------------|-------------|--|--|--|--|--|

| MAX6620ATI+                   | -40°C to +125°C | 28 TQFN-EP*     | T2855-8     |  |  |  |  |  |

| +Denotes a lead-free package. |                 |                 |             |  |  |  |  |  |

EP – Exposed paddlo

\*EP = Exposed paddle.

Typical Application Circuit appears at end of data sheet.

## M/IXI/M

\_ Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4644.com or visit Maxim's website at www.maxim-ic.com.

## **ABSOLUTE MAXIMUM RATINGS**

| VCC to GND                               | 0.3V to +6.0V                     |

|------------------------------------------|-----------------------------------|

| FAN_FAIL, SDA, SCL to GND                | 0.3V to +6.0V                     |

| ADDR, SPINUP_START, DAC_START, WD        | _START,                           |

| X1, X2 to GND                            | -0.3V to (V <sub>CC</sub> + 0.3V) |

| All Other Pins to GND                    | 0.3V to +13.5V                    |

| Input Current at DACOUT_ Pins (Note 1)   | +5mA/-50mA                        |

| Input Current at Any Pin (Note 1)        | 5mA                               |

| ESD Protection (all pins, Human Body Mod | el) (Note 2) ±2000V               |

|                                          |                                   |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |  |

|-------------------------------------------------------|--|

| 28-Pin TQFN (derate 34.5mW/°C above +70°C)2758.6mW    |  |

| Operating Temperature Range40°C to +125°C             |  |

| Junction Temperature+150°C                            |  |

| Storage Temperature Range65°C to +150°C               |  |

| Lead Temperature (soldering, 10s)+300°C               |  |

**Note 1:** Absolute Maximum Ratings indicate limits beyond which damage to the device may occur. DC and AC electrical specifications do not apply when operating the device beyond its rated operating conditions.

Note 2: Human Body Model, 100pF discharged through a  $1.5k\Omega$  resistor.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## **ELECTRICAL CHARACTERISTICS**

(T<sub>A</sub> = -40°C to +125°C, V<sub>CC</sub> = 3.0V to 5.5V, unless otherwise noted. Typical values are at T<sub>A</sub> = +25°C, V<sub>CC</sub> = 3.3V.) (Note 3)

| PARAMETER                                | SYMBOL          | CON                                                                  | DITION                                | MIN   | ТҮР     | MAX                       | UNITS |

|------------------------------------------|-----------------|----------------------------------------------------------------------|---------------------------------------|-------|---------|---------------------------|-------|

| Operating Supply Voltage                 | V <sub>CC</sub> |                                                                      |                                       | 3.0   |         | 5.5                       | V     |

| Operating Supply Current                 | ICC             | $V_{CC} = 5.5V$                                                      |                                       | 0.25  | 0.60    | mA                        |       |

| Quieseent Queelu Querent                 |                 | I <sup>2</sup> C inactive                                            |                                       |       | 0.2     | 0.5                       | mA    |

| Quiescent Supply Current                 |                 | Shutdown mode                                                        |                                       |       | 3       | 20                        | μA    |

|                                          | Vfanhi          |                                                                      |                                       | 10    | 12      | 13.5                      | V     |

| V <sub>FAN</sub> Supply Voltage          | VFANLO          |                                                                      |                                       | 4.0   | 5.0     | 5.5                       | v     |

|                                          |                 | V <sub>GND</sub> + 10V < V <sub>DACC</sub><br>V <sub>FAN</sub> = 12V | DUT_ < 11.5V,                         | -18   |         |                           |       |

| DACOUT_ Output Current                   | IDACOUT_        | V <sub>GND</sub> + 3V < V <sub>DACOU</sub><br>V <sub>FAN</sub> = 12V | -16                                   |       |         | mA                        |       |

| DACOUT_ Output Voltage                   | VDACOUT_        | IDACOUT_ = 5mA                                                       |                                       | 0.05  |         | V <sub>FAN</sub> -<br>0.1 | V     |

|                                          | DACFBHS         |                                                                      | V <sub>FAN</sub> = V <sub>FANHI</sub> |       | 256/535 |                           |       |

| DAC Feedback Voltage at Half             |                 | At DACFB_,<br>code = 0x100,<br>IDACOUT_ = 5mA                        | VFAN = VFANLO                         |       | 256/567 |                           | V     |

| Scale                                    |                 |                                                                      | $V_{FAN} = 12V$                       | 5.54  | 5.74    | 5.94                      | V     |

|                                          |                 |                                                                      | $V_{FAN} = 5V$                        | 2.05  | 2.25    | 2.45                      |       |

|                                          | DACFBFS         |                                                                      | V <sub>FAN</sub> = V <sub>FANHI</sub> |       | 511/535 |                           |       |

| DAC Feedback Voltage at Full             | DACEBES         | At DACFB_,<br>code = 0x1FF,                                          | VFAN = VFANLO                         |       | 511/567 |                           | v     |

| Scale                                    | VDACFB511       | $I_{DACOUT} = 5mA$                                                   | $V_{FAN} = 12V$                       | 11.25 | 11.45   | 11.65                     | v     |

|                                          | VDACFB511       |                                                                      | $V_{FAN} = 5V$                        | 4.3   | 4.5     | 4.7                       |       |

| Drive Voltage Resolution                 |                 |                                                                      |                                       |       | 9       |                           | Bit   |

| DACFB_ Impedance                         | RDACFB          |                                                                      |                                       |       | 1       |                           | MΩ    |

| TACH Minimum Input Pulse Width           |                 |                                                                      |                                       | 25    |         |                           | μs    |

| Internal Reference Frequency<br>Accuracy |                 | (Note 4)                                                             |                                       | -3    |         | +3                        | %     |

| TACH Count Accuracy (Note 4)             |                 | Using 32.768kHz crys                                                 | stal                                  | -0.1  |         | +0.1                      | %     |

| TACH COUNT ACCURACY (NOLE 4)             |                 | Using on-chip oscillat                                               | or                                    | -2    |         | +2                        | /0    |

## www.dELECTRICAL CHARACTERISTICS (continued)

$(T_A = -40^{\circ}C \text{ to } + 125^{\circ}C, V_{CC} = 3.0V \text{ to } 5.5V, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C, V_{CC} = 3.3V.)$  (Note 3)

| PARAMETER                                          | SYMBOL          | CONDITION                               | MIN                      | ТҮР                          | MAX                      | UNITS    |

|----------------------------------------------------|-----------------|-----------------------------------------|--------------------------|------------------------------|--------------------------|----------|

|                                                    |                 | Using 32.768kHz crystal, test at 850RPM | -1                       |                              | +1                       | <u> </u> |

| Fan Control Accuracy (Note 4)                      |                 | Using on-chip oscillator                | -3                       |                              | +3                       | %        |

| XTAL Oscillator Startup Time                       |                 |                                         |                          | 2                            |                          | S        |

| X1 Input Threshold                                 |                 |                                         |                          | 0.7                          |                          | V        |

|                                                    | VCC             |                                         |                          | 2                            |                          | M        |

| POR Threshold                                      | VFAN            |                                         |                          | 3.5                          |                          | V        |

| LOGIC (SDA, SCL, FAN_FAIL, W                       | D_START, T      | ACH_)                                   |                          |                              |                          |          |

| Input High Voltage                                 | VIH             |                                         | V <sub>CC</sub> x        |                              |                          | V        |

|                                                    | ۷IH             |                                         | 0.7                      |                              |                          | v        |

| Input Low Voltage                                  | VIL             |                                         |                          |                              | V <sub>CC</sub> x<br>0.3 | V        |

| Input High Current                                 | Ιн              |                                         |                          |                              | 1.0                      | μA       |

| Input Low Current                                  | ЦĽ              |                                         |                          |                              | -1.0                     | μA       |

| Input Capacitance                                  |                 | All digital inputs                      |                          | 6                            |                          | рF       |

| Output High Current                                |                 |                                         |                          |                              | 100                      | μA       |

| Output Low Voltage                                 |                 | I <sub>OL</sub> = 3mA                   |                          |                              | 0.4                      | V        |

| LOGIC (DAC_START, SPIN_STAI                        | RT, ADDR)       | ·                                       | •                        |                              |                          | •        |

| Input High Voltage                                 | VIH             |                                         | V <sub>CC</sub> -<br>0.5 |                              |                          | V        |

| Input Low Voltage                                  | VIL             |                                         |                          |                              | 0.5                      | V        |

| Input High Current                                 | IIH             |                                         |                          |                              | 1.0                      | μA       |

| Input Low Current                                  | ١ <sub>١L</sub> |                                         |                          |                              | -1.0                     | μA       |

| Input Capacitance                                  |                 | All digital inputs                      |                          | 6                            |                          | рF       |

| I <sup>2</sup> C-COMPATIBLE TIMING (Notes          | 5, 6)           |                                         |                          |                              |                          |          |

| Serial Clock Frequency                             | fscl            |                                         |                          |                              | 400                      | kHz      |

| Bus Free Time Between STOP<br>and START Conditions | tBUF            |                                         | 1.3                      |                              |                          | μs       |

| START Condition Hold Time                          | thd:sta         |                                         | 0.6                      |                              |                          | μs       |

| STOP Condition Setup Time                          | ts∪:sto         |                                         | 600                      |                              |                          | ns       |

| Clock Low Period                                   | tlow            |                                         | 1.3                      |                              |                          | μs       |

| Clock High Period                                  | thigh           |                                         | 0.6                      |                              |                          | μs       |

| START Condition Setup Time                         | tsu:sta         |                                         | 600                      |                              |                          | ns       |

| Data Setup Time                                    | tsu:dat         |                                         | 100                      |                              |                          | ns       |

| Data Out Hold Time                                 | tDH             |                                         | 100                      |                              |                          | ns       |

| Data In Hold Time                                  | thd:dat         | (Note 6)                                | 0                        |                              | 0.9                      | μs       |

| Maximum Receive SCL/SDA Rise<br>Time               | t <sub>R</sub>  | (Note 8)                                |                          | 300                          |                          | ns       |

| Minimum Receive SCL/SDA Rise<br>Time               | t <sub>R</sub>  | (Note 7)                                |                          | 20 + 0.1<br>x C <sub>B</sub> |                          | ns       |

**MAX6620**

www.DataSheet4U.com

## ELECTRICAL CHARACTERISTICS (continued)

$(T_A = -40^{\circ}C \text{ to } + 125^{\circ}C, V_{CC} = 3.0V \text{ to } 5.5V, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C, V_{CC} = 3.3V.)$  (Note 3)

| PARAMETER                                     | SYMBOL         | CONDITION                       | MIN                          | ТҮР | MAX | UNITS |

|-----------------------------------------------|----------------|---------------------------------|------------------------------|-----|-----|-------|

| Maximum Receive SCL/SDA Fall<br>Time          | tF             |                                 |                              | 300 |     | ns    |

| Minimum Receive SCL/SDA Fall<br>Time          | te I (Note 7)  |                                 |                              | ns  |     |       |

| Transmit SDA Fall Time t <sub>F</sub> (       |                | (Note 7)                        | 20 + 0.1<br>x C <sub>B</sub> |     | 250 | ns    |

| Pulse Width of Suppressed Spike               | tsp            | (Note 8)                        | 0                            |     | 50  | ns    |

| Output Fall Time                              |                | $C_{L} = 400 pF, I_{OUT} = 3mA$ |                              |     | 250 | ns    |

| SDA Time Low for Reset of Serial<br>Interface | <b>TIMEOUT</b> | (Note 9)                        | 20                           |     | 50  | ms    |

Note 3: All parts will operate properly over the V<sub>CC</sub> supply voltage range of 3.0V to 5.5V.

Note 4: Guaranteed by design and characterization.

Note 5: All timing specifications are guaranteed by design.

Note 6: A master device must provide a hold time of at least 300ns for the SDA signal to bridge the undefined region of SCL's falling edge.

**Note 7:**  $C_B$  = total capacitance of one bus line in pF. Tested with  $C_B$  = 400pF.

Note 8: Input filters on SDA and SCL suppress noise spikes less than 50ns.

**Note 9:** Holding the SDA line low for a time greater than t<sub>TIMEOUT</sub> will cause the devices to reset SDA to the idle state of the serial bus communication (SDA set high).

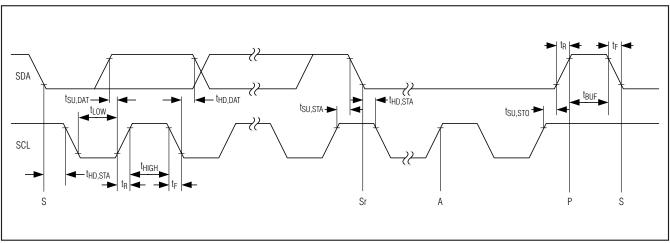

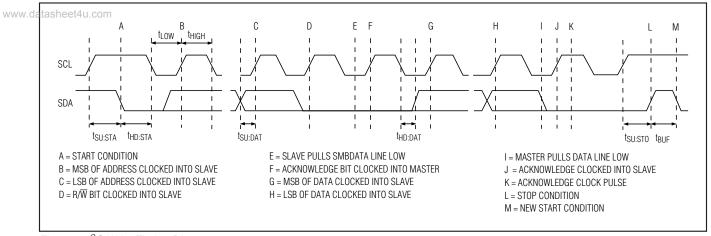

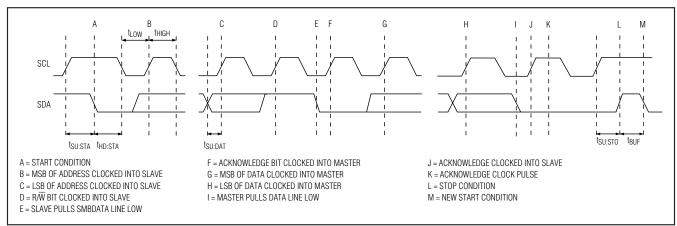

Figure 1. I<sup>2</sup>C Serial Interface Timing

**MAX6620**

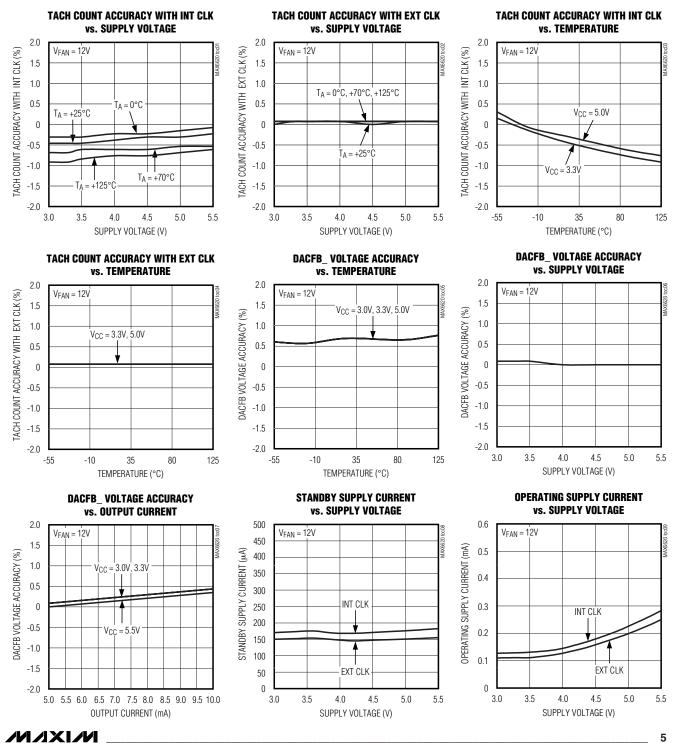

**Typical Operating Characteristics**

#### www.datasheet4u.com

(V<sub>CC</sub> = 3.3V, V<sub>FAN</sub> = 12V, T<sub>A</sub> =  $+25^{\circ}$ C, unless otherwise noted.)

**MAX6620**

www.DataSheet4U.com

da<u>tasheet4u.com</u>

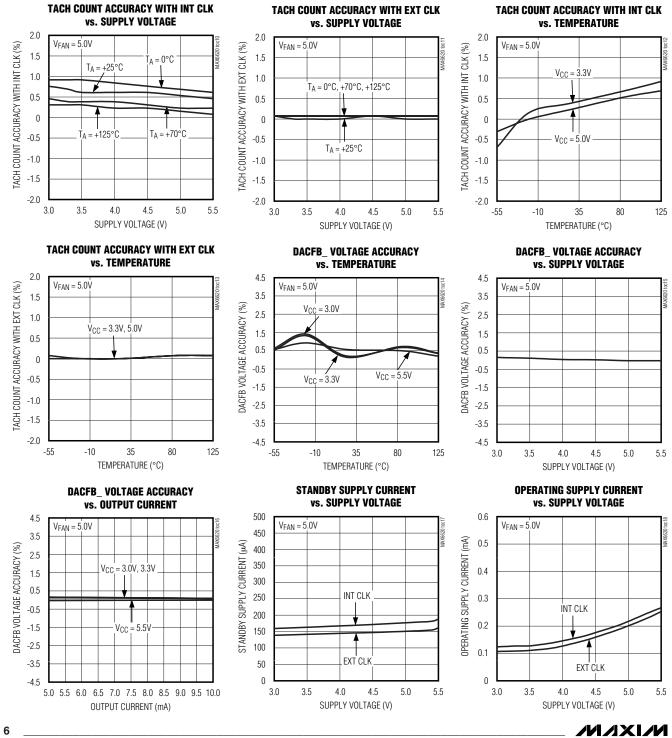

**Typical Operating Characteristics (continued)**

(V<sub>CC</sub> = 3.3V, V<sub>FAN</sub> = 12V, T<sub>A</sub> =  $+25^{\circ}C$ , unless otherwise noted.)

www.DataSheet4U.com

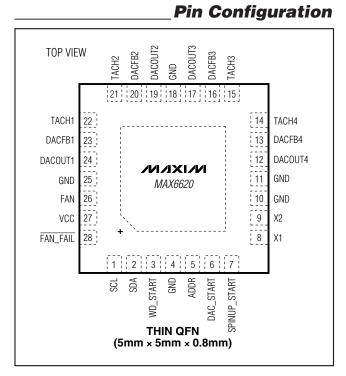

## Pin Description

| PIN                  | NAME                | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------------------|---------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                    | SCL                 | $I^{2}C$ Serial-Clock Input. Can be pulled up to 5.5V regardless of V <sub>CC</sub> . Open circuit when V <sub>CC</sub> = 0V.                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 2                    | SDA                 | Open-Drain, I <sup>2</sup> C Serial-Data Input/Output. Can be pulled up to 5.5V regardless of V <sub>CC</sub> . Open circuit when V <sub>CC</sub> = 0V.                                                                                                                                                                                                                                                                                                                                                                                                            |

| 3                    | WD_START            | Startup Watchdog Set Input. This input is sampled when power is first applied and sets the initial $I^2C$ watchdog behavior. When connected to GND, the watchdog function is disabled. When connected to V <sub>CC</sub> , the MAX6620 monitors SDA. If 10s elapse without a valid $I^2C$ transaction, the fan drive goes to 100%.                                                                                                                                                                                                                                 |

| 4, 10, 11, 18,<br>25 | GND                 | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 5                    | ADDR                | $I^2C$ Address Set Input. This input is sampled when power is first applied and sets the $I^2C$ slave address. When connected to GND, the slave address will be 0x50. When unconnected, the slave address will be 0x52. When connected to V <sub>CC</sub> , the slave address will be 0x54.                                                                                                                                                                                                                                                                        |

| 6                    | DAC_START           | Startup Fan Drive DAC Set Input. This input is sampled when power is first applied and sets the power-up value for the fan drive voltage. When connected to GND, the fan drive voltage will be 0%. When unconnected, the fan drive voltage will be 75%. When connected to V <sub>CC</sub> , the fan drive voltage will be 100%.                                                                                                                                                                                                                                    |

| 7                    | SPINUP_START        | Startup Spin-Up Set Input. This input is sampled when power is first applied and sets the initial spin-up behavior. When connected to GND, spin-up is disabled. When connected to $V_{CC}$ at power-up, the fan is driven with a full-scale drive voltage until two tachometer pulses have been detected, or 1s has elapsed. When unconnected, the fan is driven with a full-scale drive voltage until two tachometer pulses have been detected, or 0.5s has elapsed. Spin-up behavior may be modified by writing appropriate settings to the MAX6620's registers. |

| 8, 9                 | X1, X2              | Crystal Oscillator Inputs. Connections for a standard 32.768kHz quartz crystal. The internal oscillator circuitry is designed for operation with a crystal having a specified load capacitance ( $C_L$ ) of 12pF. Connect an external 32.768kHz oscillator across X1 and X2 for operation with the external oscillator. If no crystal or external oscillator is connected, the MAX6620 will use its internal oscillator.                                                                                                                                           |

| 12, 17, 19, 24       | DACOUT4-<br>DACOUT1 | Fan Drive DAC Outputs. Connect to the gate of a p-channel MOSFET or base of a PNP bipolar transistor.                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 13, 16, 20, 23       | DACFB4-<br>DACFB1   | DAC Feedback Inputs. Connect a 0.1µF capacitor between these pins and GND. Connect to the supply pin of the fan and to the drain of a p-channel MOSFET or collector of a PNP bipolar transistor.                                                                                                                                                                                                                                                                                                                                                                   |

| 14, 15, 21, 22       | TACH4-TACH1         | Fan Tachometer Logic Inputs. These inputs accept input voltages up to VFAN.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 26                   | FAN                 | Fan Power-Supply Voltage Input. Connect to the fan power supply (VFAN). Bypass with a $0.1 \mu F$ capacitor to GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27                   | VCC                 | Power-Supply Input. 3.3V nominal. Bypass $V_{CC}$ to GND with a 0.1µF capacitor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 28                   | FAN_FAIL            | Active-Low, Open-Drain Fan Failure Output. Active only when fault is present; open-circuit when $V_{CC} = 0V$ . This pin can be pulled up to 5.5V regardless of $V_{CC}$ .                                                                                                                                                                                                                                                                                                                                                                                         |

| _                    | EP                  | Exposed Paddle. Internally connected to GND. Connect to a large ground plane to maximize thermal performance. Not intended as an electrical connection point.                                                                                                                                                                                                                                                                                                                                                                                                      |

**MAX6620**

datasheet4u.com

## **\_Detailed Description**

The MAX6620 controls the speeds of up to four fans using four independent linear voltage outputs. The drive voltages for the fans are controlled directly over the I<sup>2</sup>C interface. Each of the outputs (DACOUT1– DACOUT4) drive the base of an external PNP or the gate of a p-channel MOSFET. Voltage feedback at the fan's power-supply terminal is used to force the output voltage.

The MAX6620 monitors fan tachometer logic outputs for precise (1%) control of fan RPM and detection of fan failure. When the MAX6620 is used with 2-wire fans, these inputs are not used, and the fans can be driven to the desired voltage without using tachometer feedback.

Three inputs set the fan drive status on application of power. The DAC\_START input selects the fan-supply voltage (100%, 75%, or 0%) at startup to ensure appropriate fan drive when power is first applied. The SPIN\_START input selects whether spin-up will be applied to the fans at power-up. WD\_START selects whether lack of I<sup>2</sup>C activity will force the fans to full speed. When the watchdog function is enabled, the fans will be driven to full speed if there is no I<sup>2</sup>C activity for a period of 2s, 6s, or 10s.

#### **Digital Interface**

The MAX6620 features an I<sup>2</sup>C-compatible, 2-wire serial interface consisting of a bidirectional serial data line (SDA) and a serial clock line (SCL). SDA and SCL facilitate bidirectional communication between the MAX6620 and the master at rates up to 400kHz. The master (typically a microcontroller) initiates data transfer on the bus and generates SCL. SDA and SCL require 4.7k $\Omega$  (typ) pullup resistors.

#### Bit Transfer

One data bit is transferred during each SCL clock cycle. Nine clock cycles are required to transfer the data into or out of the MAX6620. The data on SDA must remain stable during the high period of the SCL clock pulse, as changes in SDA while SCL is high are control signals (see the *START and STOP Conditions* section). Both SDA and SCL idle high.

| S ADDRESS WR                                                                                           |                            |    | ADDRESS WR A COMMA |                                              | MAND               | ND A                |      | DATA          |                                    | Α                 |                                             | Р                                                                                 |                                         |                                         |

|--------------------------------------------------------------------------------------------------------|----------------------------|----|--------------------|----------------------------------------------|--------------------|---------------------|------|---------------|------------------------------------|-------------------|---------------------------------------------|-----------------------------------------------------------------------------------|-----------------------------------------|-----------------------------------------|

|                                                                                                        | 7 bi                       | ts |                    |                                              |                    | 8 b                 | oits |               |                                    | 8 bi              | ts                                          |                                                                                   |                                         | 1                                       |

| Slave Address: equiva-<br>lent to chip-select line of<br>a 3-wire interface<br><b>Read Byte Format</b> |                            |    |                    |                                              |                    | Byte: s<br>u are wi |      | s which<br>to | set by                             | the co<br>ds, cor | a goes into to<br>mmand by<br>nfiguration r | /te (to                                                                           | set                                     |                                         |

| S                                                                                                      | ADDRESS                    | WR | Α                  | COMMAN                                       | D                  | Α                   | S    | AD            | DRESS                              | RD                | Α                                           | DATA                                                                              | Ā                                       | Р                                       |

|                                                                                                        | 7 bits                     |    |                    | 8 bits                                       |                    |                     |      | -             | 7 bits                             |                   |                                             | 8 bits                                                                            |                                         |                                         |

|                                                                                                        | Slave Add<br>lent to chip- |    |                    | Command<br>which reg<br>reading fro          | jister y           |                     |      | due           | e Address<br>to chang<br>direction |                   |                                             | Data Byte<br>the regist<br>command                                                | er set b                                |                                         |

| Send                                                                                                   | l Byte Form                | at |                    |                                              |                    |                     | Re   | ceiv          | e Byte F                           | ormat             |                                             |                                                                                   |                                         |                                         |

| s                                                                                                      | ADDRESS                    | WR | A                  | COMMAND                                      | Α                  | Р                   |      | S             | ADDRES                             | S RD              | Α                                           | DATA                                                                              | Ā                                       | Р                                       |

|                                                                                                        | 7 bits                     |    |                    | 8 bits                                       |                    |                     |      |               | 7 bits                             |                   |                                             | 8 bits                                                                            |                                         |                                         |

|                                                                                                        | TART CONDI                 | -  | m<br>Ut            | ommand Byte<br>and with no<br>sed for one-sl | data, i<br>hot con | usually<br>nmand    | /    | I             |                                    |                   |                                             | Data Byte:<br>the registe<br>by the las<br>write byte<br>also used<br>response re | er comr<br>st read<br>transn<br>for SME | nandeo<br>byte o<br>hission<br>Bus aler |

Figure 2. I<sup>2</sup>C Protocols

Figure 3. I<sup>2</sup>C Write Timing Diagram

Figure 4. I<sup>2</sup>C Read Timing Diagram

#### START and STOP Conditions

The master initiates a transmission with a START condition (S), a high-to-low transition on SDA with SCL high. The master terminates a transmission with a STOP condition (P), a low-to-high transition on SDA while SCL is high (Figure 3). The STOP condition frees the bus and places all devices in F/S mode (Figure 1). Use a repeated START condition (Sr) in place of a STOP condition to leave the bus active and in its current timing mode.

#### Acknowledge Bits

Successful data transfers are acknowledged with an acknowledge bit (A) or a not-acknowledge bit  $(\overline{A})$ . Both the master and the MAX6620 (slave) generate acknowl-

edge bits. To generate an acknowledge, the receiving device must pull SDA low before the rising edge of the acknowledge-related clock pulse (9th pulse), and keep it low during the high period of the clock pulse (Figure 4). To generate a not acknowledge, the receiver allows SDA to be pulled high before the rising edge of the acknowledge-related clock pulse, and leaves it high during the high period of the clock pulse. Monitoring the acknowledge bits allows for detection of unsuccessful data transfers. An unsuccessful data transfer happens if a receiving device is busy or if a system fault has occurred. In the event of an unsuccessful data transfer, the master should reattempt communication at a later time.

9

MAX6620

# **MAX6620**

#### Slave Address

A master initiates communication with a slave device by issuing a START condition followed by a slave address byte. As shown in Figure 5, the slave address byte consists of 7 address bits and a read/write bit (R/W). When idle, the MAX6620 continuously waits for a START condition followed by its slave address. The first four bits (MSBs) of the slave address have been factory programmed and are always **0101** and the seventh bit is **0**. Connect ADDR to GND or V<sub>CC</sub>, or leave it unconnected to program D2 and D1 of the slave address according to Table 1.

# Table 1. Slave Address Setting withADDR Pin

| ADDR CONNECTION | SLAVE ADDRESS |          |  |  |  |  |

|-----------------|---------------|----------|--|--|--|--|

| ADDR CONNECTION | HEX           | BINARY   |  |  |  |  |

| GND             | 0x50          | 0101 000 |  |  |  |  |

| Unconnected     | 0x52          | 0101 010 |  |  |  |  |

| Vcc             | 0x54          | 0101 100 |  |  |  |  |

After receiving the address, the MAX6620 (slave) issues an acknowledgement by pulling SDA low for one clock cycle.

#### Data Byte (Read and Write)

**Single Read and Burst Read.** A single read begins with the bus master issuing a START condition followed by the seven slave ID address bits and a zero (WR, Figure 2), which is followed by an acknowledge bit (A) from the slave corresponding to the slave ID. Next, the master sends out an 8-bit register address, which is also followed by an acknowledge bit from the slave. The bus master issues another START condition and the same seven slave ID address bits followed by a one (RD, Figure 2), with the slave producing an acknowledge bit. The slave then sends out the 8-bit data corresponding to the register address previously written by the master. The bus master sends back a not-acknowledge bit (A). This completes the single read process and a STOP condition is issued by the bus master.

In a burst read, the process is the same as a single read except that the bus master issues an acknowledge bit after each byte transmitted by the slave. After each acknowledge bit, the register address increments by one, and the data from the next register is transmitted by the slave. The process continues, with data reads followed by acknowledges. After the register with the highest address is read, the register pointer rolls over to point to the first register. To terminate a burst read, the bus master issues a STOP condition.

**Single Write and Burst Write.** A single write begins with the bus master issuing a START condition followed by the seven slave ID address bits and a zero (WR, Figure 2), which is followed by an acknowledge bit (A) from the slave corresponding to the slave ID. Next, the master sends out an 8-bit register address, which is also followed by an acknowledge bit from the slave. After the acknowledge bit, 8-bit data is written to the register, and the slave issues a third acknowledgement. A STOP condition is issued by the bus master to complete the single write process.

In a burst write, the process is similar to a single write except that the master does not issue a STOP condition immediately after the first byte has been written. After the first write is completed, the slave issues an acknowledge bit, the register address increments by one, and the data to be written to the next register is transmitted by the master. The process continues, with data writes followed by acknowledges. After the register with the highest available address is written, the register pointer rolls over to point to the first register. To terminate a burst write, the bus master issues a STOP condition.

#### Fan Drive

The MAX6620 uses external pass transistors to power the fans. DACOUT1-DACOUT4 adjust the powersupply voltage for each fan by driving the base of a PNP bipolar transistor, or the gate of a p-MOSFET. The resulting fan-supply voltage is fed back to DACFB\_. This closes the voltage feedback loop. The system power supply for the output devices is V<sub>FAN</sub>. V<sub>FAN</sub> is

Figure 5. MAX6620 Slave Address Byte

#### www.datasheet4u.com **MAX6620** |-----| \_\_\_\_ ۵. BIT 0 ACK BIT. BIT 0 ACK BIT AM ۵. AM BIT 0 ACK BIT ACK BIT AM AS ACK BIT AS 8-BIT DATA BIT 0 .BIT 0 FIRST 8-BIT DATA LAST 8-BIT DATA BIT 7.. LAST 8-BIT DATA 8-BIT DATA BIT 7.. BIT 7. BIT 7.. ACK BIT AS BIT 7.. BIT 0 AS ----BIT 0 ACK BIT ACK BIT AS 7-BIT SLAVE ID AS 7-BIT SLAVE ID BIT 7.. BIT 8-BIT REGISTER ADDRESS FIRST 8-BIT DATA S S BIT 7. ACK BIT BIT 7. AS ACK BIT AS BIT 0 ACK BIT BIT 0 AS 8-BIT REGISTER ADDRESS 8-BIT REGISTER ADDRESS .BIT 0 8-BIT REGISTER ADDRESS ACK BIT AS BIT 0 0 BIT 7.. BIT 7.. BIT 7.. ACK BIT AS ACK BIT 7-BIT SLAVE ID AS ACK BIT BIT 0 0 BIT 0 AS S: 2-WIRE BUS START CONDITION BY MASTER P: 2-WIRE BUS STOP CONDITION BY MASTER P: 2-WIRE BUS STOP CONDITION BY MASTER ARA ACKNOWLEDGE BY MASTER ANA ACKNOWLEDGE BY MASTER ANA: NO ACKNOWLEDGE BY MASTER 0 BIT 7.. BIT 0 0 7-BIT SLAVE ID 7-BIT SLAVE ID - s 7-BIT SLAVE ID SINGLE WRITE BURST READ SINGLE READ BURST WRITE BIT 7.. BIT 7.. .]\_\_\_\_ BIT 7... \_\_\_\_\_ S S \_|\_ ŗ S

# **Quad Linear Fan-Speed Controller**

Figure 6. Read and Write Summary

www.DataSheet4U.com

nominally 12V or 5V. The drive to the fans is proportional to VFAN. See the *Fan\_Target Drive Voltage Registers* and the *Applications Information* sections for more details.

#### Fan-Speed Control

**DAC (Voltage) Mode.** In DAC mode, the MAX6620 simply sets the voltage that powers the fan. The fan's speed is related, but not precisely proportional to, the drive voltage. The drive voltage is set by the Fan\_Target Drive Voltage registers and may be read from the Fan\_ Drive Voltage registers. Because the output voltage can ramp to new values at a controlled rate, the values in the two registers may be different. See the *Register Descriptions* and *Applications Information* sections for details.

**RPM Mode.** In RPM mode, the MAX6620 monitors tachometer output pulses from the fan and adjusts the fan drive voltage to force the fan's speed to the desired value. Fan speed is measured by counting the number of internal 8192Hz clock cycles that take place during a selectable number of tachometer periods. The number of clock cycles counted (11-bit value) is stored in the Fan\_ TACH Count registers, and the desired number of cycles is stored in the Fan\_ Target TACH Count registers. See the *Register Descriptions* and *Applications Information* sections for details.

**Rate-of-Change Control.** Sudden changes in fan speed can be easily heard by users. The MAX6620 helps reduce the audibility of fan-speed changes by controlling the rate at which the drive to the fan is incremented. Four bits in the Fan\_ Dynamics registers set the rate at which the fan drive voltage is incremented. This allows the time required for a change in fan speed to be varied from 0 (in DAC mode only) to several minutes. See the *Register Descriptions* and *Applications Information* sections for details.

**Monitoring Tachometer Signals.** The TACH\_ inputs accept tachometer or "locked-rotor" output signals from 3- or 4-wire fans. When measuring fan speed, the MAX6620 counts the number of internal 8192Hz clock cycles that occur during 1, 2, 4, 8, 16, or 32 tachometer periods. The number of tachometer periods is selectable for each fan by using the appropriate Fan\_ Dynamics register. Tachometer pulses <25µs in duration are ignored to minimize the effect of noise on the tachometer lines.

The TACH count for a given RPM can be obtained from the following equation:

TACH count =

$$\frac{60}{NP \times RPM} \times SR \times 8192 = \frac{491520 \times SR}{NP \times RPM}$$

where:

NP = number of tachometer pulses per revolution. Most general-purpose brushless DC fans produce two tachometer pulses per revolution.

SR = 1, 2, 4, 8, 16, or 32. See the Fan\_ Speed Range information in the *Fan\_ Dynamics Registers (06h, 07h, 08h, 09h)*—*POR = 0100 1100* section.

The tachometer count consists of 11 bits in the Fan\_ TACH Count registers and is available in RPM and DAC modes. In RPM mode, the desired fan count is written to the Fan\_ Target TACH Count registers.

#### Fan Failure Detection

When enabled, the MAX6620 monitors the TACH inputs to determine when a fan has failed. For fans with tachometer outputs, failure is detected in various ways depending on the fan control mode. In every case, four consecutive fault detections are required to decide whether the fan has failed. In DAC mode, the Fan\_ Target TACH Count registers hold the upper limit for tachometer count values; a fault condition is identified when a TACH count exceeds the value written to the Fan\_ Target TACH Count registers for more than 1s. In RPM mode, a fault condition is identified when any of the following three conditions occur for more than 1s: 1) the TACH count exceeds the value of the Fan\_ Target TACH Count registers while the fan drive voltage is at full-scale, 2) the TACH count exceeds two times the Fan\_ Target TACH Count value, or 3) the TACH count reaches its full count of 7FF.

Some fans have locked rotor outputs that produce a logic-level output to indicate that the fan has stopped spinning. These signals can be monitored by setting D2:D1 in the Fan\_ Configuration registers. D2 selects locked rotor or tachometer monitoring and D1 selects the polarity of the locked rotor signal. A fan fault has occurred when a locked rotor signal has been present for 1s.

Fan failure is indicated in the Fan Fault register and also with the open-drain FAN\_FAIL output. The FAN\_FAIL output may be masked using the mask bits in the Fan Fault register. When a fan failure is detected, drive to the affected fan is removed. Drive may be restored by writing a new DAC or fan count target to the fan's control registers. The global configuration regis-

ter's bit D4 can be used to cause a fan failure to force

#### Watchdog

The MAX6620 includes an optional I<sup>2</sup>C watchdog function that monitors the I<sup>2</sup>C bus for transactions. When the watchdog function is enabled, all fans will be forced to full speed if no I<sup>2</sup>C transactions occur within a selected period (2s, 6s, or 10s).

#### Spin-Up

When a fan is not spinning, and a voltage less than the nominal fan-supply voltage is applied to its powersupply terminals, it may fail to start spinning. To overcome this, the full nominal supply voltage may be applied to the fan terminals for a short time before a lower voltage is applied. This "spin-up" period allows the fan to overcome inertia and begin operating. Spinup is controlled using the Fan\_ Configuration registers. Spin-up can be disabled, or it can cause the fan to be driven with the full supply voltage until it produces two tachometer pulses, up to a maximum of 0.5s, 1s, or 2s when the fan is started.

#### POR Options

Three inputs allow set up of the MAX6620's behavior at power-up. These inputs are sampled when power is first applied to the MAX6620:

- **WD\_START.** Connect WD\_START to V<sub>CC</sub> to enable, or to ground to disable, the watchdog function. When enabled using WD\_START, the timeout period is 10s. After power is applied, the watchdog function may be enabled or disabled through the global configuration register.

- **SPINUP\_START.** At power-up, spin-up operation is controlled by the SPINUP\_START pin, which can be connected to ground (spin-up disabled), V<sub>CC</sub> (spin-up for a maximum of 1s), or unconnected (spin-up for a maximum of 0.5s).

- **DAC\_START.** This input controls the fan drive voltage (for all four fans) at power-up. When connected to ground, the initial fan drive voltage will be 0V. When connected to  $V_{CC}$ , the initial fan drive voltage will be full scale. When unconnected, the initial fan drive voltage will be 75% of V<sub>FAN</sub>.

# **MAX6620**

|                         |                                                                                  |             |                                                                                                                   |                             |                             |                             |                                                                                                                                                                                                                                 |                                                                                                                         |                        | Regis                  |  |

|-------------------------|----------------------------------------------------------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------|-----------------------------|-----------------------------|-----------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|------------------------|------------------------|--|

| 8                       | I <sup>2</sup> C<br>Watchdog<br>Status<br>(read only):<br>1 =<br>elapsed         | Fan 1 Mask  |                                                                                                                   |                             |                             |                             |                                                                                                                                                                                                                                 |                                                                                                                         |                        |                        |  |

| 5                       | I <sup>2</sup> C Watchdog:<br>0 = No watchdog<br>01 = 2s<br>10 = 6s<br>11 = 10s  | Fan 2 Mask  | Locked<br>Rotor<br>Polarity:<br>0 = Iow<br>1 = high                                                               |                             |                             |                             |                                                                                                                                                                                                                                 |                                                                                                                         |                        |                        |  |

| D2                      | 1 <sup>2</sup> C Watchdog:<br>00 = No watchdog<br>01 = 2s<br>10 = 6s<br>11 = 10s | Fan 3 Mask  | TACH/<br>Locked<br>Rotor:<br>0 = TACH<br>1 = locked<br>rotor                                                      | c                           | _                           | ſ                           | nge:<br>C mode)<br>A mode)<br>A mode)<br>LSB<br>LSB<br>LSB<br>LSB<br>SB<br>SB<br>SB                                                                                                                                             |                                                                                                                         |                        |                        |  |

| B3                      | OSC:<br>0 = internal<br>1 = XTAL                                                 | Fan 4 Mask  | TACH<br>input<br>enable                                                                                           | Configuration               | Same as Fan 1 Configuration | Same as Fan 1 Configuration | DAC Rate-of-Change:<br>000 = 0s per LSB (DAC mode)<br>0.0625s per LSB (RPM mode)<br>001 = 0.015625s per LSB<br>011 = 0.03125s per LSB<br>011 = 0.0325s per LSB<br>101 = 0.25s per LSB<br>110 = 0.25 per LSB<br>111 = 1s per LSB | Same as Fan 1 Dynamics                                                                                                  | Same as Fan 1 Dynamics | Same as Fan 1 Dynamics |  |

| D4                      | Fans to<br>100% on<br>failure:<br>0 = enabled<br>1 = disabled                    | Fan 1 Fault |                                                                                                                   | Same as Fan 1 Configuration | àame as Fan<br>àame as Fan  | àame as Fan 1               | DAC<br>000 = 05<br>0.0625s<br>0.0625s<br>001 =<br>101<br>101<br>110<br>111                                                                                                                                                      | Same as Far                                                                                                             | Same as Fan            | Same as Far            |  |

| D5                      | Bus<br>Timeout<br>(35ms):<br>0 = enabled<br>1 = disabled                         | Fan 2 Fault | Spin-Up:<br>00 = No spin-up<br>01 = two TACH counts<br>or 0.5s<br>10 = two TACH counts<br>or 1s<br>or 1s<br>or 2s | 0)                          | 0)                          | 0)                          | oeriods):                                                                                                                                                                                                                       |                                                                                                                         |                        |                        |  |

| 90                      | POR:<br>0 = normal<br>1 = reset                                                  | Fan 3 Fault | Spin-Up:<br>00 = No spin<br>01 = two TACH<br>or 0.55<br>10 = two TACH<br>11 = two TACH<br>or 12<br>or 25          |                             |                             |                             |                                                                                                                                                                                                                                 | Speed Range (TACH periods);<br>000 = 1<br>001 = 2<br>010 = 4<br>011 = 8<br>100 = 16<br>110 = 32<br>111 = 32<br>111 = 32 |                        |                        |  |

| 70                      | <u>Run:</u><br>0 = run<br>1 = standby                                            | Fan 4 Fault | Mode:<br>0 = DAC<br>1 = RPM                                                                                       |                             |                             |                             | Speed R                                                                                                                                                                                                                         |                                                                                                                         |                        |                        |  |

| FUNCTION                | Global<br>Configuration                                                          | Fan Fault   | Fan 1<br>Configuration                                                                                            | Fan 2<br>Configuration      | Fan 3<br>Configuration      | Fan 4<br>Configuration      | Fan 1<br>Dynamics                                                                                                                                                                                                               | Fan 2<br>Dynamics                                                                                                       | Fan 3<br>Dynamics      | Fan 4<br>Dynamics      |  |

| POR<br>STATE            | XXX0 0000                                                                        | 0000 1111   | 0000 0XX0                                                                                                         | 0000 0XX0                   | 0000 0XX0                   | 0000 0XX0                   | 0100 1100                                                                                                                                                                                                                       | 0100 1100                                                                                                               | 0100 1100              | 0100 1100              |  |

| REGISTER<br>NO./ADDRESS | ЮО                                                                               | 01h         | ٥Zh                                                                                                               | 03h                         | 04h                         | 05h                         | ୦୦                                                                                                                                                                                                                              | 07h                                                                                                                     | 08h                    | 460                    |  |

| RW                      | RW                                                                               | RM          | WA                                                                                                                | R/W                         | RM                          | R/W                         | R<br>N<br>N                                                                                                                                                                                                                     | RM                                                                                                                      | RM                     | RM                     |  |

## Registers

**Register Map**

www.datasheet4u.com

#### **Register Map (continued)** Full D3 5 В 8 5 D4 D2 Ω 02 Б D5 ВÜ D5 ВЗ В Same as Fan 1 Target Drive Voltage Same as Fan 1 Target Drive Voltage Same as Fan 1 Target Drive Voltage Same as Fan 1 Target TACH Count Same as Fan 1 Target TACH Count Same as Fan 1 Target TACH Count Same as Fan 1 TACH Count Same as Fan 1 Drive Voltage Same as Fan 1 Drive Voltage Same as Fan 1 TACH Count Same as Fan 1 Drive Voltage Same as Fan 1 TACH Count DG 5 D6 ä D 4 D5 D7 D5 2 07 88 D6 88 DG 50 ő D3 5 50 01 D10 D10 6 22 88 $D^2$ 88 Fan 4 Target Drive Voltage Fan 1 Target Drive Voltage Fan 3 Target Drive Voltage Fan 2 Target TACH Count Fan 2 Target Drive Voltage Fan 1 TACH Count Fan 2 TACH Count Fan 3 Target TACH Count Fan 4 Target TACH Count Fan 1 Drive Voltage Fan 4 Drive Voltage Fan 3 TACH Fan 4 TACH Fan 2 Drive Voltage Fan 3 Drive Voltage Fan 1 Target TACH Count FUNCTION Count Count X = Depends on input states at power-up. XXXX XXXX XXXX XXXX XXXX XXXX 0011 1100 0011 1100 XXXX XXXX X000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 0000 X000 0000 X000 0000 1111 1111 1111 1111 1111 1111 1111 1111 1110 0000 0000 0000 0000 0000 0000 0000 0011 1100 0000 0000 0011 1100 0000 0000 X000 000X 1110 0000 1110 0000 1110 0000 0000 0000 0000 0000 POR STATE REGISTER NO./ADDRESS 12h 1Ah 1Bh 1 Ch ę 11h 13h 1<del>4</del>h 17h 18h Чgh ЧŪ 1Eh 20h 21h 22h 23h 25h 26h 27h 28h 29h 2Ah 2Ch 2Eh 2Fh 15h 님 2Bh 2Dh МN М М М М Š М М Š ſ ſ £ ſ £ ſ ſĽ £

**MAX6620**

.datasheet4u.co

## \_\_\_\_\_Register Descriptions

|     |     | Global Configuration Register (00h)—POR = 0000 0XXX                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BIT | R/W | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 7   | R/W | Run:<br>0 = run<br>1 = standby                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 6   | R/W | POR:<br>0 = normal operation<br>1 = reset all registers to POR values<br>This bit automatically resets itself and will always return a 0 when read.                                                                                                                                                                                                                                                                                                                                                                                   |

| 5   | R/W | I <sup>2</sup> C Bus Timeout:<br>0 = enabled<br>1 = disabled<br>The I <sup>2</sup> C interface will reset if SDA is low for more than 35ms.                                                                                                                                                                                                                                                                                                                                                                                           |

| 4   | R/W | <ul> <li>Fans to 100% on failure:</li> <li>0 = if a fan failure is detected, all other fan channels immediately go to full-scale drive voltage to ensure adequate cooling</li> <li>1 = disabled</li> </ul>                                                                                                                                                                                                                                                                                                                            |

| 3   | R/W | Oscillator Selection:<br>Selects on-chip oscillator or 32.768kHz crystal/ceramic resonator. Use crystal if 1% RPM accuracy is required.<br>0 = internal oscillator (default at power-on)<br>1 = external 32.768kHz crystal<br>When switching from the internal oscillator to an external crystal, the MAX6620 operates from the internal<br>oscillator until the crystal oscillator has started up. If the crystal is damaged or the oscillator fails to start,<br>the MAX6620 will continue to operate from the internal oscillator. |

www.datasheet4u.com

| BIT | R/W | FUNCTION                                                         |                                                                                                                                                                                                                                |                                                    |                                                                      |  |  |  |  |  |

|-----|-----|------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------|--|--|--|--|--|

| 2   |     | transactions<br>will go to full-<br>If the watchd<br>previous DA | <b>g:</b><br>, the watchdog monitors SDA and S0<br>between the master and the MAX66<br>-scale drive voltage.<br>og times out and valid I <sup>2</sup> C transacti<br>C value. The master can then progra<br>the normal manner. | 20 within the watchdog<br>ons begin to occur agair | period, all fan output voltages<br>n, operation will resume with the |  |  |  |  |  |

|     | R/W | periodically,                                                    | tchdog function is active, ensure th<br>for example reading a status regist<br>te is set by the state of the WD_STA                                                                                                            | er.                                                | ates to the MAX6620                                                  |  |  |  |  |  |

|     |     | D2:D1                                                            | I <sup>2</sup> C WATCHDOG PERIOD (s)                                                                                                                                                                                           | POR CONDITION                                      | _                                                                    |  |  |  |  |  |

| 1   |     | 00                                                               | Inactive (no watchdog)                                                                                                                                                                                                         | WD_START = GND                                     |                                                                      |  |  |  |  |  |

|     |     | 01                                                               | 2                                                                                                                                                                                                                              | _                                                  |                                                                      |  |  |  |  |  |

|     |     | 10                                                               | 6                                                                                                                                                                                                                              | _                                                  |                                                                      |  |  |  |  |  |

|     |     | 11                                                               | 10                                                                                                                                                                                                                             | WD_START = V <sub>CC</sub>                         |                                                                      |  |  |  |  |  |

|     |     |                                                                  |                                                                                                                                                                                                                                |                                                    |                                                                      |  |  |  |  |  |

|     |     | I <sup>2</sup> C Watchdo                                         | g Status:<br>Insactions occurred within watchdo                                                                                                                                                                                | a pariad                                           |                                                                      |  |  |  |  |  |

| BIT | R/W      | FUNCTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                     |                                                                |             |  |  |  |

|-----|----------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------|----------------------------------------------------------------|-------------|--|--|--|

|     |          | <ul> <li>Fan 4 Fault Status:</li> <li>Indicates which fans have had faults detected. When a fan fault is detected, the drive to the fan is disabled ar the corresponding fault bit is set. The fault bits latch until they are cleared by reading, thus allowing short-term faults to be identified. After a fault status bit is cleared by reading, the corresponding output voltage will remain zero until a Fan_Target Drive Voltage register or Fan_Target TACH Register is written. Writing new target drive voltage or target TACH count will cause drive to be applied to the fan again, at which time a new failure-detection cycle will begin.</li> <li>Fault Conditions Are:</li> </ul> |                                     |                                                                |             |  |  |  |

|     |          | MODE                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | FAN_ DRIVE<br>VOLTAGE REGISTER      | CONDITION                                                      | TIME<br>(s) |  |  |  |

| 7   | R        | DAC                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | Any                                 | TACH count exceeds value of Fan_ Target<br>TACH count          | >1          |  |  |  |

|     |          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                     | Locked rotor asserts                                           |             |  |  |  |