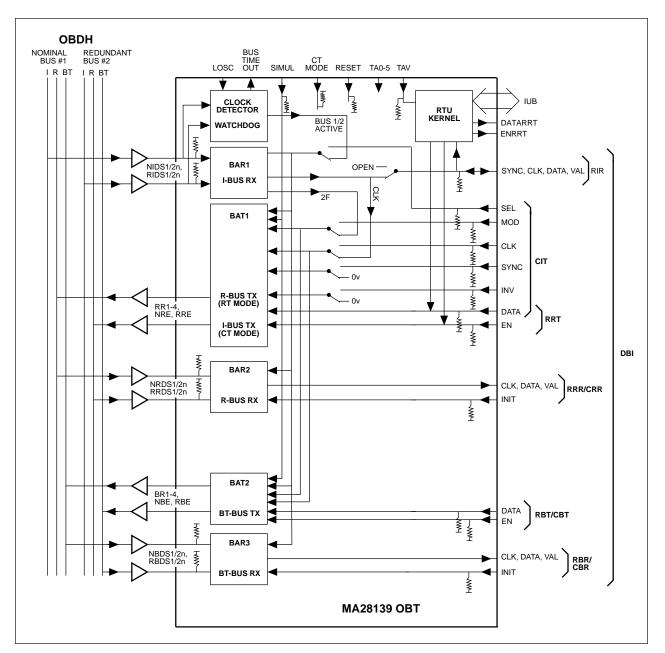

**OBDH Bus Terminal**

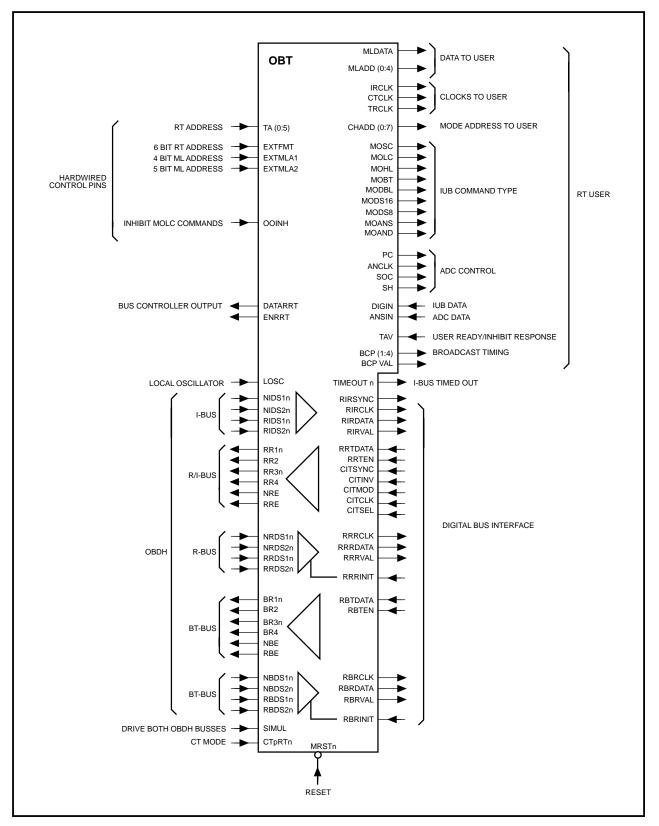

The OBT ASIC will interface any user to the ESA On Board Data Handling bus. Developed under ESA Contract, it conforms to ESA OBDH, Digital Bus Interface and Internal User Bus Standards.

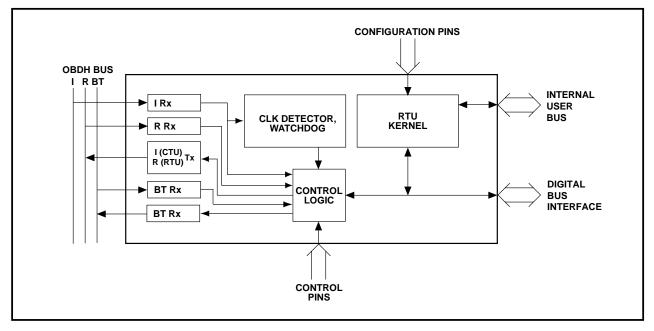

The OBT has 2 separate functions. The first is a 5 channel modem which, on the bus side, provides the digital waveforms necessary to operate the Litton Bus drivers, and receives the outputs of the Litton bus detectors. On the user side, it provides an input / output at Digital Bus Interface level. The second function, internally coupled to the first, provides a multiplexing / demultiplexing function of the DBI signals down to Internal User Bus levels and vectored 16 bit serial register read and write commands (see section 7.2 of ESA standard TTC-B-01). In effect, the second function of the OBT provides the core of an RTU.

The Interrogation and Response bus data streams of the two functions may be either coupled together (in RT mode) or isolated (in CT mode). The device may hence be used as a modem only, an RTU kernel only or as a combined modem and RTU kernel. In RT mode, the Interrogation bus data stream can be observed and the Response bus data from associated devices, such as an MA28138 Remote Bus Interface, can be combined with that from the RTU kernel before being used by the modem circuits to modulate the Response bus. Bi-directional access to the Block Transfer bus is provided in either mode.

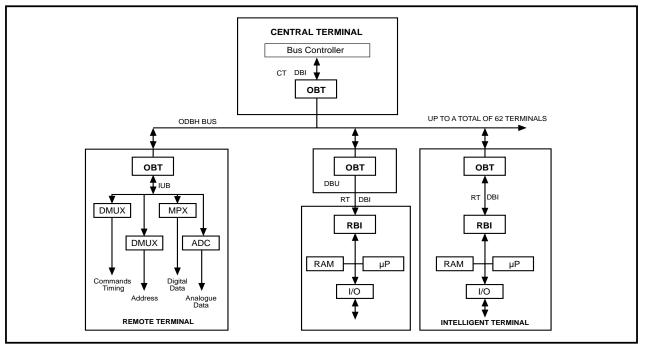

When used to interface a central terminal to the OBDH bus, the OBT should be continuously clocked in order to output timing to all users on the I-bus as dummy interrogations from the CT. Commands and telemetry are normally sent on the I and BT busses whilst responses and telemetry normally return on the R and BT busses.

#### **FEATURES**

- Radiation Hard

- Low Power Consumption

- Single CMOS-SOS ASIC Implementation

- Latch-up Free

- High SEU Immunity

- Fully Compliant with ESA OBDH, IUB, DBI and RBI Specification

- Contains OBDH Bus Modem and RTU Kernel

- Supports Bi-directional Data Transfer on Response and Block Transfer Bus

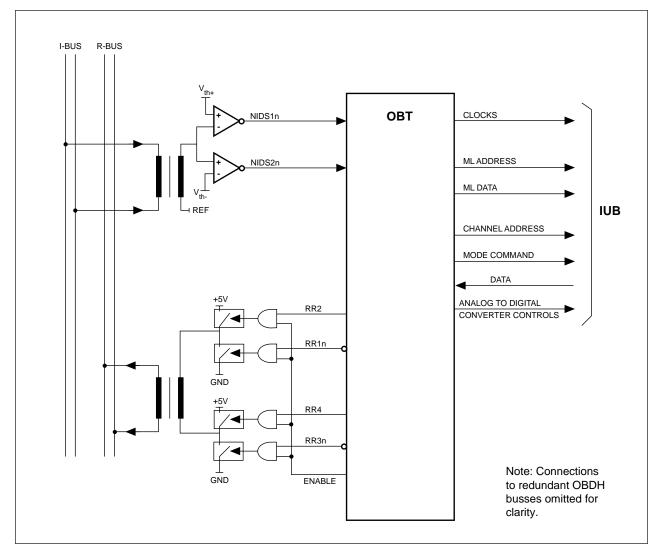

Figure 1: Block Diagram

## **APPLICATION**

**Figure 2: Application**

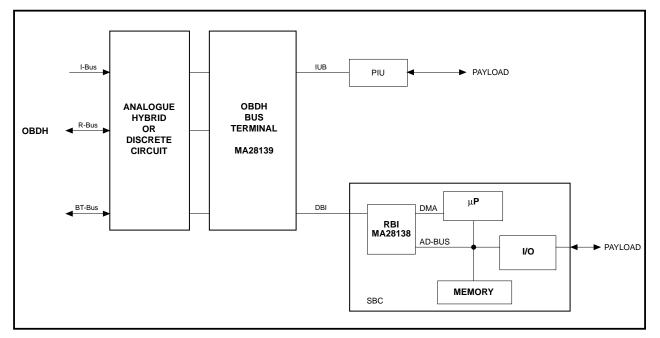

# **PAYLOAD INTERFACES**

The OBT converts the OBDH bus to an Internal User Bus, and a Digital Bus Interface. The OBT can connect OBDH to existing ESA standard payload interfaces such as the MSS PIU (payload interface unit), ICU (intelligent control unit), SBC (single board MIL-STD-1750 computer) or FTC (fault tolerant computer).

The OBT and analogue components/transformers can be integrated in the PIU, ICU, SBC, etc.

#### FUNCTIONAL DESCRIPTION

In RT mode, power up resets the OBT and causes it to deselect both busses. Two watchdog counters monitor the Nominal I-bus and the Redundant I-bus. If either bus becomes active, that bus will be selected. If the selected bus stops, the OBT watchdog times out and resets both the OBT and the user. If both busses become active, the Nominal bus will be selected in preference to the Redundant one. A change in bus selection will always result in the OBT and the user being reset. Responses from the user are always returned on the selected bus. Setting 'SIMUL' high causes both BATs to drive both the Nominal and the Redundant busses irrespective of the current bus selection. The time-out period may be set to any desired number of bits by varying the 'LOSC' frequency. The OBT derives all timing from, and is synchronous with, the selected I-bus. The OBT demodulates the I-bus to the DBI and decodes commands to the IUB.

The CTpRTn mode pin causes the modem circuits and the RTU Kernel to be either cascade or isolated. If CTpRTn is low (RT mode), the RIRSYNC, CLK, DATA and VAL signals are routed to the RTU Kernel and the associated pins act as outputs; responses from the RTU Kernel are ORed with those from the external RRTDATA and RRTEN inputs and can be independently monitored on the DATARRT and ENRRT pins. In this mode any reset caused by the Clock Detector watchdogs is also combined with the power up reset input.

If CTpRTn is high (CT mode), the modem and RTU Kernel functions are isolated to permit the device to be used as either a modem within the CTU or an RTU Kernel interfacing to an external modem where the RIRSYNC, CLK, DATA and VAL pins act as inputs. The right-hand multiplexer bank is switched to the upper position so that the CT drives the OBDH via the CIT and CBT (if used) pins and receives responses/telemetry via the CRR and CBR (if used) pins. Note: in CT mode, BAT1 must be connected to the l-busses.

In RT mode, the CITSEL, MOD, CLK, SYNC and INV pins are disabled and the clocks are supplied by the I-bus BAR in response to the selected bus. In CT mode, the Clock Detector is functional and drives the TIMEOUTn pin but is unable to cause internal reset on time-out; in this mode the CT must supply all clocks and select the operational bus.

| Functional Signal                        | CT Mode Source<br>(CTpRTn = '1') | RT Mode Source<br>(CTpRTn = '0')        |

|------------------------------------------|----------------------------------|-----------------------------------------|

| BAT1, 2 modulation clock                 | CITMOD input pin                 | Recovered R2F                           |

| BAT1, 2 data clock                       | CITCLK input pin                 | Recovered RIRCLK                        |

| BAT1 data input                          | RRTDATA input pin                | RRTDATA OR DATARRT (RTU Kernel)         |

| BAT1 tx enable                           | '1'                              | RRTEN OR DATAEN (RTU Kernel)            |

| BAT1 sync code tx enable                 | CITSYNC input pin                | ·0'                                     |

| BAT1 bit invalidate tx enable            | CITINV input Pin                 | ·0'                                     |

| BAT1, 2 bus selection                    | CITSEL and SIMUL input pins      | Detected active bus and SIMUL input pin |

| BAT2 data input                          | RBTDATA input Pin                | RBTDATA input pin                       |

| BAT2 tx enable                           | RBTEN input pin                  | RBTEN input pin                         |

| BAT1, 2, BAR1, 2, 3 reset                | MRSTn input pin                  | TIMEOUTn AND MRSTn input pin            |

| RIRSYNC, CLK, DATA,<br>VAL pin direction | outputs                          | inputs                                  |

| BAT/BAR and RTU Kernel coupling          | separated                        | coupled                                 |

The changes depending upon selection of RT mode or CT mode with the CTpRTn pin are defined in the table below:

Figure 4: Architecture

**Note:** Switches in lower position - RT mode Switches in upper position - CT mode

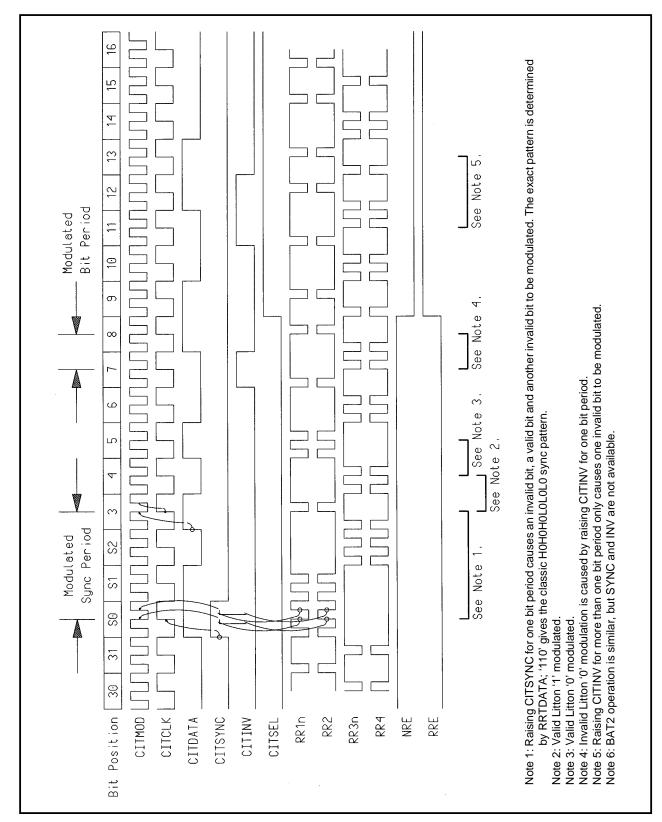

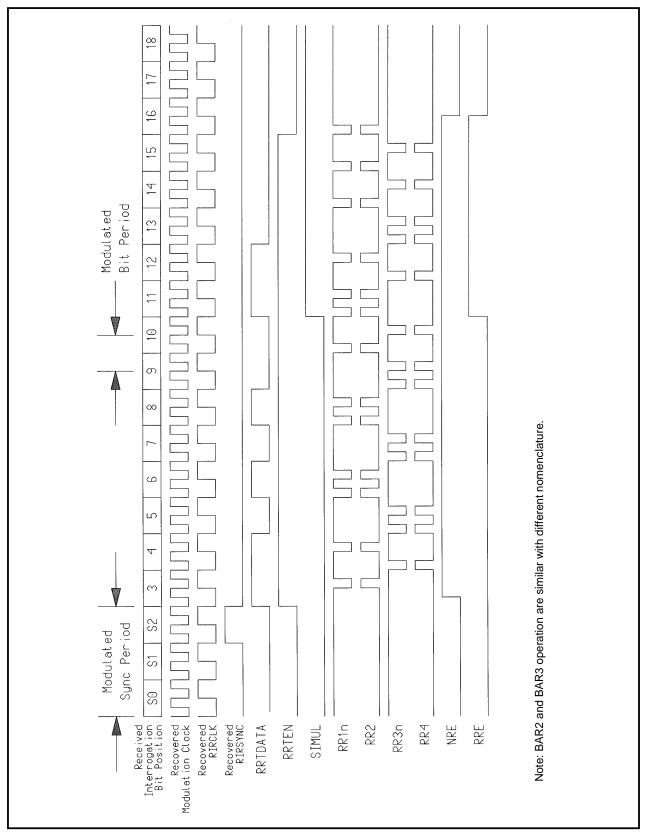

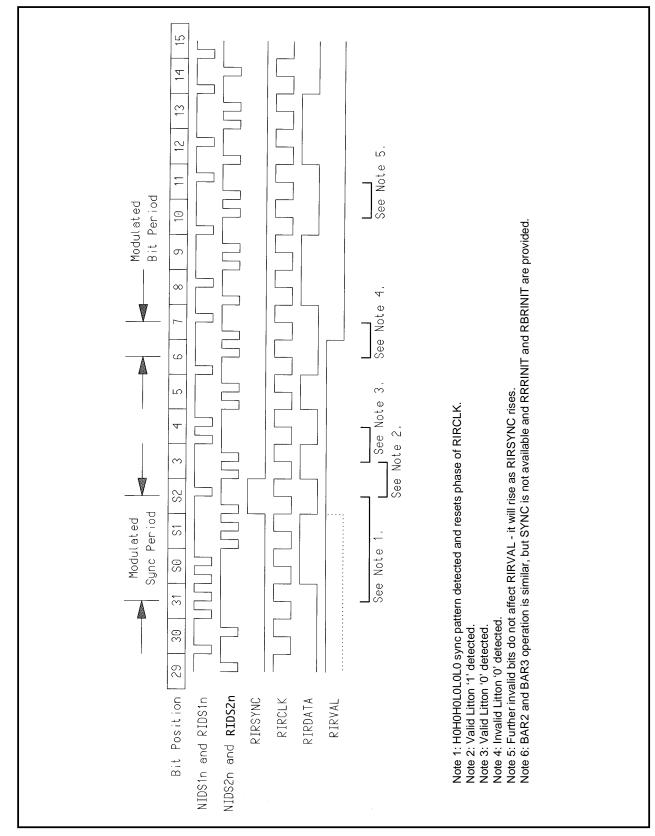

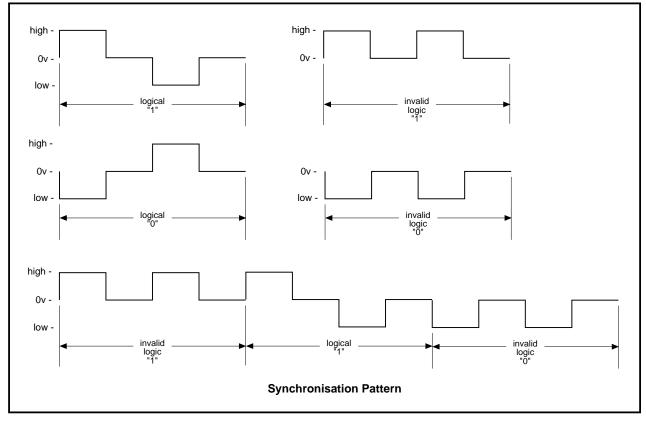

**MODEM Modulation Waveforms** are compliant with ESA document THB/Apo/KZ/1386/av. Waveforms indicating the operation of BAT1, 2 and BAR1, 2, 3 in both the CT and RT modes are shown in Figures 5 to 8.

Figure 5: CT Mode Bus Adaptor Transmitter Waveforms

Figure 6: RT Mode Bus Adaptor Transmitter Waveforms

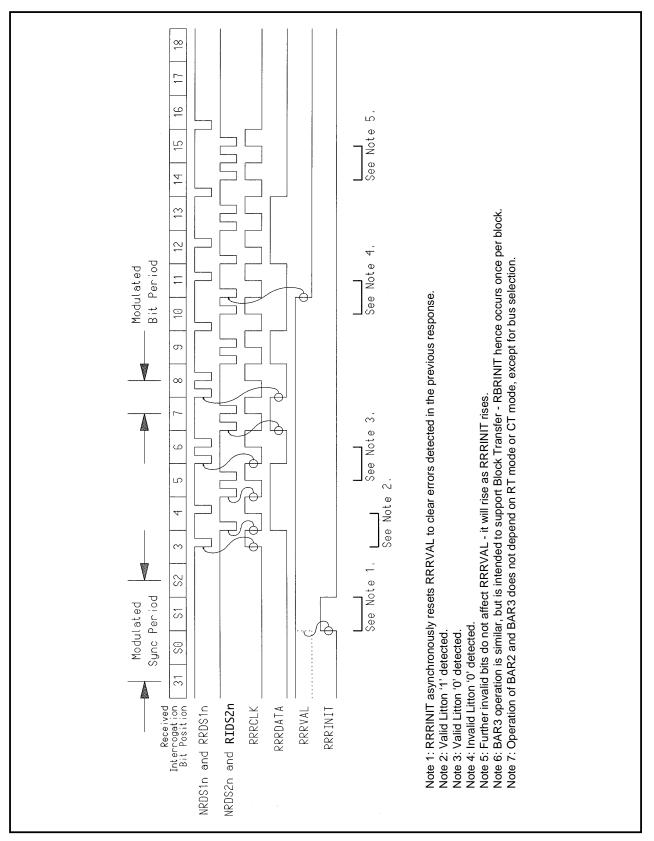

Figure 8: BAR2 Bus Adaptor Receiver Waveforms

## **CLOCK DETECTOR OPERATION**

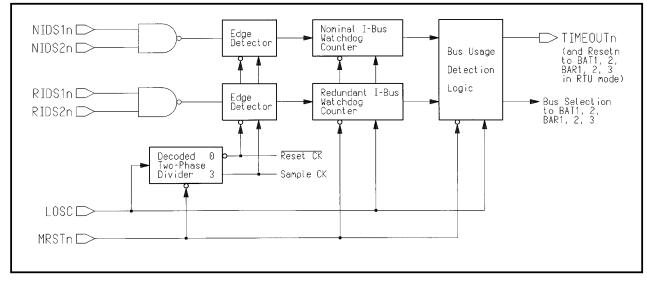

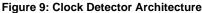

The Clock Detector architecture is shown in Figure 9; a separate channel is essentially provided for each of the Nominal and Redundant Interrogation busses. Associated waveforms are shown in Figure 10.

Each channel contains an Edge Detector and a 5-bit Watchdog Counter which respond only to high-to-low transitions on their respective Interrogation bus DS1n inputs. A common Bus Usage Detection circuit is used to generate timeout pulses (used for internal and external reset) and bus selection signals from the results of the watchdogs.

The local oscillator input, LOSC, is divided and decoded to generate an active low reset and an active high sample clock. When applied to both input Edge Detectors, these signals permit input high-to-low transitions to be detected for one LOSC cycle in every two (between the reset  $\downarrow$  and sample clock  $\uparrow$ ). Once such transitions have been detected by a sample clock, the associated watchdog counter is reset. The MSB of each watchdog counter is used as an indication of its bus's status - active or inactive. Should the watchdog counter overflow (i.e. its MSB be set to 1), the associated bus will be considered inactive.

The status of the Nominal and Redundant Interrogation busses is used to determine internal bus selection for the modulation of Response and Block Transfer data in the device's RT mode. If neither bus is considered active, the TIMEOUTn pin will be held low and RT mode reception of all 3 busses will be inhibited. If one bus is considered active, RT mode reception will occur on the same set of bus circuits (redundancy) as the active Interrogation bus. If both busses are considered active, RT mode reception from the Nominal set of bus circuits will be performed. RT mode transmission will always occur on the same set of bus circuits (redundancy) as selected for reception unless the SIMUL pin is held high, in which case transmission will occur simultaneously on both the Nominal and Redundant busses. Both watchdog counters are fully set at power up to mark both busses as inactive - in this way, a missing LOSC input will not cause inactive busses to be deemed active.

For a single detected input transition, 17.5 to 18.5 LOSC cycles will elapse before the relevant bus is considered inactive. If near-instantaneous Nominal-to-Redundant or Dual-to-Redundant bus handover occurs, the change-over will be delayed by 18 to 19 LOSC cycles, in order to preserve the priority of the Nominal bus. If near-instantaneous Redundant-to-Nominal or Redundant-to-Dual bus handover occurs, the change-over will occur after 1.5 to 2.5 LOSC cycles since the Nominal bus takes priority. In either of these cases, a 1 LOSC cycle TIMEOUTn pulse is always generated to ensure that internal reset occurs.

The frequency of the local oscillator may be varied to make the nominal time-out period of 17.5 LOSC cycles correspond to any desired number of (missing) bits on the Interrogation bus. Variation of the duty cycle does not vary the time-out period. After 16 LOSC cycles without detected input transitions, the associated watchdog times-out and is detected on the next LOSC  $\uparrow$  edge; the generation of a TIMEOUTn pulse and reset are then inevitable.

For proper Clock Detector operation, (at least) one high-tolow input transition must be detected within a period of 16 LOSC cycles of the last such detection, but transitions made during alternate LOSC cycles (the phase is difficult to predict) will not be detected. Local oscillator clock signals which are harmonically-related to the modulation clock by an integer ratio are thus a cause for concern, although this problem is perhaps only likely to occur in experimental set-ups.

Figure 10: MA28139 Clock Detector Operation

The requirement to respect set-up and hold times for the capture of the Edge Detector outputs by the LOSC high-to-low transition means that LOSC signals which are harmonically-related to the Litton modulation clock but whose phase can not be controlled can never be guaranteed to provide reliable operation.

For asynchronous local oscillator signals, there will be no concern if we are simply able to place two or more Litton DSn high-to-low edges into each LOSC cycle, so that:

$\tau_{\text{MOD}} \leq \tau_{\text{LOSC}} \text{ - } t_{\text{SU}} \text{ - } t_{\text{HOLD}}$

and the time-out period of 16  $\tau_{LOSC}$  is hence approximately 8 bit periods or more.

However, suppose that the periods of the modulation clock and the local oscillator clock are such that the relationship between them is:

$\tau_{MOD} = m \tau_{LOSC}$

where m is a positive integer.

In order to respect the setup and hold times,  $t_{\text{SU}}$  +  $t_{\text{HOLD}}$  respectively, between the DSn  $\downarrow$ , and LOSC  $\downarrow$  edges, it is necessary to avoid such harmonic relationships; it can be shown that around these spot frequencies it is necessary to ensure that either:

$\label{eq:total_states} \begin{array}{l} w \ \tau_{MOD} \geq x \ \tau_{LOSC} + t_{SU} + t_{HOLD} \\ \text{or} \\ y \ \tau_{MOD} \leq z \ \tau_{LOSC} \text{-} t_{SU} \text{-} t_{HOLD} \end{array}$

where the integer constants w, x, y and z are given in the table below.

Since two modulation clock cycles occur per bit, the timeout period at these harmonics will then be:

16  $\tau_{LOSC} \approx$  16  $\tau_{MOD}$  / m  $\approx$  8 / m bit periods.

| m  | w  | x  | у  | Z  | Approx. time-out<br>period (bit periods) |

|----|----|----|----|----|------------------------------------------|

| 1  | 15 | 15 | 17 | 17 | 8                                        |

| 2  | 7  | 15 | 8  | 15 | 4                                        |

| 3  | 5  | 15 | 5  | 15 | 2.67                                     |

| 4  | 3  | 13 | 4  | 15 | 2                                        |

| 5  | 3  | 15 | 3  | 15 | 1.6                                      |

| 6  | 2  | 13 | 2  | 11 | 1.33                                     |

| 7  | 1  | 7  | 1  | 7  | 1.14                                     |

| 8  | 1  | 9  | 2  | 15 | 1                                        |

| 9  | 1  | 9  | 1  | 9  | 0.88                                     |

| 10 | 1  | 11 | 1  | 9  | 0.8                                      |

| 11 | 1  | 11 | 1  | 11 | 0.73                                     |

| 12 | 1  | 13 | 1  | 11 | 0 67                                     |

| 13 | 1  | 13 | 1  | 13 | 0.62                                     |

| 14 | 1  | 15 | 1  | 13 | 0.57                                     |

| 15 | 1  | 15 | 1  | 15 | 0.53                                     |

In summary, slow local oscillator clocks which cause relatively long timeout periods  $\geq 8$  bit periods are not considered a problem; very long time-outs can be reliably implemented. For shorter time-out periods, however, it is necessary to avoid harmonic relationships between the Litton modulation clock and the local oscillator. The simplest practical method for avoiding such relationships would be to arrange for the ratio

$n = \tau_{MOD} / \tau_{LOSC}$

to have a half-integer value such that n = 0.5, 1.5, 2.5, ...using an independent crystal oscillator if necessary.

#### **OBDH / IUB INTERFACE**

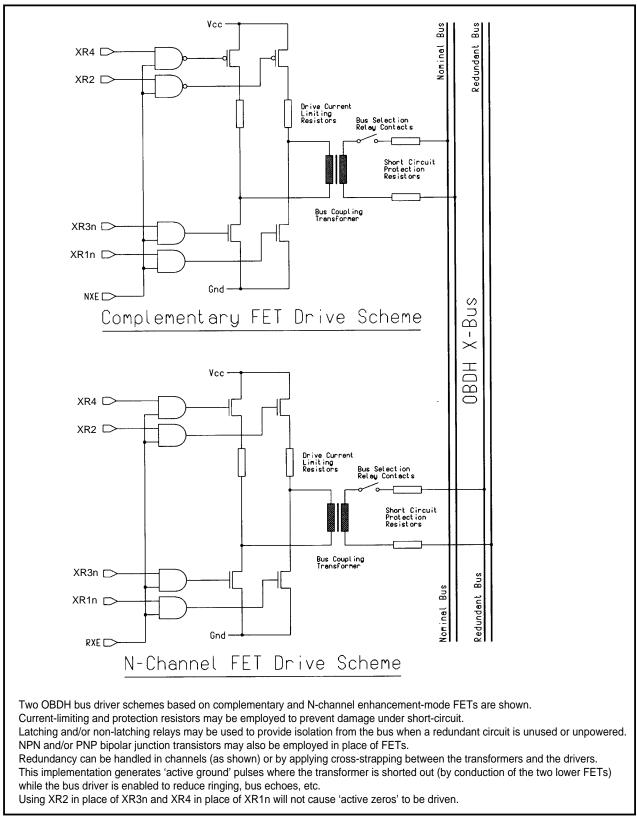

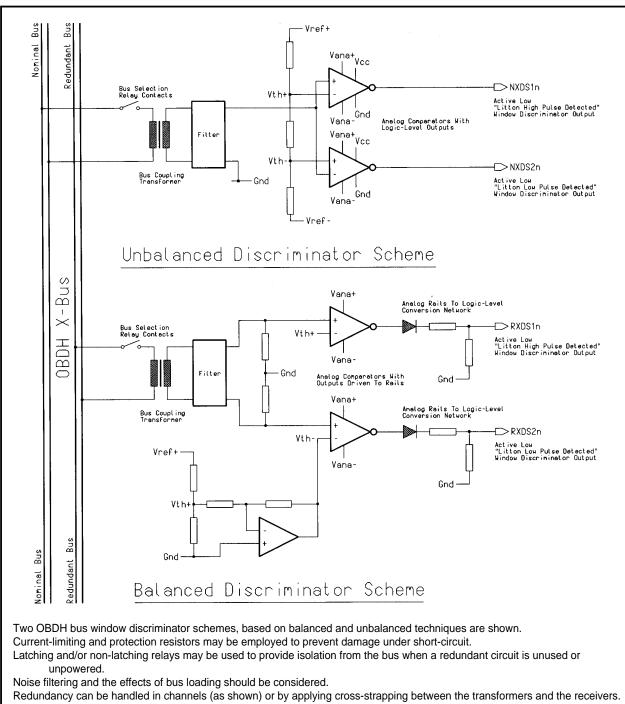

The Central Terminal Unit controls timing, commands and telemetry to all subsystems on the OBDH bus. ESA TTC-B-01 specifies the OBDH to be 2 redundant sets (Nominal and Redundant) of 2 twisted pairs (Interrogation and Response bus) plus an optional redundant 3rd twisted pair (Block Transfer bus), Litton modulated (self clocking with parity on each bit), balanced transformer coupled for less than 1 error in 100 million bits on a 25 metre bus. The data rate is nominally 500K Bits/sec although the chip itself supports up to 5MBits/ sec. The OBT is transformer coupled with adjustable reference and threshold levels as shown below. Litton more positive than V<sub>th+</sub> makes discriminator signal NIDS1n low. Litton more negative than V<sub>th-</sub> makes NIDS2n low. OBT RR1n, RR2, RR3n, RR4 control 4 switches which drive the bus with bipolar Litton code when enabled. For clarity redundancy is not shown below:

TTC-B-01 also specifies the IUB. The OBT supplies specified clocks, memory load address for ML data (or channel address for mode command) and responds on the R bus with a 13 zeroes response as acknowledgement. If the command requires data aquisition, the OBT responds with a 13 or 21 bit response containing 8 or 16 bits (respectively) of user data, controlling external ADC as required.

Figure 11: OBDH to IUB interface

#### **RTU KERNEL PROTOCOL VIOLATIONS**

Some commands to the RTU Kernel cannot be completed within one Interrogation period (or "slot") because of the need to provide a slow external interface as defined in ESA standard TTC-B-01. These are commands for 16-bit Digital Serial Acquisition (S16) and 16-bit Memory Load (ML). In addition, it is also possible to inhibit On/Off commands by pin configuration.

Consequently:

- a Memory Load command cannot be followed by another Memory Load command in the next Interrogation; the second command of such a sequence will be ignored,

- a 16-bit Digital Serial Acquisition (S16) cannot be followed by another acquisition or command in the next Interrogation; the second command of such a sequence will be ignored,

- a Long On/Off command will be ignored if the On/Off command Inhibit input pin, OOINH, is high.

Note that in all MODE Dependent Command and Acquisition Interrogations, bits 23 to 30 of the Interrogation are output as an 8 bit channel address on CHADD(0:7). ESA standard TTC-B-01, p.110 specifies a 7 bit channel address in bits 27 to 29, leaving bit 30 as Reserved. For complete compliance with this standard, CHADD(7) should be disregarded and CHADD(0:6) only should be used.

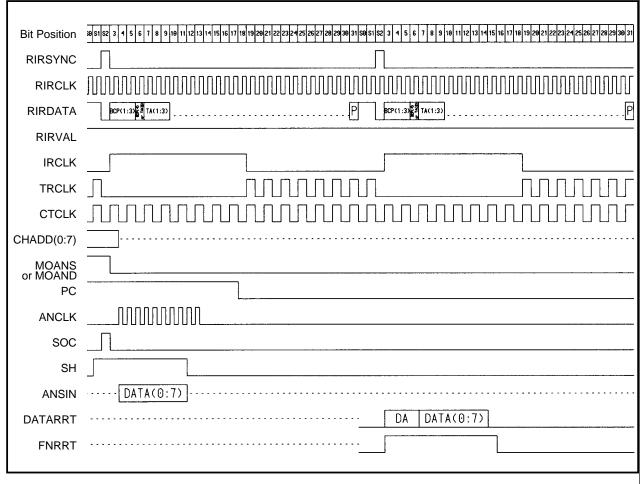

The signals generated by the RTU Kernel during 8-bit Single-Ended and 8-bit Double-Ended Analog Data Acquisitions are intended for connection to an 8-bit serial ADC module. The outputs PC, ANCLK, SOC and SH are intended to provide ADC power control, conversion clock, start of conversion pulse and sample/hold control respectively.

RTU Kernel BroadCast Pulse and BCP Validity Waveforms are shown in Figure 12.

RTU Kernel Memory Load Command Waveforms are shown in Figure 13.

RTU Kernel MODE Dependent Command and Acquisition Waveforms are shown in Figures 14 - 17.

#### **RTU KERNEL MODE DEFINITIONS**

The mode field contained in bits 19 to 22 of the Interrogation is decoded during acquisition commands to drive one of the MOSC, MOLC, MOHL, MOBT, MODBL, MODS8, MODS16, MOANS or MOAND outputs. Mode decoding is an extension of that defined in ESA standard TTC-B-01 Table 7.1 and is shown in Table 1 below:

| Mode Code |        |        |        | Associated                                 |            |

|-----------|--------|--------|--------|--------------------------------------------|------------|

| Bit 19    | Bit 20 | Bit 21 | Bit 22 | Function                                   | Output Pin |

| 0         | 0      | 0      | 0      | Unused                                     | -          |

| 0         | 0      | 0      | 1      | Short Switch Closure On/Off Command        | MOSC       |

| 0         | 0      | 1      | 0      | Long Switch Closure On/Off Command         | MOLC       |

| 0         | 0      | 1      | 1      | High Power Switch Closure On/Off Cmd       | MOHL       |

| 0         | 1      | 0      | 0      | Unused                                     | -          |

| 0         | 1      | 0      | 1      | Unused                                     | -          |

| 0         | 1      | 1      | 0      | Unused                                     | -          |

| 0         | 1      | 1      | 1      | Block Transfer Command                     | MOBT       |

| 1         | 0      | 0      | 0      | 8-bit Digital Bi-Level Data Acquisition    | MODBL      |

| 1         | 0      | 0      | 1      | Unused                                     | -          |

| 1         | 0      | 1      | 0      | 16-bit Serial Digital Data Acquisition     | MODS16     |

| 1         | 0      | 1      | 1      | 8-bit Serial Digital Data Acquisition      | MODS8      |

| 1         | 1      | 0      | 0      | 8-bit Single-Ended Analog Data Acquisition | MOANS      |

| 1         | 1      | 0      | 1      | Unused                                     | -          |

| 1         | 1      | 1      | 0      | 8-bit Double-Ended Analog Data Acquisition | MOAND      |

| 1         | 1      | 1      | 1      | Unused                                     | -          |

**Table 1: RTU Kernel Mode Definitions**

| Bit Position          | n 588 51 528 3 4 5 6 7 8 9 119 11 12 13 14 15 16 17 18 19 28 21 22 23 24 25 26 27 28 29 38 31 58 51 52 3                                                                                                                                                                                                                                   | 4 5 6 7 8 9 19 11 12 13 14 15 16 17 18 19 29 21 22 23 24 25 26 27 28 29 38 31 |

|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------|

| RIRSYNC               | ;                                                                                                                                                                                                                                                                                                                                          |                                                                               |

| RIRCLK                |                                                                                                                                                                                                                                                                                                                                            |                                                                               |

| RIRDATA               |                                                                                                                                                                                                                                                                                                                                            | P(1:3)                                                                        |

| RIRVAL                | -                                                                                                                                                                                                                                                                                                                                          |                                                                               |

| BCP(1:4)              | BCP(1:4)                                                                                                                                                                                                                                                                                                                                   | BCP(1:4)                                                                      |

| BCPVAL                |                                                                                                                                                                                                                                                                                                                                            |                                                                               |

|                       |                                                                                                                                                                                                                                                                                                                                            |                                                                               |

| Bit Position          | 1 30[51[52] 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 58 51 52 3                                                                                                                                                                                                                                     | 4 5 6 7 8 9 18 11 12 13 14 15 16 17 18 19 28 21 22 23 24 25 26 27 28 29 38 31 |

| RIRSYNC               | ;                                                                                                                                                                                                                                                                                                                                          |                                                                               |

| RIRCLK                |                                                                                                                                                                                                                                                                                                                                            |                                                                               |

| RIRDATA               |                                                                                                                                                                                                                                                                                                                                            | (1:3 <b>4</b>                                                                 |

| RIRVAL                |                                                                                                                                                                                                                                                                                                                                            |                                                                               |

| BCP(1:4)              | ) BCP(1:4) E                                                                                                                                                                                                                                                                                                                               | 3CP(1:4)                                                                      |

| BCPVAL                |                                                                                                                                                                                                                                                                                                                                            |                                                                               |

|                       |                                                                                                                                                                                                                                                                                                                                            |                                                                               |

| (1) =                 | = BCP(4) or TA(0)                                                                                                                                                                                                                                                                                                                          |                                                                               |

| if<br>Note 2: (F<br>m | Bit 6 of the Interrogation will be interpreted as BCP(4) if (EXTFM<br>f (EXTFMT = 1), the BCP (4) output will be 0 and bit 6 will be inter<br>(RIRVAL = 0) (presumably because of bad Interrogation length o<br>nodem), bad received parity in bit 31 of the Interrogation or wron<br>nterrogation to be rejected and will set BCPVAL = 0. | erpreted as TA(0).<br>r received Litton coding errors detected by the         |

|                       | - ,                                                                                                                                                                                                                                                                                                                                        |                                                                               |

Figure 12: BroadCast Pulse and BCP Validity Waveforms

| Bit Position 585152 3 4 5 6 7 8 9 18 11 12 13 14 15 16 17 18 19 28 21 22 23 24 25 26 27 28 29 38 31 58 51 52 3 4 5 6 7 8 9 18 11 12 13 14 15 16 17 18 19 28 21 22 23 24 25 26 27 28 29 38 31 58 51 52 3 4 5 6 7 8 9 18 11 12 13 14 15 16 17 18 19 28 21 22 23 24 25 26 27 28 29 38 31 |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

| RIRDATA BOP(1:3) TA(1:3) HAA MEMORY LOAD DATA(0:15) P BOP(1:3) TA(1:3) Further Memory Lead Interropetion to game device P                                                                                                                                                             |

| RIRVAL                                                                                                                                                                                                                                                                                |

| IRCLK                                                                                                                                                                                                                                                                                 |

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

| MLADD(0:4) MEMORY LOAD ADDRESS(0:4)                                                                                                                                                                                                                                                   |

| MLDATA                                                                                                                                                                                                                                                                                |

| DATARRT                                                                                                                                                                                                                                                                               |

| ENRRT                                                                                                                                                                                                                                                                                 |

| Bit Position                                                                                                                                                                                                                                                                          |

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

| RIRDATA BCP(1:3) TA(1:3) Memory Loed Interroget ion now possible P BCP(1:3) TA(1:3)                                                                                                                                                                                                   |

| RIRVAL                                                                                                                                                                                                                                                                                |

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

|                                                                                                                                                                                                                                                                                       |

| MLADD(0:4)                                                                                                                                                                                                                                                                            |

| MLDATA 7> MEMORY LOAD DATA(8) MEMORY LOAD DATA(9:15)                                                                                                                                                                                                                                  |

| DATARRT                                                                                                                                                                                                                                                                               |

| ENRRT                                                                                                                                                                                                                                                                                 |

| (1) = BCP(4) or TA(0)<br>(2) = TA(4:5) or MLA(0:1)                                                                                                                                                                                                                                    |

| Note 1: One Memory Load command takes 2 Interrogations to complete. Consecutive Memory Load commands are hence not                                                                                                                                                                    |

| possible and form a protocol violation. The second Memory Load command of such a sequence will be rejected.<br>Note 2: For a Memory Load command to be decoded, the evaluated Memory Load Address must be non-zero. An evaluated                                                      |

| Memory Load Address of zero implies data aquisition.<br>Note 3: The Memory Load Address which is evaluated for decoding and addressing usage may vary from 3 to 5 bits.                                                                                                               |

| If (EXTMLA1 = 1) and (EXTMLA2 = 0), the Memory Load Address field is extended to 4 bits and bit 11of the Interrogation will be treated as MLA(1).                                                                                                                                     |

| If (EXTMLA2 = 1), the Memory Load Address field is extended to 5 bits and bits 10 and 11of the Interrogation will be treated as MLA(0:1).                                                                                                                                             |

| Any Interrogation bits treated as Extended Memory Load Address bits will not be treated as Terminal Address bits; this facility is intended for 2x or 4x size expansion provided that up to 4 consecutive Terminal Addresses can be used.                                             |

| Note 4: The Memory Load command response is always 13-zeros.                                                                                                                                                                                                                          |

Figure 13: Memory Load Command Waveforms

| Bit Position      | sajstisz 3 4 5 6 7 8 9 10/11/12/13/14/15/16/17/18/19/20/21/22/23/24/25/25/27/28/29/30/31/50/51/52 3 4 5 6 7 8 9 10/11/12/13/14/15/16/17/18/19/20/21/22/23/24/25/25/27/28/29/30/31/5                                                                                                            |

|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RIRSYNC           |                                                                                                                                                                                                                                                                                                |

| RIRCLK            |                                                                                                                                                                                                                                                                                                |

| RIRDATA           | BCP(1:3)     Minimum LA(2:1)     DA     MODE     CHANNEL     P     BCP(1:3)     Monoru Lood. Accousing in the provide process is given to closure                                                                                                                                              |

| RIRVAL            |                                                                                                                                                                                                                                                                                                |

| IRCLK             |                                                                                                                                                                                                                                                                                                |

| TRCLK             |                                                                                                                                                                                                                                                                                                |

| CTCLK             |                                                                                                                                                                                                                                                                                                |

| CHADD(0:7)        | CHANNEL(0:7)                                                                                                                                                                                                                                                                                   |

| MODS8 or<br>MODBL |                                                                                                                                                                                                                                                                                                |

| DIGIN             | DATA(0:7)                                                                                                                                                                                                                                                                                      |

| DATARRT           |                                                                                                                                                                                                                                                                                                |

| ENRRT             |                                                                                                                                                                                                                                                                                                |

| Bit Position      | x8 51 52 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 28 21 22 23 24 25 26 27 28 29 39 31 98 51 52 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 28 21 22 23 24 25 26 27 28 29 39 31                                                                                                              |

| RIRSYNC           | Π                                                                                                                                                                                                                                                                                              |

| RIRCLK            |                                                                                                                                                                                                                                                                                                |

| RIRDATA           | β0P(1:3)≰ <sup>3</sup> / <sub>2</sub> Tλ(1:3)                                                                                                                                                                                                                                                  |

| RIRVAL            |                                                                                                                                                                                                                                                                                                |

| IRCLK             |                                                                                                                                                                                                                                                                                                |

| TRCLK             |                                                                                                                                                                                                                                                                                                |

| CTCLK             |                                                                                                                                                                                                                                                                                                |

| CHADD(0:7)        |                                                                                                                                                                                                                                                                                                |

| MODS8 or<br>MODBL |                                                                                                                                                                                                                                                                                                |

| DIGIN             |                                                                                                                                                                                                                                                                                                |

| DATARRT           | DA DATA(0:7)                                                                                                                                                                                                                                                                                   |

| ENRRT             | ·····                                                                                                                                                                                                                                                                                          |

|                   | y acquisition command to be decoded, the evaluated Memory Load Address must be zero. An evaluated Memory Load<br>ss of non-zero does not imply data acquisition.                                                                                                                               |

| Note 2: The Me    | For hor 2ero does not many data acquisitor.<br>emory Load Address which is evaluated for decoding and addressing usage may vary from 3 to 5 bits.<br>MLA1 = 1 and $(EXTMLA2 = 0)$ , the Memory Load Address field is extended to 4 bits and bit 11 of the Interrogation will be                |

| treated           | as MLA(1).<br>MLA2 = 1), the Memory Load Address field is extended to 5 bits and bits 10 and 11of the Interrogation will be                                                                                                                                                                    |

| Any Int           | as MLA(0:1).<br>terrogation bits treated as Extended Memory Load Address bits will not be treated as Terminal Address bits; this facility is                                                                                                                                                   |

| Note 3: The 8-    | ed for 2x or 4x size expansion provided that up to 4 consecutive Terminal Addresses can be used.<br>bit Digital Serial and 8-bit Digital Bi-Level Acquisition command responses are always 13 bits in length; the Destination<br>as is simply copied from the Interrogation into the Response. |

|                   |                                                                                                                                                                                                                                                                                                |

| Bit Position                                           | 568 511 52 3 4 5 6 7 8 9 18 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 50 51 52 3 4 5 6 7 8 9 18 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 30 31 5                                                                                                                                                                                                                                                                                                                                  |

|--------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RIRSYNC                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RIRCLK                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RIRDATA                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RIRVAL                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IRCLK                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TRCLK                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CTCLK                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CHADD(0:7)                                             | CHANNEL(0:7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| MODS16                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DIGIN                                                  | DATA(0:7)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| DATARRT                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| ENRRT                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Bit Position                                           | x8 51 52 3 4 5 6 7 8 9 18 11 12 13 14 15 16 17 18 19 28 21 22 23 24 25 26 27 28 29 38 31 58 51 52 3 4 5 6 7 8 9 18 11 12 13 14 15 16 17 18 19 28 21 22 23 24 25 26 27 28 29 38 31                                                                                                                                                                                                                                                                                                                                      |

| RIRSYNC                                                | $\square \qquad \square$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| RIRCLK                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| RIRDATA                                                | BCP(1:3) ฐ TA(1:3) mutes Any ecquisition now possible P BCP(1:3) ฐ TA(1:3) mutes                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| RIRVAL                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IRCLK                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| TRCLK                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CTCLK                                                  |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| CHADD(0:7)                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| MODS16                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| DIGIN                                                  | DATA(8:15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| DATARRT                                                | DA DATA(0:7) DATA(8:15)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| ENRRT                                                  | ······                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Closure<br>will be re<br>Note 2: For any a             | acquisition command to be decoded, the evaluated Memory Load Address must be zero. An evaluated Memory Load                                                                                                                                                                                                                                                                                                                                                                                                            |

| Note 3: The Men<br>If (EXTM<br>treated a               | of non-zero does not imply data acquisition.<br>nory Load Address which is evaluated for decoding and addressing usage may vary from 3 to 5 bits.<br>LA1 = 1) and (EXTMLA2 = 0), the Memory Load Address field is extended to 4 bits and bit 11 of the Interrogation will be<br>is MLA(1).                                                                                                                                                                                                                             |

| treated a<br>Any Inter<br>intended<br>Note 4: The 16-b | LA2 = 1), the Memory Load Address field is extended to 5 bits and bits 10 and 11 of the Interrogation will be<br>s MLA(0:1).<br>rogation bits treated as Extended Memory Load Address bits will not be treated as Terminal Address bits; this facility is<br>for 2x or 4x size expansion provided that up to 4 consecutive Terminal Addresses can be used.<br>it Digital Serial Acquisition command response is always 21 bits in length; the Destination Address is simply<br>om the Interrogation into the Response. |

Figure 15: 16-Bit Digital Serial Acquisition Waveforms

| Bit Position                                                        | 589 51 52 3 4 5 6 7 8 9 19 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 38 31 589 51 52 3 4 5 6 7 8 9 10 11 12 13 14 15 16 17 18 19 20 21 22 23 24 25 26 27 28 29 38 31                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|---------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RIRSYNC                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RIRCLK                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| RIRDATA                                                             | BCP(1:3) TA(1:3) TA(1: |

| RIRVAL                                                              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| IRCLK                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |