#### **General Description**

The MAX5134-MAX5137 is a family of pin-compatible and software-compatible 16-bit and 12-bit DACs. The MAX5134/MAX5135 are low-power, quad 16-/12-bit, buffered voltage-output, high-linearity DACs. The MAX5136/MAX5137 are low-power, dual 16-/12-bit, buffered voltage-output, high-linearity DACs. They use a precision internal reference or a precision external reference for rail-to-rail operation. The MAX5134–MAX5137 accept a wide +2.7V to +5.25V supply-voltage range to accommodate most low-power and low-voltage applications. These devices accept a 3-wire SPITM-/QSPITM-/MICROWIRETM-/DSP-compatible serial interface to save board space and reduce the complexity of optically isolated and transformer-isolated applications. The digital interface's double-buffered hardware and software LDAC provide simultaneous output updates. The serial interface features a READY output for easy daisy-chaining of several MAX5134-MAX5137 devices and/or other compatible devices. The MAX5134-MAX5137 include a hardware input to reset the DAC outputs to zero or midscale upon power-up or reset, providing additional safety for applications that drive valves or other transducers that need to be off during power-up. The high linearity of the DACs makes these devices ideal for precision control and instrumentation applications. The MAX5134-MAX5137 are available in an ultra-small (4mm x 4mm), 24-pin TQFN package and are specified over the -40°C to +105°C extended industrial temperature range.

#### **Applications**

Automatic Test Equipment

Automatic Tuning

Communication Systems

**Data Acquisition**

Gain and Offset Adjustment

Portable Instrumentation

Power-Amplifier Control

Process Control and Servo Loops

Programmable Voltage and Current Sources

#### Functional Diagrams and Typical Operating Circuit appear at end of data sheet.

SPI and QSPI are trademarks of Motorola Inc. MICROWIRE is a trademark of National Semiconductor Corp.

#### **Features**

- 16-/12-Bit Resolution in a 4mm x 4mm, 24-Pin **TQFN Package**

- ♦ Hardware-Selectable to Zero/Midscale DAC **Output on Power-Up or Reset**

- ♦ Double-Buffered Input Registers

- **LDAC** Asynchronously Updates DAC Outputs Simultaneously

- ♦ READY Facilitates Daisy Chaining

- **♦** High-Performance 10ppm/°C Internal Reference

- **Guaranteed Monotonic Over All Operating** Conditions

- ♦ Wide +2.7V to +5.25V Supply Range

- ♦ Rail-to-Rail Buffered Output Operation

- Low Gain Error (Less Than ±0.5%FS) and Offset (Less Than ±10mV)

- 30MHz 3-Wire SPI-/QSPI-/MICROWIRE-/ **DSP-Compatible Serial Interface**

- **♦** CMOS-Compatible Inputs with Hysteresis

- ♦ Low-Power Consumption (ISHDN = 2μA max)

#### **Ordering Information**

| PART         | PIN-<br>PACKAGE | RESOLUTION<br>(BITS) | INL<br>(LSB) |

|--------------|-----------------|----------------------|--------------|

| MAX5134AGTG+ | 24 TQFN-EP*     | 16 Quad              | ±8           |

| MAX5135GTG+  | 24 TQFN-EP*     | 12 Quad              | ±1           |

| MAX5136AGTG+ | 24 TQFN-EP*     | 16 Dual              | ±8           |

| MAX5137GTG+  | 24 TQFN-EP*     | 12 Dual              | ±1           |

<sup>+</sup>Denotes a lead-free/RoHS-compliant package.

Note: All devices are specified over the -40°C to +105°C operating temperature range.

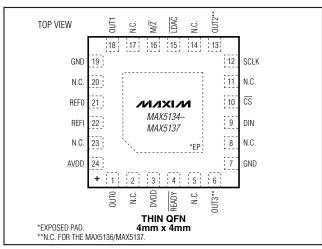

#### Pin Configuration

<sup>\*</sup>EP = Exposed pad.

#### **ABSOLUTE MAXIMUM RATINGS**

| AVDD to GND            | 0.3V to +6V             |

|------------------------|-------------------------|

| DVDD to GND            | 0.3V to +6V             |

| OUT0-OUT3 to GND       | 0.3V to the lower of    |

|                        | (AVDD + 0.3V) and +6V   |

| REFI, REFO, M/Z to GND | 0.3V to the lower of    |

|                        | (AVDD + 0.3V) and $+6V$ |

| SCLK, DIN, CS to GND   | 0.3V to the lower of    |

|                        | (DVDD + 0.3V) and $+6V$ |

| LDAC, READY to GND     | 0.3V to the lower of    |

|                        | (DVDD + 0.3V) and $+6V$ |

| Continuous Power Dissipation ( $T_A = +70$ °C) |                |

|------------------------------------------------|----------------|

| 24-Pin TQFN (derate at 17.5mW/°C above         | +70°C)2222.2mW |

| Maximum Current into Any Input or Output       |                |

| with the Exception of $M/\overline{Z}$ Pin     |                |

| Maximum Current into M/Z Pin                   | ±5mA           |

| Operating Temperature Range                    | 40°C to +105°C |

| Storage Temperature Range                      | 65°C to +150°C |

| Lead Temperature (soldering, 10s)              | +300°C         |

|                                                |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{AVDD} = 2.7V \text{ to } 5.25V, V_{DVDD} = 2.7V \text{ to } 5.25V, V_{AVDD} \ge V_{DVDD}, V_{GND} = 0, V_{REFI} = V_{AVDD} - 0.25V, C_{OUT} = 200pF, R_{OUT} = 10k\Omega, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$

| PARAMETER                                  | SYMBOL            | C                            | ONDITIONS              | MIN      | TYP           | MAX   | UNITS        |

|--------------------------------------------|-------------------|------------------------------|------------------------|----------|---------------|-------|--------------|

| STATIC ACCURACY (Notes 1, 2)               |                   |                              |                        | <u>.</u> |               |       |              |

| Danakakian                                 | NI                | MAX5134/MAX51                | 36                     | 16       |               |       | Dite         |

| Resolution                                 | N                 | MAX5135/MAX51                | 37                     | 12       |               |       | Bits         |

| Integral Nonlinearity                      | INL               | V <sub>REFI</sub> = 5V,      | (Note 3)               | -8       | ±2            | +10   | LSB          |

| (MAX5134/MAX5136)                          | IINL              | AVDD = 5.25V                 | T <sub>A</sub> = +25°C |          |               | ±6    | LSB          |

| Integral Nonlinearity<br>(MAX5135/MAX5137) | INL               | V <sub>REFI</sub> = 5V, AVD[ | D = 5.25V              | -1       | +0.25         | +1    | LSB          |

| Differential Nonlinearity                  | DNL               | Guaranteed mone              | otonic                 | -1.0     |               | +1.0  | LSB          |

| Offset Error                               | OE                | (Note 4)                     |                        | -10      | ±1            | +10   | mV           |

| Offset-Error Drift                         |                   |                              |                        |          | ±4            |       | μV/°C        |

| Gain Error                                 | GE                | (Note 4)                     |                        | -0.5     | ±0.2          | +0.5  | % of FS      |

| Gain Temperature Coefficient               |                   |                              |                        |          | ±2            |       | ppm<br>FS/°C |

| REFERENCE INPUT                            | l .               | 1                            |                        | · '      |               |       |              |

|                                            |                   | AVDD = 3V to 5.2             | 25V                    | 2        |               | AVDD  |              |

| Reference-Input Voltage Range              | VREFI             | AVDD = 2.7V to 3             | 2                      |          | AVDD -<br>0.2 | V     |              |

| Reference-Input Impedance                  |                   |                              |                        |          | 113           |       | kΩ           |

| INTERNAL REFERENCE                         |                   |                              |                        | <u>.</u> |               |       |              |

| Reference Voltage                          | V <sub>REFO</sub> | $T_{A} = +25^{\circ}C$       |                        | 2.437    | 2.440         | 2.443 | V            |

| Reference Temperature Coefficient          |                   | (Note 5)                     |                        |          | 10            | 25    | ppm/°C       |

| Reference Output Impedance                 |                   |                              |                        |          | 1             |       | Ω            |

| Line Regulation                            |                   |                              |                        |          | 100           |       | ppm/V        |

| Maximum Capacitive Load                    | CR                |                              |                        |          | 0.1           |       | nF           |

\_ /N/XI/N

#### www.deLECTRICAL CHARACTERISTICS (continued)

$(V_{AVDD}=2.7V \text{ to } 5.25V,\ V_{DVDD}=2.7V \text{ to } 5.25V,\ V_{AVDD} \ge V_{DVDD},\ V_{GND}=0,\ V_{REFI}=V_{AVDD}-0.25V,\ C_{OUT}=200pF,\ R_{OUT}=10k\Omega,\ T_A=T_{MIN}\ \text{to } T_{MAX},\ \text{unless otherwise noted.}$  Typical values are at  $T_A=+25^{\circ}C.)$

| PARAMETER                                      | SYMBOL          | CONDITIONS                                                                     | MIN           | TYP  | MAX            | UNITS  |

|------------------------------------------------|-----------------|--------------------------------------------------------------------------------|---------------|------|----------------|--------|

| DAC OUTPUT VOLTAGE (Note                       | 2)              |                                                                                | •             |      |                |        |

| Output Voltage Range                           |                 | No load                                                                        | 0.02          |      | AVDD<br>- 0.02 | V      |

| DC Output Impedance                            |                 |                                                                                |               | 0.1  |                | Ω      |

| Maximum Capacitive Load                        | CL              | Series resistance = $0\Omega$                                                  |               | 0.2  |                | nF     |

| (Note 5)                                       | OL.             | Series resistance = $500\Omega$                                                |               | 15   |                | μF     |

| Resistive Load                                 | RL              |                                                                                | 2             |      |                | kΩ     |

| Short-Circuit Current                          | Isc             | AVDD = 5.25V                                                                   |               | ±35  |                | mA     |

|                                                | 130             | AVDD = 2.7V                                                                    | -40           | ±20  | +40            | 1117 ( |

| Power-Up Time                                  |                 | From power-down mode                                                           |               | 25   |                | μs     |

| DIGITAL INPUTS (SCLK, DIN, O                   | S, LDAC) (No    | te 6)                                                                          |               |      |                |        |

| Input High Voltage                             | V <sub>IH</sub> |                                                                                | 0.7 x<br>DVDD |      |                | V      |

| Input Low Voltage                              | VIL             |                                                                                |               |      | 0.3 x<br>DVDD  | V      |

| Input Leakage Current                          | I <sub>IN</sub> | V <sub>IN</sub> = 0 or DVDD                                                    | -1            | ±0.1 | +1             | μΑ     |

| Input Capacitance                              | CIN             |                                                                                |               |      | 10             | рF     |

| DIGITAL OUTPUTS (READY)                        |                 |                                                                                |               |      |                |        |

| Output High Voltage                            | Voн             | ISOURCE = 3mA                                                                  | DVDD<br>- 0.5 |      |                | V      |

| Output Low Voltage                             | V <sub>OL</sub> | ISINK = 2mA                                                                    |               |      | 0.4            | V      |

| DYNAMIC PERFORMANCE                            |                 |                                                                                |               |      |                |        |

| Voltage-Output Slew Rate                       | SR              | Positive and negative                                                          |               | 1.25 |                | V/µs   |

| Voltage-Output Settling Time                   | ts              | 1/4 scale to 3/4 scale V <sub>REFI</sub> = AVDD = 5V settle to ±2 LSB (Note 5) |               | 5    |                | μs     |

| Digital Feedthrough                            |                 | Code 0, all digital inputs from 0 to DVDD                                      |               | 0.5  |                | nV∙s   |

| Major Code Transition Analog<br>Glitch Impulse |                 |                                                                                |               | 12   |                | nV∙s   |

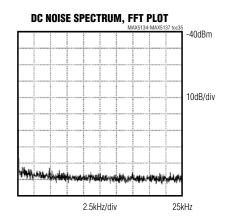

| Output Noise                                   |                 | 10kHz                                                                          |               | 120  |                | nV/√Hz |

| Integrated Output Noise                        |                 | 1Hz to 10kHz                                                                   |               | 18   |                | μV     |

| DAC-to-DAC Crosstalk                           |                 |                                                                                |               | 25   |                | nV∙s   |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{AVDD} = 2.7V \text{ to } 5.25V, V_{DVDD} = 2.7V \text{ to } 5.25V, V_{AVDD} \ge V_{DVDD}, V_{GND} = 0, V_{REFI} = V_{AVDD} - 0.25V, C_{OUT} = 200pF, R_{OUT} = 10k\Omega, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } T_A = +25^{\circ}C.)$

| PARAMETER                       | SYMBOL            | CONDITIONS                                 | MIN | TYP | MAX  | UNITS |

|---------------------------------|-------------------|--------------------------------------------|-----|-----|------|-------|

| POWER REQUIREMENTS (Note 7      | 7)                |                                            |     |     |      |       |

| Analog Supply Voltage Range     | AVDD              |                                            | 2.7 |     | 5.25 | V     |

| Digital Supply Voltage Range    | DVDD              |                                            | 2.7 |     | AVDD | V     |

| Supply Current                  | lavdd             | No load, all digital inputs at 0 or DVDD   |     | 2.5 | 3.6  | mA    |

| (MAX5134/MAX5135)               | I <sub>DVDD</sub> | 140 load, all digital iliputs at 0 of DVDD |     | 1   | 10   | μΑ    |

| Supply Current                  | lavdd             | No load, all digital inputs at 0 or DVDD   |     | 1.5 | 2.3  | mA    |

| (MAX5136/MAX5137)               | IDVDD             | Tho load, all digital inputs at 0 of DVDD  |     | 1   | 10   | μΑ    |

| Power-Down Supply Current       | IAVPD             | No load, all digital inputs at 0 or DVDD   |     | 0.2 | 2    | μA    |

| Tower-Down Supply Current       | I <sub>DVPD</sub> | 140 load, all digital iliputs at 0 of DVDD |     | 0.1 | 2    | μΑ    |

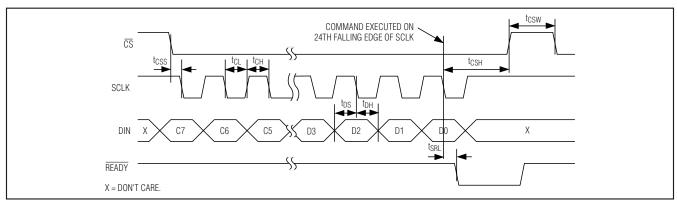

| TIMING CHARACTERISTICS (Not     | te 8) (Figure     | 1)                                         |     |     |      |       |

| Serial-Clock Frequency          | fsclk             |                                            | 0   |     | 30   | MHz   |

| SCLK Pulse-Width High           | tCH               |                                            | 13  |     |      | ns    |

| SCLK Pulse-Width Low            | tCL               |                                            | 13  |     |      | ns    |

| CS Fall-to-SCLK Fall Setup Time | tcss              |                                            | 8   |     |      | ns    |

| SCLK Fall-to CS-Rise Hold Time  | tcsh              |                                            | 5   |     |      | ns    |

| DIN-to-SCLK Fall Setup Time     | tDS               |                                            | 10  |     |      | ns    |

| DIN-to-SCLK Fall Hold Time      | tDH               |                                            | 2   |     |      | ns    |

| SCLK Fall to READY Transition   | tsrl              | (Note 9)                                   |     |     | 30   | ns    |

| CS Pulse-Width High             | tcsw              |                                            | 33  |     |      | ns    |

| LDAC Pulse Width                | tLDACPWL          |                                            | 33  |     |      | ns    |

- Note 1: Static accuracy tested without load.

- Note 2: Linearity is tested within 20mV of GND and AVDD, allowing for gain and offset error.

- Note 3: Codes above 2047 are guaranteed to be within ±8 LSB.

- Note 4: Gain and offset tested within 100mV of GND and AVDD

- Note 5: Guaranteed by design.

- **Note 6:** Device draws current in excess of the specified supply current when a digital input is driven with a voltage of VI < DVDD 0.6V or VI > 0.5V. At VI = 2.2V with DVDD = 5.25V, this current can be as high as 2mA. The SPI inputs are CMOS-input level compatible. The 30MHz clock frequency cannot be guaranteed for a minimum signal swing.

- Note 7: Excess current from AVDD is 10mA when powered without DVDD. Excess current from DVDD is 1mA when powered without AVDD.

- Note 8: All timing specifications are with respect to the digital input and output thresholds.

- Note 9: Maximum daisy-chain clock frequency is limited to 25MHz.

Figure 1. Serial-Interface Timing Diagram

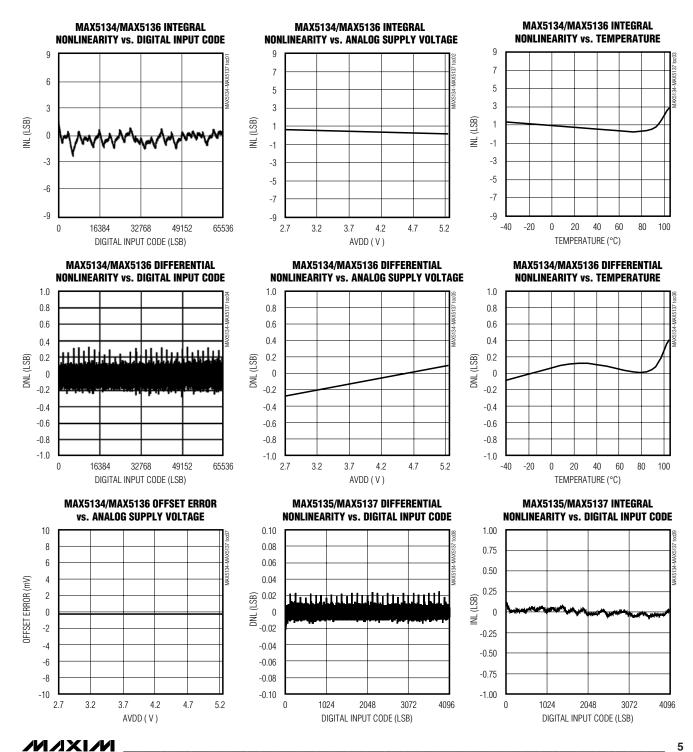

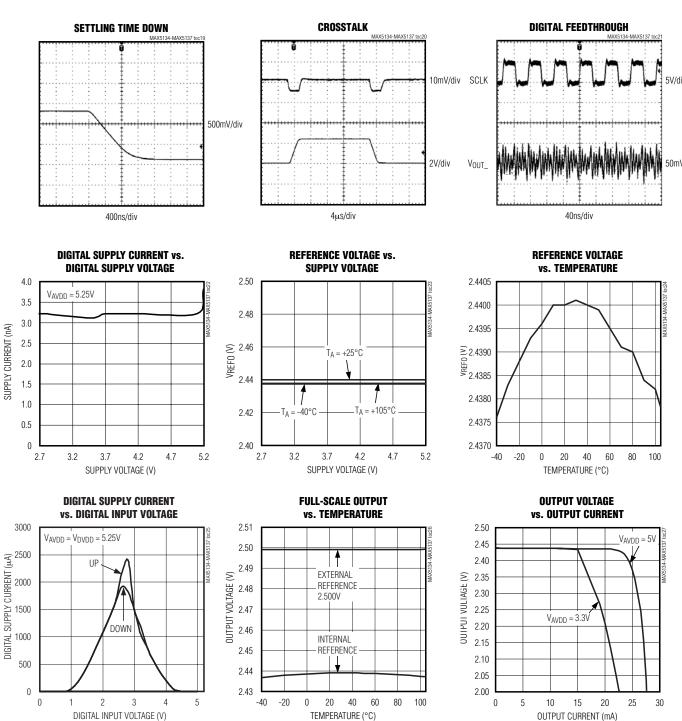

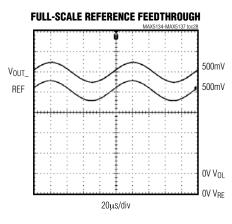

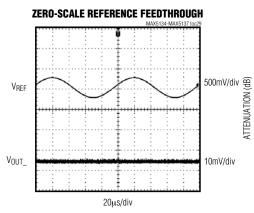

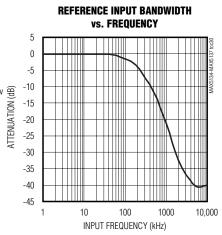

**Typical Operating Characteristics**

www.datasheet4u.com

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# MAX5134-MAX5137

# Pin-/Software-Compatible, 16-/12-Bit, Voltage-Output DACs

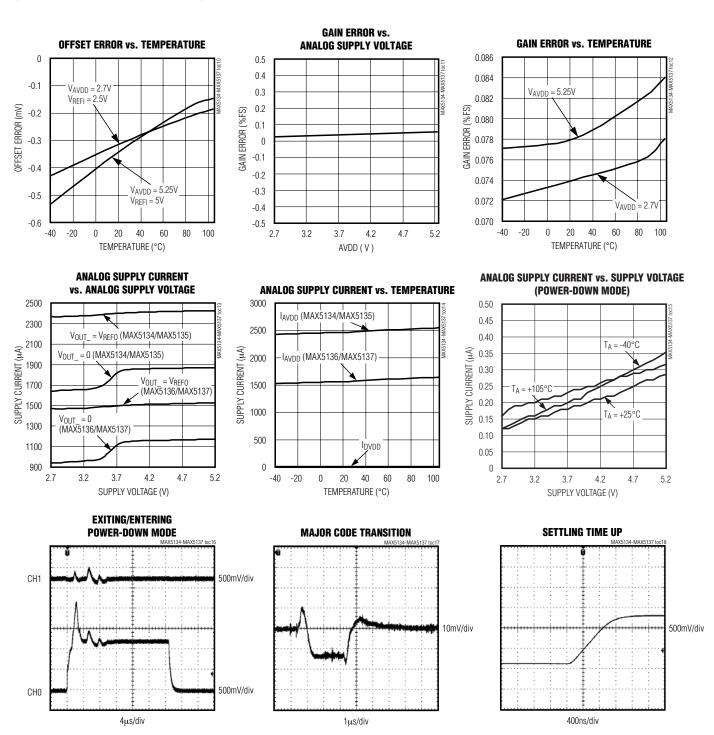

#### \_Typical Operating Characteristics (continued)

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

Typical Operating Characteristics (continued)

www.datasheet4u.com

SUPPLY CURRENT (nA)

MIXIM

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

# MAX5134-MAX5137

## Pin-/Software-Compatible, 16-/12-Bit, Voltage-Output DACs

$(T_A = +25^{\circ}C, \text{ unless otherwise noted.})$

Pin Description

| Р                                 | PIN                                      |                  |                                                                                                                                                                       |  |

|-----------------------------------|------------------------------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| MAX5134<br>MAX5135                | MAX5136<br>MAX5137                       | NAME             | FUNCTION                                                                                                                                                              |  |

| 1                                 | 1                                        | OUT0             | Channel 0 Buffered DAC Output                                                                                                                                         |  |

| 2, 5, 8,<br>11, 14, 17,<br>20, 23 | 2, 5, 6, 8,<br>11, 13, 14,<br>17, 20, 23 | N.C.             | No Connection. Not internally connected.                                                                                                                              |  |

| 3                                 | 3                                        | DVDD             | Digital Power Supply. Bypass DVDD with a 0.1µF capacitor to GND.                                                                                                      |  |

| 4                                 | 4                                        | READY            | Active-Low Ready. Indicated configuration ready. Use $\overline{\text{READY}}$ as $\overline{\text{CS}}$ for consecutive part or as feedback to the $\mu\text{C}$ .   |  |

| 6                                 | _                                        | OUT3             | Channel 3 Buffered DAC Output                                                                                                                                         |  |

| 7, 19                             | 7, 19                                    | GND              | Ground                                                                                                                                                                |  |

| 9                                 | 9                                        | DIN              | Data In                                                                                                                                                               |  |

| 10                                | 10                                       | CS               | Active-Low Chip-Select Input                                                                                                                                          |  |

| 12                                | 12                                       | SCLK             | Serial-Clock Input                                                                                                                                                    |  |

| 13                                | _                                        | OUT2             | Channel 2 Buffered DAC Output                                                                                                                                         |  |

| 15                                | 15                                       | LDAC             | Load DAC Input. Active-low hardware load DAC input.                                                                                                                   |  |

| 16                                | 16                                       | $M/\overline{Z}$ | Power-Up Reset Select. Connect $M/\overline{Z}$ to DVDD to power up the DAC outputs to midscale. Connect $M/\overline{Z}$ to GND to power up the DAC outputs to zero. |  |

| 18                                | 18                                       | OUT1             | Channel 1 Buffered DAC Output                                                                                                                                         |  |

| 21                                | 21                                       | REFO             | Reference Voltage Output                                                                                                                                              |  |

| 22                                | 22                                       | REFI             | Reference Voltage Input. Bypass REFI with a 0.1µF capacitor to GND when using external reference.                                                                     |  |

| 24                                | 24                                       | AVDD             | Analog Power Supply. Bypass AVDD with a 0.1µF capacitor to GND.                                                                                                       |  |

| _                                 |                                          | EP               | Exposed Pad. Internally connected to GND. Connect to a large ground plane to maximize thermal performance. Not intended as an electrical connection point.            |  |

#### **Detailed Description**

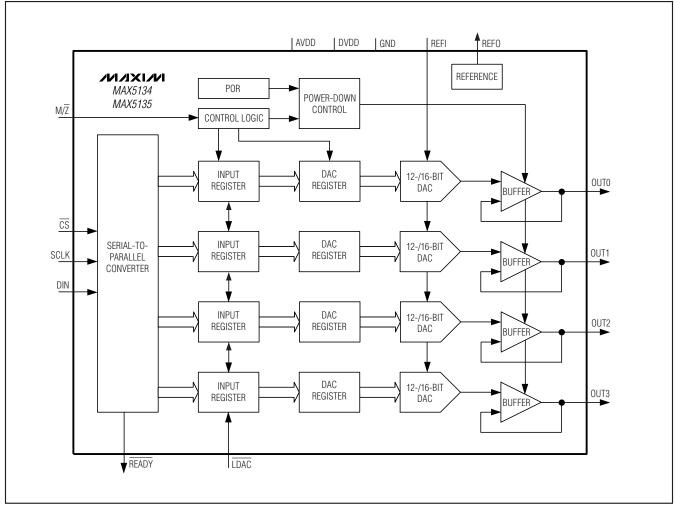

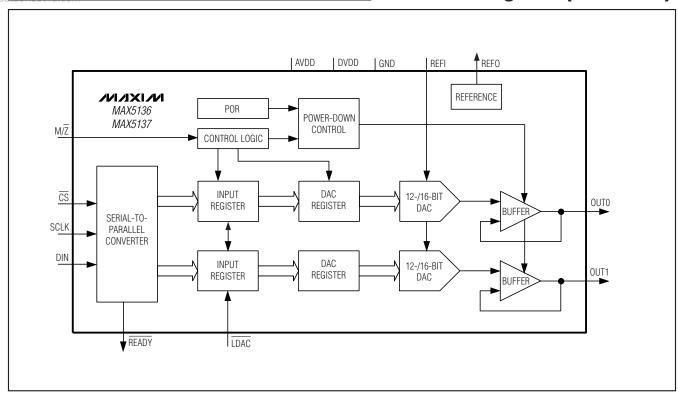

The MAX5134-MAX5137 is a family of pin-compatible and software-compatible 16-bit and 12-bit DACs. The MAX5134/MAX5135 are low-power, guad 16-/12-bit, buffered voltage-output, high-linearity DACs. The MAX5136/MAX5137 are low-power, dual 16-/12-bit. buffered voltage-output, high-linearity DACs. The MAX5134-MAX5137 minimize the digital noise feedthrough from input to output by powering down the SCLK and DIN input buffers after completion of each 24bit serial input. On power-up, the MAX5134-MAX5137 reset the DAC outputs to zero or midscale, depending on the state of the  $M/\overline{Z}$  input, providing additional safety for applications that drive valves or other transducers that need to be off on power-up. The MAX5134-MAX5137 contain a segmented resistor string-type DAC, a serial-in parallel-out shift register, a DAC register, poweron reset (POR) circuit, and control logic. On the falling edge of the clock (SCLK) pulse, the serial input (DIN) data is shifted into the device, MSB first. During power-down, an internal  $80k\Omega$  resistor pulls DAC outputs to GND.

#### **Output Amplifiers (OUT0-OUT3)**

The MAX5134–MAX5137 include internal buffers for all DAC outputs. The internal buffers provide improved load regulation and transition glitch suppression for the DAC outputs. The output buffers slew at 1.25V/ $\mu$ s and drive up to 2k $\Omega$  in parallel with 200pF. The analog supply voltage (AVDD) determines the maximum output voltage range of the device as AVDD powers the output buffers.

#### DAC Reference

#### Internal Reference

The MAX5134-MAX5137 feature an internal reference with a nominal output of +2.44V. Connect REFO to REFI when using the internal reference. Bypass REFO to GND with a 47pF (maximum 100pF) capacitor. Alternatively if heavier decoupling is required, use a 1k $\Omega$  series resistor with a 1µF capacitor to ground. REFO can deliver up to 100µA of current with no degradation in performance. Configure other reference voltages by applying a resistive potential divider with a total resistance greater than 33k $\Omega$  from REFO to GND.

www.datasheet4u

#### External Reference

The external reference input features a typical input impedance of 113kΩ and accepts an input voltage from +2V to AVDD. Connect an external voltage supply between REFI and GND to apply an external reference. Leave REFO unconnected. Visit <a href="https://www.maxim-ic.com/products/references">www.maxim-ic.com/products/references</a> for a list of available external voltage-reference devices.

#### AVDD as Reference

Connect AVDD to REFI to use AVDD as the reference voltage. Leave REFO unconnected.

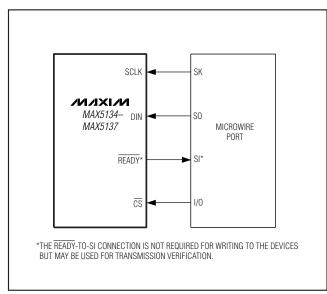

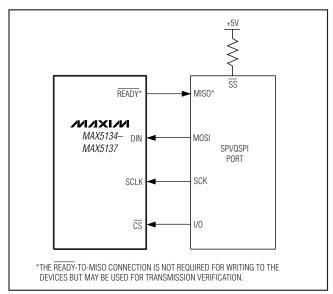

#### **Serial Interface**

The MAX5134–MAX5137 3-wire serial interface is compatible with MICROWIRE, SPI, QSPI, and DSPs (Figures 2, 3). The interface provides three inputs, SCLK,  $\overline{\text{CS}}$ , and DIN and one output,  $\overline{\text{READY}}$ . Use  $\overline{\text{READY}}$  to verify communication or to daisy-chain multiple devices (see the  $\overline{\text{READY}}$  section).  $\overline{\text{READY}}$  is capable of driving a 20pF load with a 30ns (max) delay from the falling edge of SCLK. The chip-select input ( $\overline{\text{CS}}$ ) frames the serial data loading at DIN. Following a chip-select input's

high-to-low transition, the data is shifted synchronously and latched into the input register on each falling edge of the serial-clock input (SCLK). Each serial word is 24 bits. The first 8 bits are the control word followed by 16 data bits (MSB first), as shown in Table 1. The serial input register transfers its contents to the input registers after loading 24 bits of data. To initiate a new data transfer, drive  $\overline{\text{CS}}$  high, keep  $\overline{\text{CS}}$  high for a minimum of 33ns before the next write sequence. The SCLK can be either high or low between  $\overline{\text{CS}}$  write pulses. Figure 1 shows the timing diagram for the complete 3-wire serial-interface transmission.

The MAX5134–MAX5137 digital inputs are double buffered. Depending on the command issued through the serial interface, the input register(s) can be loaded without effecting the DAC register(s) using the write command. To update the DAC registers, either pulse the  $\overline{\text{LDAC}}$  input low to asynchronously update all DAC outputs, or use the software  $\overline{\text{LDAC}}$  command. Use the writethrough commands (see Table 1) to update the DAC outputs immediately after the data is received. Only use the writethrough command to update the DAC output immediately.

Table 1. Operating Mode Truth Table\*

|    |    |    |    |          |          |          |          | :   | 24-B | T W | ORD |          |          |          |          |          |       |                   |                                                                                                                |

|----|----|----|----|----------|----------|----------|----------|-----|------|-----|-----|----------|----------|----------|----------|----------|-------|-------------------|----------------------------------------------------------------------------------------------------------------|

|    |    | С  | ON | TROL     | BITS     | 3        |          |     |      |     |     | 1        | DATA     | BITS     | 3        |          |       |                   |                                                                                                                |

| М  | SB |    |    |          |          |          |          |     |      |     |     |          |          |          |          |          | LSB   | DESC              | FUNCTION                                                                                                       |

| C7 | C6 | C5 | C4 | СЗ       | C2       | C1       | CO       | D15 | D14  | D13 | D12 | D11      | D10      | D9       | D8       | D7       | D6-D0 |                   |                                                                                                                |

| 0  | 0  | 0  | 0  | 0        | 0        | 0        | 0        | Χ   | Χ    | Χ   | Χ   | Χ        | Χ        | Χ        | Χ        | Χ        | Χ     | NOP               | No operation.                                                                                                  |

| 0  | 0  | 0  | 0  | 0        | 0        | 0        | 1        | X   | X    | X   | X   | DAC<br>3 | DAC<br>2 | DAC<br>1 | DAC<br>0 | X        | X     | LDAC              | Move contents of input<br>to DAC registers<br>indicated by 1's. No<br>effect on registers<br>indicated by 0's. |

| 0  | 0  | 0  | 0  | 0        | 0        | 1        | 0        | Χ   | Χ    | Χ   | Χ   | Χ        | Χ        | Χ        | Χ        | Χ        | Χ     | CLR               | Software clear.                                                                                                |

| 0  | 0  | 0  | 0  | 0        | 0        | 1        | 1        | X   | X    | X   | X   | DAC<br>3 | DAC<br>2 | DAC<br>1 | DAC<br>0 | READY_EN | X     | Power<br>Control  | Power down DACs indicated by 1's. Set READY_EN = 1 to enable READY.                                            |

| 0  | 0  | 0  | 0  | 0        | 1        | 0        | 1        | 0   | 0    | 0   | 0   | 0        | 0        | LIN      | 0        | 0        | 0     | Linearity         | Optimize DAC linearity.                                                                                        |

| 0  | 0  | 0  | 1  | DAC<br>3 | DAC<br>2 | DAC<br>1 | DAC<br>0 | D15 | D14  | D13 | D12 | D11      | D10      | D9       | D8       | D7       | D6    | Write             | Write to selected input registers (DAC output not affected).                                                   |

| 0  | 0  | 1  | 1  | DAC<br>3 | DAC<br>2 | DAC<br>1 | DAC<br>0 | D15 | D14  | D13 | D12 | D11      | D10      | D9       | D8       | D7       | D6    | Write-<br>through | Write to selected input and DAC registers, DAC outputs updated (writethrough).                                 |

| 0  | 0  | 1  | 0  | 0        | 0        | 0        | 0        | Χ   | Χ    | Χ   | Χ   | Χ        | Χ        | Χ        | Χ        | Х        | Χ     | NOP               | No operation.                                                                                                  |

<sup>\*</sup>For the MAX5136/MAX5137, DAC2 and DAC3 do not exist. For the MAX5135/MAX5137, D0-D3 are don't-care bits.

The MAX5134/MAX5136 DAC code is unipolar binary with Vout\_ = (code/65,536) x VREF. The MAX5135/MAX5137 DAC code is unipolar binary with Vout\_ = (code/4096) x VREF. See Table 1 for the serial interface commands.

Connect the MAX5134–MAX5137 DVDD supply to the supply of the host DSP or microprocessor. The AVDD supply may be set to any voltage within the operating range of 2.7V to 5.25V, but must be greater than or equal to the DVDD supply.

#### Writing to the Devices

Write to the MAX5134-MAX5137 using the following sequence:

- 1) Drive  $\overline{\text{CS}}$  low, enabling the shift register.

- 2) Clock 24 bits of data into DIN (C7 first and D0 last), observing the specified setup and hold times. Bits

- D15-D0 are the data bits that are written to the internal register.

- 3) After clocking in the last data bit, drive  $\overline{\text{CS}}$  high.  $\overline{\text{CS}}$  must remain high for 33ns before the next transmission is started.

Figure 1 shows a write operation for the transmission of 24 bits. If  $\overline{\text{CS}}$  is driven high at any point prior to receiving 24 bits, the transmission is discarded.

#### READY

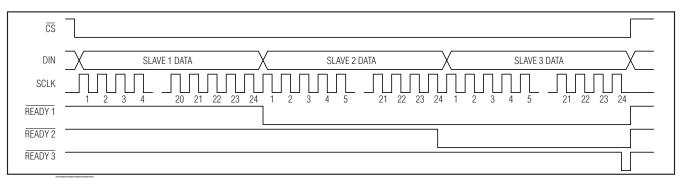

Connect  $\overline{READY}$  to a microcontroller (µC) input to monitor the serial interface for valid communications. The  $\overline{READY}$  pulse appears 24 clock cycles after the negative edge of  $\overline{CS}$  (Figure 4). Since the MAX5134–MAX5137 look at the first 24 bits of the transmission following the falling edge of  $\overline{CS}$ , it is possible to daisy chain devices with different command word lengths.  $\overline{READY}$  goes high 16ns after  $\overline{CS}$  is driven high.

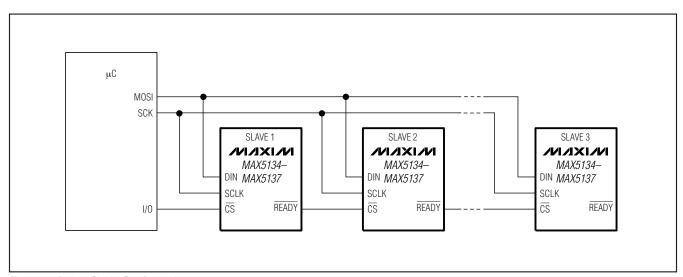

Figure 2. Connections for MICROWIRE

Figure 3. Connections for SPI/QSPI

Figure 4. READY Timing

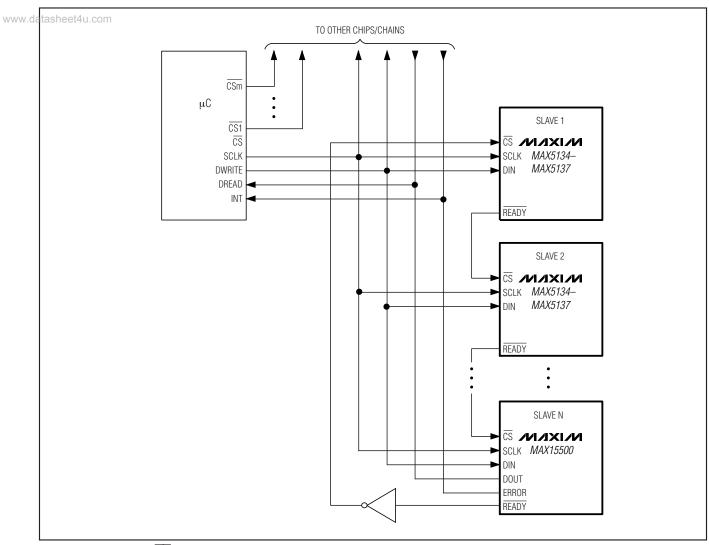

Daisy chain multiple MAX5134–MAX5137 devices by connecting the first device conventionally, then connect its  $\overline{READY}$  output to the  $\overline{CS}$  of the following device. Repeat for any other devices in the chain, and drive the SCLK and DIN lines in parallel (Figure 5). When sending commands to daisy-chained devices, the devices are accessed serially starting with the first device in the chain. The first 24 data bits are read by the first device, the second 24 data bits are read by the second device and so on (Figure 4). Figure 6 shows the configuration when  $\overline{CS}$  is not driven by the  $\mu C$ . These devices can be daisy chained with other compatible devices such as the MAX15500 output conditioner.

To perform a daisy-chain write operation, drive  $\overline{\text{CS}}$  low and output the data serially to DIN. The propagation of the  $\overline{\text{READY}}$  signal then controls how the data is read by each device. As the data propagates through the daisy chain, each individual command in the chain is executed on the 24th falling clock edge following the falling edge of the respective  $\overline{\text{CS}}$  input. To update just one device in a daisy chain, send the no-op command to the other devices in the chain.

If  $\overline{\text{READY}}$  is not required, write command 0x03 (power control) and set READY\_EN = 0 (see Table 1) to disable the  $\overline{\text{READY}}$  output.

#### Clear Command

The MAX5134–MAX5137 feature a software clear command (0x02). The software clear command acts as a software POR, erasing the contents of all registers. All outputs return to the state determined by the M/Z input.

#### Power-Down Mode

The MAX5134–MAX5137 feature a software-controlled individual power-down mode for each channel. The internal reference and biasing circuits power down to conserve power when all 4 channels are powered down. In power-down, the outputs disconnect from the buffers and are grounded with an internal  $80k\Omega$  resistor. The DAC register holds the retained code so that the output is restored when the channel powers up. The serial interface remains active in power-down mode.

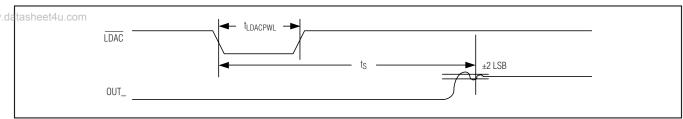

#### Load DAC (LDAC) Input

The MAX5134-MAX5137 feature an active-low LDAC logic input that allows the outputs to update asynchronously. Keep LDAC high during normal operation (when the device is controlled only through the serial interface). Drive LDAC low to simultaneously update all DAC outputs with data from their respective input registers. Figure 7 shows the LDAC timing with respect to OUT . Holding LDAC low causes the input registers to become transparent and data written to the DAC registers to immediately update the DAC outputs. A software command can also activate the LDAC operation. To activate LDAC by software, set control word 0x01 and data bits A11-A8 to select which DAC to load, and all other data bits to don't care. See Table 1 for the data format. This operation updates only the DAC outputs that are flagged with a 1. DAC outputs flagged with a 0 remain unchanged.

Figure 5. Daisy-Chain Configuration

Figure 6. Daisy Chain (CS Not Used)

Figure 7. Output Timing

#### **Applications Information**

#### **Power-On Reset (POR)**

On power-up, the input registers are set to zero, DAC outputs power up to zero or midscale, depending on the configuration of  $M/\overline{Z}$ . Connect  $M/\overline{Z}$  to GND to power the outputs to GND. Connect  $M/\overline{Z}$  to AVDD to power the outputs to midscale.

To optimize DAC linearity, wait until the supplies have settled. Set the LIN bit in the DAC linearity register; wait 10ms, and clear the LIN bit.

#### **Unipolar Output**

The MAX5134–MAX5137 unipolar output voltage range is 0 to  $V_{REFI}$ . The output buffers each drive a load of  $2k\Omega$  in parallel with 200pF.

#### **Bipolar Output**

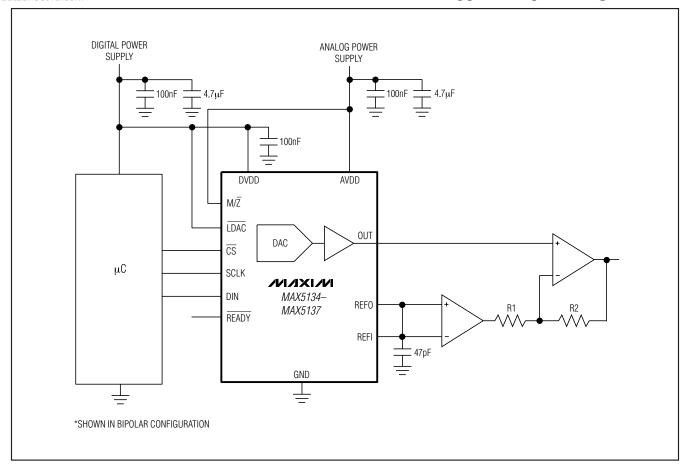

Use the MAX5134–MAX5137 in bipolar applications with additional external components (see the *Typical Operating Circuit*).

## **Power Supplies and Bypassing Considerations**

For best performance, use a separate supply for the MAX5134-MAX5137. Bypass both DVDD and AVDD with high-quality ceramic capacitors to a low-impedance ground as close as possible to the device. Minimize lead lengths to reduce lead inductance. Connect both MAX5134-MAX5137 GND inputs to the analog ground plane.

## Table 2. MAX5134/MAX5136 Input Code vs. Output Voltage

| DAC LATCH CONTENTS  | ANALOG OUTDUT Voice                                       |  |  |  |

|---------------------|-----------------------------------------------------------|--|--|--|

| MSB LSB             | ANALOG OUTPUT, V <sub>OUT</sub>                           |  |  |  |

| 1111 1111 1111 1111 | V <sub>REF</sub> x (65,535/65,536)                        |  |  |  |

| 1000 0000 0000 0000 | V <sub>REF</sub> x (32,768/65,536) = 1/2 V <sub>REF</sub> |  |  |  |

| 0000 0000 0000 0001 | V <sub>REF</sub> x (1/65,536)                             |  |  |  |

| 0000 0000 0000 0000 | 0                                                         |  |  |  |

#### **Layout Considerations**

Digital and AC transient signals on GND inputs can create noise at the outputs. Connect both GND inputs to form the star ground for the DAC system. Refer remote DAC loads to this system ground for the best possible performance. Use proper grounding techniques, such as a multilayer board with a low-inductance ground plane, or star connect all ground return paths back to the MAX5134–MAX5137 GND. Carefully lay out the traces between channels to reduce AC crosscoupling and crosstalk. Do not use wire-wrapped boards and sockets. Use shielding to improve noise immunity. Do not run analog and digital signals parallel to one another (especially clock signals) and avoid routing digital lines underneath the MAX5134–MAX5137 package.

#### **Definitions**

#### **Integral Nonlinearity (INL)**

INL is the deviation of the measured transfer function from a best fit straight line drawn between two codes. For the MAX5134/MAX5136, this best fit line is a line drawn between codes 3072 and 64,512 of the transfer function, once offset and gain errors have been nullified. For the MAX5135/MAX5137, this best fit line is a line drawn between codes 192 and 4032 of the transfer function, once offset and gain errors have been nullified.

#### **Differential Nonlinearity (DNL)**

DNL is the difference between an actual step height and the ideal value of 1 LSB. If the magnitude of the DNL is greater than -1 LSB, the DAC guarantees no missing codes and is monotonic.

Table 3. MAX5135/MAX5137 Input Code vs. Output Voltage

| DAC  | LATCH | CONT | ENTS | ANALOG OUTPUT, V <sub>OUT</sub> |  |  |  |

|------|-------|------|------|---------------------------------|--|--|--|

| MSB  |       |      | LSB  | ANALOG OUTPUT, VOUT_            |  |  |  |

| 1111 | 1111  | 1111 | XXXX | V <sub>REF</sub> x (4095/4096)  |  |  |  |

| 1000 | 0000  | 0000 | XXXX | V <sub>REF</sub> x (2048/4096)  |  |  |  |

| 0000 | 0000  | 0001 | XXXX | V <sub>REF</sub> x (1/4096)     |  |  |  |

| 0000 | 0000  | 0000 | XXXX | 0                               |  |  |  |

Offset Error

Offset error indicates how well the actual transfer function matches the ideal transfer function at a single point. Typically, the point at which the offset error is specified is at or near the zero-scale point of the transfer function.

#### **Gain Error**

Gain error is the difference between the ideal and the actual full-scale output voltage on the transfer curve, after nullifying the offset error. This error alters the slope of the transfer function and corresponds to the same percentage error in each step.

#### **Settling Time**

The settling time is the amount of time required from the start of a transition, until the DAC output settles to the new output value within the converter's specified accuracy.

#### **Digital Feedthrough**

Digital feedthrough is the amount of noise that appears on the DAC output when the DAC digital control lines are toggled.

#### **Digital-to-Analog Glitch Impulse**

A major carry transition occurs at the midscale point where the MSB changes from low to high and all other bits change from high to low, or where the MSB changes from high to low and all other bits change from low to high. The duration of the magnitude of the switching glitch during a major carry transition is referred to as the digital-to-analog glitch impulse.

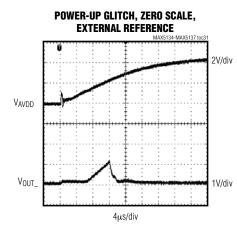

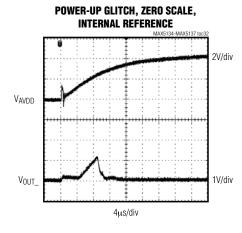

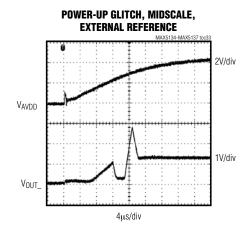

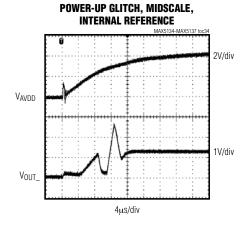

#### **Digital-to-Analog Power-Up Glitch Impulse**

The digital-to-analog power-up glitch is the duration of the magnitude of the switching glitch that occurs as the device exits power-down mode.

#### **DC DAC-to-DAC Crosstalk**

Crosstalk is the amount of noise that appears on a DAC output set to 0 when the other DAC is updated from 0 to AVDD

**Chip Information**

PROCESS: BICMOS

# **Functional Diagrams**

### Functional Diagrams (continued)

#### w.datasheet4u.com\_\_\_\_\_\_Typical Operating Circuit

#### **Package Information**

For the latest package outline information and land patterns, go to www.maxim-ic.com/packages

| PACKAGE TYPE | PACKAGE CODE | DOCUMENT NO. |

|--------------|--------------|--------------|

| 24 TQFN-EP   | T2444-4      | 21-0139      |

www.datasheet4u.com Revision History

| REVISION<br>NUMBER | REVISION<br>DATE | DESCRIPTION                                | PAGES<br>CHANGED |

|--------------------|------------------|--------------------------------------------|------------------|

| 0                  | 7/08             | Initial release of MAX5134                 | _                |

| 1                  | 10/08            | Initial release of MAX5135/MAX5136/MAX5137 | 1–19             |

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.