### **General Description**

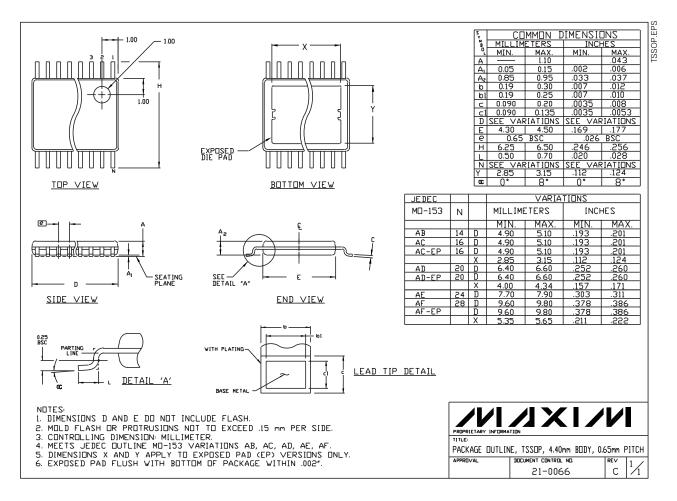

The MAX5101 parallel-input, voltage-output, triple 8-bit digital-to-analog converter (DAC) operates from a single +2.7V to +5.5V supply and comes in a space-saving 16-pin TSSOP package. Internal precision buffers swing Rail-to-Rail®. For all three DACs, the internal reference voltage is tied to VDD.

The MAX5101 has separate input latches for each of its three DACs. Data is transferred to the input latches from a common 8-bit input port. The DACs are individually selected through address inputs A0 and A1 and are updated by bringing WR low.

The MAX5101 features a 1µA software shutdown mode, as well as a power-on reset mode that resets all registers to code 00 hex on power-up.

## **Applications**

Digital Gain and Offset Adjustment Programmable Attenuators Portable Instruments Power-Amp Bias Control

#### **Features**

- ♦ +2.7V to +5.5V Single-Supply Operation

- ♦ Ultra-Low Supply Current 0.3mA while Operating 1µA in Software Shutdown Mode

- ♦ Ultra-Small 16-Pin TSSOP Package

- ♦ Output Buffer Amplifiers Swing Rail-to-Rail

- ♦ Power-On Reset Sets All Registers to Zero

### **Ordering Information**

| PART        | TEMP. RANGE    | PIN-<br>PACKAGE | INL<br>(LSB) |

|-------------|----------------|-----------------|--------------|

| MAX5101AEUE | -40°C to +85°C | 16 TSSOP        | ±1           |

| MAX5101BEUE | -40°C to +85°C | 16 TSSOP        | ±2           |

#### **Functional Diagram**

### INPUT ► OUTA DAC A LATCH A INPLIT OUTB D0-D7 DAC B LATCH B INPLIT ► OUTC DAC C LATCH C CONTROL MIXIM LOGIC MAX5101 WR

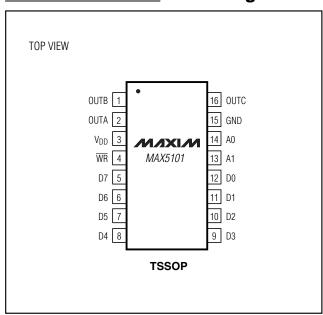

## Pin Configuration

Rail-to-Rail is a registered trademark of Nippon Motorola, Ltd.

MIXIM

Maxim Integrated Products 1

For free samples & the latest literature: http://www.maxim-ic.com, or phone 1-800-998-8800. For small orders, phone 1-800-835-8769.

#### **ABSOLUTE MAXIMUM RATINGS**

| $\begin{array}{llllllllllllllllllllllllllllllllllll$ | Operating Temperature Range  MAX5101_EUE |

|------------------------------------------------------|------------------------------------------|

| Maximum Current into Any Pin±50mA                    | Storage Temperature Range65°C to +150°   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS**

$(V_{DD} = +2.7 V \text{ to } +5.5 V, R_L = 10 k\Omega, C_L = 100 pF, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted. Typical values are at } V_{DD} = +3 V \text{ and } T_A = +25 ^{\circ}\text{C.})$

| PARAMETER                                    | SYMBOL | CONDITIONS                                    | MIN | TYP    | MAX               | UNITS  |

|----------------------------------------------|--------|-----------------------------------------------|-----|--------|-------------------|--------|

| STATIC ACCURACY                              |        |                                               | _   |        |                   | •      |

| Resolution                                   |        |                                               |     |        | 8                 | Bits   |

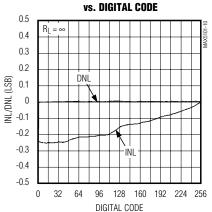

|                                              | INII   | MAX5101A                                      |     |        |                   | - LSB  |

| Integral Nonlinearity (Note 1)               | INL    | MAX5101B                                      |     |        | ±2                | LSB    |

| Differential Nonlinearity (Note 1)           | DNL    | Guaranteed monotonic                          |     |        | ±1                | LSB    |

| Zero-Code Error                              | ZCE    | Code = 00 hex                                 |     |        | ±20               | mV     |

| Zero-Code-Error Supply<br>Rejection          |        | Code = 00 hex, V <sub>DD</sub> = 2.7V to 5.5V |     |        | 10                | mV     |

| Zero-Code Temperature<br>Coefficient         |        | Code = 00 hex                                 |     | ±10    |                   | μV/°C  |

| Gain Error (Note 2)                          |        | Code = F0 hex                                 |     |        | ±1                | %      |

| Gain-Error Temperature<br>Coefficient        |        | Code = F0 hex                                 |     | ±0.001 |                   | LSB/°C |

| DAC OUTPUTS                                  |        |                                               |     |        |                   |        |

| Output Voltage Range                         |        | R <sub>L</sub> = ∞                            | 0   |        | $V_{\mathrm{DD}}$ | V      |

| DIGITAL INPUTS                               | '      |                                               | _   |        |                   | •      |

| Lancott High Malkana                         | VIH    | V <sub>DD</sub> = 2.7V to 3.6V                | 2   |        |                   | V      |

| Input High Voltage                           |        | V <sub>DD</sub> = 3.6V to 5.5V                | 3   |        |                   |        |

| Input Low Voltage                            | VIL    |                                               |     |        | 0.8               | V      |

| Input Current I <sub>IN</sub>                |        | $V_{IN} = V_{DD}$ or GND                      |     |        | ±1.0              | μΑ     |

| Input Capacitance                            | CIN    |                                               |     | 10     |                   | pF     |

| DYNAMIC PERFORMANCE                          |        |                                               |     |        |                   |        |

| Output Voltage Slew Rate                     |        | From code 00 to code F0 hex                   |     | 0.6    |                   | V/µs   |

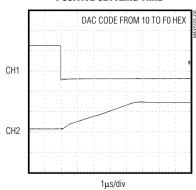

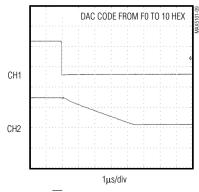

| Output Settling Time (Note 3)                |        | To 1/2LSB, from code 10 to code F0 hex        |     | 6      |                   | μs     |

| Channel-to-Channel Isolation (Note 4)        |        | Code 00 to code FF hex                        |     | 500    |                   | nVs    |

| Digital Feedthrough (Note 5) Code 00 to code |        | Code 00 to code FF hex                        |     | 0.5    |                   | nVs    |

|                                              | •      |                                               |     |        |                   |        |

#### **ELECTRICAL CHARACTERISTICS (continued)**

$(V_{DD} = +2.7 V \text{ to } +5.5 V, R_L = 10 k\Omega, C_L = 100 pF, T_A = T_{MIN} \text{ to } T_{MAX}, \text{ unless otherwise noted.}$  Typical values are at  $V_{DD} = +3 V$  and  $T_A = +25 ^{\circ} C.)$

| PARAMETER                          | SYMBOL         | CONDITIONS                                    | MIN | TYP | MAX | UNITS |  |

|------------------------------------|----------------|-----------------------------------------------|-----|-----|-----|-------|--|

| Digital-to-Analog Glitch Impulse   |                | Code 80 hex to code 7F hex                    |     | 90  |     | nVs   |  |

| Wideband Amplifier Noise           |                |                                               |     | 60  |     | μVRMS |  |

| Shutdown Recovery Time             | tsdr           | To ±1/2LSB of final value of V <sub>OUT</sub> |     | 13  |     | μs    |  |

| Time to Shutdown                   | tsdn           | I <sub>DD</sub> < 5µA                         |     | 20  |     | μs    |  |

| POWER SUPPLIES                     | POWER SUPPLIES |                                               |     |     |     |       |  |

| Power-Supply Voltage               | $V_{DD}$       |                                               | 2.7 |     | 5.5 | V     |  |

| Supply Current (Note 6)            | IDD            |                                               |     | 280 | 520 | μΑ    |  |

| Shutdown Current                   |                |                                               |     | 1   | 3   | μΑ    |  |

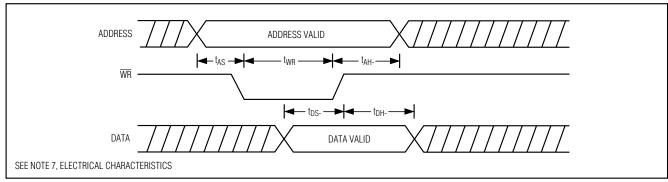

| DIGITAL TIMING (Figure 1) (Note 7) |                |                                               |     |     |     |       |  |

| Address to WR Setup                | tas            |                                               | 5   |     |     | ns    |  |

| Address to WR Hold                 | tah            |                                               | 0   |     |     | ns    |  |

| Data to WR Setup                   | tDS            |                                               | 25  |     |     | ns    |  |

| Data to WR Hold                    | tDH            |                                               | 0   |     |     | ns    |  |

| WR Pulse Width                     | twR            |                                               | 20  |     |     | ns    |  |

- Note 1: Reduced digital code range (code 00 hex to code F0 hex) due to swing limitations when the output amplifier is loaded.

- Note 2: Gain error is: [100 (V<sub>F0,meas</sub> ZCE V<sub>F0,ideal</sub>) / V<sub>DD</sub>]. Where V<sub>F0,meas</sub> is the DAC output voltage with input code F0 hex, and V<sub>F0,ideal</sub> is the ideal DAC output voltage with input code F0 hex (i.e., V<sub>DD</sub> 240 / 256).

- Note 3: Output settling time is measured from the 50% point of the falling edge of WR to ±1/2LSB of Vour's final value.

- **Note 4:** Channel-to-Channel Isolation is defined as the glitch energy at a DAC output in response to a full-scale step change on any other DAC output. The measured channel has a fixed code of 80 hex.

- Note 5: Digital Feedthrough is defined as the glitch energy at any DAC output in response to a full-scale step change on all eight data inputs with WR at V<sub>DD</sub>.

- **Note 6:**  $R_L = \infty$ , digital inputs at GND or  $V_{DD}$ .

- Note 7: Timing measurement reference level is (V<sub>IH</sub> + V<sub>IL</sub>) / 2.

Figure 1. Timing Diagram

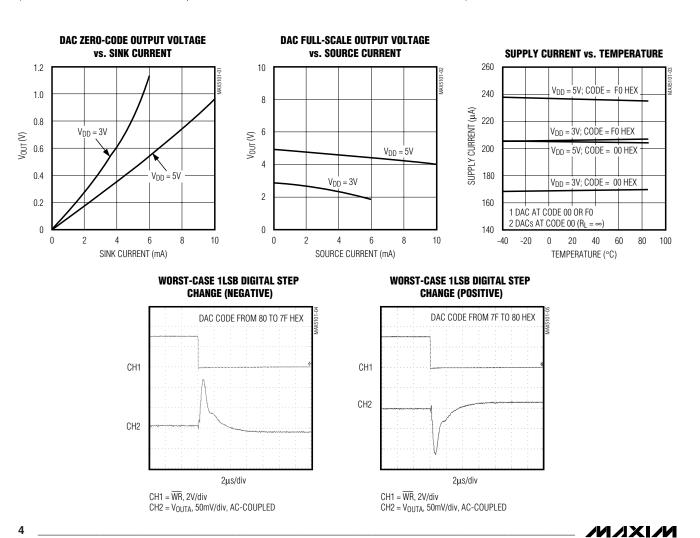

## **Typical Operating Characteristics**

$(V_{DD} = +3V, R_L = 10k\Omega, C_L = 100pF, code = FF hex, T_A = +25°C, unless otherwise noted.)$

## Typical Operating Characteristics (continued)

$(V_{DD} = +3V, R_L = 10k\Omega, C_L = 100pF, code = FF hex, T_A = +25^{\circ}C, unless otherwise noted.)$

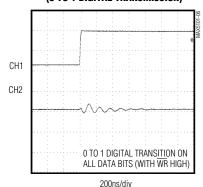

#### DIGITAL FEEDTHROUGH GLITCH IMPULSE (0 TO 1 DIGITAL TRANSMISSION)

CH1 = D7, 2V/div CH2 = V<sub>OUTA</sub>, 1mV/div, AC-COUPLED

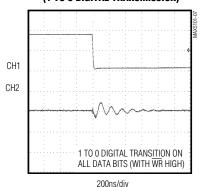

## DIGITAL FEEDTHROUGH GLITCH IMPULSE (1 TO 0 DIGITAL TRANSMISSION)

CH1 = D7, 2V/div CH2 = V<sub>OUTB</sub>, 1mV/div, AC-COUPLED

#### POSITIVE SETTLING TIME

$CH1 = \overline{WR}, 2V/div$  $CH2 = V_{OUTA}, 2V/div$

#### **NEGATIVE SETTLING TIME**

$\begin{aligned} \text{CH1} &= \overline{\text{WR}}, \, 2\text{V/div} \\ \text{CH2} &= \text{V}_{\text{OUTA}}, \, 2\text{V/div} \end{aligned}$

## INTEGRAL AND DIFFERENTIAL NONLINEARITY

### **Pin Description**

|      |                 | · · · · · · · · · · · · · · · · · · ·                                                         |  |  |

|------|-----------------|-----------------------------------------------------------------------------------------------|--|--|

| PIN  | NAME            | FUNCTION                                                                                      |  |  |

| 1    | OUTB            | DAC B Voltage Output                                                                          |  |  |

| 2    | OUTA            | DAC A Voltage Output                                                                          |  |  |

| 3    | V <sub>DD</sub> | Positive Supply Voltage. Bypass VDD to GND using a 0.1µF capacitor.                           |  |  |

| 4    | WR              | Write Input (active low). Use WR to load data into the DAC input latch selected by A0 and A1. |  |  |

| 5–12 | D7-D0           | Data Inputs 7–0                                                                               |  |  |

| 13   | A1              | DAC Address Select Bit (MSB)                                                                  |  |  |

| 14   | A0              | DAC Address Select Bit (LSB)                                                                  |  |  |

| 15   | GND             | Ground                                                                                        |  |  |

| 16   | OUTC            | DAC C Voltage Output                                                                          |  |  |

### **Detailed Description**

#### **Digital-to-Analog Section**

The MAX5101 uses a matrix decoding architecture for the digital-to-analog converters (DACs). The internal reference voltage is connected to VDD and divided down by a resistor string placed in a matrix fashion. Row and column decoders select the appropriate tab from the resistor string to provide the needed analog voltages. The resistor network converts the 8-bit digital input into an equivalent analog output voltage in proportion to the supply voltage (VDD). The resistor string presents a code-independent input impedance to the supply and guarantees a monotonic output.

The voltages are buffered by rail-to-rail op amps connected in a follower configuration to provide a rail-to-rail output (see *Functional Diagram*).

#### **Output Buffer Amplifiers**

The DAC outputs are internally buffered by a precision amplifier with a typical slew rate of 0.6V/µs. The typical settling time to  $\pm 1/2 LSB$  at the output is 6µs when loaded with  $10k\Omega$  in parallel with 100pF.

#### **DAC Reference Voltage**

The MAX5101's reference is internally tied to  $V_{DD}$ . The output voltage ( $V_{OUT}$ ) for any DAC is represented by a digitally programmable voltage source as follows:

$V_{OUT} = (N_B \cdot V_{DD}) / 256$

where  $\ensuremath{\mathsf{N}}\xspace_B$  is the numeric value of the DAC binary input code.

#### **Digital Inputs and Interface Logic**

In the MAX5101, address lines A0 and A1 select the DAC that receives data from D0-D7, as shown in Table 1. When WR is low, the addressed DAC's input latch is transparent. Data is latched when WR is high. The DAC outputs (OUTA, OUTB) represent the data held in the three 8-bit input latches. To avoid output glitches in the MAX5101, ensure that data is valid before WR goes low.

#### **Low-Power Shutdown Mode**

The MAX5101 features a software shutdown mode. A write performed to address A1 = H and A0 = H causes the device to shut down. A subsequent write to any of the other three addresses disables shutdown and turns the analog circuitry on. As the MAX5101 comes out of shutdown, all registers retain their digital values prior to shutdown. However, when the device powers up (i.e., VDD ramps up), all latches are internally preset with code 00 hex. In shutdown, the output amplifiers enter a high-impedance state. When bringing the device out of shutdown, allow 13µs for the output to stabilize.

#### Power-Supply Bypassing and Ground Management

Digital or AC transient signals on GND can create noise at the analog output. Return GND to the highest-quality ground available. Bypass V<sub>DD</sub> with a 0.1µF capacitor, located as close to V<sub>DD</sub> and GND as possible.

Careful PC board ground layout minimizes crosstalk between the DAC outputs and digital inputs.

TRANSISTOR COUNT: 6848

## Table 1. MAX5101 Addressing Table (partial)

| WR | <b>A</b> 1 | A0 | OPERATION                     |

|----|------------|----|-------------------------------|

| Н  | Х          | Х  | Input data latched            |

| L  | L          | L  | DAC A input latch transparent |

| L  | L          | Н  | DAC A input latch transparent |

| L  | Н          | L  | DAC A input latch transparent |

| L  | Н          | Н  | Enter shutdown mode           |

H = high state, L = low state, X = don't care

\_\_\_\_\_Chip Information

## **Package Information**

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

8 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600

© 1999 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.