#### General Description

The MAX503 is a low-power, 10-bit, voltage-output digital-to-analog converter (DAC) that uses single 5V or dual  $\pm5V$  supplies. This device has an internal voltage reference plus an output buffer amplifier. Operating current is only 250µA from a single 5V supply, making it ideal for portable and battery-powered applications. In addition, the shrink small-outline package (SSOP) measures only 0.1 square inches, using less board area than an 8-pin DIP. 10-bit resolution is achieved through laser trimming of the DAC, op amp, and reference. No further adjustments are necessary.

Internal gain-setting resistors can be used to define a DAC output voltage range of 0V to +2.048V, 0V to +4.096V, or ±2.048V. Four-quadrant multiplication is possible without the use of external resistors or op amps. The parallel logic inputs are double buffered and are compatible with 4-bit, 8-bit, and 16-bit microprocessors. For a hardware and software compatible 12-bit upgrade, refer to the MAX530 data sheet. For DACs with similar features but with a serial data interface, refer to the MAX504/MAX515 data sheet.

#### Applications

Battery-Powered Data-Conversion Products

Minimum Component-Count Analog Systems

Digital Offset/Gain Adjustment

Industrial Process Control

Arbitrary Function Generators

Automatic Test Equipment

Microprocessor-Controlled Calibration

#### \_\_\_\_\_Features

- **♦ Buffered Voltage Output**

- ♦ Internal 2.048V Voltage Reference

- ♦ Operates from Single 5V or Dual ±5V Supplies

- Low Power Consumption: 250μA Operating Current 40μA Shutdown-Mode Current

- ♦ SSOP Package Saves Space

- Relative Accuracy: ±1/2 LSB Max Over Temperature

- Guaranteed Monotonic Over Temperature

- 4-Quadrant Multiplication with No External Components

- **♦ Power-On Reset**

- ♦ Double-Buffered Parallel Logic Inputs

#### Ordering Information

| PART      | TEMP. RANGE    | PIN-PACKAGE           |

|-----------|----------------|-----------------------|

| MAX503CNG | 0°C to +70°C   | 24 Narrow Plastic DIP |

| MAX503CWG | 0°C to +70°C   | 24 Wide SO            |

| MAX503CAG | 0°C to +70°C   | 24 SSOP               |

| MAX503ENG | -40°C to +85°C | 24 Narrow Plastic DIP |

| MAX503EWG | -40°C to +85°C | 24 Wide SO            |

| MAX503EAG | -40°C to +85°C | 24 SSOP               |

Refer to the MAX530 for military temperature or die equivalents.

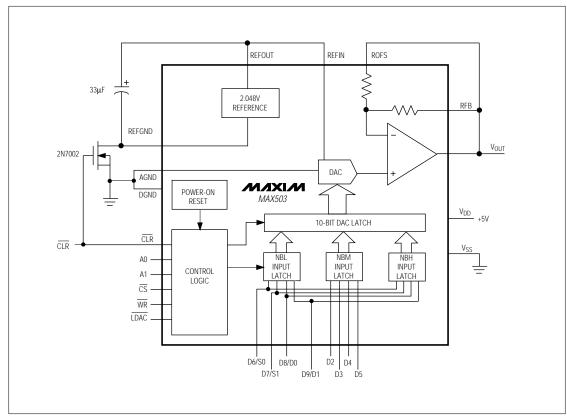

#### Functional Diagram

#### REFOUT REFIN ROFS 18 RFB 2.048V REFERENCE VOUT REFGND AGND DAC POWER-ON $V_{DD}$ RESET DGND 19 10-BIT DAC LATCH $V_{SS}$ CLR A0 8 9 A1 NRM 11 CONTROL cs LOGIC 10 WR LDAC D8/D0 D2 D4

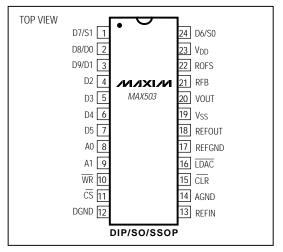

#### Pin Configuration

MIXIM

Maxim Integrated Products 1

Call toll free 1-800-998-8800 for free samples or literature.

#### **ABSOLUTE MAXIMUM RATINGS**

| V <sub>DD</sub> to DGND and V <sub>DD</sub> to AGN | D0.3V, +6V                                         |

|----------------------------------------------------|----------------------------------------------------|

| VSS to DGND and VSS to AGNI                        | 06V, +0.3V                                         |

| V <sub>DD</sub> to V <sub>SS</sub>                 | 0.3V, +12V                                         |

| AGND to DGND                                       | 0.3V, +0.3V                                        |

| REFGND to AGND                                     | 0.3V, (V <sub>DD</sub> + 0.3V)                     |

| Digital Input Voltage to DGND                      | 0.3V, (V <sub>DD</sub> + 0.3V)                     |

| REFIN                                              | (Vss - 0.3V), (Vpp + 0.3V)                         |

| REFOUT                                             | (V <sub>SS</sub> - 0.3V), (V <sub>DD</sub> + 0.3V) |

| REFOUT to REFGND                                   | 0.3V, (V <sub>DD</sub> + 0.3V)                     |

| RFB                                                | (Vss - 0.3V), (Vpp + 0.3V)                         |

| ROFS                                               | (V <sub>SS</sub> - 0.3V), (V <sub>DD</sub> + 0.3V) |

|                                                    |                                                    |

| VOUT to AGND (Note 1)                                   | DD<br>nA |

|---------------------------------------------------------|----------|

| Continuous Power Dissipation ( $T_A = +70$ °C)          |          |

| Narrow Plastic DIP (derate 13.33mW/°C above +70°C)1067n | ηW       |

| Wide SO (derate 11.76mW/°C above +70°C) 941m            | ٦W       |

| SSOP (derate 8.00mW/°C above +70°C)640m                 | ٦W       |

| Operating Temperature Ranges                            |          |

| MAX503C_G0°C to +70                                     | °С       |

| MAX503E_G40°C to +85                                    | °C       |

| Storage Temperature Range65°C to +165                   | °C       |

| Lead Temperature (soldering, 10sec)+300                 | °C       |

|                                                         |          |

Note 1: The output may be shorted to  $V_{DD}$ ,  $V_{SS}$ , DGND, or AGND if the continuous package power dissipation and current ratings are not exceeded. Typical short-circuit currents are 20mA.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ELECTRICAL CHARACTERISTICS—Single +5V Supply**

$(V_{DD}=5V, V_{SS}=0V, AGND=DGND=REFGND=0V, REFIN=2.048V (external), RFB=ROFS=VOUT, C_{REFOUT}=33\mu F, R_L=10k\Omega, C_L=100pF, TA=TMIN to TMAX, unless otherwise noted.)$

| PARAMETER                                  | SYMBOL CONDITIONS |                                                               | MIN | TYP  | MAX                   | UNITS  |  |  |

|--------------------------------------------|-------------------|---------------------------------------------------------------|-----|------|-----------------------|--------|--|--|

| STATIC PERFORMANCE                         |                   |                                                               |     |      |                       |        |  |  |

| Resolution                                 | N                 |                                                               | 10  |      |                       | Bits   |  |  |

| Relative Accuracy                          | INL               | (Note 2)                                                      |     |      | ±0.5                  | LSB    |  |  |

| Differential Nonlinearity                  | DNL               | Guaranteed monotonic                                          |     |      | ±1                    | LSB    |  |  |

| Unipolar Offset Error                      | Vos               |                                                               | 0   | 0.25 | 3                     | LSB    |  |  |

| Unipolar Offset<br>Temperature Coefficient | TCVos             |                                                               |     | 3    |                       | ppm/°C |  |  |

| Unipolar Offset-Error<br>Supply Rejection  | PSRR              | 4.5V ≤ V <sub>DD</sub> ≤ 5.5V                                 |     | 0.1  |                       | LSB/V  |  |  |

| Gain Error (Note 2)                        | GE                | DAC latch = all 1s,<br>VOUT < V <sub>DD</sub> - 0.4V (Note 2) |     |      | ±1                    | LSB    |  |  |

| Gain-Error Temperature Coefficient         |                   |                                                               |     | 1    |                       | ppm/°C |  |  |

| Gain-Error Power-Supply Rejection          | PSRR              | $4.5V \le V_{DD} \le 5.5V$                                    |     | 0.1  |                       | LSB/V  |  |  |

| DAC VOLTAGE OUTPUT (VOUT                   | Γ)                |                                                               |     |      |                       |        |  |  |

| Output Voltage Range                       |                   |                                                               | 0   |      | V <sub>DD</sub> - 0.4 | V      |  |  |

| Resistive Load                             |                   | VOUT = 2V, load regulation ≤ ±0.5LSB                          | 2   |      |                       | kΩ     |  |  |

| DC Output Impedance                        |                   |                                                               |     | 0.2  |                       | Ω      |  |  |

| Short-Circuit Current                      | I <sub>SC</sub>   |                                                               |     | 12   |                       | mA     |  |  |

| REFERENCE INPUT (REFIN)                    | •                 |                                                               | •   |      |                       |        |  |  |

| Reference Input Range                      |                   |                                                               | 0   |      | V <sub>DD</sub> - 2   | V      |  |  |

| Reference Input Resistance                 |                   | Code dependent, minimum at code 0101                          | 40  |      |                       | kΩ     |  |  |

| Reference Input Capacitance                |                   | Code dependent (Note 3)                                       | 10  |      | 50                    | pF     |  |  |

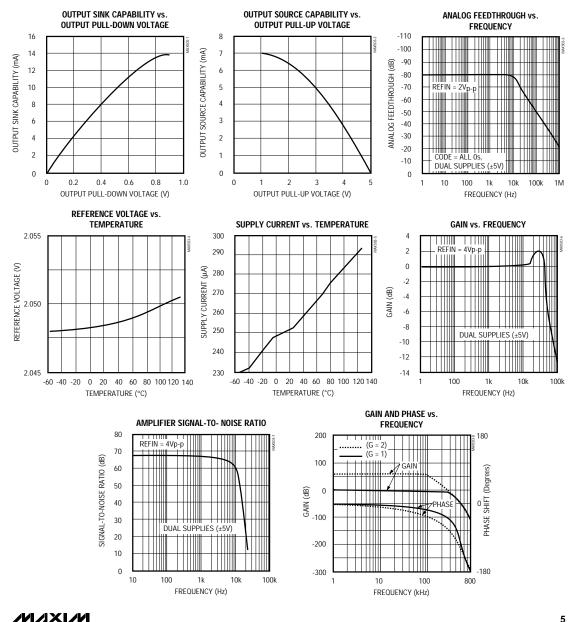

| AC Feedthrough                             |                   | (Note 4)                                                      |     | -80  |                       | dB     |  |  |

#### ELECTRICAL CHARACTERISTICS—Single +5V Supply (continued)

$(V_{DD}=5V,\,V_{SS}=0V,\,AGND=DGND=REFGND=0V,\,REFIN=2.048V\,\,(external),\,RFB=ROFS=VOUT,\,C_{REFOUT}=33\mu F,\,R_L=10k\Omega,\,C_L=100pF,\,T_A=T_{MIN}\,\,to\,T_{MAX},\,unless\,\,otherwise\,\,noted.)$

| PARAMETER                              | SYMBOL            | CONDITIONS                                                   | MIN   | TYP   | MAX   | UNITS  |  |

|----------------------------------------|-------------------|--------------------------------------------------------------|-------|-------|-------|--------|--|

| REFERENCE OUTPUT (REFOL                | JT)               | 1                                                            |       |       |       |        |  |

|                                        |                   | $T_A = +25^{\circ}C$                                         | 2.024 | 2.048 | 2.072 |        |  |

| Reference Tolerance                    | VREFOUT           | MAX503C                                                      |       |       | 2.081 | V      |  |

|                                        |                   | MAX503E                                                      | 2.011 |       | 2.085 | 1      |  |

| Reference Output Resistance            | RREFOUT           | (Note 5)                                                     |       |       | 2     | Ω      |  |

| Power-Supply Rejection Ratio           | PSRR              | $4.5V \le V_{DD} \le 5.5V$                                   |       | 200   |       | μV/V   |  |

| Noise Voltage                          | en                | 0.1Hz to 10kHz                                               |       | 400   |       | µVр-р  |  |

| Temperature Coefficient                |                   |                                                              |       | 30    |       | ppm/°C |  |

| Required External Capacitor            | CREFOUT           |                                                              | 3.3   |       |       | μF     |  |

| DYNAMIC PERFORMANCE                    | 1                 |                                                              |       |       |       |        |  |

| Voltage Output Slew Rate               |                   | TA = +25°C                                                   | 0.15  | 0.25  |       | V/µs   |  |

| Voltage Output Settling Time           |                   | To ±0.5LSB, VOUT = 2V                                        |       | 25    |       | μs     |  |

| Digital Feedthrough                    |                   | $\overline{WR} = V_{DD}$ , digital inputs all 1s to all 0s   |       | 5     |       | nV-s   |  |

| Signal-to-Noise Plus                   | CINIAD            | Unity gain (Note 4)                                          |       | 68    |       | -ID    |  |

| Distortion Ratio                       | SINAD             | Gain = 2 (Note 4)                                            |       | 68    | dB    |        |  |

| DIGITAL INPUTS (S0, S1, D0-E           | 9, LDAC, C        | LR, CS, WR, A0, A1)                                          |       |       |       |        |  |

| Logic High Input                       | VIH               |                                                              | 2.4   |       |       | V      |  |

| Logic Low Input                        | V <sub>IL</sub>   |                                                              |       |       | 0.8   | V      |  |

| Digital Leakage Current                |                   | V <sub>IN</sub> = 0V or V <sub>DD</sub>                      |       |       | ±1    | μΑ     |  |

| Digital Input Capacitance              |                   |                                                              |       | 8     |       | pF     |  |

| POWER SUPPLIES                         | •                 |                                                              | •     |       |       |        |  |

| Positive Supply-Voltage Range          | $V_{DD}$          |                                                              | 4.5   |       | 5.5   | V      |  |

| Positive Supply Current                | I <sub>DD</sub>   | Outputs unloaded, all digital inputs = 0V or V <sub>DD</sub> |       | 250   | 400   | μΑ     |  |

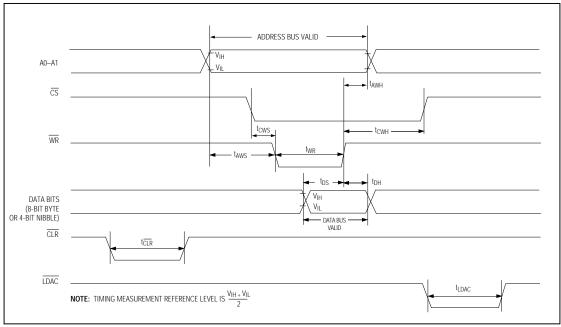

| SWITCHING CHARACTERISTIC               | cs                |                                                              |       |       |       |        |  |

| Address to WR Setup                    | t <sub>AWS</sub>  |                                                              | 5     |       |       | ns     |  |

| Address to WR Hold                     | tawh              |                                                              | 5     |       |       | ns     |  |

| CS to WR Setup                         | tcws              |                                                              | 0     |       |       | ns     |  |

| CS to WR Hold                          | tcwH              |                                                              | 0     |       |       | ns     |  |

| Data to WR Setup                       | t <sub>DS</sub>   |                                                              | 45    |       |       | ns     |  |

| Data to WR Hold                        | t <sub>DH</sub>   |                                                              | 0     |       |       | ns     |  |

| WR Pulse Width                         | twR               |                                                              | 45    |       |       | ns     |  |

| LDAC Pulse Width                       | t <sub>LDAC</sub> |                                                              | 45    |       |       | ns     |  |

| CLR Pulse Width                        | t <sub>CLR</sub>  |                                                              | 45    |       |       | ns     |  |

| Internal Power-On Reset<br>Pulse Width | tpor              | (Note 3)                                                     |       | 1.3   | 10    | μs     |  |

#### **ELECTRICAL CHARACTERISTICS—Dual ±5V Supplies**

$(V_{DD}=5V,\,V_{SS}=-5V,\,AGND=DGND=REFGND=0V,\,REFIN=2.048V\,\,(external),\,RFB=ROFS=VOUT,\,C_{REFOUT}=33\mu F,\,R_{L}=10k\Omega,\,C_{L}=100pF,\,T_{A}=T_{MIN}\,to\,T_{MAX},\,unless\,otherwise\,noted.)$

| PARAMETER                                      | SYMBOL              | CONDITIONS                                                   | MIN            | TYP    | MAX                   | UNITS  |

|------------------------------------------------|---------------------|--------------------------------------------------------------|----------------|--------|-----------------------|--------|

| STATIC PERFORMANCE                             |                     |                                                              |                |        |                       | ı      |

| Resolution                                     | N                   |                                                              | 10             |        |                       | Bits   |

| Relative Accuracy                              | INL                 |                                                              |                |        | +0.5                  | LSB    |

| Differential Nonlinearity                      | DNL                 | Guaranteed monotonic                                         |                |        | ±1                    | LSB    |

| Bipolar Offset Error                           | Vos                 |                                                              |                |        | ±3                    | LSB    |

| Bipolar Offset<br>Temperature Coefficient      | TCVos               |                                                              |                | 3      |                       | ppm/°C |

| Bipolar Offset-Error<br>Power-Supply Rejection | PSRR                | $4.5V \le V_{DD} \le 5.5V$ , $-5.5V \le V_{SS} \le -4.5V$    |                | 0.1    |                       | LSB/V  |

| Gain Error                                     |                     |                                                              |                |        | ±1                    | LSB    |

| Gain-Error Temperature Coefficient             | TC                  |                                                              |                | 1      |                       | ppm/°C |

| Gain-Error Power-Supply Rejection              | PSRR                | $4.5V \le V_{DD} \le 5.5V$ , $-5.5V \le V_{SS} \le -4.5V$    |                | 0.1    |                       | LSB/V  |

| DAC VOLTAGE OUTPUT (VOU                        | Γ)                  |                                                              | •              |        |                       |        |

| Output Voltage Range                           |                     |                                                              | $V_{SS} + 0.4$ |        | V <sub>DD</sub> - 0.4 | V      |

| Resistive Load                                 |                     | VOUT = 2V, load regulation ≤ ±0.5LSB                         | 2              |        |                       | kΩ     |

| DC Output Impedance                            |                     |                                                              |                | 0.2    |                       | Ω      |

| Short-Circuit Current                          | I <sub>SC</sub>     |                                                              |                | 20     |                       | mA     |

| REFERENCE INPUT (REFIN)                        |                     |                                                              | 1              |        |                       |        |

| Reference Input Range                          |                     |                                                              | Vss + 2        |        | V <sub>DD</sub> - 2   | V      |

| Reference Input Resistance                     |                     | Code dependent, minimum at code 0101                         | 40             |        |                       | kΩ     |

| Reference Input Capacitance                    |                     | Code dependent (Note 3)                                      | 10             |        | 50                    | pF     |

| AC Feedthrough                                 |                     | (Note 4)                                                     |                | -80    |                       | dB     |

| REFERENCE OUTPUT (REFOU                        | <b>T)</b> —Specific | cations are identical to those under Single +5V Sup          | pply           |        |                       |        |

| DYNAMIC PERFORMANCE—Sp                         | ecifications        | s are identical to those under Single +5V Supply             |                |        |                       |        |

| DIGITAL INPUTS (S0, S1, D0-D                   | 9, LDAC, C          | LR, CS, WR, A0, A1)—Specifications are identical             | to those un    | der Si | ngle +5V S            | Supply |

| POWER SUPPLIES                                 |                     |                                                              |                |        |                       |        |

| Positive Supply Voltage                        | V <sub>DD</sub>     |                                                              | 4.5            |        | 5.5                   | V      |

| Negative Supply Voltage                        | Vss                 |                                                              | -5.5           |        | 0                     | V      |

| Positive Supply Current                        | I <sub>DD</sub>     | Outputs unloaded, all digital inputs = 0V or V <sub>DD</sub> |                | 250    | 400                   | μΑ     |

| Negative Supply Current                        | I <sub>SS</sub>     | Outputs unloaded, all digital inputs = 0V or V <sub>DD</sub> |                | 150    | 200                   | μΑ     |

| SWITCHING CHARACTERISTIC                       | <b>S</b> —Specific  | cations are identical to those under Single +5V Sup          | ply            |        |                       |        |

Note 2: In single supply, INL and GE are calculated from code 3 to code 1023 (code excludes S0 and S1).

Note 3: Guaranteed by design.

Note 4: REFIN = 1kHz, 2.0Vp-p.

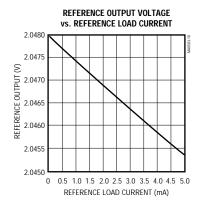

Note 5: Tested at I<sub>OUT</sub> = 100µA. The reference can typically source up to 5mA (see *Typical Operating Characteristics*).

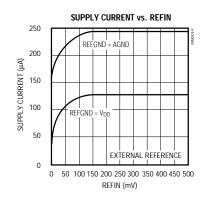

#### Typical Operating Characteristics

(Single +5V supply, unity gain, code = all 1s,  $T_A = +25$ °C, unless otherwise noted.)

#### \_Typical Operating Characteristics (continued)

(Single +5V supply, unity gain, code = all 1s,  $T_A = +25$ °C, unless otherwise noted.)

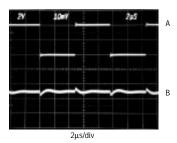

#### DIGITAL FEEDTHROUGH

A: S0, S1, D0–D9 = 100kHz, 4Vp-p <u>B: V0UT, 10mV/div</u> <u>LDAC</u> = <u>CS</u> = HIGH

5µs/div

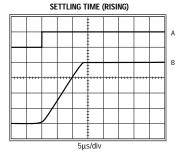

SETTLING TIME (FALLING)

A: DIGITAL INPUTS FALLING EDGE, 5V/div B: VOUT, NO LOAD, 1V/div DUAL SUPPLY (±5V) LDAC = LOW BIPOLAR CONFIGURATION VREFIN = 2V

A: DIGITAL INPUTS RISING EDGE, B: VOUT, NO LOAD, 1V/div DUAL SUPPLY (±5V) LDAC = LOW BIPOLAR CONFIGURATION V<sub>REFIN</sub> = 2V

6

MIXIM

#### \_Pin Description

| PIN | NAME            | FUNCTION                                                                                                                                                                         |

|-----|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1   | D7/S1           | D7 input when A0 = A1 = 1, or S1 input when A0 = 0 and A1 = 1. Always set S1 to 0.*                                                                                              |

| 2   | D8/ D0          | D8 input when A0 = A1 = 1, or D0 input when A0 = 0 and A1 = 1.*                                                                                                                  |

| 3   | D9/ D1          | D9 input when A0 = A1 = 1, or D1 input when A0 = 0 and A1 = 1.*                                                                                                                  |

| 4   | D2              | D2 Input Data, or tie to S0 and multiplex when A0 = 1 and A1 = 0.*                                                                                                               |

| 5   | D3              | D3 Input Data, or tie to S1 and multiplex when A0 = 1 and A1 = 0.*                                                                                                               |

| 6   | D4              | D4 Input Data, or tie to D0 and multiplex when A0 = 1 and A1 = 0.*                                                                                                               |

| 7   | D5              | D5 Input Data, or tie to D1 and multiplex when A0 = 1 and A1 = 0.*                                                                                                               |

| 8   | AO              | Address Line A0. With A1, used to multiplex 4 of 12 data lines to load low (NBL), middle (NBM), and high (NBH) 4-bit nibbles. (12 bits can also be loaded as 8+4.)               |

| 9   | A1              | Address Line A1. Set A0 = A1 = 0 for NBL and NBM, A0 = 0 and A1 = 1 for NBL, A0 = 1 and A1 = 0 for NBM, or A0 = A1 = 1 for NBH. See Table 2 for complete input latch addressing. |

| 10  | WR              | Write Input (active low). Used with $\overline{\text{CS}}$ to load data into the input latch selected by A0 and A1.                                                              |

| 11  | CS              | Chip Select (active low). Enables addressing and writing to this chip from common bus lines.                                                                                     |

| 12  | DGND            | Digital Ground                                                                                                                                                                   |

| 13  | REFIN           | Reference Input. Input for the R-2R DAC. Connect an external reference to this pin or a jumper to REFOUT (pin 18) to use the internal 2.048V reference.                          |

| 14  | AGND            | Analog Ground                                                                                                                                                                    |

| 15  | CLR             | Clear (active low). A low on CLR resets the DAC latches to all 0s.                                                                                                               |

| 16  | LDAC            | Load DAC Input (active low). Driving this asynchronous input low transfers the contents of the input latch to the DAC latch and updates VOUT.                                    |

| 17  | REFGND          | Reference Ground must be connected to AGND when using the internal reference. Connect to V <sub>DD</sub> to disable the internal reference and save power.                       |

| 18  | REFOUT          | Reference Output. Output of the internal 2.048V reference. Tie to REFIN to drive the R-2R DAC.                                                                                   |

| 19  | V <sub>SS</sub> | Negative Power Supply. Usually ground for single-supply or -5V for dual-supply operation.                                                                                        |

| 20  | VOUT            | Voltage Output. Op-amp buffered DAC output.                                                                                                                                      |

| 21  | RFB             | Feedback Pin. Op-amp feedback resistor. Always connect to VOUT.                                                                                                                  |

| 22  | ROFS            | Offset Resistor Pin. Connect to VOUT for G = 1, to AGND for G = 2, or to REFIN for bipolar output.                                                                               |

| 23  | V <sub>DD</sub> | Positive Power Supply (+5V)                                                                                                                                                      |

| 24  | D6/S0           | D6 input when A0 = A1 = 1, or S0 input when A0 = 0 and A1 = 1. Always set S0 to 0.*                                                                                              |

$<sup>^{\</sup>star}$  This applies to 4 + 4 + 4 input loading mode. See Table 2 for 8 + 4 input loading mode.

#### Detailed Description

The MAX503 consists of a parallel-input logic interface, a 10-bit R-2R ladder, a reference, and an op amp. The Functional Diagram shows the control lines and signal flow through the input data latch to the DAC latch, as well as the 2.048V reference and output op amp. Total supply current is typically 250µA with a single +5V supply. This circuit is ideal for battery-powered, microprocessor-controlled applications where high accuracy, no adjustments, and minimum component count are key requirements.

#### R-2R Ladder

The MAX503 uses an "inverted" R-2R ladder network with a BiCMOS op amp to convert 10-bit digital data to analog voltage levels. Figure 1 shows a simplified diagram of the R-2R DAC and op amp. Unlike a standard DAC, the MAX503 uses an "inverted" ladder network. Normally, the REFIN pin is the current output of a standard DAC and would be connected to the summing junction, or virtual ground, of an op amp. In this standard DAC configuration, however, the output voltage would be the inverse of

V— ROFS MIXIM MAX503 OUTPUT BUFFER 2D 2R MSB  $R=80k\boldsymbol{\Omega}$ RFFIN AGND REFOUT DAC LATCH MSB LSB 2.048V NBM NBH REFGND INPUT INPUT INPUT D6/S0 D8/D0 D2 \*SHOWN FOR ALL 1s D9/D1 D3

Figure 1. Simplified MAX503 DAC Circuit

the reference voltage. The MAX503's topology makes the ladder output voltage the same polarity as the reference input, making the device suitable for single-supply operation. The BiCMOS op amp is then used to buffer, invert, or amplify the ladder signal.

Ladder resistors are nominally  $80k\Omega$  to conserve power and are laser trimmed for gain and linearity. The input impedance at REFIN is code dependent. When the DAC register is all 0s, all rungs of the ladder are grounded and REFIN is open or no load. Maximum loading (minimum REFIN impedance) occurs at code 010101.... Minimum reference input impedance at this code is guaranteed to be not less than  $40k\Omega$ .

The REFIN and REFOUT pins allow the user to choose between driving the R-2R ladder with the on-chip reference or an external reference. REFIN may be below analog ground when using dual supplies. See the *External Reference* and *Four-Quadrant Multiplication* sections for more information.

#### Internal Reference

The on-chip reference is laser trimmed to generate 2.048V at REFOUT. The output stage can source and sink current so REFOUT can settle to the correct voltage quickly in response to code-dependent loading changes. Typically, source current is 5mA and sink current is  $100\mu A$ .

REFOUT connects the internal reference to the R-2R DAC ladder at REFIN. The R-2R ladder draws  $50\mu A$  maximum load current. If any other connection is made to REFOUT, ensure that the total load current is less than  $100\mu A$  to avoid gain errors.

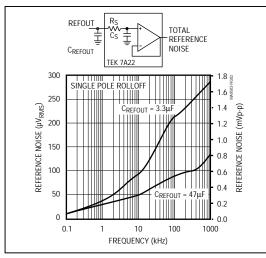

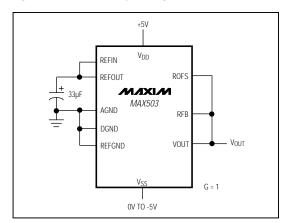

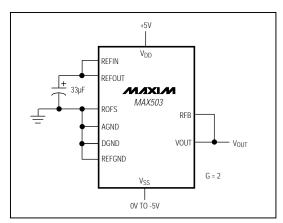

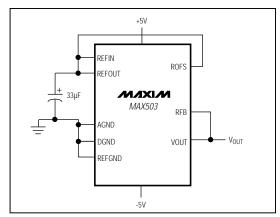

A separate REFGND pin is provided to isolate reference currents from other analog and digital ground currents. To achieve specified noise performance, connect a 33µF capacitor from REFOUT to REFGND (see Figure 2). Using smaller capacitance values increases noise, and values less than 3.3µF may compromise the reference's stability. For applications requiring the lowest noise, insert a buffered RC filter between REFOUT and REFIN. When using the internal reference, REFGND must be connected to AGND. In applications not requiring the internal reference, connect REFGND to VDD, which shuts down the reference. This saves typically 100µA of VDD supply current and eliminates the need for CREFOUT.

8 \_\_\_\_\_\_\_MAXIM

Figure 2. Reference Noise vs. Frequency

#### **Output Buffer**

The output amplifier uses a folded cascode input stage and a type AB output stage. Large output devices with low series resistance allow the output to swing to ground in single-supply operation. The output buffer is unity-gain stable. Input offset voltage and supply current are laser trimmed. Settling time is 25µs to 0.01% of final value. The output is short-circuit protected and can drive a  $2k\Omega$  load with more than 100pF of load capacitance. The op amp may be placed in unity-gain (G = 1), in a gain of two (G = 2), or in a bipolar-output mode by using the ROFS and RFB pins. These pins are used to define a DAC output voltage range of 0V to  $+2.048V,\,0V$  to +4.096V or  $\pm2.048V,\,by$  connecting ROFS to VOUT, GND, or REFIN. RFB is always connected to VOUT. Table 1 summarizes ROFS usage.

Table 1. ROFS Usage

| ROFS<br>CONNECTED TO: | DAC OUTPUT<br>RANGE | OP-AMP<br>GAIN |

|-----------------------|---------------------|----------------|

| VOUT                  | 0V to 2.048V        | G = 1          |

| AGND                  | 0V to 4.096V        | G = 2          |

| REFIN                 | -2.048V to +2.048V  | Bipolar        |

Note: Assumes RFB = VOUT and REFIN = REFOUT = 2.048V

#### External Reference

An external reference in the range ( $V_{SS}$  + 2V) to ( $V_{DD}$  - 2V) may be used with the MAX503 in dual-supply, unity-gain operation. In single-supply, unity-gain operation, the reference must be positive and may not exceed ( $V_{DD}$  - 2V). The reference voltage determines the DAC's full-scale output.

If an upgrade to the internal reference is required, the 2.5V MAX873A is ideal: ±15mV initial accuracy, 7ppm/°C (max) temperature coefficient.

#### Power-On Reset

An internal power-on reset (POR) circuit forces the DAC register to reset to all 0s when  $V_{DD}$  is first applied. The POR pulse is typically 1.3 $\mu$ s; however, it may take 2ms for the internal reference to charge its large filter capacitor and settle to its trimmed value.

In addition to POR, a clear  $(\overline{CLR})$  pin, when held low, sets the DAC register to all 0s.  $\overline{CLR}$  operates asynchronously and independently from chip select  $(\overline{CS})$ . With the DAC input at all 0s, the op-amp output is at zero for unity-gain and G=2 configurations, but it is at -V<sub>REF</sub> for the bipolar configuration.

#### Shutdown Mode

The MAX503 is designed for low power consumption. Understanding the circuit allows power consumption management for maximum efficiency. In single-supply mode ( $V_{DD} = +5V$ ,  $V_{SS} = GND$ ) the initial supply current is typically only 160µA, including the reference, op amp, and DAC. This low current occurs when the power-on reset circuit clears the DAC to all 0s and forces the op-amp output to zero (unipolar mode only). See the Supply Current vs. REFIN graph in the Typical Operating Characteristics. Under this condition, there is no internal load on the reference (DAC = all 0s, REFIN is open circuit) and the op amp operates at its minimum quiescent current. The CLR signal resets the MAX503 to these same conditions and can be used to control a power-saving mode when the DAC is not being used by the system.

MIXIM

Figure 3. Low-Current Shutdown Mode

#### **Table 2. Input Latch Addressing**

| CLR | CS | WR | LDAC | A0 | A1 | DATA UPDATED                                 |

|-----|----|----|------|----|----|----------------------------------------------|

| L   | Χ  | Χ  | Х    | Χ  | Χ  | Reset DAC latches                            |

| Н   | Н  | Χ  | Н    | Χ  | Х  | No operation                                 |

| Н   | Χ  | Н  | Н    | Χ  | Х  | No operation                                 |

| Н   | L  | L  | Н    | Н  | Н  | NBH (D6-D9)                                  |

| Н   | L  | L  | Н    | Н  | L  | NBM (D2-D5)                                  |

| Н   | L  | L  | Н    | L  | Н  | NBL (S0 = 0, S1 = 0,<br>D0, D1)              |

| Н   | Н  | Н  | L    | Χ  | Х  | Update DAC only                              |

| Н   | L  | L  | Х    | L  | L  | NBL and NBM (S0, S1, D0-D5), DAC not updated |

| Н   | L  | L  | L    | Н  | Н  | NBH and update DAC                           |

An additional 110µA of supply current can be saved when the internal reference is not used by connecting REFGND to VDD. A low on-resistance N-channel FET, such as the 2N7002, can be used to turn off the internal reference to create a shutdown mode with minimum current drain (Figure 3). When  $\overline{\text{CLR}}$  is high, the transistor pulls REFGND to AGND and the reference and DAC operate normally. When  $\overline{\text{CLR}}$  goes low, REFGND is pulled up to  $\overline{\text{VDD}}$  and the reference is shut down. At the same time,  $\overline{\text{CLR}}$  resets the DAC register to all 0s, and the op-amp output goes to 0V for unity-gain and G = 2 modes. This reduces the total single-supply operating current from 250µA (400µA max) to typically 40µA in shutdown mode.

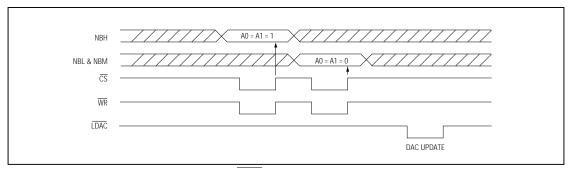

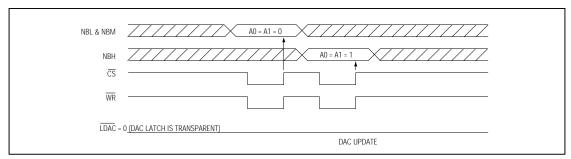

Figure 4. MAX503 Write-Cycle Timing Diagram

A small error voltage is added to the reference output by the reference current flowing through the N-channel pull-down transistor. The switch's on resistance should be less than  $5\Omega$ . A typical reference current of  $100\mu\text{A}$  would add 0.5mV to REFOUT. Since the reference current and on resistance increase with temperature, the overall temperature coefficient will degrade slightly.

As data is loaded into the DAC and the output moves above GND, the op-amp quiescent current increases to its nominal value and the total operating current averages 250 $\mu$ A. Using dual supplies ( $\pm$ 5V), the op amp is fully biased continuously, and the V<sub>DD</sub> supply current is more constant at 250 $\mu$ A. The V<sub>SS</sub> current is typically 150 $\mu$ A.

The MAX503 logic inputs are compatible with TTL and CMOS logic levels. However, to achieve the lowest power dissipation, drive the digital inputs with rail-to-rail CMOS logic. With TTL logic levels, the power requirement increases by a factor of approximately 2.

#### Parallel Logic Interface

In order to provide hardware and software compatibility with the 12-bit MAX530, the MAX503 employs a 12-bit digital interface. As shown in Figure 3, there is actually a 12-bit input latch, and therefore 12 bits of data should be written. The two least significant bits (S1 and S0) are sub-LSB, and must always be 0s. Designed to interface with 4-bit, 8-bit, and 16-bit microprocessors (µPs), the MAX503 uses 8 data pins and double-buffered logic inputs to load data as 4 + 4 + 4 or 8 + 4. The 12-bit DAC latch is updated simultaneously through the control signal LDAC. Signals A0, A1, WR, and CS select which input latches to update. The 12-bit data is broken down into nibbles (NB); NBL is the enable signal for the lowest 4 bits (S0, S1, D0, D1), NBM is the enable for the middle 4 bits, and NBH is the enable for the highest and most significant 4 bits. Table 2 lists the address decoding scheme.

Refer to Figure 4 for the MAX503 write-cycle timing diagram.

**MIXINN**

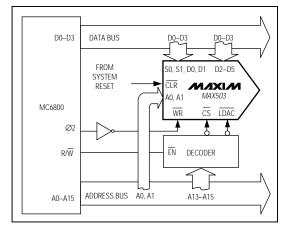

Figure 5. 4-Bit μP Interface

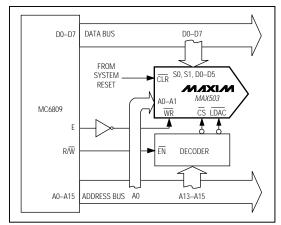

Figure 7. 8-Bit and 16-Bit μP Interface

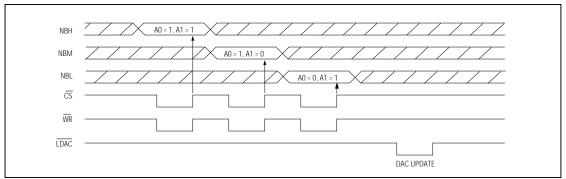

Figure 6. 4-Bit µP Timing Sequence

Figure 8a. 8-Bit and 16-Bit  $\mu P$  Timing Sequence Using  $\overline{LDAC}$

Figure 8b. 8-Bit and 16-Bit  $\mu P$  Timing Sequence with  $\overline{LDAC} = 0$

Figure 9. Unipolar Configuration (0V to +2.048V Output)

Figure 5 shows the circuit configuration for a 4-bit  $\mu P$  application. Figure 6 shows the corresponding timing sequence. The 4 low bits (S0, S1, D0, D1) are connected in parallel to the other 4 bits (D2–D5) and then to the  $\mu P$  bus. Address lines A0 and A1 enable the input data latches for the high, middle, or low data nibbles. The  $\mu P$  sends chip select ( $\overline{CS}$ ) and write ( $\overline{WR}$ ) signals to latch in each of three nibbles in three cycles when the data is valid

Figure 7 shows a typical interface to an 8-bit or a 16-bit  $\mu P.$  Connect 8 data bits from the data bus to pins S0, S1, and D0–D5 on the MAX503. With  $\overline{LDAC}$  held high, the user can load NBH or NBL + NBM in any order. Figure 8a shows the corresponding timing sequence. For fastest throughput, use Figure 8b's sequence. Address lines A0 and A1 are tied together and the DAC is loaded in 2 cycles as 8 + 4. In this scheme, with  $\overline{LDAC}$  held low, the DAC latch is transparent. Always load NBL and NBM first, followed by NBH.

Figure 10. Unipolar Configuration (0V to +4.096V Output)

$\overline{\text{LDAC}}$  is asynchronous with respect to  $\overline{\text{WR}}.$  If  $\overline{\text{LDAC}}$  is brought low before or at the same time  $\overline{\text{WR}}$  goes high,  $\overline{\text{LDAC}}$  must remain low for at least 50ns to ensure the correct data is latched. Data is latched into DAC registers on  $\overline{\text{LDAC}}$ 's rising edge.

#### **Unipolar Configuration**

The MAX503 is configured for a 0V to  $V_{REFIN}$  unipolar output range by connecting ROFS and RFB to VOUT (Figure 9). The converter operates from either single or dual supplies in this configuration. See Table 3 for the DAC-latch contents (input) vs. the analog VOUT (output). In this range, 1LSB =  $V_{REFIN}$  (2 -10).

A 0V to 2V<sub>REFIN</sub> unipolar output range is set up by connecting ROFS to AGND and RFB to VOUT (Figure 10). Table 4 shows the DAC-latch contents vs. VOUT. The MAX503 operates from either single or dual supplies in this mode. In this range, 1LSB =  $(2)(V_{REFIN})(2^{-10}) = (V_{REFIN})(2^{-9})$ .

NIXIN

## Table 3. Unipolar Binary Code Table (0V to VREFIN Output), Gain = 1

|      | INPUT | *      | OUTPUT                                       |

|------|-------|--------|----------------------------------------------|

| 1111 | 1111  | 11(00) | (V <sub>REFIN</sub> ) $\frac{1023}{1024}$    |

| 1000 | 0000  | 01(00) | (V <sub>REFIN</sub> ) $\frac{513}{1024}$     |

| 1000 | 0000  | 00(00) | $(V_{REFIN})\frac{512}{1024} = +V_{REFIN}/2$ |

| 0111 | 1111  | 11(00) | (V <sub>REFIN</sub> ) 511 1024               |

| 0000 | 0000  | 01(00) | (V <sub>REFIN</sub> ) 1/1024                 |

| 0000 | 0000  | 00(00) | OV                                           |

<sup>\*</sup> Write 10-bit data words with two sub-LSB 0s because the DAC input latch is 12 bits wide.

#### **Bipolar Configuration**

A -V<sub>REFIN</sub> to +V<sub>REFIN</sub> bipolar range is set up by connecting ROFS to REFIN and RFB to VOUT, and operating from dual ( $\pm$ 5V) supplies (Figure 11). Table 5 shows the DAC-latch contents (input) vs. VOUT (output). In this range, 1LSB = V<sub>REFIN</sub> (2 -9).

#### Four-Quadrant Multiplication

The MAX503 can be used as a four-quadrant multiplier by connecting ROFS to REFIN and RFB to VOUT, and using (1) an offset binary digital code, (2) bipolar power supplies, and (3) a bipolar analog input at REFIN within the range V<sub>SS</sub> + 2V to V<sub>DD</sub> - 2V, as shown in Figure 12.

In general, a 10-bit DAC's output is  $D(V_{REFIN})(G)$ , where "G" is the gain (1 or 2) and "D" is the binary representation of the digital input divided by  $2^{10}$  or 1,024. This formula is precise for unipolar operation. However, for bipolar, offset binary operation, the MSB is really a polarity bit. No resolution is lost because the number of steps is the same. The output voltage, however, has been shifted from a range of, for example, 0V to 4.096V (G=2) to a range of -2.048V to +2.048V.

Keep in mind that when using the DAC as a four-quadrant multiplier, the scale is skewed. The negative full scale is -VREFIN, while the positive full scale is +VREFIN - 1LSB.

Table 4. Unipolar Binary Code Table (0V to 2VREFIN Output), Gain = 2

|      | INPUT | *      | OUTPUT                                                 |

|------|-------|--------|--------------------------------------------------------|

| 1111 | 1111  | 11(00) | +2 (V <sub>REFIN</sub> ) 1023<br>1024                  |

| 1000 | 0000  | 01(00) | +2 (V <sub>REFIN</sub> ) $\frac{513}{1024}$            |

| 1000 | 0000  | 00(00) | $+2 \text{ (V}_{REFIN}) \frac{512}{1024} = +V_{REFIN}$ |

| 0111 | 1111  | 11(00) | +2 (V <sub>REFIN</sub> ) 511<br>1024                   |

| 0000 | 0000  | 01(00) | +2 (V <sub>REFIN</sub> ) 1/1024                        |

| 0000 | 0000  | 00(00) | OV                                                     |

<sup>\*</sup> Write 10-bit data words with two sub-LSB 0s because the DAC input latch is 12 bits wide.

## Table 5. Bipolar (Offset Binary) Code Table (-VREFIN to +VREFIN Output)

|      | INPUT | *      | ОИТРИТ                                     |

|------|-------|--------|--------------------------------------------|

| 1111 | 1111  | 11(00) | (+V <sub>REFIN</sub> ) $\frac{511}{512}$   |

| 1000 | 0000  | 01(00) | (+V <sub>REFIN</sub> ) 1/512               |

| 1000 | 0000  | 00(00) | 0V                                         |

| 0111 | 1111  | 11(00) | (-V <sub>REFIN</sub> ) 1/512               |

| 0000 | 0000  | 01(00) | (-V <sub>REFIN</sub> ) 511 512             |

| 0000 | 0000  | 00(00) | $(-V_{REFIN})\frac{512}{512} = -V_{REFIN}$ |

<sup>\*</sup> Write 10-bit data words with two sub-LSB 0s because the DAC input latch is 12 bits wide.

4 \_\_\_\_\_\_MXIM

Figure 11. Bipolar Configuration (-2.048V to +2.048V Output)

# VDD REFIN ROFS REFGND ROFS AGND MAX503 RFB DGND VOUT Vout

Figure 12. Four-Quadrant Multiplying Circuit

#### Applications Information

#### Single-Supply Linearity

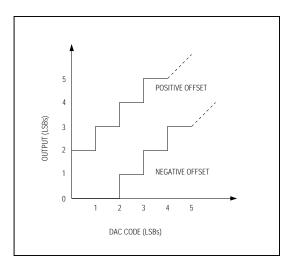

As with any amplifier, the MAX503's output op amp offset can be positive or negative. When the offset is positive, it is easily accounted for. However, when the offset is negative, the output cannot follow linearly when there is no negative supply. In that case, the amplifier output (VOUT) remains at ground until the DAC voltage is sufficient to overcome the offset and the output becomes positive. The resulting transfer function is shown in Figure 13.

Normally, linearity is measured after allowing for zero error and gain error. Since, in single-supply operation, the actual value of a negative offset is unknown, it cannot be accounted for during test. In the MAX503, linearity and gain error are measured from code 3 to code 1023 (see Note 2 under *Electrical Characteristics*). The output amplifier offset does not affect monotonicity, and these DACs are guaranteed monotonic starting with code zero. In dual-supply operation, linearity and gain error are measured from code 0 to 1023.

#### Power-Supply Bypassing and Ground Management

Best system performance is obtained with printed circuit boards that use separate analog and digital ground planes. Wire-wrap boards are not recommended. The two ground planes should be connected together at the low-impedance power-supply source.

AGND and REFGND should be connected together, and then to DGND at the chip. For single-supply applications, connect Vss to AGND at the chip. The best

ground connection may be achieved by connecting the AGND, REFGND, and DGND pins together and connecting that point to the system analog ground plane. If DGND is connected to the system digital ground, digital noise may get through to the DAC's analog portion.

Bypass V<sub>DD</sub> (and V<sub>SS</sub> in dual-supply mode) with a  $0.1\mu F$  ceramic capacitor connected between V<sub>DD</sub> and AGND (and between V<sub>SS</sub> and AGND). Mount the capacitors with short leads close to the device.

#### **AC Considerations**

#### Digital Feedthrough

High-speed data at any of the digital input pins may couple through the DAC package and cause internal stray capacitance to appear as noise at the DAC output, even though  $\overline{\text{LDAC}}$  and  $\overline{\text{CS}}$  are held high (see *Typical Operating Characteristics*). This digital feedthrough is tested by holding  $\overline{\text{LDAC}}$  and  $\overline{\text{CS}}$  high and toggling the data inputs from all 1s to all 0s.

#### Analog Feedthrough

Because of internal stray capacitance, higher-frequency analog input signals at REFIN may couple to the output, even when the input digital code is all 0s, as shown in the *Typical Operating Characteristics* graph Analog Feedthrough vs. Frequency. It is tested by setting CLR to low (which sets the DAC latches to all 0s) and sweeping REFIN.

Figure 13. Single-Supply DAC Transfer Function

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

16 \_\_\_\_\_\_Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 (408) 737-7600

© 1994 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.