## 24-bit 192kHz 2Vrms Multi-Channel CODEC

#### **DESCRIPTION**

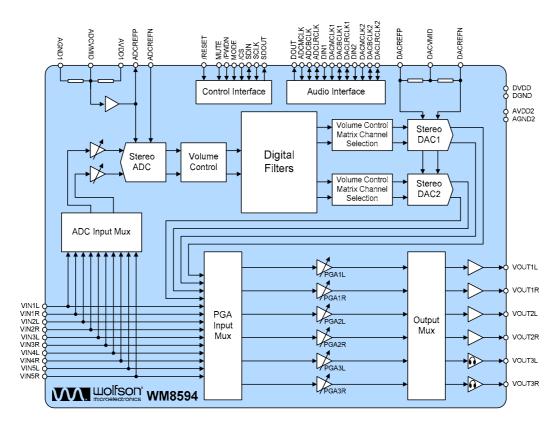

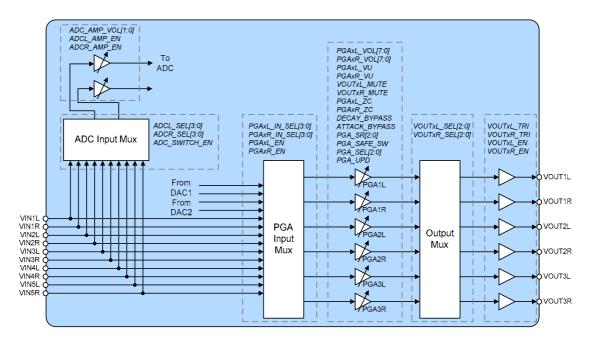

The WM8594 is a high performance multi-channel audio CODEC with flexible input/output selection and digital and analogue volume control. Features include a 24-bit stereo ADC with digital gain control, two 24-bit DACs with independent digital volume control, and a range of input/output channel selection options with analogue volume control, for flexible routing within current and future audio systems.

The WM8594 accepts five stereo audio inputs at line levels up to 2Vrms. One stereo input can be routed to the ADC. All inputs can be routed to the output.

The WM8594 outputs three stereo audio channels at line levels up to 2Vrms, which can be selected from any of the analogue inputs and DAC outputs. Additionally, one stereo output is available with a headphone driver. The DAC channels include independent digital volume control, and all three stereo output channels include analogue volume control with soft ramp.

The WM8594 supports up to 2Vrms analogue inputs, 2Vrms outputs, with sampling rates from 32kHz to 192kHz for the DACs, and 32kHz to 96kHz for the ADC.

The WM8594 is ideal for audio applications requiring high performance and flexible routing options, including flat panel digital TV and DVD recorder.

The device is controlled via a serial interface with support for 2-wire and 3-wire control with full readback. Control of mute, powerdown and reset can also be achieved by pin selection.

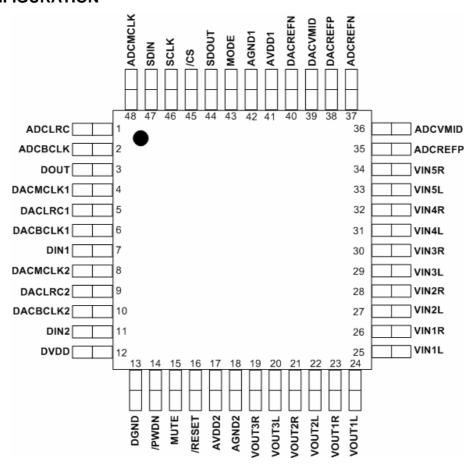

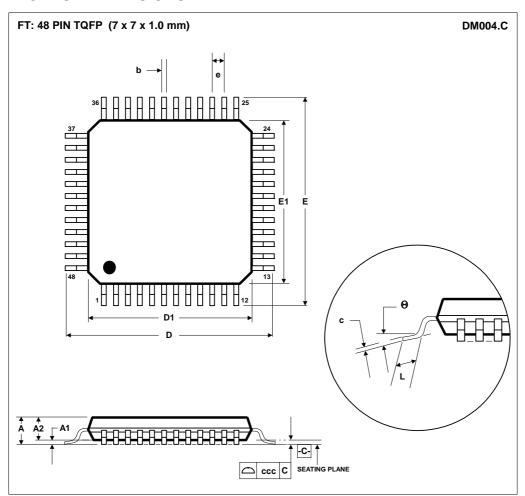

The WM8594 is available in a 48-lead TQFP package.

## **FEATURES**

- Multi-channel CODEC with 5 stereo input selector and 3 stereo output selector

- 4-channel DAC, 2-channel ADC

- Five stereo 2Vrms stereo inputs with analogue bypass to three stereo 2Vrms outputs

- Stereo headphone driver

- Audio performance

- DAC: 100dB SNR typical ('A' weighted @ 48kHz)

- DAC: -90dB THD typical

- ADC: 100dB SNR typical ('A' weighted @ 48kHz)

- ADC: -90dB THD typical

- Independent sampling rates for ADC, DAC1 and DAC2

- DACs sampling frequency 32kHz to 192kHz

- ADC sampling frequency 32kHz to 96kHz

- ADC digital gain control: +30dB to -97dB

- DAC digital volume control: +12dB to -100dB

- Analogue Volume control with soft ramp: +6dB to -73.5dB

- All volume controls include zero cross detection to prevent pops and clicks

- 2 and 3-wire serial control interface with readback and hardware reset, mute and powerdown pins

- Master or slave clocking modes

- Programmable format audio data interface modes

- I<sup>2</sup>S, LJ, RJ, DSP

- 3.3V / 9V analogue, 3.3V digital supply operation

- 48-lead TQFP package

## **APPLICATIONS**

- Digital Flat Panel TV

- DVD-RW

## **BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| DESCRIPTION                                                                | 1        |

|----------------------------------------------------------------------------|----------|

| FEATURES                                                                   |          |

| APPLICATIONS                                                               |          |

| BLOCK DIAGRAM                                                              | 2        |

| TABLE OF CONTENTS                                                          | 3        |

| PIN CONFIGURATION                                                          | 4        |

| ORDERING INFORMATION                                                       | 4        |

| PIN DESCRIPTION                                                            | 5        |

| ABSOLUTE MAXIMUM RATINGS                                                   |          |

| RECOMMENDED OPERATING CONDITIONS                                           |          |

| SUPPLY CURRENT CONSUMPTION                                                 |          |

| ELECTRICAL CHARACTERISTICS                                                 |          |

| TERMINOLOGY                                                                |          |

| MASTER CLOCK TIMING                                                        |          |

| DIGITAL AUDIO INTERFACE TIMING - SLAVE MODE                                | 12       |

| DIGITAL AUDIO INTERFACE TIMING - MASTER MODE                               |          |

| CONTROL INTERFACE TIMING – 2-WIRE MODE                                     | 14       |

| CONTROL INTERFACE TIMING – 3-WIRE MODE                                     | 15       |

| POWER ON RESET (POR)                                                       | 16       |

| DEVICE DESCRIPTION                                                         | 17       |

| INTRODUCTION                                                               | 17       |

| CONTROL INTERFACE                                                          |          |

| 2-WIRE (SM-BUS COMPATIBLE) SERIAL CONTROL INTERFACE MODE                   |          |

| 3-WIRE (SPI COMPATIBLE) SERIAL CONTROL INTERFACE MODE                      |          |

| GLOBAL ENABLE CONTROL                                                      |          |

| DIGITAL AUDIO INTERFACE                                                    |          |

| DIGITAL AUDIO DATA SAMPLING RATES                                          |          |

| DIGITAL AUDIO DATA FORMATS                                                 |          |

| DAC FEATURES                                                               |          |

| ADC FEATURESANALOGUE ROUTING CONTROL                                       |          |

| POP AND CLICK PERFORMANCE                                                  |          |

| REGISTER MAP                                                               |          |

| DIGITAL FILTER CHARACTERISTICS                                             |          |

|                                                                            |          |

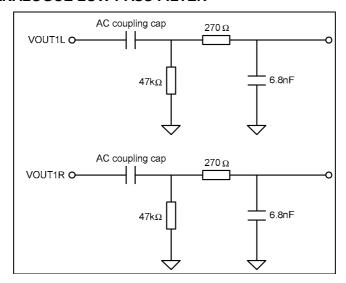

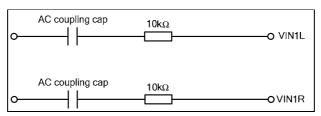

| APPLICATIONS INFORMATION RECOMMENDED EXTERNAL COMPONENTS                   |          |

|                                                                            |          |

| RECOMMENDED ANALOGUE LOW PASS FILTEREXTENDED INPUT IMPEDANCE CONFIGURATION | /5<br>75 |

| RELEVANT APPLICATION NOTES                                                 |          |

| PACKAGE DIMENSIONS                                                         |          |

| IMPORTANT NOTICE                                                           |          |

| ADDRESS:                                                                   |          |

| ADDINEOG                                                                   | 10       |

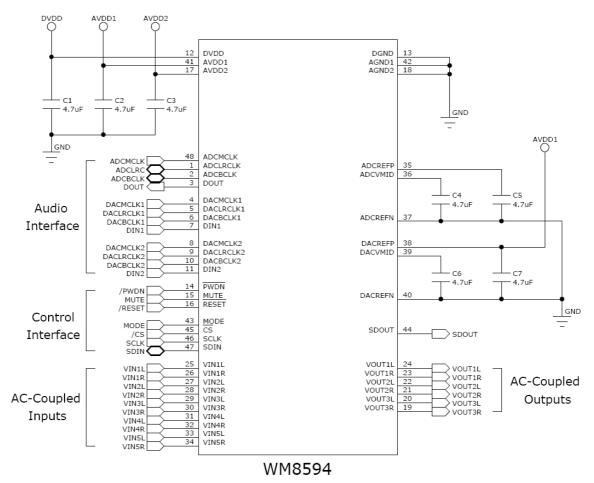

## **PIN CONFIGURATION**

## **ORDERING INFORMATION**

| DEVICE        | TEMPERATURE<br>RANGE | PACKAGE                                  | MOISTURE SENSITIVITY<br>LEVEL | PEAK SOLDERING<br>TEMPERATURE |

|---------------|----------------------|------------------------------------------|-------------------------------|-------------------------------|

| WM8594SEFT/V  | -25 to +85°C         | 48-lead TQFP<br>(Pb-free)                | MSL1                          | 260°C                         |

| WM8594SEFT/RV | -25 to +85°C         | 48-lead TQFP<br>(Pb-free, tape and reel) | MSL1                          | 260°C                         |

Note:

Reel quantity = 2,200

# **PIN DESCRIPTION**

| PIN | NAME     | TYPE                 | DESCRIPTION                                          |

|-----|----------|----------------------|------------------------------------------------------|

| 1   | ADCLRC   | Digital Input/Output | ADC audio interface left/right clock input/output    |

| 2   | ADCBCLK  | Digital Input/Output | ADC audio interface bit clock input/output           |

| 3   | DOUT     | Digital Output       | ADC data output                                      |

| 4   | DACMCLK1 | Digital Input        | DAC1 master clock                                    |

| 5   | DACLRC1  | Digital input        | DAC1 audio interface left/right clock input          |

| 6   | DACBCLK1 | Digital Input        | DAC1 audio interface bit clock input                 |

| 7   | DIN1     | Digital Input        | DAC 1 data input                                     |

| 8   | DACMCLK2 | Digital Input        | DAC2 master clock                                    |

| 9   | DACLRC2  | Digital input        | DAC2 audio interface left/right clock input          |

| 10  | DACBCLK2 | Digital Input        | DAC2 audio interface bit clock input                 |

| 11  | DIN2     | Digital Input        | DAC 2 data input                                     |

| 12  | DVDD     | Supply               | Digital supply                                       |

| 13  | DGND     | Supply               | Digital ground                                       |

| 14  | /PWDN    | Digital Input        | Hardware standby mode                                |

| 15  | MUTE     | Digital Input        | Hardware DAC mute                                    |

| 16  | /RESET   | Digital Input        | Hardware reset                                       |

| 17  | AVDD2    | Supply               | Analogue 9V supply                                   |

| 18  | AGND2    | Supply               | Analogue ground                                      |

| 19  | VOUT3R   | Analogue Output      | Output selector channel 3 right output               |

| 20  | VOUT3L   | Analogue Output      | Output selector channel 3 left output                |

| 21  | VOUT2R   | Analogue Output      | Output selector channel 2 right output               |

| 22  | VOUT2L   | Analogue Output      | Output selector channel 2 left output                |

| 23  | VOUT1R   | Analogue Output      | Output selector channel 1 right output               |

| 24  | VOUT1L   | Analogue Output      | Output selector channel 1 left output                |

| 25  | VIN1L    | Analogue Input       | Input selector channel 1 left input                  |

| 26  | VIN1R    | Analogue Input       | Input selector channel 1 right input                 |

| 27  | VIN2L    | Analogue Input       | Input selector channel 2 left input                  |

| 28  | VIN2R    | Analogue Input       | Input selector channel 2 right input                 |

| 29  | VIN3L    | Analogue Input       | Input selector channel 3 left input                  |

| 30  | VIN3R    | Analogue Input       | Input selector channel 3 right input                 |

| 31  | VIN4L    | Analogue Input       | Input selector channel 4 left input                  |

| 32  | VIN4R    | Analogue Input       | Input selector channel 4 right input                 |

| 33  | VIN5L    | Analogue Input       | Input selector channel 5 left input                  |

| 34  | VIN5R    | Analogue Input       | Input selector channel 5 right input                 |

| 35  | ADCREFP  | Analogue Input       | Positive reference for ADC                           |

| 36  | ADCVMID  | Analogue Output      | Midrail divider decoupling pin for ADC               |

| 37  | ADCREFN  | Analogue Input       | Ground reference for ADC                             |

| 38  | DACREFP  | Analogue Input       | Positive reference for DACs                          |

| 39  | DACVMID  | Analogue Output      | Midrail divider decoupling pin for DACs              |

| 40  | DACREFN  | Analogue Input       | Ground reference for DACs                            |

| 41  | AVDD1    | Supply               | Analogue 3.3V supply                                 |

| 42  | AGND1    | Supply               | Analogue ground                                      |

| 43  | MODE     | Digital Input        | Software mode select (High = 3-wire, Low = 2-wire)   |

| 44  | SDOUT    | Digital Output       | Software mode: serial control interface data output  |

| 45  | /CS      | Digital Input        | Software mode: serial control interface chip select  |

| 46  | SCLK     | Digital Input        | Software mode: serial control interface clock signal |

| 47  | SDIN     | Digital Input        | Software mode: serial control interface data signal  |

| 48  | ADCMCLK  | Digital Input        | ADC master clock input                               |

#### **ABSOLUTE MAXIMUM RATINGS**

Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics at the test conditions specified.

ESD Sensitive Device. This device is manufactured on a CMOS process. It is therefore generically susceptible to damage from excessive static voltages. Proper ESD precautions must be taken during handling and storage of this device.

Wolfson tests its package types according to IPC/JEDEC J-STD-020B for Moisture Sensitivity to determine acceptable storage conditions prior to surface mount assembly. These levels are:

MSL1 = unlimited floor life at <30°C / 85% Relative Humidity. Not normally stored in moisture barrier bag.

MSL2 = out of bag storage for 1 year at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

MSL3 = out of bag storage for 168 hours at <30°C / 60% Relative Humidity. Supplied in moisture barrier bag.

The Moisture Sensitivity Level for each package type is specified in Ordering Information.

| CONDITION                                            | MIN        | MAX          |

|------------------------------------------------------|------------|--------------|

| Digital supply voltage, DVDD                         | -0.3V      | +4.5V        |

| Analogue supply voltage, AVDD1                       | -0.3V      | +7V          |

| Analogue supply voltage, AVDD2                       | -0.3V      | +15V         |

| Voltage range digital inputs                         | DGND -0.3V | DVDD + 0.3V  |

| Voltage range analogue inputs                        | TBD        | AVDD1 + 0.2V |

| Master Clock Frequency                               |            | 38.462MHz    |

| Ambient temperature (supplies applied)               | -55°C      | +125°C       |

| Storage temperature                                  | -65°C      | +150°C       |

| Pb free package body temperature (reflow 10 seconds) |            | +260°C       |

| Package body temperature (soldering 2 minutes)       |            | +183°C       |

#### Note:

## THERMAL PERFORMANCE

| PARAMETER                                | SYMBOL         | TEST<br>CONDITIONS | MIN | TYP                | MAX | UNIT |

|------------------------------------------|----------------|--------------------|-----|--------------------|-----|------|

| Thermal resistance – junction to ambient | $R_{	heta JA}$ |                    |     | 51.7<br>See note 1 |     | °C/W |

#### Notes:

- 1. Figure given for package mounted on 4-layer FR4 according to JESD51-7. (No forced air flow is assumed).

- 2. Thermal performance figures are estimated.

<sup>1.</sup> Analogue and digital grounds must always be within 0.3V of each other.

## RECOMMENDED OPERATING CONDITIONS

| PARAMETER                   | SYMBOL         | TEST CONDITIONS | MIN  | TYP | MAX | UNIT |

|-----------------------------|----------------|-----------------|------|-----|-----|------|

| Digital power supply        | DVDD           |                 | 2.97 | 3.3 | 3.6 | V    |

| Analogue power supply       | AVDD1          |                 | 2.97 | 3.3 | 3.6 | V    |

| Analogue power supply       | AVDD2          |                 | 8.1  | 9   | 9.9 | V    |

| Ground                      | DGND/AGND1/    |                 |      | 0   |     | V    |

|                             | AGND2          |                 |      |     |     |      |

| Operating temperature range | T <sub>A</sub> |                 | -25  |     | +85 | °C   |

#### Notes:

- 1. Digital supply (DVDD) must never be more than 0.3V greater than AVDD1 in normal operation.

- 2. Digital ground (DGND) and analogue grounds (AGND1, AGND2) must never be more than 0.3V apart.

## **SUPPLY CURRENT CONSUMPTION**

| PARAMETER               | SYMBOL             | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-------------------------|--------------------|-----------------|-----|-----|-----|------|

| Digital supply current  | I <sub>DVDD</sub>  |                 |     | TBD |     | mA   |

| Analogue supply current | I <sub>AVDD1</sub> |                 |     | TBD |     | mA   |

| Analogue supply current | I <sub>AVDD2</sub> |                 |     | TBD |     | mA   |

| Standby current         |                    |                 |     | TBD |     | μA   |

## **ELECTRICAL CHARACTERISTICS**

#### **Test Conditions**

AVDD2=9V, AVDD1=DVDD=3.3V, AGND1=AGND2=0V, DGND=0V, T<sub>A</sub>=+25°C, 1kHz signal, fs=48kHz, MCLK=256fs unless otherwise stated

| PARAMETER                                  | SYMBOL          | TEST CONDITIONS                   | MIN        | TYP               | MAX        | UNIT |

|--------------------------------------------|-----------------|-----------------------------------|------------|-------------------|------------|------|

| Digital logic levels                       |                 |                                   |            |                   |            |      |

| Input low level                            | V <sub>IL</sub> |                                   |            |                   | 0.3xDVDD   | V    |

| Input high level                           | V <sub>IH</sub> |                                   | 0.7xDVDD   |                   |            | V    |

| Output low level                           | $V_{OL}$        |                                   |            |                   | 0.1 x DVDD | V    |

| Output high level                          | V <sub>OH</sub> |                                   | 0.9 x DVDD |                   |            | V    |

| Digital input leakage current              |                 |                                   |            | TBD               |            | μA   |

| Digital input leakage capacitance          |                 |                                   |            | TBD               |            | pF   |

| Analogue Reference Levels                  | 1               | 1                                 | I.         | JI.               | <u>l</u>   |      |

| ADC Midrail Voltage                        | ADCVMID         |                                   |            | AVDD1/2           |            | V    |

| ADC Buffered Positive<br>Reference Voltage | ADCREFP         |                                   |            | ADCVMID           |            | V    |

| DAC Midrail Voltage                        | DACVMID         |                                   |            | DACREFP/2         |            | V    |

| Potential divider resistance               |                 | AVDD1 to ADCVMID ADCVMID to AGND1 |            | 100               |            | kΩ   |

|                                            |                 | DACVREFP to DACVMID               |            | 50                |            | kΩ   |

|                                            |                 | DACVMID to DACVREFN               |            | (Note 2)          |            |      |

|                                            |                 | VMID_SEL[1:0] = 01                |            |                   |            |      |

| Analogue Line Outputs                      |                 |                                   |            |                   |            |      |

| Output signal level (0dB)                  |                 | $R_L = 10k\Omega$                 | TBD        | 2.0x<br>AVDD2 / 9 | TBD        | Vrms |

| Maximum capacitance load                   |                 |                                   |            |                   | 11         | nF   |

| Minimum resistance load                    |                 |                                   | 1          |                   |            | kΩ   |

## **Test Conditions**

AVDD2=9V, AVDD1=DVDD=3.3V, AGND1=AGND2=0V, DGND=0V, T<sub>A</sub>=+25°C, 1kHz signal, fs=48kHz, MCLK=256fs unless otherwise stated

| PARAMETER                                | SYMBOL | TEST CONDITIONS                      | MIN  | TYP       | MAX | UNIT     |

|------------------------------------------|--------|--------------------------------------|------|-----------|-----|----------|

| Analogue Headphone Outputs               | 1      | 1                                    |      |           |     | 1        |

| Output signal level (0dB)                |        | $R_L = 32\Omega$                     | TBD  | 0.8x      | TBD | Vrms     |

| ,                                        |        |                                      |      | AVDD2/9   |     |          |

| Minimum resistance load                  |        |                                      | 16   |           |     | Ω        |

| Analogue Inputs                          |        |                                      |      |           |     | •        |

| Input signal level (0dB)                 |        |                                      |      | 2.0 x     | TDD | \/=====  |

|                                          |        |                                      |      | AVDD1/3.3 | TBD | Vrms     |

| Input impedance                          |        |                                      | 10   | 11        | 12  | kΩ       |

| Extended input impedance                 |        | External resistor =                  |      | 21        |     | kΩ       |

| (Note 3)                                 |        | 10kΩ                                 |      |           |     |          |

| Input capacitance                        |        |                                      |      | TBD       |     | nF       |

| DAC Performance                          |        |                                      |      |           |     |          |

| Signal to Noise Ratio <sup>1,5</sup>     | SNR    | A-weighted                           | TBD  | 100       |     | dB       |

|                                          |        | @ fs = 48kHz                         |      |           |     |          |

|                                          |        | A-weighted                           |      | 100       |     | dB       |

|                                          |        | @ fs = 96kHz                         |      |           |     |          |

|                                          |        | A-weighted                           |      | 100       |     | dB       |

|                                          |        | @ fs = 192kHz                        |      |           |     |          |

| Dynamic Range <sup>2,5</sup>             | DNR    | A-weighted, -60dB full               | TBD  | 100       |     | dB       |

|                                          |        | scale input                          |      |           |     | <u> </u> |

| Total Harmonic Distortion <sup>3,5</sup> | THD    | 1kHz, 0dBFS                          |      | -90       | TBD | dB       |

|                                          |        | @ fs = 48kHz                         |      |           |     |          |

|                                          |        | 1kHz, 0dBFS                          |      | -90       |     | dB       |

|                                          |        | @ fs = 96kHz                         |      |           |     |          |

|                                          |        | 1kHz, 0dBFS                          |      | -90       |     | dB       |

|                                          |        | @ fs = 192kHz                        |      |           |     |          |

| Channel Separation <sup>4,5</sup>        |        |                                      |      | 100       |     | dB       |

| Channel Level Matching                   |        |                                      |      | 0.1       |     | dB       |

| Channel Phase Deviation                  |        |                                      |      | 0.05      |     | Degree   |

| Power supply rejection ratio             | PSRR   | 1kHz, 100mVpp                        | TBD  | 50        |     | dB       |

|                                          |        | 20Hz to 20kHz,                       |      | TBD       |     | dB       |

|                                          |        | 100mVpp                              |      |           |     |          |

| ADC Performance                          | 1      | T                                    |      |           |     | 1        |

| Signal to Noise Ratio <sup>1,5</sup>     | SNR    | A-weighted, 0dB gain                 | TBD  | 100       |     | dB       |

|                                          |        | @ fs = 48kHz                         |      |           |     | in .     |

|                                          |        | A-weighted, 0dB gain<br>@ fs = 96kHz |      | 97        |     | dB       |

| Dynamic Range <sup>2,5</sup>             | DNR    | A-weighted, -60dB full               | TBD  | 100       |     | dB       |

| Dynamic Nange                            | אוע    | scale input                          | טטו  | 100       |     | UD       |

| Total Harmonic Distortion <sup>3,5</sup> | THD    | 1kHz, -1dBFS                         |      | -90       | TBD | dB       |

|                                          |        | @ fs = 48kHz                         |      |           | ==  |          |

|                                          |        | 1kHz, -1dBFS                         |      | -87       |     | dB       |

|                                          |        | @ fs = 96kHz                         |      | '.        |     |          |

| Channel Separation <sup>4,5</sup>        |        |                                      |      | 100       |     | dB       |

| Channel Level Matching                   |        |                                      |      | 0.1       |     | dB       |

| Channel Phase Deviation                  | 1      |                                      |      | 0.05      |     | Degree   |

| Power Supply Rejection Ratio             | PSRR   |                                      | TBD  | 50        |     | dB       |

| . S. S. Supply Rejodion Railo            | . 5141 |                                      | . 50 | TBD       |     | dB       |

| Analogue Bypass Paths                    | I      | 1                                    |      | 100       |     | 1 40     |

| Signal to Noise Ratio <sup>1,5</sup>     | SNR    | A-weighted                           |      | 100       |     | dB       |

| Dynamic Range <sup>2,5</sup>             | DNR    | A-weighted A-weighted                |      | 100       |     | dB       |

|                                          | I DINK | A-WEIGHTEG                           |      | IUU       |     | ı uD     |

**Test Conditions**

AVDD2=9V, AVDD1=DVDD=3.3V, AGND1=AGND2=0V, DGND=0V, T<sub>A</sub>=+25°C, 1kHz signal, fs=48kHz, MCLK=256fs unless otherwise stated

| PARAMETER                            | SYMBOL | TEST CONDITIONS             | MIN | TYP      | MAX | UNIT   |

|--------------------------------------|--------|-----------------------------|-----|----------|-----|--------|

| Channel Separation <sup>4,5</sup>    |        |                             |     | 100      |     | dB     |

| Channel Level Matching               |        |                             |     | 0.1      |     | dB     |

| Channel Phase Deviation              |        |                             |     | 0.05     |     | Degree |

| Headphone Amplifier                  |        |                             |     |          |     |        |

| Output signal level (0dB)            |        |                             |     | 0.8      |     | Vrms   |

| Signal to Noise Ratio <sup>1,5</sup> | SNR    | A-weighted                  |     |          |     | dB     |

| Total Harmonic Distortion            | THD    | $P_O=20$ mW, $R_L=16\Omega$ |     |          |     | dB     |

|                                      |        | $P_O=20$ mW, $R_L=32\Omega$ |     |          |     | dB     |

| Channel Separation <sup>4,5</sup>    |        |                             |     |          |     | dB     |

| Power Supply Rejection Ratio         | PSRR   |                             |     | TBD      |     | dB     |

| Digital Volume Control               | •      | -                           |     | -        | •   | •      |

| ADC minimum digital volume           |        |                             |     | -97      |     | dB     |

| ADC maximum digital volume           |        |                             |     | +30      |     | dB     |

| ADC volume step size                 |        |                             |     | 0.5      |     | dB     |

| DAC minimum digital volume           |        |                             |     | -100     |     | dB     |

| DAC maximum digital volume           |        |                             |     | +12      |     | dB     |

| DAC volume step size                 |        |                             |     | 0.5      |     | dB     |

| Analogue Volume Control              |        |                             |     |          |     |        |

| Minimum gain                         |        |                             |     | -73.5    |     | dB     |

| Maximum gain                         |        |                             |     | +6       |     | dB     |

| Step size                            |        |                             |     | 0.5      |     | dB     |

| Mute attenuation                     |        |                             |     | TBD      |     | dB     |

| Crosstalk                            |        |                             |     |          |     |        |

| DAC to ADC                           |        | 1kHz signal,                |     | 100      |     | dB     |

|                                      |        | ADC fs=48kHz,               |     |          |     |        |

|                                      |        | DAC fs=44.1kHz              |     |          |     |        |

|                                      |        | 20kHz signal,               |     | 100      |     | dB     |

|                                      |        | ADC fs=48kHz,               |     |          |     |        |

|                                      |        | DAC fs=44.1kHz              |     |          |     |        |

| ADC to DAC                           |        | 1kHz signal,                |     | 100      |     | dB     |

|                                      |        | ADC fs=48kHz,               |     |          |     |        |

|                                      |        | DAC fs=44.1kHz              |     |          |     |        |

|                                      |        | 20kHz signal,               |     | 100      |     | dB     |

|                                      |        | ADC fs=48kHz,               |     |          |     |        |

|                                      |        | DAC fs=44.1kHz              |     | <u> </u> |     | 1      |

## **TERMINOLOGY**

- Signal-to-noise ratio (dBFS) SNR is the difference in level between a reference full scale output signal and the

device output with no signal applied. This ratio is also called idle channel noise. (No Auto-zero or Automute function is

employed in achieving these results).

- 2. Dynamic range (dBFS) DNR is a measure of the difference in level between the highest and lowest components of a signal. Normally a THD measurement at -60dBFS. The measured signal is then corrected by adding 60dB to the result, e.g. THD @ -60dBFS = -30dB, DNR = 90dB.

- 3. Total Harmonic Distortion (dBFS) THD is the difference in level between a reference full scale output signal and the first seven odd harmonics of the output signal. To calculate the ratio, the fundamental frequency of the output signal is notched out and an RMS value of the next seven odd harmonics is calculated.

- 4. Channel Separation (dB) Also known as Cross-Talk. This is a measure of the amount one channel is isolated from the other. Normally measured by sending a full scale signal down one channel and measuring the other.

5. All performance measurements carried out with 20kHz low pass filter, and where noted an A-weighted filter. Failure to use such a filter will result in higher THD and lower SNR and Dynamic Range readings than are found in the Electrical Characteristics. The low pass filter removes out of band noise; although it is not audible it may affect dynamic specification values.

#### Notes:

- 1. All minimum and maximum values are subject to change.

- 2. This resistance is selectable using VMID\_SEL[1:0] see Figure 49 for full details.

- 3. See p75 for details of extended input impedance configuration.

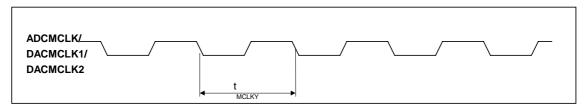

## **MASTER CLOCK TIMING**

Figure 1 MCLK Timing

## **Test Conditions**

AVDD1, DVDD = 3.3V, AVDD2 = 9V, AGND1, AGND2, DGND = 0V,  $T_A = +25^{\circ}C$

| PARAMETER                       | SYMBOL             | MIN   | TYP | MAX   | UNIT |

|---------------------------------|--------------------|-------|-----|-------|------|

| Master Clock Timing Information |                    |       |     |       |      |

| MCLK System clock cycle time    | t <sub>MCLKY</sub> | 27    |     | 120   | ns   |

| MCLK Duty cycle                 |                    | 40:60 |     | 60:40 | %    |

| MCLK Period Jitter              |                    |       |     | 200   | ps   |

| MCLK Rise/Fall times            |                    |       |     | 10    | ns   |

**Table 1 Master Clock Timing Requirements**

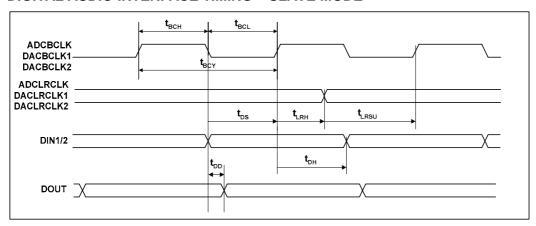

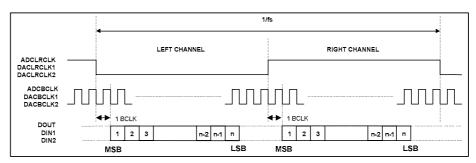

## **DIGITAL AUDIO INTERFACE TIMING – SLAVE MODE**

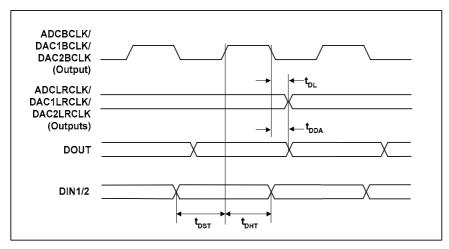

Figure 2 Slave Mode Digital Audio Data Timing

#### **Test Conditions**

AVDD1, DVDD = 3.3V, AVDD2 = 9V, AGND1, AGND2, DGND = 0V,  $T_A$  =  $+25^{\circ}C$ , Slave Mode, fs = 48kHz, ADCMCLK, DACMCLK = 256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                                                                  | SYMBOL            | MIN | TYP | MAX | UNIT |

|--------------------------------------------------------------------------------------------|-------------------|-----|-----|-----|------|

| Audio Data Input Timing Information                                                        |                   |     |     |     |      |

| ADCBCLK / DACBCLK1 / DACBCLK2 cycle time                                                   | t <sub>BCY</sub>  | 80  |     |     | ns   |

| ADCBCLK / DACBCLK1 / DACBCLK2 pulse width high                                             | t <sub>BCH</sub>  | 30  |     |     | ns   |

| ADCBCLK / DACBCLK1 / DACBCLK2 pulse width low                                              | t <sub>BCL</sub>  | 30  |     |     | ns   |

| ADCBCLK / DACBCLK1 / DACBCLK2 rise/fall times                                              |                   |     |     | 5   | ns   |

| ADCLRCLK / DACLRCLK1 / DACLRCLK2 set-up time to ADCBCLK / DACBCLK1 / DACLRCLK2 rising edge | t <sub>LRSU</sub> | 22  |     |     | ns   |

| ADCLRCLK / DACLRCLK1 / DACLRCLK2 hold time from ADCBCLK / DACBCLK1 / DACBCLK2 rising edge  | t <sub>LRH</sub>  | 25  |     |     | ns   |

| ADCLRCLK / DACLRCLK1 / DACLRCLK2 rise/fall times                                           |                   |     |     | 5   | ns   |

| DIN1/2 hold time from DACBCLK1 / DACBCLK2 rising edge                                      | t <sub>DH</sub>   | 25  |     |     | ns   |

| DOUT propagation delay from ADCBCLK falling edge                                           | t <sub>DD</sub>   | 4   |     | 16  | ns   |

**Table 2 Slave Mode Audio Interface Timing**

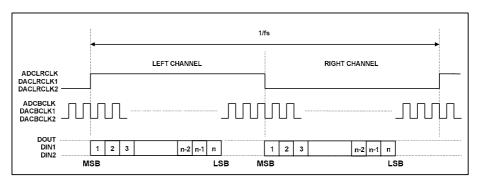

# **DIGITAL AUDIO INTERFACE TIMING - MASTER MODE**

Figure 3 Master Mode Digital Audio Data Timing

#### **Test Conditions**

AVDD1, DVDD = 3.3V, AVDD2 = 9V, AGND1, AGND2, DGND = 0V,  $T_A$  = +25°C, Slave Mode, fs = 48kHz, ADCMCLK, DACMCLK = 256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                                                                           | SYMBOL           | MIN | TYP | MAX | UNIT |

|-----------------------------------------------------------------------------------------------------|------------------|-----|-----|-----|------|

| Audio Data Input Timing Information                                                                 |                  |     |     |     |      |

| ADCLRCLK / DACLRCLK1 / DACLRCLK2 propagation delay from ADCBCLK / DACBCLK1 / DACLRCLK2 falling edge | t <sub>DL</sub>  | 4   |     | 16  | ns   |

| DOUT propagation delay from ADCBCLK falling edge                                                    | t <sub>DDA</sub> | 4   |     | 16  | ns   |

| DIN1 / DIN2 setup time to DACBCLK1 / DACBCLK2 rising edge                                           | t <sub>DST</sub> | 22  |     |     | ns   |

| DIN1 / DIN2 hold time to DACBCLK1 / DACBCLK2 rising edge                                            | t <sub>DHT</sub> | 25  |     |     | ns   |

**Table 3 Master Mode Audio Interface Timing**

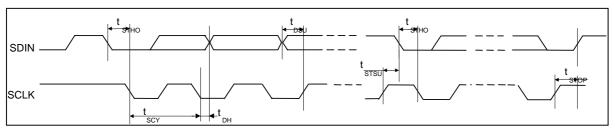

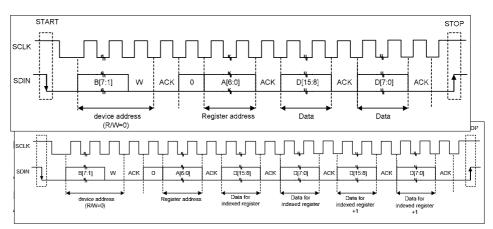

# **CONTROL INTERFACE TIMING – 2-WIRE MODE**

Figure 4 Control Interface Timing – 2-Wire Serial Control Mode

#### **Test Conditions**

AVDD1, DVDD = 3.3V, AVDD2 = 9V, AGND1, AGND2, DGND = 0V,  $T_A$  =  $+25^{\circ}C$ , Slave Mode, fs = 48kHz, ADCMCLK, DACMCLK = 256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                     | SYMBOL                             | MIN   | TYP | MAX   | UNIT |  |  |  |  |  |

|-----------------------------------------------|------------------------------------|-------|-----|-------|------|--|--|--|--|--|

| Program Register Input Information            | Program Register Input Information |       |     |       |      |  |  |  |  |  |

| SCLK pulse cycle time                         | t <sub>SCY</sub>                   | 2500  |     |       | ns   |  |  |  |  |  |

| SCLK duty cycle                               |                                    | 40/60 |     | 60/40 | %    |  |  |  |  |  |

| SCLK frequency                                |                                    |       |     | 400   | kHz  |  |  |  |  |  |

| Hold Time (Start Condition)                   | tsтно                              | 600   |     |       | ns   |  |  |  |  |  |

| Setup Time (Start Condition)                  | tstsu                              | 600   |     |       | ns   |  |  |  |  |  |

| Data Setup Time                               | t <sub>DSU</sub>                   | 100   |     |       | ns   |  |  |  |  |  |

| SDIN, SCLK Rise Time                          |                                    |       |     | 300   | ns   |  |  |  |  |  |

| SDIN, SCLK Fall Time                          |                                    |       |     | 300   | ns   |  |  |  |  |  |

| Setup Time (Stop Condition)                   | t <sub>STOP</sub>                  | 600   |     |       | ns   |  |  |  |  |  |

| Data Hold Time                                | t <sub>DHO</sub>                   |       |     | 900   | ns   |  |  |  |  |  |

| Pulse width of spikes that will be suppressed | t <sub>ps</sub>                    | 2     |     | 8     | ns   |  |  |  |  |  |

Table 4 Control Interface Timing – 2-Wire Serial Control Mode

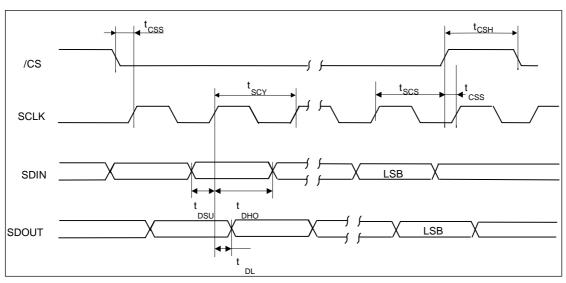

## **CONTROL INTERFACE TIMING – 3-WIRE MODE**

Figure 5 Control Interface Timing – 3-Wire Serial Control Mode

#### **Test Conditions**

AVDD1, DVDD = 3.3V, AVDD2 = 9V, AGND1, AGND2, DGND = 0V,  $T_A = +25$ °C, Slave Mode, fs = 48kHz, ADCMCLK, DACMCLK = 256fs, 24-bit data, unless otherwise stated.

| PARAMETER                                     | SYMBOL           | MIN   | TYP | MAX   | UNIT |  |  |  |

|-----------------------------------------------|------------------|-------|-----|-------|------|--|--|--|

| Program Register Input Information            |                  |       |     |       |      |  |  |  |

| SCLK rising edge to CSB rising edge           | t <sub>scs</sub> | 60    |     |       | ns   |  |  |  |

| SCLK pulse cycle time                         | t <sub>SCY</sub> | 80    |     |       | ns   |  |  |  |

| SCLK duty cycle                               |                  | 40/60 |     | 60/40 | %    |  |  |  |

| SDIN to SCLK set-up time                      | t <sub>DSU</sub> | 20    |     |       | ns   |  |  |  |

| SDIN hold time from SCLK rising edge          | t <sub>DHO</sub> | 20    |     |       | ns   |  |  |  |

| SDOUT propagation delay from SCLK rising edge | t <sub>DL</sub>  |       |     | 5     | ns   |  |  |  |

| CSB pulse width high                          | tcsн             | 20    |     |       | ns   |  |  |  |

| CSB rising/falling to SCLK rising             | t <sub>CSS</sub> | 20    |     |       | ns   |  |  |  |

| Pulse width of spikes that will be suppressed | t <sub>ps</sub>  | 2     |     | 8     | ns   |  |  |  |

Table 5 Control Interface Timing – 3-Wire Serial Control Mode

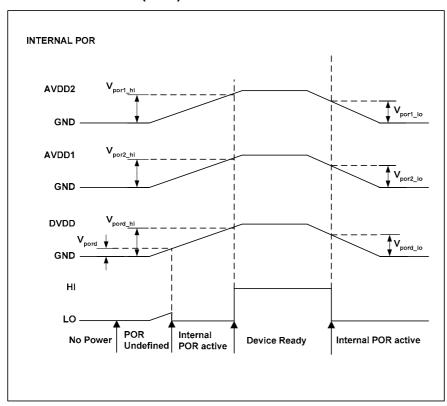

# **POWER ON RESET (POR)**

Figure 1 Power Supply Timing Requirements

#### **Test Conditions**

$DVDD = 3.3V, \ AVDD1 = 3.3V, \ AVDD2 = 9V \ DGND = AGND1 = AGND2 = 0V, \ T_A = +25^{\circ}C, \ T_{A\_max} = +125^{\circ}C, \ T_{A\_min} = -25^{\circ}C \ AVDD1_{max} = DVDD_{max} = 3.63V, \ AVDD1_{min} = DVDD_{min} = 2.97V, \ AVDD2_{max} = 9.9V, \ AVDD2_{min} = 8.1V$

| PARAMETER                                     | SYMBOL               | TEST CONDITIONS    | MIN  | TYP  | MAX  | UNIT |

|-----------------------------------------------|----------------------|--------------------|------|------|------|------|

| Power Supply Input Timing                     | Information          |                    |      | •    |      |      |

| VDD level to POR defined (DVDD rising)        | V <sub>pord</sub>    | Measured from DGND | 0.27 | 0.36 | 0.60 | V    |

| VDD level to POR rising edge (DVDD rising)    | $V_{pord\_hi}$       | Measured from DGND | 1.34 | 1.88 | 2.32 | V    |

| VDD level to POR falling edge (DVDD falling)  | V <sub>pord_lo</sub> | Measured from DGND | 1.32 | 1.86 | 2.30 | V    |

| VDD level to POR rising edge (AVDD1 rising)   | V <sub>por1_hi</sub> | Measured from DGND | 1.65 | 1.68 | 1.85 | V    |

| VDD level to POR falling edge (AVDD1 falling) | V <sub>por1_lo</sub> | Measured from DGND | 1.63 | 1.65 | 1.83 | V    |

| VDD level to POR rising edge (AVDD2 rising)   | V <sub>por2_hi</sub> | Measured from DGND | 1.80 | 1.86 | 2.04 | V    |

| VDD level to POR falling edge (AVDD2 falling) | V <sub>por2_lo</sub> | Measured from DGND | 1.76 | 1.8  | 2.02 | V    |

**Table 6 Power on Reset**

#### **DEVICE DESCRIPTION**

#### INTRODUCTION

The WM8594 is a high performance multi-channel audio CODEC with 2Vrms line level inputs and outputs and flexible analogue input / output switching. The device comprises a 24-bit stereo ADC, two 24-bit stereo DACs with independent sampling rates and digital volume control, and a flexible analogue input and output multiplexer. Analogue inputs and outputs are all at 2Vrms line level, minimising external component count.

The DACs can operate from independent left/right clocks, bit clocks and master clocks with independent data inputs. Alternatively, the DACs can be synchronised to use the same clocks with independent data inputs. Each of the DAC audio interfaces can be configured to operate in ether master or slave clocking modes. In master mode, left/right clocks and bit clocks are all outputs. In slave mode, left/right clocks and bit clocks are all inputs.

The ADC uses a separate left/right clock, bit clock and master clock, allowing independent recording and playback in audio applications. The ADC audio interface can be configured to operate in either master or slave clocking mode. In master mode, left/right clocks and bit clocks are all outputs. In slave mode, left/right clocks and bit clocks are all inputs.

The ADC includes digital gain control, allowing signals to be gained and attenuated between +30dB and -97dB in 0.5dB steps.

The DACs include independent digital volume control, which is adjustable between +12dB and -100 dB in 0.5dB steps. The DACs can be configured to output stereo audio data and a range of mono audio options.

The input multiplexer accepts five stereo line level inputs at up to 2Vrms. One stereo input can be routed to the ADC, and all five stereo inputs can be routed to the output multiplexer.

The output multiplexer includes analogue volume control with zero cross, adjustable between +6dB and -73.5dB in 0.5dB steps, and configurable soft ramp rate. Analogue audio is output at 2Vrms line level.

Control of the internal functionality of the device is by 2-wire serial control interface with readback. The interface may be asynchronous to the audio data interface as control data will be resynchronised to the audio processing internally. In addition, control of mute, power-down and reset may also be achieved by pin selection.

Operation using system clocks of 128fs, 192fs, 256fs, 384fs, 512fs, 768fs or 1152fs is provided. ADC and both DACs may be clocked independently. Sampling rates from 32kHz to 192kHz are supported for both DACs provided the appropriate master clocks are input. Sampling rates from 32kHz to 96kHz are supported for the ADC provided the appropriate master clock is input.

The audio data interface supports right justified, left justified, and I<sup>2</sup>S interface formats along with a highly flexible DSP serial port interface format.

#### **CONTROL INTERFACE**

Control of the WM8594 is achieved by a 2-wire SM-bus-compliant or 3-wire SPI compliant serial interface with readback. Software interface mode is selected using the MODE pin as shown in Table 7 below:

| MODE | INTERFACE FORMAT |

|------|------------------|

| Low  | 2 wire           |

| High | 3 wire           |

Table 7 Control Interface Mode Selection

## 2-WIRE (SM-BUS COMPATIBLE) SERIAL CONTROL INTERFACE MODE

Many devices can be controlled by the same bus, and each device has a unique 7-bit address.

#### **REGISTER WRITE**

The controller indicates the start of data transfer with a high to low transition on SDIN while SCLK remains high. This indicates that a device address and data will follow. All devices on the 2-wire bus respond to the start condition and shift in the next eight bits on SDIN (7-bit address and read/write bit, MSB first). If the device address received matches the address of the WM8594, the WM8594 responds by pulling SDIN low on the next clock pulse (ACK). If the address is not recognised, the WM8594 returns to the idle condition and waits for a new start condition with valid address.

When the WM8594 has acknowledged a correct address, the controller sends the first byte of control data (B23 to B16, i.e. the WM8594 register address). The WM8594 then acknowledges the first data byte by pulling SDIN low for one SCLK pulse. The controller then sends a second byte of control data (B15 to B8, i.e. the first 8 bits of register data), and the WM8594 acknowledges again by pulling SDIN low for one SCLK pulse. Finally, the controller sends a third byte of control data (B7 to B0, i.e. the final 8 bits of register data), and the WM8594 acknowledges again by pulling SDIN low for one SCLK pulse.

The transfer of data is complete when there is a low to high transition on SDIN while SCLK is high. After receiving a complete address and data sequence the WM8594 returns to the idle state and waits for another start condition. If a start or stop condition is detected out of sequence at any point during data transfer (i.e. SDIN changes while SCLK is high), the WM8594 reverts to the idle condition.

The WM8594 device address is 34h (0110100) or 36h (0110110), selectable by control of /CS.

| /CS (PIN 45) | 2-WIRE BUS ADDRESS |

|--------------|--------------------|

| 0            | 34h (0110100)      |

| 1            | 36h (0110110)      |

**Table 8 2-Wire Control Interface Bus Address Selection**

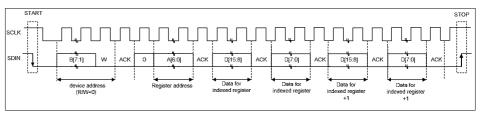

Figure 7. As with normal register writes, the controller indicates the start of data transfer with a high to low transition on SDIN while SCLK remains high, and all devices on the bus receive the device address

When the WM8594 has acknowledged a correct address, the controller sends the first byte of control data (A6 to A0, i.e. the WM8594 initial register address). The WM8594 then acknowledges the first control data byte by pulling SDIN low for one SCLK pulse. The controller then sends a byte of register data. The WM8594 acknowledges the first byte of register data, auto-increments the register address to be written to, and waits for the next byte of register data. Subsequent bytes of register data can be written to consecutive registers of the WM8594 without setting up the device and register address.

The transfer of data is complete when there is a low to high transition on SDIN while SCLK is high.

Figure 7 2-Wire Auto-Increment Register Write

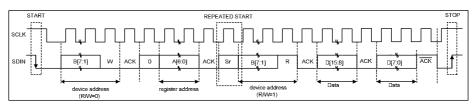

#### **REGISTER READBACK**

The WM8594 allows readback of all registers with data output on the bidirectional SDIN pin. The protocol is similar to that used to write to the device. The controller will issue the device address followed by a write bit, and the register index will then be passed to the WM8594.

At this point the controller will issue a repeated start condition and resend the device address along with a read bit. The WM8594 will acknowledge this and the WM8594 will become a slave transmitter.

The WM8594 will place the data from the indexed register onto SDIN MSB first. When the controller receives the first byte of data, it acknowledges it. When the controller receives the second and final byte of data it will not acknowledge receipt of the data indicating that it will resume master transmitter control of SDIN. The controller will then issue a stop command completing the read cycle.

Figure 8 2-wire Read Protocol

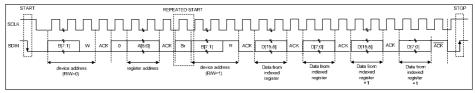

## **AUTO-INCREMENT REGISTER READBACK**

It is possible to read from multiple consecutive registers in continuous readback mode. Continuous readback mode is selected by setting AUTO\_INC.

In continuous readback mode, the WM8594 will return the indexed register first, followed by consecutive registers in increasing index order until the controller issues a stop sequence.

Figure 9 2-Wire Auto-Increment Register Readback

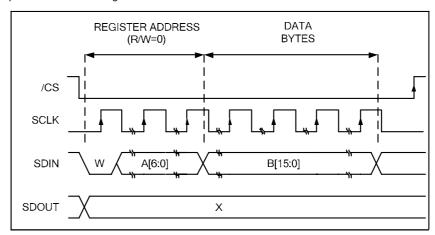

# 3-WIRE (SPI COMPATIBLE) SERIAL CONTROL INTERFACE MODE REGISTER WRITE

SDIN is used for the program data, SCLK is used to clock in the program data and /CS is use to latch in the program data. SDIN is sampled on the rising edge of SCLK. The 3-wire interface write protocol is shown in Figure 10.

Figure 10 3-Wire Serial Interface Write Protocol

- · W indicates write operation.

- A[6:0] is the register index.

- B[15:0] is the data to be written to the register indexed.

- /CS is edge sensitive the data is latched on the rising edge of /CS.

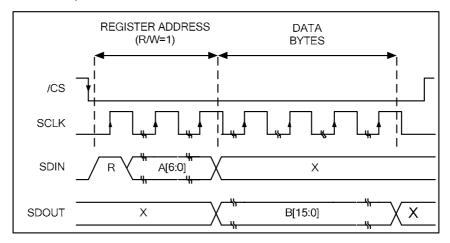

#### **REGISTER READ-BACK**

The read-only status registers can be read back via the SDOUT pin. Read Back is enabled when the R/W bit is high. The data can then be read by writing to the appropriate register address, to which the device will respond with data.

Figure 11 3-Wire Serial Interface Readback Protocol

#### **REGISTER RESET**

Any write to register R0 (00h) will reset the WM8594. All register bits are reset to their default values.

#### **DEVICE ID AND REVISION**

Reading from register R0 returns the device ID. Reading from register R1 returns the device revision number.

| REGISTER<br>ADDRESS | BIT  | LABEL     | DEFAULT  | DESCRIPTION                                    |

|---------------------|------|-----------|----------|------------------------------------------------|

| R0                  | 15:0 | DEVICE_ID | 10000101 | Device ID                                      |

| DEVICE_ID           |      | [15:0]    | 10010100 | A read of this register will return the device |

| 00h                 |      |           |          | ID, 0x8594.                                    |

| R1                  | 7:0  | REVNUM    | N/A      | Device Revision                                |

| REVISION            |      | [7:0]     |          | A read of this register will return the device |

| 01h                 |      |           |          | revision number. This number is sequentially   |

|                     | 1    |           |          | incremented if the device design is updated.   |

Table 9 Device ID and Revision Number

#### **GLOBAL ENABLE CONTROL**

The WM8594 includes a number of enable and disable mechanisms to allow the device to be powered on and off in a pop-free manner. A global enable control bit enables the ADC, DAC and analogue paths. For full details of pop-free operation, see 'Pop and Click Performance' on page 44.

| REGISTER<br>ADDRESS | BIT | LABEL   | DEFAULT | DESCRIPTION                                          |

|---------------------|-----|---------|---------|------------------------------------------------------|

| R12                 | 0   | GLOBAL_ | 0       | Device Global Enable                                 |

| ENABLE<br>0Ch       |     | EN      |         | 0 = ADC, DAC and PGA ramp control circuitry disabled |

|                     |     |         |         | 1 = ADC, DAC and PGA ramp control circuitry enabled  |

**Table 10 Global Enable Control**

#### **DIGITAL AUDIO INTERFACE**

Digital audio data is transferred to and from the WM8594 via the digital audio interface. The DACs have independent data inputs and master clocks, bit clocks and left/right frame clocks, and operate in both master or slave mode The ADC has independent master clock, bit clock and left/right frame clock in addition to its data output, and can operate in both master and slave modes.

## **MASTER MODE**

The ADC audio interface requires both a left/right frame clock (ADCLRCLK) and a bit clock (ADCBCLK). These can be supplied externally (slave mode) or they can be generated internally (master mode). Selection of master and slave mode is achieved by setting ADC\_MSTR in ADC Control Register 15.

The frequency of ADCLRCLK in master mode is dependent upon the ADC master clock frequency and the ADC\_SR[2:0] bits.

The frequency of ADCBCLK in master mode can be selected by ADC\_BCLKDIV[1:0].

The DAC audio interfaces require both left/right frame clocks (DACLRCLK1, DACLRCLK2) and bit clocks (DACBCLK1, DACBCLK2). These can be supplied externally (slave mode) or they can be generated internally (master mode). Selection of master and slave mode is achieved by setting DAC1\_MSTR in DAC1 Control Register 4 and DAC2\_MSTR in DAC2 Control Register 9.

The frequency of DACLRCLK1 in master mode is dependent upon the DAC1 master clock frequency and the DAC1\_SR[2:0] bits. Similarly the frequency of DACLRCLK2 in master mode is dependent upon the DAC2 master clock frequency and the DAC2\_SR[2:0] bits.

The frequency of DACBCLK1 and DACBCLK2 in master mode can be selected by DAC1\_BCLKDIV[1:0] and DAC2\_BCLKDIV[1:0].

|      | EGISTER<br>DDRESS | BIT | LABEL   | DEFAULT | DESCRIPTION                                                 |

|------|-------------------|-----|---------|---------|-------------------------------------------------------------|

|      | R3                | 2:0 | DAC1_   | 000     | DAC MCLK:LRCLK Ratio                                        |

| DA   | C1_CTRL2          |     | SR[2:0] |         | 000 = Auto detect                                           |

|      | 03h               |     |         |         | 001 = 128fs                                                 |

|      |                   |     |         |         | 010 = 192fs                                                 |

|      |                   |     |         |         | 011 = 256fs                                                 |

|      |                   |     |         |         | 100 = 384fs                                                 |

|      |                   |     |         |         | 101 = 512fs                                                 |

|      |                   |     |         |         | 110 = 768fs                                                 |

|      |                   |     |         |         | 111 = 1152fs                                                |

|      |                   | 5:3 | DAC1_   | 000     | DAC1 BCLK Rate                                              |

|      |                   |     | BCLKDIV |         | 000 = MCLK / 4                                              |

|      |                   |     | [2:0]   |         | 001 = MCLK / 8                                              |

|      |                   |     |         |         | 010 = 32fs                                                  |

|      |                   |     |         |         | 011 = 64fs                                                  |

|      |                   |     |         |         | 100 = 128fs                                                 |

|      |                   |     |         |         | All other values of DAC1_BCLKDIV[2:0] are                   |

|      |                   |     |         |         | reserved                                                    |

|      | R4                | 0   | DAC1_   | 0       | DAC1 Master Mode Select                                     |

| DA   | C1_CTRL3<br>04h   |     | MSTR    |         | 0 = Slave mode, DACBCLK1 and DACLRCLK1 are inputs to WM8594 |

|      |                   |     |         |         | 1 = Master mode, DACBCLK1 and                               |

|      | D0                | 0.0 | DACO    | 000     | DACLECLK1 are outputs from WM8594                           |

| D.4. | R8                | 2:0 | DAC2_   | 000     | DAC MCLK:LRCLK Ratio                                        |

| DA   | C1_CTRL2          |     | SR[2:0] |         | 000 = Auto detect                                           |

|      | 08h               |     |         |         | 001 = 128fs                                                 |

|      |                   |     |         |         | 010 = 192fs                                                 |

|      |                   |     |         |         | 011 = 256fs<br>100 = 384fs                                  |

|      |                   |     |         |         | 100 = 36415<br>101 = 512fs                                  |

|      |                   |     |         |         | 110 = 768fs                                                 |

|      |                   |     |         |         | 111 = 1152fs                                                |

|      |                   | 5:3 | DAC2_   | 000     | DAC2 BCLK Rate                                              |

|      |                   | 5.5 | BCLKDIV | 000     | 000 = MCLK / 4                                              |

|      |                   |     | [2:0]   |         | 000 = MCLK / 4<br>001 = MCLK / 8                            |

|      |                   |     | [2.0]   |         | 010 = 32fs                                                  |

|      |                   |     |         |         | 011 = 64fs                                                  |

|      |                   |     |         |         | 100 = 128fs                                                 |

|      |                   |     |         |         | All other values of DAC2_BCLKDIV[2:0] are                   |

|      |                   |     |         |         | reserved                                                    |

|      | R9                | 0   | DAC2_   | 0       | DAC2 Master Mode Select                                     |

| DA   | C2_CTRL3          |     | MSTR    |         | 0 = Slave mode, DACBCLK2 and                                |

|      | _<br>09h          |     |         |         | DACLRCLK2 are inputs to WM8594                              |

|      |                   |     |         |         | 1 = Master mode, DACBCLK2 and                               |

|      |                   |     |         |         | DACLRCLK2 are outputs from WM8594                           |

|      | R14               | 2:0 | ADC_    | 000     | ADC MCLK:LRCLK Ratio                                        |

| AD   | C_CTRL2           |     | SR[2:0] |         | 000 = Auto detect                                           |

|      | 0Eh               |     |         |         | 001 = 128fs                                                 |

|      |                   |     |         |         | 010 = 192fs                                                 |

|      |                   |     |         |         | 011 = 256fs                                                 |

|      |                   |     |         |         | 100 = 384fs                                                 |

|      |                   |     |         |         | 101 = 512fs                                                 |

|      |                   |     |         |         | 110 = 768fs                                                 |

| 1    |                   |     |         |         |                                                             |

| REGISTER<br>ADDRESS | BIT | LABEL    | DEFAULT | DESCRIPTION                                       |

|---------------------|-----|----------|---------|---------------------------------------------------|

|                     | 5:3 | ADC_BCLK | 000     | ADC BCLK Rate                                     |

|                     |     | DIV[2:0] |         | 000 = MCLK / 4                                    |

|                     |     |          |         | 001 = MCLK / 8                                    |

|                     |     |          |         | 010 = 32fs                                        |

|                     |     |          |         | 011 = 64fs                                        |

|                     |     |          |         | 100 = 128fs                                       |

|                     |     |          |         | All other values of ADC_BCLKDIV[2:0] are reserved |

| R15                 | 0   | ADC_     | 0       | ADC Master Mode Select                            |

| ADC_CTRL3           |     | MSTR     |         | 0 = Slave mode, ADCBCLK and ADCLRCLK              |

| 0Fh                 |     |          |         | are inputs to WM8594                              |

|                     |     |          |         | 1 = Master mode, ADCBCLK and                      |

|                     |     |          |         | ADCLRCLK are outputs from WM8594                  |

**Table 11 ADC Master Mode Control**

#### **SLAVE MODE**

In slave mode, the master clock to left/right clock ratio can be auto-detected or set manually by register write.

| REGISTER<br>ADDRESS | BIT | LABEL   | DEFAULT | DESCRIPTION          |

|---------------------|-----|---------|---------|----------------------|

| R3                  | 2:0 | DAC1_   | 000     | DAC MCLK:LRCLK Ratio |

| DAC1_CTRL2          |     | SR[2:0] |         | 000 = Auto detect    |

| 03h                 |     |         |         | 001 = 128fs          |

| R8                  | 2:0 | DAC2_   | 000     | 010 = 192fs          |

| DAC2_CTRL2          |     | SR[2:0] |         | 011 = 256fs          |

| 08h                 |     |         |         | 100 = 384fs          |

|                     |     |         |         | 101 = 512fs          |

|                     |     |         |         | 110 = 768fs          |

|                     |     |         |         | 111 = 1152fs         |

| R14                 | 2:0 | ADC_    | 000     | ADC MCLK:LRCLK Ratio |

| ADC_CTRL2           |     | SR[2:0] |         | 000 = Auto detect    |

| 0Eh                 |     |         |         | 001 = reserved       |

|                     |     |         |         | 010 = reserved       |

|                     |     |         |         | 011 = 256fs          |

|                     |     |         |         | 100 = 384fs          |

|                     |     |         |         | 101 = 512fs          |

|                     |     |         |         | 110 = 768fs          |

|                     |     |         |         | 111 = Reserved       |

Table 12 Slave Mode MCLK to LRCLK Ratio Control

## **DIGITAL AUDIO DATA SAMPLING RATES**

In a typical digital audio system there is one central clock source producing a reference clock to which all audio data processing is synchronised. This clock is often referred to as the audio system's master clock. The WM8594 uses independent master clocks for ADC and DACs. The external master clocks can be applied directly to the ADCMCLK, DACMCLK1 and DACMCLK2 input pins. In a system where there are a number of possible sources for the reference clock, it is recommended that the clock source with the lowest jitter be used for the master clock to optimise the performance of the WM8594.

In slave clocking mode the WM8594 has a master detection circuit that automatically determines the relationship between the master clock frequency (ADCMCLK, DACMCLK1, DACMCLK2) and the sampling rate (ADCLRCLK, DACLRCLK1, DACLRCLK2), to within +/- 32 system clock periods. The master clocks must be synchronised with the left/right clocks, although the device is tolerant of phase variations or jitter on the master clocks.

The ADC supports master clock to sampling clock ratios of 256fs to 768fs and sampling rates of 32kHz to 96kHz, provided the internal signal processing of the ADC is programmed to operate at the correct rate. The DACs support master clock to sampling clock ratios of 128fs to 1152fs and sampling rates of 32kHz to 192kHz, provided the internal signal processing of the DACs is programmed to operate at the correct rate.

Table 13 shows typical master clock frequencies and sampling rates supported by the WM8594 ADC. Table 14 shows typical master clock frequencies and sampling rates supported by the WM8594 DACs.

|                          | MASTER CLOCK FREQUENCY (MHZ) |             |             |             |  |  |  |

|--------------------------|------------------------------|-------------|-------------|-------------|--|--|--|

| Sampling Rate (ADCLRCLK) | 256fs                        | 384fs       | 512fs       | 768fs       |  |  |  |

| 32kHz                    | 8.192                        | 12.288      | 16.384      | 24.576      |  |  |  |

| 44.1kHz                  | 11.2896                      | 16.9344     | 22.5792     | 33.8688     |  |  |  |

| 48kHz                    | 12.288                       | 18.432      | 24.576      | 36.864      |  |  |  |

| 88.2kHz                  | 22.5792                      | 33.8688     | Unavailable | Unavailable |  |  |  |

| 96kHz                    | 24.576                       | Unavailable | Unavailable | Unavailable |  |  |  |

**Table 13 ADC Master Clock Frequency Versus Sampling Rate**

| Sampling Rate            |             |             | MASTER C    | NCY (MHZ)   |             |             |             |

|--------------------------|-------------|-------------|-------------|-------------|-------------|-------------|-------------|

| (DACLRCLK1<br>DACLRCLK2) | 128fs       | 192fs       | 256fs       | 384fs       | 512fs       | 768fs       | 1152fs      |

| 32kHz                    | Unavailable | Unavailable | 8.192       | 12.288      | 16.384      | 24.576      | 36.864      |

| 44.1kHz                  | Unavailable | 8.4672      | 11.2896     | 16.9344     | 22.5792     | 33.8688     | Unavailable |

| 48kHz                    | Unavailable | 9.216       | 12.288      | 18.432      | 24.576      | 36.864      | Unavailable |

| 88.2kHz                  | 11.2896     | 16.9344     | 22.5792     | 33.8688     | Unavailable | Unavailable | Unavailable |

| 96kHz                    | 12.288      | 18.432      | 24.576      | 36.864      | Unavailable | Unavailable | Unavailable |

| 176.4kHz                 | 22.5792     | 33.8688     | Unavailable | Unavailable | Unavailable | Unavailable | Unavailable |

| 192kHz                   | 24.576      | 36.864      | Unavailable | Unavailable | Unavailable | Unavailable | Unavailable |

Table 14 DAC Master Clock Frequency Versus Sampling Rate

#### **DIGITAL AUDIO DATA FORMATS**

The WM8594 supports a range of common audio interface formats:

- I<sup>2</sup>S

- Left Justified (LJ)

- Right Justified (RJ)

- DSP Mode A

- DSP Mode B

All formats send the MSB first and support word lengths of 16, 20, 24 and 32 bits, with the exception of 32 bit RJ mode, which is not supported.

Audio data for each stereo channel is time multiplexed with the interface's left/right clock indicating whether the left or right channel is present. The left/right clock is also used as a timing reference to indicate the beginning or end of the data words.

In LJ, RJ and I<sup>2</sup>S modes, the minimum number of bit clock periods per left/right clock period is two times the selected word length. The left/right clock must be high for a minimum of bit clock periods equivalent to the word length, and low for the same period. For example, for a word length of 24 bits, the left/right clock must be high for a minimum of 24 bit clock periods and low for a minimum of 24 bit clock periods. Any mark to space ratio is acceptable for the left/right clock provided these requirements are met.

In DSP modes A and B, left and right channels must be time multiplexed and input on DIN1. LRCLK is used as a frame synchronisation signal to identify the MSB of the first input word. The minimum number of bit clock periods per left/right clock period is two times the selected word length. Any mark to space ratio is acceptable for the left/right clock provided the rising edge is correctly positioned.

#### **I2S MODE**

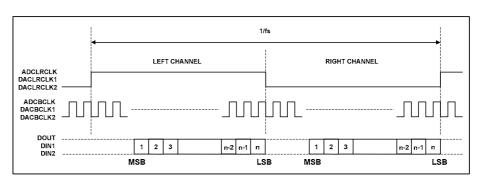

In I<sup>2</sup>S mode, the MSB of input data is sampled on the second rising edge of bit clock following a left/right clock transition. The MSB of output data changes on the first falling edge of bit clock following a left/right clock transition, and may be sampled on the next rising edge of bit clock. Left/right clocks are low during the left channel audio data samples and high during the right channel audio data samples.

Figure 12 I2S Mode Timing

#### **LEFT JUSTIFIED (LJ) MODE**

In LJ mode, the MSB of the input data is sampled by the WM8594 on the first rising edge of bit clock following a left/right clock transition. The MSB of output data changes on the same falling edge of bit clock as left/right clock and may be sampled on the next rising edge of bit clock. Left/right clock is high during the left channel audio data samples and low during the right channel audio data samples.

Figure 13 LJ Mode Timing

#### **RIGHT JUSTIFIED (RJ) MODE**

In RJ mode the LSB of input data is sampled on the rising edge of bit clock preceding a left/right clock transition. The LSB of output data changes on the falling edge of bit clock preceding a left/right clock transition, and may be sampled on the next rising edge of bit clock. Left/right clock is high during the left channel audio data samples and low during the right channel audio data samples.

Figure 14 RJ Mode Timing

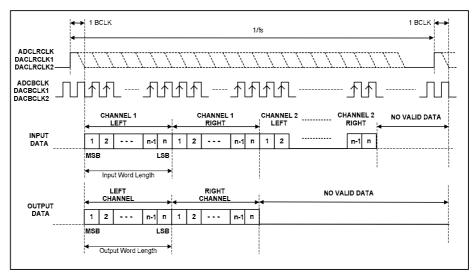

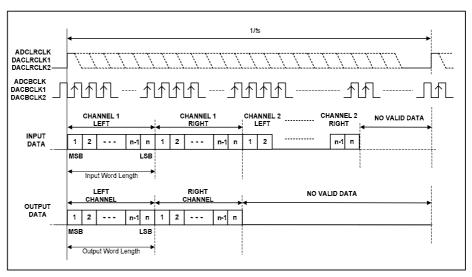

#### **DSP MODE A**

In DSP Mode A, the MSB of channel 1 left data input is sampled on the second rising edge of bit clock following a left/right clock rising edge. Channel 1 right data then follows. The MSB of output data changes on the first falling edge of bit clock following a left/right clock transition and may be sampled on the rising edge of bit clock. The right channel data is contiguous with the left channel data.

Figure 15 DSP Mode A Timing

#### **DSP MODE B**

In DSP Mode B, the MSB of channel 1 left data input is sampled on the first bit clock rising edge following a left/right clock rising edge. Channel 1 right data then follows. The MSB of output data changes on the same falling edge of BCLK as the low to high left/right clock transition and may be sampled on the rising edge of bit clock. The right channel data is contiguous with the left channel data.

Figure 16 DSP Mode B Timing

#### **DIGITAL AUDIO INTERFACE CONTROL**

The control of the audio interface formats is achieved by register write. Dynamically changing the audio data format may cause erroneous operation and is not recommended.

Interface timing is such that the input data and left/right clock are sampled on the rising edge of the interface bit clock. Output data changes on the falling edge of the interface bit clock. By setting the appropriate bit clock and left/tight clock polarity bits, the WM8594 ADC and DACs can sample data on the opposite clock edges.

The control of audio interface formats and clock polarities is summarised in Table 15.

| REGISTER<br>ADDRESS | BIT | LABEL    | DEFAULT | DESCRIPTION                                                    |

|---------------------|-----|----------|---------|----------------------------------------------------------------|

| R2                  | 1:0 | DAC1_    | 10      | DAC1 Audio Interface Format                                    |

| DAC1_CTRL1          |     | FMT[1:0] |         | 00 = Right Justified                                           |

| 02h                 |     |          |         | 01 = Left Justified                                            |

|                     |     |          |         | $10 = I^2 S$                                                   |

|                     |     |          |         | 11 = DSP                                                       |

|                     | 3:2 | DAC1_    | 10      | DAC1 Audio Interface Word Length                               |

|                     |     | WL[1:0]  |         | 00 = 16-bit                                                    |

|                     |     |          |         | 01 = 20-bit                                                    |

|                     |     |          |         | 10 = 24-bit                                                    |

|                     |     |          |         | 11 = 32-bit (not available in Right Justified mode)            |

|                     | 4   | DAC1_BCP | 0       | DAC1 BCLK Polarity                                             |

|                     |     |          |         | 0 = DACBCLK not inverted - data latched on rising edge of BCLK |

|                     |     |          |         | 1 = DACBCLK inverted - data latched on                         |

|                     |     |          |         | falling edge of BCLK                                           |

|                     | 5   | DAC1_LRP | 0       | DAC1 LRCLK Polarity                                            |

|                     |     |          |         | 0 = DACLRCLK not inverted                                      |

|                     |     |          |         | 1 = DACLRCLK inverted                                          |

| R7                  | 1:0 | DAC2_    | 10      | DAC2 Audio Interface Format                                    |

| DAC2_CTRL1          |     | FMT[1:0] |         | 00 = Right Justified                                           |

| 07h                 |     |          |         | 01 = Left Justified                                            |

|                     |     |          |         | $10 = I^2 S$                                                   |

|                     |     |          |         | 11 = DSP                                                       |

|                     | 3:2 | DAC2_    | 10      | DAC2 Audio Interface Word Length                               |

|                     |     | WL[1:0]  |         | 00 = 16-bit                                                    |

|                     |     |          |         | 01 = 20-bit                                                    |

|                     |     |          |         | 10 = 24-bit                                                    |

|                     |     |          |         | 11 = 32-bit (not available in Right Justified mode)            |

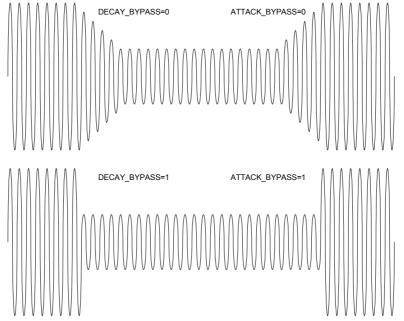

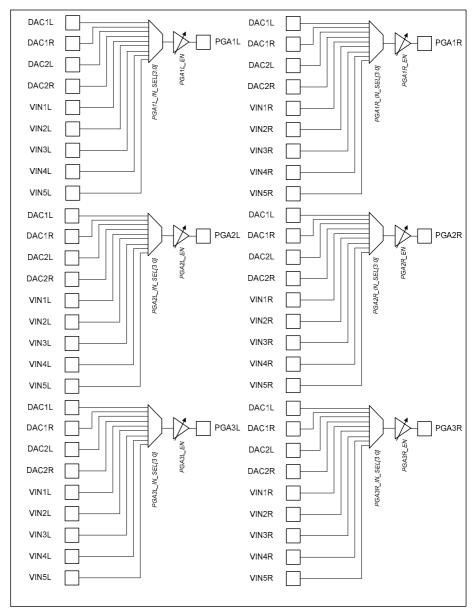

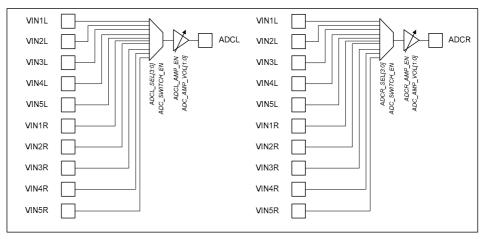

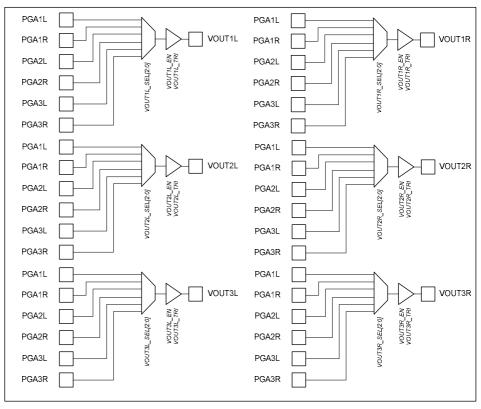

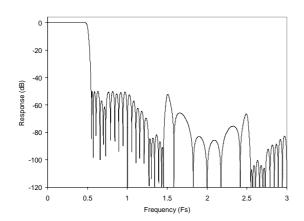

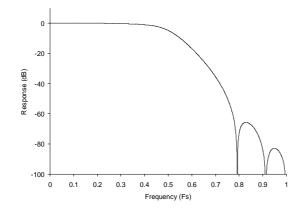

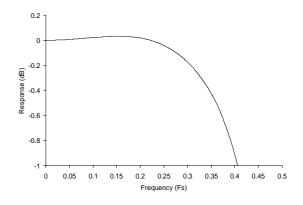

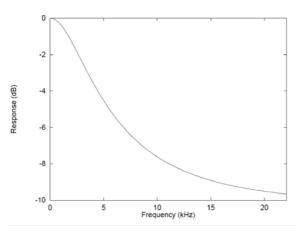

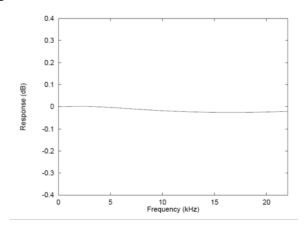

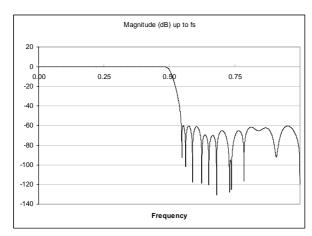

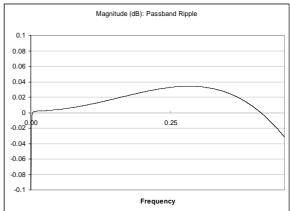

|                     | 4   | DAC2_BCP | 0       | DAC2 BCLK Polarity                                             |