National Semiconductor

April 1999

# LM1295

# **DC Controlled Geometry Correction System for Continuous Sync Monitors**

# **General Description**

The LM1295 is specifically designed for use in a continuous sync monitor. The injection-locked vertical oscillator operates from 50 Hz to 170 Hz, covering all known video monitors. A differential output current is provided in order to prevent ground interaction.

The IC provides two outputs composed of the summation of DC controlled 1st and 2nd order output terms. The first output corrects for EW pincushion and trapezoid. The second corrects for parallelogram and bow.

A DC controlled output is provided for vertical dynamic focus correction.

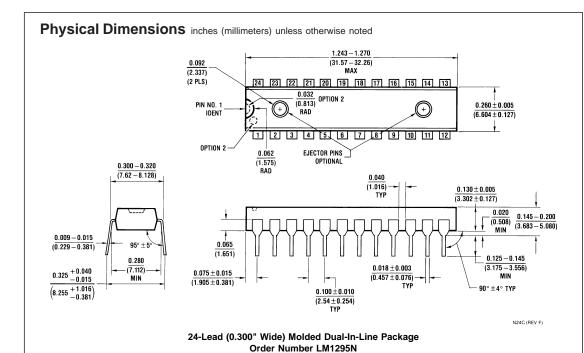

The IC is packaged in a 24-pin narrow DIP package and operates on a single 12V power supply.

#### **Features**

- Vertical scanning frequency 50 Hz-170 Hz

- DC controlled correction term amplitudes

- Up to 125 kHz bandwidth for dynamic input signals

- Minimum external parts count

- Multiple IC connection for convergence applications flexibility

- Stable vertical amplitude over temperature

- Compatible with the LM1291 Horizontal PLL in a H/V system

- Dynamic vertical deflection correction for second anode high voltage drop

- Both positive and negative going correction signals

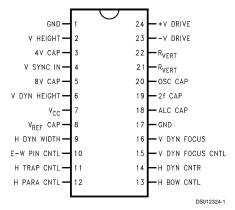

# **Connection Diagram**

FIGURE 1. Order Number LM1295N See NS Package Number N24C

© 1999 National Semiconductor Corporation

DS012324

# **Absolute Maximum Ratings** (Notes 1, 3)

If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/ Distributors for availability and specifications.

15V Supply Voltage

Input Voltage (DC, pins 2, 4, 6, 10, 11, 12, 13, 15) 5V  $5 V_{PP}$ Input Voltage (AC, Pin 4)

Power Dissipation (Note 4)

(Above 25 C Derate Based on  $\theta_{JA}$  and  $T_J$ )

1.8W Thermal Resistance  $(\theta_{JA})$ 70°C/W Junction Temperature (T<sub>J</sub>) 150°C

ESD Susceptibility (Note 5) 1.8 kV Storage Temperature –65°C to +150°C Lead Temperature (Soldering, 10 sec.) 265°C

# **Operating Ratings** (Note 2)

Operating Temperature Range -20°C to +80°C Supply Voltage ( $V_{CC}$ )  $10.8 \text{V} \leq \text{V}_{\text{CC}} \leq 13.2 \text{V}$

Input Voltage (DC, pins 2, 4, 6, 10, 11, 12, 13, 15)

Input Voltage (AC, pin 4)  $4 V_{PP}$

# **Electrical Characteristics**

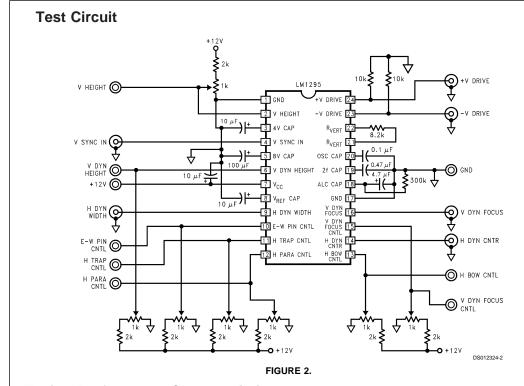

See Test Circuit (Figure 2); T<sub>A</sub> = 25°C; V<sub>CC</sub> = 12V.

| Symbol             | Parameter                                                                                          | Conditions                                                                                                             | Typical<br>(Note 6) | Limit<br>(Note 7) | Units                 |

|--------------------|----------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------|-----------------------|

| I <sub>cc</sub>    | Supply Current                                                                                     | All Control Inputs = 3V                                                                                                | 25                  | 35                | mA<br>(max)           |

| V <sub>REF</sub>   | Internal Ref Voltage at Pin 8                                                                      |                                                                                                                        | 8.2                 |                   | V                     |

| R <sub>IN</sub>    | Input Resistance                                                                                   | Pins 6, 10–13, 15                                                                                                      | 50                  | 30                | kΩ<br>(min)           |

| F <sub>FR</sub>    | Free-Run Frequency                                                                                 |                                                                                                                        | 45                  |                   | Hz                    |

| F <sub>max</sub>   | Maximum Frequency                                                                                  |                                                                                                                        | 170                 |                   | Hz                    |

| Cntlbw             | Control Inputs Bandwidth                                                                           | Pins 6, 10–13, 15                                                                                                      | 125                 |                   | kHz                   |

| V <sub>HTS</sub>   | Vertical Height Temperature<br>Stability                                                           | V Height = 4V, V Dyn Height = 3V,<br>F = 100 Hz, T <sub>A</sub> = 0°C to 70°C (Note 9)                                 | 1                   |                   | %                     |

| $V_{DIFF}$         | Vertical Differential Output Current                                                               | V Height = 4V, V Dyn Height = 4V,<br>Pin 24 Minus Pin 23                                                               |                     | 1                 | mA(min)               |

| V <sub>SYNH</sub>  | V Sync High Input Voltage                                                                          |                                                                                                                        |                     | 2.4               | V(min)                |

| V <sub>SYNL</sub>  | V Sync Low Input Voltage                                                                           |                                                                                                                        |                     | 0.8               | V<br>(max)            |

| V <sub>CMRR</sub>  | Vertical Output CMRR                                                                               | V <sub>O</sub> = 1V to 4V, V Height = 2V,<br>V Dyn Height = 3V                                                         | 30                  |                   | dB                    |

| V <sub>PSRR</sub>  | Vertical Output PSSR                                                                               | V <sub>CC</sub> = 10.8V to 13.2V, V Height = 2V,<br>V Dyn Height = 3V                                                  | 30                  |                   | dB                    |

| V <sub>OP-P</sub>  | Vertical Peak Output Voltage                                                                       | R <sub>L</sub> = 10k                                                                                                   | 6                   | 5                 | V <sub>PP</sub> (min) |

| $V_{RERR}$         | Vertical Ramp Distortion                                                                           | (Note 8) V Height = 4V,<br>V Dyn Height = 3V                                                                           | 1                   |                   | %                     |

| V <sub>SOERR</sub> | Vertical Parabola Distortion                                                                       | (Note 9) V Height = 2.2V, F = 100 Hz,<br>V Dyn Height = 3V                                                             | 8                   |                   | %                     |

| CR <sub>FO</sub>   | First Order (Ramp) Correction,<br>H Dyn Cntr (Pin 14)                                              | Pin 12 = 0V<br>Pin 12 = 4V<br>V Dyn Height = 3V, V Height = 4V,<br>Parabola Nulled                                     | 2.50<br>2.25        |                   | V <sub>PP</sub>       |

| CR <sub>FO</sub>   | First Order (Ramp) Correction,<br>H Dyn Width (Pin 19)                                             | Pin 11 = 0V<br>Pin 11 = 4V<br>V Dyn Height = 3V, V Height = 4V,<br>Parabola Nulled                                     | 0.85<br>0.75        |                   | V <sub>PP</sub>       |

| CP <sub>SO</sub>   | Parabola Correction Range,<br>H Dyn Cntr (Pin 14),<br>H Dyn Width (Pin 9),<br>V Dyn Focus (Pin 16) | Pins 10, 13, 15 = 0V Pins 10, 13, 15 = 4V V Dyn Height = 3V, V Height = 4V, Ramp Nulled for H Dyn Cntr and H Dyn Width | 1.2                 |                   | V <sub>PP</sub>       |

## **Electrical Characteristics** (Continued)

See Test Circuit (Figure 2); T<sub>A</sub> = 25°C; V<sub>CC</sub> = 12V.

| Symbol           | Parameter      | Conditions                                    | Typical<br>(Note 6) | Limit<br>(Note 7) | Units    |

|------------------|----------------|-----------------------------------------------|---------------------|-------------------|----------|

| V <sub>ODC</sub> | Output DC Bias | Pins 9, 14 and 16; All Control Inputs at 2.2V | 4.0                 |                   | $V_{DC}$ |

| Io               | Output Current | Pins 9, 14 and 16                             | 5.0                 |                   | mA       |

- Note 1: Absolute Maximum Ratings indicate limits beyond which damage to the device may occur.

- Note 2: Operating Ratings indicate conditions for which the device is functional, but do not guarantee specific performance limits. For guaranteed specifications and test conditions, see the Electrical Characteristics. The guaranteed specifications apply only for the test conditions listed. Some performance characteristics may degrade when the device is not operated under the listed test conditions.

- Note 3: All voltages are measured with respect to GND, unless otherwise specified.

- Note 4: The maximum power dissipation must be derated at elevated temperatures and is dictated by  $T_{Jmax}$ ,  $\theta_{JA}$ , and the ambient temperature,  $T_A$ . The maximum allowable power dissipation at any temperature is  $P_D = (T_{Jmax} T_A)/\theta_{JA}$  or the number given in the Absolute Maximum Ratings, whichever is lower. For this device,  $T_{Jmax} = 150^{\circ}\text{C}$ . The typical thermal resistance  $(\theta_{JA})$  of these parts when board mounted follow: LM1295N 70°C/W.

- Note 5: Human body model, 100 pF capacitor discharged through a 1.5 k $\Omega$  resistor.

- Note 6: Typicals are at  $T_A = T_J = 25^{\circ}C$  and represent most likely parametric norm.

- Note 7: Tested limits are guaranteed to National's AOQL (Average Outgoing Quality Level).

- Note 8: The deviation from a straight line drawn through measured points at 5% and 95% of the ramp is used to calculate distortion.

- Distortion = 100 (deviation, volts)/(95% value 5% value, volts). Deviations are measured at 1/3 and 3/3 of the ramp time period.

- Note 9: The deviation from a theoretical parabola drawn through the apex of the actual parabola is used to calculate distortion.

- Distortion = 100 (deviation, volts)/(theoretical parabola, volts) at measuring point. Nine points are measured.

- Note 10: The amplitude stability versus temperature is typically 1% or less at 100 Hz when a standard 10k 5% ¼W carbon film resistor is connected between pins 21 and 22 and located close to the package. The negative temperature coefficient of the resistor corrects for the negative temperature coefficient of the LM1295. The typical amplitude stability of the LM1295 by itself is 2%.

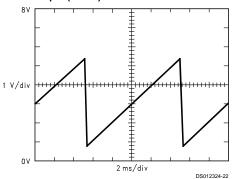

$\textbf{Typical Performance Characteristics} \ \ T_{A} = 25^{\circ}C, \ V_{Height} = 0V \ to \ 4V, \ V_{Dyn \ Height} = 3V$

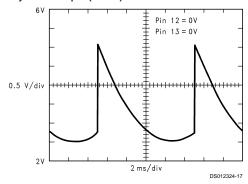

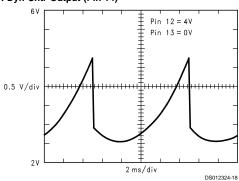

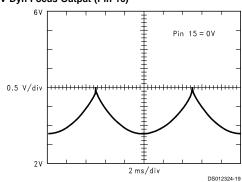

$\textbf{Typical Performance Characteristics} \ \, T_{A} = 25^{\circ}\text{C}, \, F = 100 \, \, \text{Hz}, \, V_{Height} = 4\text{V}, \, V_{Dyn \,\, Height} = 3\text{V}, \, \text{Test Circuit} - \textit{Figure 2}$ H Dyn Width Output (Pin 9) H Dyn Width Output (Pin 9) Pin 10 = 0V Pin 10 = 0V Pin 11 = 0V Pin 11 = 4V 0.5 V/div 0.5 V/div 2 ms/div 2 ms/div DS012324-10 DS012324-11 H Dyn Width Output (Pin 9) H Dyn Width Output (Pin 9) Pin 10 = 4V Pin 10 = 4V Pin 11 = 0V Pin 11 = 4V 0.5 V/div 2 ms/div 2 ms/div DS012324-13 DS012324-14 H Dyn Ctr Output (Pin 14) H Dyn Ctr Output (Pin 14) Pin 12 = 4V Pin 12 = 0V Pin 13 = 4V Pin 13 = 4V 0.5 V/div 0.5 V/div 2٧ 2 ms/div 2 ms/div DS012324-15 DS012324-16

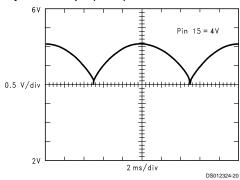

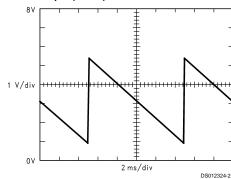

**Typical Performance Characteristics** T<sub>A</sub> = 25°C, F = 100 Hz, V<sub>Height</sub> = 4V, V<sub>Dyn Height</sub> = 3V, Test Circuit — *Figure 2* (Continued)

#### H Dyn Cntr Output (Pin 14)

#### H Dyn Cntr Output (Pin 14)

#### V Dyn Focus Output (Pin 16)

#### V Dyn Focus Output (Pin 16)

#### -V Drive Output (Pin 23)

#### +V Drive Output (Pin 24)

# **Circuit Description**

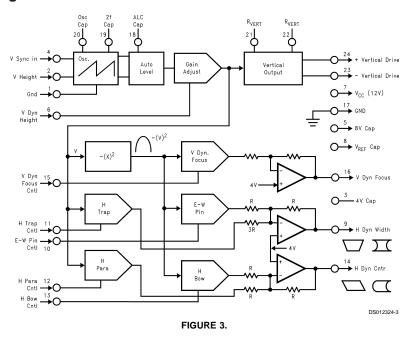

(See Figure 3, Block Diagram)

The LM1295 has outputs which provide signals for correcting the following CRT distortions: Vertical de-focusing, East-West pincushion, horizontal trapezoid, horizontal paral-

lelogram and horizontal bow. The amount and polarity of the corrections are controlled by voltages between 0V and 4V. The corrections track the vertical output amplitude.

The LM1295 has five major sections: the vertical oscillator/amplifier, the parabolic function generator and three voltage-controlled channels with the correction term outputs.

# Circuit Description (Continued)

#### **VERTICAL OSCILLATOR**

The vertical oscillator is an injection-locked ramp generator with automatic level control. The automatic level control maintains the oscillator output ramp height with changes in input frequency. The oscillator requires negative-going TTL level vertical sync pulses, wider than 200 ns, to lock. In the absence of vertical sync, the oscillator runs at free-run frequency. The vertical output amplitude is controlled by a voltage between 0V and 4V on the V Height input with a range of about 1.8 to 1, and by a voltage between 3V and 4V on the Vertical Dynamic Height input with a range of about 1.3 to 1. The control bandwidth of the V Height input is low due to the automatic level control, but that of the Vertical Dynamic Height is greater than 125 kHz. The oscillator has a circuit, requiring an external capacitor, 2f Cap, that prevents the oscillator from locking at twice the vertical sync frequency. The oscillator ramp voltage is converted into differential currents superimposed on DC currents of about 315 uA for each output. The voltage to current conversion gain is inversely proportional to the value of the resistor connected between the Rvert pins (21 and 22). Differential current outputs are provided instead of voltage to avoid ground noise. The ramp voltage goes to the parabolic function generator and to two multipliers used as voltage controlled amplifiers, one for horizontal trapezoid correction and the other for horizontal parallelogram correction.

#### PARABOLIC FUNCTION GENERATOR

The parabolic function generator makes a parabolic waveform from the vertical ramp. Its output goes to three multipliers used as voltage controlled amplifiers, one each for V Dyn Focus, E-W Pin, and H Bow.

#### **VOLTAGE CONTROLLED AMPLIFIERS**

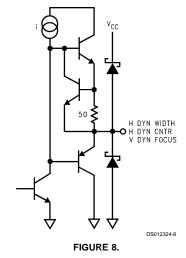

The V Dyn Focus voltage controlled amplifier is controlled by the V Dyn Focus Cntl input. Its output goes to an op amp whose output is V Dyn Focus. The voltage controlled amplifier has zero gain at approx. 2V input, maximum positive gain at 4V, and maximum negative gain at 0V. The E-W Pin, H Bow, H Trap and H Para voltage controlled amplifiers are identical to the V Dyn Focus stage, each adjusted by its corresponding Cntl input. The bandwidth of the Cntl inputs is greater than 125 kHz. The E-W Pin and H Bow amplifiers have the parabolic waveform as their input, and the H Trap and H Para amplifiers have the vertical ramp as their input. The parabolic waveform and the ramp amplitudes track the vertical output amplitude so the correction amplitudes follow accordingly. The outputs of the E-W Pin amplifier (parabola) and the H Trap amplifier (ramp) are summed together in an op amp summing circuit, with H Trap weight 1/3 that of E-W Pin. The output of the summing amplifier is H Dyn Width, used for correcting E-W pincushion and horizontal trapezoid distortion. The outputs of the H Bow amplifier (parabola) and the H Para amplifier (ramp) are summed together similarly, with H Bow and H Para equally weighted. The output of the summing amplifier is H Dyn Cntr, used for correcting horizontal bow and horizontal parallelogram distortion. All three op amp outputs are identical structures and are typical low output impedance type op amp outputs, capable of sinking or sourcing 5 mA minimum.

### **Block Diagram**

# **Pin Descriptions**

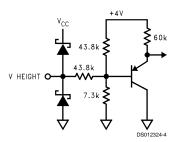

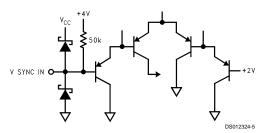

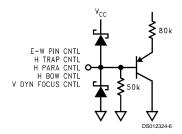

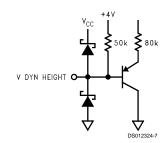

See  $\it Figure~4$  through  $\it Figure~8$  for Input and Output schematics.

**GND (Pin 1):** This pin should be connected to the power ground at pin 17.

V Height (Pin 2): Vertical Height. A voltage between 0V and 4V on this pin controls the amplitude of the +V and –V Drive currents, with increasing voltage giving increasing current. The control range is approximately 1.8 to 1. The response time is slow, being limited by the automatic level control loop.

**4 V Cap (Pin 3):** 4 Volt Cap Capacitor. A 10  $\mu$ F capacitor, aluminum electrolytic or tantalum, should be connected between pin 3 (positive side) and GND (pin 17) to bypass the internal 4V reference.

V Sync In (Pin 4): Vertical Sync Input. The vertical sync input takes a negative-going TTL level pulse which injection locks the vertical oscillator to the vertical sync frequency if it is above the LM1295 minimum frequency. The input threshold level is approximately 2V, so pulses other than TTL level are satisfactory as long as they cross the 2V threshold with at least a 400 mV margin either side. The minimum pulse width is approximately 200 ns. For free-running detection (no V Sync in), this input should be at logic high.

8 V Cap (Pin 5): 8 Volt Capacitor. A 100  $\mu$ F capacitor, aluminum electrolytic or tantalum, should be connected between pin 5 (positive side) and GND (pin 17) to bypass the internal 8V reference

V Dyn Height (Pin 6): Vertical Dynamic Height. A voltage between 3V and 4V on this pin controls the amplitude of the +V and -V Drive currents with increasing voltage giving increasing current. The control range is approximately 1.3 to 1. The bandwidth of this input is DC to greater than 125 kHz in contrast to the slow Vertical Height input.

$V_{CC}$  (Pin 7): Power, 12V nominal.  $V_{CC}$  should be bypassed to GND (pin 17) with a 10  $\mu$ F aluminum electrolytic or tantalum capacitor.

**Vref Cap (Pin 8):** Voltage Reference Cap. A 10  $\mu$ F capacitor, aluminum electrolytic or tantalum, should be connected between pin 8 (positive side) and GND (pin 17).

H Dyn Width (Pin 9): Horizontal Dynamic Width. This output consists of the sum of the vertical ramp and the parabola derived from the ramp. The amplitude and polarity of the ramp signal is DC controlled by H Trap Cntl (pin 11) and of the parabola by E-W Pin Cntl (pin 10). The weighting of the ramp is ½ the parabola; i.e., with the H Trap and E-W Pin Cntls at 4V, the output is 3 parts parabola and 1 part ramp. Horizontal Dynamic Width is used to correct for trapezoid and east-west pincushion distortion. The output stage is similar to a standard op-amp output. The bandwidth from either of the 2 control pins to the output is DC to greater than 125 kHz.

E-W Pin Cntl (Pin 10): East-West Pincushion Control. A voltage of 0V to 4V adjusts the polarity and the amount of parabola in the Horizontal Dynamic Width (pin 9) output. At approximately 2V, the amount is zero. From 2V to 4V, the amplitude increases and the parabola is positive-going. From 2V to 0V, the amplitude increases and the parabola is negative-going.

H Trap Cntl (Pin 11): Horizontal Trapezoid Control. A voltage of 0V to 4V adjusts the polarity and the amount of vertical ramp in the Horizontal Dynamic Width (pin 9) output. At approximately 2V, the amount is zero. From 2V to 4V, the amplitude increases and the ramp is positive-going. From 2V to 0V, the amplitude increases and the ramp is negative-going.

H Para Cntl (Pin 12): Horizontal Parallelogram Control. A voltage of 0V to 4V adjusts the polarity and the amount of vertical ramp in the Horizontal Dynamic Center (pin 14) output. At approximately 2V, the amount is zero. From 2V to 4V, the amplitude increases and the ramp is positive-going. From 2V to 0V, the amplitude increases and the ramp is negative-going.

H Bow Cntl (Pin 13): Horizontal Bow Control. A voltage of 0V to 4V adjusts the polarity and the amount of parabola in the Horizontal Dynamic Center (pin 14) output. At approximately 2V, the amount is zero. From 2V to 4V, the amplitude increases and the parabola is positive-going. From 2V to 0V, the amplitude increases and the parabola is negative-going.

H Dyn Cntr (Pin 14): Horizontal Dynamic Center. This output consists of the sum of the vertical ramp and the parabola derived from the ramp. The amplitude and polarity of the ramp signal is DC controlled by H Para Cntl (pin 12) and of the parabola by H Bow Cntl (pin 13). The difference between this output and the Horizontal Dynamic Width output is in the weighting of the ramp, which is equal to the parabola; i.e., with the H Para and H Bow Cntls at 4V, the output is 1 part parabola and 1 part ramp. Horizontal Dynamic Center is used to correct for parallelogram and bow distortion. The output stage is similar to a standard op-amp output. The bandwidth from either of the 2 control pins to the output is DC to greater than 125 kHz.

V Dyn Focus Cntl (Pin 15): Vertical Dynamic Focus Control. A voltage of 0V to 4V adjusts the polarity and the amount of parabola in the Vertical Dynamic Focus (pin 16) output. At approximately 2V, the amount is zero. From 2V to 4V, the amplitude increases and the parabola is positivegoing. From 2V to 0V, the amplitude increases and the parabola is negative-going.

V Dyn Focus (Pin 16): Vertical Dynamic Focus. This output consists of the parabola derived from the vertical ramp. The amplitude and polarity are controlled by V Dyn Focus Cntl. The output stage is similar to a standard op-amp output. The bandwidth from the control pin to the output is DC to greater than 125 kHz.

**GND** (Pin 17): Ground. This is the power supply ground for the 12V supply and the point to which the bypass capacitors are returned.

**ALC Cap (Pin 18):** Automatic Level Control Capacitor. This capacitor is part of the level control circuit that maintains constant vertical height in spite of vertical sync frequency changes. The recommended value is 4.7  $\mu$ F, aluminum electrolytic or tantalum capacitor. If the VCO capacitor value is changed, this capacitor value should change in the same ratio. A 300k resistor should be connected from this pin to ground.

**2f Cap (Pin 19):** Double frequency Capacitor. This capacitor prevents the vertical oscillator from locking at twice the vertical sync frequency. The recommended value is  $0.47~\mu\text{F}$ . If the VCO capacitor value is changed, this capacitor value should change in the same ratio.

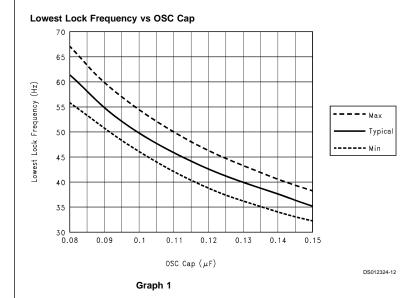

**Osc Cap (Pin 20):** A timing capacitor is connected from this pin to ground for the internal oscillator. The capacitance determines the lowest lock frequency. See Graph 1.

Rvert (Pin 21): Vertical Resistor. One end of the Vertical Resistor connects to this pin. This resistor determines the gain of the vertical ramp current generator. The gain is inversely proportional to the resistance. It is recommended that this be a standard 5% 1/4W carbon film resistor whose negative tem-

# Pin Descriptions (Continued)

perature coefficient corrects for the negative temperature coefficient of the LM1295. The resistor should be located near the LM1295. The recommended value is 10 k $\Omega$ .

Rvert (Pin 22): Vertical Resistor. The other end of the Vertical Resistor connects to this pin.

**– V Drive (Pin 23):** – Vertical Drive. This is the negative-going vertical ramp output current of the differential pair. The ramp current waveform is superimposed on a direct

current of approximately 315  $\mu A$ . The waveform amplitude is determined by the Vertical Height (pin 2) control voltage and the Vertical Dynamic Height (pin 6) control voltage. The current can be converted into voltage by a resistor (typically 10  $k\Omega$ ) to ground or by a differential amplifier using the differential currents as inputs. The voltage compliance of the output is typically 6V.

+ V Drive (Pin 24): + Vertical Drive. This is the same as – V Drive except it is the positive-going output current of the differential pair.

# **Input/Output Schematics**

FIGURE 4.

FIGURE 5.

FIGURE 6.

FIGURE 7.

# Typical Application LM1295 GND V DRIVE 22 V HEIGHT V SYNC V SYNC V SYNC V HIGHT 10 µF 10 µ

11 H TRAP CNTL 12 H PARA CNTL

100 μF

H WIDTH

DS012324-9

TO H WIDTH ONE-SHOT (CAP CHARGING CURRENT)

Note: LM1295 is designed to drive a differential input vertical deflection amplifier. The LM1295, however, can also drive a single-ended input vertical deflection amplifier by just using either the +V drive or -V drive pins.

H DYN 14 CNTR H BOW 13 CNTL

10k

FIGURE 9.

NS Package Number N24C

# LIFE SUPPORT POLICY

NATIONAL'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT AND GENERAL COUNSEL OF NATIONAL SEMICONDUCTOR CORPORATION. As used herein:

- 1. Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- 2. A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.national.com

#### National Semiconductor Europe

Fax: +49 (0) 1 80-530 85 86 Fax: +49 (0) 1 80-530 85 86 Email: europe. support@nsc.com Deutsch Tel: +49 (0) 1 80-530 85 85 English Tel: +49 (0) 1 80-532 78 32 Français Tel: +49 (0) 1 80-532 93 58 Italiano Tel: +49 (0) 1 80-534 16 80

National Semiconductor Asia Pacific Customer Response Group Fax: 65-2504466 Email: sea.support@nsc.com National Semiconductor Japan Ltd. Tel: 81-3-5639-7560 Fax: 81-3-5639-7507

National does not assume any responsibility for use of any circuitry described, no circuit patent licenses are implied and National reserves the right at any time without notice to change said circuitry and specifications.