### **DATA SHEET**

## HFC - U 2BD

# ISDN HDLC FIFO controller for U interface

Copyright 1994, 1995, 1996 Cologne Chip Designs All Rights Reserved

The information presented can not be considered as assured characteristics. Data can change without notice. Parts of the information presented may be protected by patent or other rights.

March 1997

#### Contents

| 1 General description                                                   |      |

|-------------------------------------------------------------------------|------|

| 1.1 Applications                                                        |      |

| 1.2 Mode description                                                    |      |

| 1.2.1 ISA-PC mode                                                       |      |

| 1.2.2 Processor interface modes                                         | 6    |

| 2 Pin description                                                       | 7    |

| 2.1 ISA-PC bus and microprocessor interface                             |      |

| 2.2 SRAM Interface                                                      |      |

| 2.3 Oscillator                                                          |      |

| 2.4 GCI/IOM bus interface                                               |      |

| 2.5 Slot enable signals                                                 |      |

| 2.6 Interrupt outputs                                                   |      |

| 2.7 Reset                                                               |      |

| 2.8 Miscellaneous pins                                                  |      |

| 2.9 Power supply                                                        |      |

| 2.10 RESET characteristics                                              | .12  |

| 3 Functional description                                                | 12   |

| 3.1 ISA-PC mode                                                         |      |

| 3.1.1 Programming of I/O addresses                                      |      |

| 3.1.2 ISA-PC bus interface                                              |      |

| 3.2 Processor mode                                                      |      |

| 3.3 Register description                                                |      |

| 3.3.1 FIFO control registers                                            |      |

| 3.3.2 Registers of the GCI/IOM bus section                              |      |

| 3.3.3 Interrupt and status register                                     |      |

| 3.4 Watchdog / timer                                                    |      |

| 3.5 FIFOs                                                               |      |

| 3.5.1 FIFO channel operation                                            |      |

| 3.5.1.1 Send channels (B1, B2 and D transmit)                           |      |

| 3.5.1.2 FIFO full condition in send channels                            |      |

| 3.5.1.3 Receive Channels (B1, B2 and D reiceive)                        | .21  |

| 3.5.1.4 FIFO full condition in receive channels                         |      |

| 3.5.1.5 FIFO initialisation                                             |      |

| 3.5.2 Transparent mode of HFC-U                                         |      |

| 3.6 External SRAM                                                       |      |

| 3.7 Busy synchronisation                                                |      |

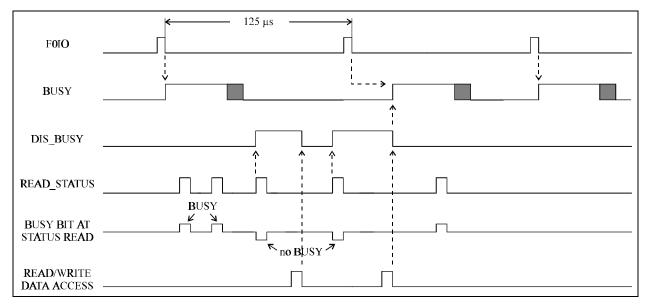

| 3.7.1 Busy synchronisation with status read                             | .26  |

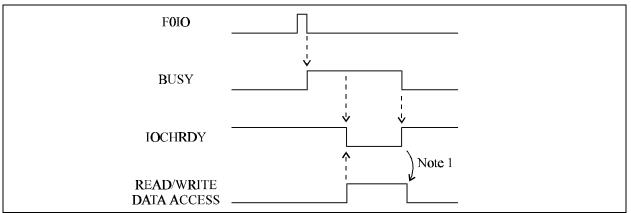

| 3.7.2 Busy synchronisation with IOCHRDY                                 | .27  |

| 4 Register bit description                                              | .28  |

| 4.1 Register bit description of GCI/IOM bus section                     | .28  |

| 4.2 Register bit description of interrupt, status and control registers |      |

|                                                                         |      |

| 5 Electrical characteristics                                            | .35  |

| 6 Timing characteristics                                                | .37  |

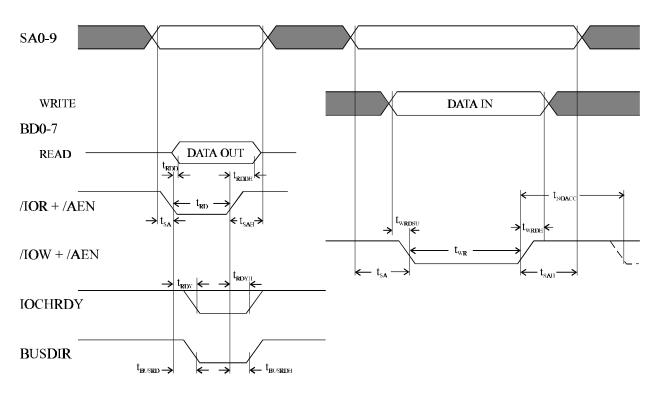

| 6.1 ISA-PC bus or processor access                                      |      |

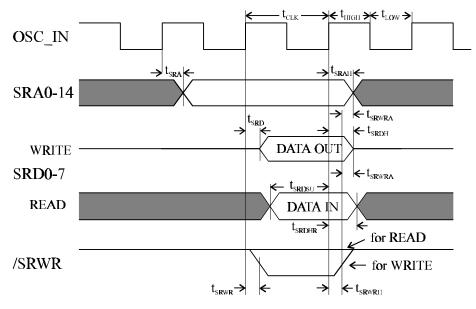

| 6.2 SRAM access                                                         |      |

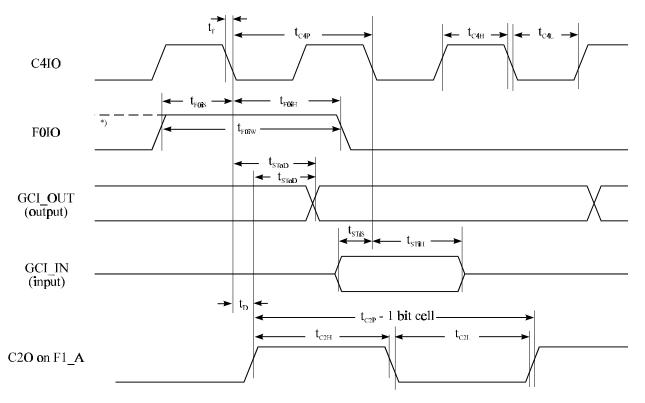

| 6.3 GCI/IOM timing                                                      | . 39 |

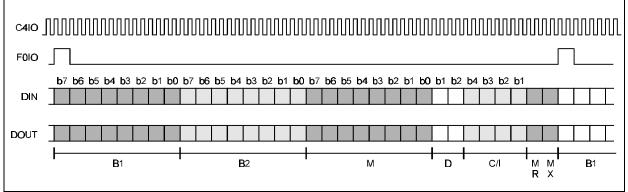

| 7 GCI frame structure                                                   | 41   |

|                                                                         |      |

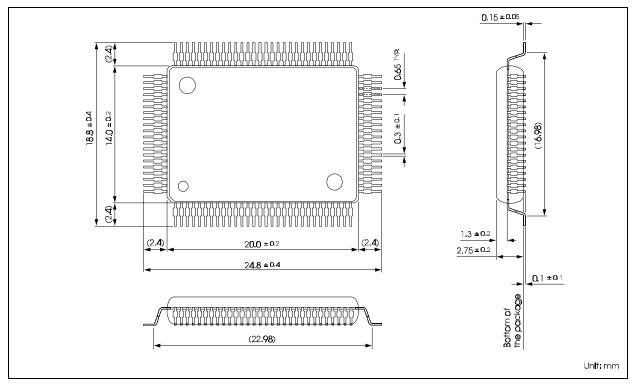

| 8 HFC-U package dimensions                                              | .42  |

#### Figures

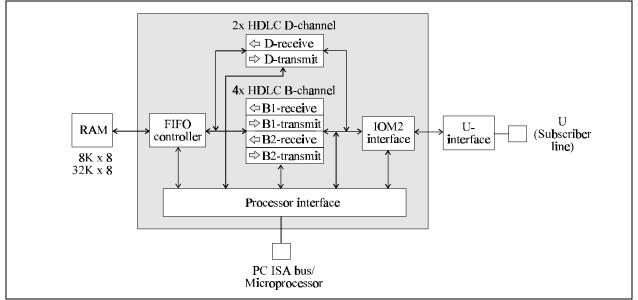

| Figure 1: HFC-U block diagram                                            | 5 |

|--------------------------------------------------------------------------|---|

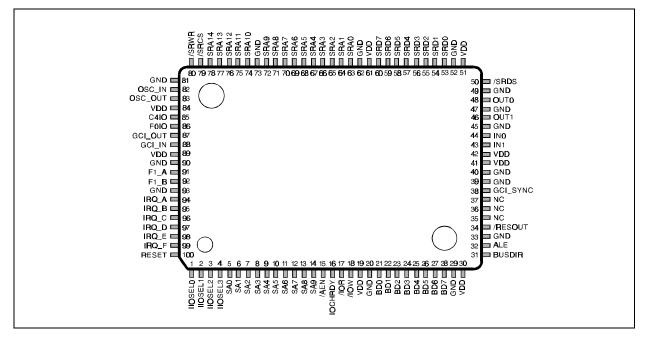

| Figure 2: Pin Connection                                                 |   |

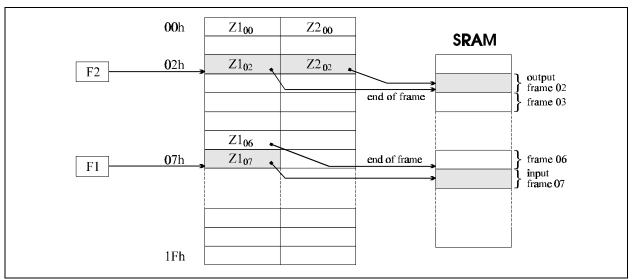

| Figure 3: FIFO Organisation (shown for B-channel, similar for D-channel) |   |

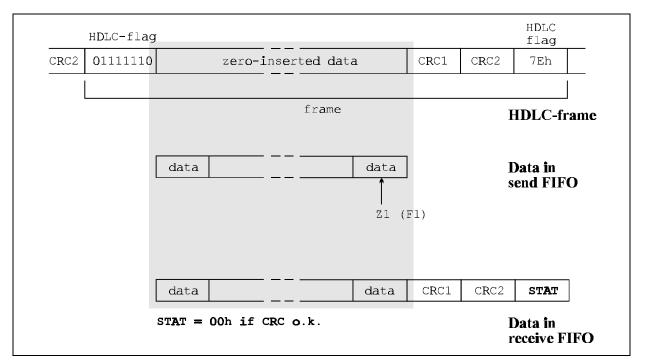

| Figure 4: FIFO Data Organisation                                         |   |

| Figure 5: Timing relations and delayed BUSY                              |   |

| Figure 6: Function of IOCHRDY                                            |   |

| Figure 7: Single channel GCI format                                      |   |

| Figure 8: HFC-U package dimensions                                       |   |

#### Tables

| Table 1: Selected I/O address after reset | .13  |

|-------------------------------------------|------|

| Table 2: SRAM size and FIFO depth         | . 25 |

#### **Timing Diagrams**

| Timing Diagram 1: ISA-PC bus or processor access |  |

|--------------------------------------------------|--|

| Timing Diagram 2: SRAM access                    |  |

| Timing Diagram 3: GCI/IOM timing                 |  |

### Features

- Independent Read and Write HDLC-Channels f or 2 ISDN B-channels and one ISDN Dchannel

- B1 and B2 transparent mode independently selectable

- FIFO-depth: 4x 7.5 KByte (B-channel) and 2x 512 Byte (D-channel)

- max. 31 HDLC frames (B-channel) and 15 HDLC frames (D-channel) per channel and direction in FIFO

- 56 kbit/s restricted mode for U.S. ISDN lines selectable

- PCM30 interface configurable to interface MITEL ST <sup>TM</sup> bus (MVIP<sup>TM</sup>), Siemens IOM2 <sup>TM</sup> or GCI<sup>TM</sup> for interface to U-chip

- O direct 8 bit ISA-PC bus interface with buffers for ISA-databus

- One of 6 interrupt channels on ISA-PC bus selectable by software

- Only 2 I/O-addresses used on ISA-PC bus

- programmable ISA-I/O-addresses

- microprocessor interface compatible to Motorala bus and Siemens/Intel bus

- Timer with interrupt and watchdog capability in processor mode

- 3-5V supply voltage

- rectangular QFP 100 case

### **1** General description

The HFC-U is an ISDN HDLC basic rate controller for so called "passive" ISDN PC cards with integrated interface to U-chip. It only needs a U-chip and an external SRAM to form a high performance ISDN PC card. Most problems with passive ISDN PC cards as small FIFOs and massive interrupt load for the host CPU are overcome by the HFC-U. So we call ISDN cards with the HFC-U "semi-active".

Additionally the HFC-U can be used as a microprocessor peripheral in non-PC applications.

The FIFOs of the HFC-U are realized with an external SRAM. Also an industrial standard serial interface for telecom peripheral ICs is implemented. A U-chip is normally connected to this interface.

#### 1.1 Applications

- O ISDN PC card

- ISDN terminal adapter

- O ISDN PABX

- O ISDN modems

Figure 1: HFC-U block diagram

#### **1.2** Mode description

The HFC-U has 4 different bus modes, which can be selected by the lines ALE and IIOSEL0-IIOSEL3.

Depending on the selected mode the function of several pins is different (see: Pin description).

#### 1.2.1 ISA-PC mode

Mode 1: ALE to GND, IIOSEL3-0 from 0001 to 1111

In mode 1 the HFC-U is addressed by two successive port addresses on the ISA-PC bus. The port address is selected by the lines SA0 - SA9.

The address with SA0='1' is for register selection and the address with SA0='0' is used for data read/write (see also: 3.1).

#### **1.2.2** Processor interface modes

The processor modes are selected by IIOSEL3-0 = '0000' (see also 3.2).

- Mode 2: Motorola bus with control signals /CS, R/W, /DS is selected by setting ALE to VDD.

- Mode 3: Siemens/Intel bus with seperated address bus and databus and control signals /CS, /WR, /RD is selected by setting ALE to GND.

- Mode 4: Intel bus with multiplexed address and databus with control signals /CS, /WR, /RD, ALE. ALE latches the address. The addresslines SA0-SA7 must be connected to the datalines BD0-BD7.

The lines SA0-SA7 are used for direct addressing the internal registers of the HFC-U.

### 2 Pin description

Figure 2: Pin Connection

| Pin No. | Pin Name | Input                      | Mode  | Function                        |

|---------|----------|----------------------------|-------|---------------------------------|

|         |          | <u>O</u> utput<br>Tristate |       |                                 |

|         |          |                            |       | Mode/initial I/O address select |

| 1       | IIOSEL0  | I <sup>u)</sup>            | all   | bit 0                           |

| 2       | IIOSEL1  | I <sup>u)</sup>            | all   | bit 1                           |

| 3       | IIOSEL2  | I <sup>u)</sup>            | all   | bit 2                           |

| 4       | IIOSEL3  | I <sup>u)</sup>            | all   | bit 3                           |

|         |          |                            |       | Regsiter/ISA-PC address bus     |

| 5       | SA0      | Ι                          | all   | Address bit 0                   |

| 6       | SA1      | Ι                          | all   | Address bit 1                   |

| 7       | SA2      | Ι                          | all   | Address bit 2                   |

| 8       | SA3      | Ι                          | all   | Address bit 3                   |

| 9       | SA4      | Ι                          | all   | Address bit 4                   |

| 10      | SA5      | Ι                          | all   | Address bit 5                   |

| 11      | SA6      | Ι                          | all   | Address bit 6                   |

| 12      | SA7      | Ι                          | all   | Address bit 7                   |

| 13      | SA8      | Ι                          | 1     | Address bit 8                   |

|         |          | Ι                          | 2,3,4 | must be connected to GND or VDD |

| 14      | SA9      | Ι                          | 1     | Address bit 9                   |

|         |          | Ι                          | 2,3,4 | must be connected to GND or VDD |

#### 2.1 ISA-PC bus and microprocessor interface

<sup>u)</sup> internal pull up

| Pin No. | Pin Name | <u>I</u> nput    | Mode  | Function                                                                   |

|---------|----------|------------------|-------|----------------------------------------------------------------------------|

|         |          | <u>O</u> utput   |       |                                                                            |

|         |          | <u>T</u> ristate |       |                                                                            |

| 15      | /AEN     | Ι                | 1     | PC bus address enable                                                      |

|         | /CS      | Ι                | 2,3,4 | chipselect low active                                                      |

| 16      | IOCHRDY  | OT <sup>1)</sup> | 1     | I/O channel ready                                                          |

|         |          | OT <sup>1)</sup> | 2,3,4 | low active wait signal for external processor                              |

| 17      | /IOR     | Ι                | 1,3,4 | I/O read enable                                                            |

|         | /DS      | Ι                | 2     | I/O data strobe                                                            |

| 18      | /IOW     | Ι                | 1,3,4 | I/O write enable                                                           |

|         | R/W      | Ι                | 2     | Read/Write select (WR='0')                                                 |

| 21      | BD0      | I/O              | all   | Databus bit 0 (LSB)                                                        |

| 22      | BD1      | I/O              | all   | Databus bit 1                                                              |

| 23      | BD2      | I/O              | all   | Databus bit 2                                                              |

| 24      | BD3      | I/O              | all   | Databus bit 3                                                              |

| 25      | BD4      | I/O              | all   | Databus bit 4                                                              |

| 26      | BD5      | I/O              | all   | Databus bit 5                                                              |

| 27      | BD6      | I/O              | all   | Databus bit 6                                                              |

| 28      | BD7      | I/O              | all   | Databus bit 7 (MSB)                                                        |

| 31      | BUSDIR   | 0                | all   | Databus direction signal for external busdriver<br>'0' BD0-BD7 are outputs |

| 32      | ALE      | Ι                |       | Address latch enable                                                       |

|         |          |                  |       | ALE to GND and IIOSEL0-3 $\neq$ 0000: mode 1                               |

|         |          |                  |       | ALE to VDD and IIOSEL0-3=0000: mode 2                                      |

|         |          |                  |       | ALE to GND and IIOSEL0-3=0000: mode 3                                      |

|         |          |                  |       | pulse on ALE and IIOSEL0-3=0000: mode 4                                    |

<sup>1)</sup> open drain, external pull up resistor required

#### 2.2 SRAM Interface

| Pin No. | Pin Name | Input                              | Function                     |

|---------|----------|------------------------------------|------------------------------|

|         |          | <u>O</u> utput<br><u>T</u> ristate |                              |

|         |          |                                    | SRAM data bus                |

| 53      | SRD0     | I/O                                | SRAM data bit 0 (LSB)        |

| 54      | SRD1     | I/O                                | SRAM data bit 1              |

| 55      | SRD2     | I/O                                | SRAM data bit 2              |

| 56      | SRD3     | I/O                                | SRAM data bit 3              |

| 57      | SRD4     | I/O                                | SRAM data bit 4              |

| 58      | SRD5     | I/O                                | SRAM data bit 5              |

| 59      | SRD6     | I/O                                | SRAM data bit 6              |

| 60      | SRD7     | I/O                                | SRAM data bit 7 (MSB)        |

|         |          |                                    | SRAM address bus             |

| 63      | SRA0     | 0                                  | SRAM address bus bit 0 (LSB) |

| 64      | SRA1     | 0                                  | SRAM address bus bit 1       |

March 1997

| Pin No. | Pin Name | <u>I</u> nput    | Function                       |

|---------|----------|------------------|--------------------------------|

|         |          | <u>O</u> utput   |                                |

|         |          | <u>T</u> ristate |                                |

| 65      | SRA2     | 0                | SRAM address bus bit 2         |

| 66      | SRA3     | 0                | SRAM address bus bit 3         |

| 67      | SRA4     | 0                | SRAM address bus bit 4         |

| 68      | SRA5     | 0                | SRAM address bus bit 5         |

| 69      | SRA6     | 0                | SRAM address bus bit 6         |

| 70      | SRA7     | 0                | SRAM address bus bit 7         |

| 71      | SRA8     | 0                | SRAM address bus bit 8         |

| 72      | SRA9     | 0                | SRAM address bus bit 9         |

| 74      | SRA10    | 0                | SRAM address bus bit 10        |

| 75      | SRA11    | 0                | SRAM address bus bit 11        |

| 76      | SRA12    | 0                | SRAM address bus bit 12        |

| 77      | SRA13    | 0                | SRAM address bus bit 13        |

| 78      | SRA14    | 0                | SRAM address bus bit 14 (MSB)  |

|         |          |                  | SRAM control signals           |

| 50      | /SRDS    | Ο                | Data strobe to external device |

| 79      | /SRCS    | 0                | SRAM chip select               |

| 80      | /SRWR    | 0                | SRAM write enable              |

#### 2.3 Oscillator

| 82 | OSC_IN  | Ι | Oscillator input or quarz connection<br>12.288 Mhz for HFC-U with PCM30 bus function |

|----|---------|---|--------------------------------------------------------------------------------------|

| 83 | OSC_OUT | 0 | Oscillator output or quarz connection                                                |

#### 2.4 **GCI/IOM** bus interface

| Pin No. | Pin Name | <u>I</u> nput<br>Output<br><u>T</u> ristate | Mode | Function                                      |

|---------|----------|---------------------------------------------|------|-----------------------------------------------|

| 85      | C4IO     | I/O <sup>u)</sup>                           | all  | double bit clock                              |

|         |          |                                             |      | GCI/IOM bus clock master output               |

|         |          |                                             |      | GCI/IOM bus clock slave input (reset default) |

| 86      | F0IO     | I/O <sup>u)</sup>                           | all  | Frame synchronisation, 8kHz pulse for GCI/IOM |

|         |          |                                             |      | bus frame synchronisation                     |

|         |          |                                             |      | GCI/IOM bus master output                     |

|         |          |                                             |      | GCI/IOM bus slave input (reset default)       |

| 87      | GCI_OUT  | I/OT <sup>u)</sup>                          | all  | GCI/IOM bus data II output                    |

|         |          |                                             |      | B1/B2 slot programmable as input or output    |

| 88      | GCI_IN   | I/OT <sup>u)</sup>                          | all  | GCI/IOM bus data I input                      |

|         |          |                                             |      | B1/B2 slot programmable as input or output    |

| 38      | GCI_SYNC | I <sup>u)</sup>                             | all  | synchronisation input for GCI in master mode  |

|         |          |                                             |      | Must be feed with 8 kHz signal or left open.  |

<sup>u)</sup> internal pull up

# **2.5** Slot enable signals (e. g. for PCM codecs)

| 91 | F1_A | 0 | all | enable signal for external CODEC A<br>Programmable as positive (reset default) or<br>negative pulse.                  |

|----|------|---|-----|-----------------------------------------------------------------------------------------------------------------------|

| 92 | F1_B | 0 | all | enable signal for external CODEC B or 2nd HFC-<br>U<br>Programmable as positive (reset default) or<br>negative pulse. |

#### 2.6 **Interrupt outputs**

| Pin No. | Pin Name | <u>I</u> nput<br><u>O</u> utput<br><u>T</u> ristate | Mode  | Function                                     |

|---------|----------|-----------------------------------------------------|-------|----------------------------------------------|

| 94      | IRQ_A    | OT                                                  | 1     | PC bus interrupt request A                   |

|         | /IRQ_P   | OT <sup>1)</sup>                                    | 2,3,4 | processor interrupt request low active       |

| 95      | IRQ_B    | OT                                                  | 1     | PC bus interrupt request B                   |

|         | IRQ_P    | OT <sup>2)</sup>                                    | 2,3,4 | processor interrupt request high active      |

| 96      | IRQ_C    | OT                                                  | 1     | PC bus interrupt request C                   |

|         | /WD_RES  | OT <sup>1)</sup>                                    | 2,3,4 | Watchdog expired, external reset low active  |

| 97      | IRQ_D    | OT                                                  | 1     | PC bus interrupt request D                   |

|         | WD_RES   | OT <sup>2)</sup>                                    | 2,3,4 | Watchdog expired, external reset high active |

| 98      | IRQ_E    | OT                                                  | 1     | PC bus interrupt request E                   |

| 99      | IRQ_F    | OT                                                  | 1     | PC bus interrupt request F                   |

1)

open drain, external pull up resistor required open source, external pull down resistor required 2)

#### 2.7 Reset

| 34  | /RESOUT | 0 |     | Reset output for external device (low active)<br>/RESOUT becomes active when RESET is active<br>or soft reset is active |

|-----|---------|---|-----|-------------------------------------------------------------------------------------------------------------------------|

| 100 | RESET   | Ι | all | Reset for HFC-U (high active)                                                                                           |

#### **Miscellaneous pins** 2.8

| 35, 36, | NC   |   |     | No connection (leave pins open)            |

|---------|------|---|-----|--------------------------------------------|

| 37      |      |   |     |                                            |

| 44      | IN0  | Ι | all | input pin 0, e. g. for power U-line detect |

| 43      | IN1  | Ι | all | input pin 1, e. g. for power U-line detect |

| 48      | OUT0 | Ο | all | output pin 0, e. g. for external LEDs      |

| 46      | OUT1 | 0 | all | output pin 1, e. g. for external LED       |

#### 2.9 **Power supply**

| Pin No.                         | Pin Name | Function         |

|---------------------------------|----------|------------------|

| 19, 30, 41, 42, 51, 61, 84, 89  | VDD      | VDD (+3V to +5V) |

| 20, 29, 33, 39, 40, 45, 47, 49, | GND      | GND              |

| 52, 62, 73, 81, 90, 93          |          |                  |

#### dimportant!

All power supply pins VDD and GND must be directly connected to each other.

To keep VDD and GND bounce to a minimum a bypass capacitor (10 nF to 100 nF) should be placed between each pair of VDD/GND pins.

#### 2.10 **RESET** characteristics

C4IO and F0IO are inputs are reset.

The lines F1\_A and F1\_B are '0'.

Registers which are cleared are explained in the register section of this data sheet.

### **3** Functional description

#### 3.1 ISA-PC mode

#### 3.1.1 Programming of I/O addresses

The HFC-U occupies two consecutive addresses in the I/O map of a PC if it is in ISA-PC mode. It decodes only the 10 lower address lines as most slot cards do on the ISA-PC bus. On the lower of both addresses SA0 = 0; on the higher SA0=1.

After every Master Reset (RESET = 1) the I/O address select circuit inside the HFC-U is in hardware mode. In this mode the HFC-U can not be accessed until it is initialised to an I/O address.

At first one of 15 different I/O addresses must be selected by the 4 inputs IIOSEL0 .. IIOSEL3 as Table 1 shows:

| IIOSEL  | Selected I/O address |

|---------|----------------------|

| 3210    |                      |

| 0 0 0 0 | processor mode       |

| 0001    | 2E0h                 |

| 0010    | 2D0h                 |

| 0011    | 210h                 |

| 0100    | 2C0h                 |

| 0101    | 200h                 |

| 0110    | 2F8h                 |

| 0111    | 2E8h                 |

| 1000    | 2B0h                 |

| 1001    | 3E0h                 |

| 1010    | 320h                 |

| 1011    | 278h                 |

| 1100    | 310h                 |

| 1101    | 330h                 |

| 1110    | 300h                 |

| 1111    | 3E8h                 |

Table 1: Selected I/O address after reset

The hardware selected I/O address might have an address collision with another I/O device in the PC.

After a hardware reset (RESET = 1) you must first write an I/O address into the HFC-U to set the I/O address for every further access to the device.

#### The procedure is as follows:

First you must write the lower 8 bits of the new I/O address you want into the lower address (SA0 = 0) of the hardware selected I/O address. The LSB of the new address is a don't care bit because the HFC-U always occupies two I/O addresses.

Then the additional 2 bits of the new I/O address have to be written into the higher address (SA0 = 1) of the hardware selected I/O address. The other 6 bits in the byte must have a special pattern to switch over to the software selected address mode. This pattern must be 0101 01 **aa**, whereby **aa** are the 2 higher address bits.

e.g.: wanted I/O address: 3A4h / 3A5h

| IIOSEL(3:0): 0001<br>then hardware selected I/O address is:                                           | <b>2E0h</b> =                            | 10 1110 0000 b           |

|-------------------------------------------------------------------------------------------------------|------------------------------------------|--------------------------|

| write the value <b>A4h</b> or <b>A5h</b> into <b>2E0h</b> write the value <b>57h</b> into <b>2E1h</b> | = 1010 010<br>= 0101 01<br>1<br>0101 011 | b pattern<br>1 b address |

| x = don't core                                                                                        |                                          |                          |

x = don't care

All further accesses to the HFC-U can only be done on the addresses **3A4h** / **3A5h**. Only a master reset on the RESET pin will switch back the HFC-U into hardware selected address mode.

d hint:

It's useful to solve a possible address conflict by programming the I/O address as early as possible. It is recommendable to set the address with a simple .SYS driver in a DOS environment.

#### **3.1.2 ISA-PC bus interface**

The HFC-U only uses 2 I/O addresses with SA0 switches between data or control information in ISA-PC mode. As normal only 10 bits of the ISA-PC bus address are used for I/O address selection.

| SA0 | /IOR | /IOW | /AEN | Operation     |

|-----|------|------|------|---------------|

| Х   | Х    | X    | 1    | no access     |

| Х   | 1    | 1    | X    | no access     |

| 0   | 0    | 1    | 0    | read data     |

| 0   | 1    | 0    | 0    | write data    |

| 1   | 0    | 1    | 0    | read status   |

| 1   | 1    | 0    | 0    | write control |

X = don't care

#### *d* important!

ALE must be connected to GND and at least one of the IIOSEL0-3 must be '1' or open!

The HFC-U has no memory or DMA access to any component on the ISA-PC bus.

Because of its power drive characteristic it needs no external driver for the ISA-PC bus data lines.

If necessary you can add an external bus driver. In this case the output BUSDIR determines the driver direction.

BUSDIR = 1 means that data is driven into the HFC-U;

BUSDIR = 0 means that the HFC-U is read and data is driven to the external bus.

#### 3.2 Processor mode

In the microprocessor mode the HFC-U uses 256 I/O addresses (SA0 - SA7).

| /IOR<br>/DS | /IOW<br>R/W | /CS | ALE | Operation  | Mode |

|-------------|-------------|-----|-----|------------|------|

| X           | X           | 1   | X   | no access  | all  |

| 1           | 1           | X   | X   | no access  | all  |

| 0           | 1           | 0   | 1   | read data  | 2    |

| 0           | 0           | 0   | 1   | write data | 2    |

| 0           | 1           | 0   | 0   | read data  | 3    |

| 1           | 0           | 0   | 0   | write data | 3    |

| 0           | 1           | 0   | 0*) | read data  | 4    |

| 1           | 0           | 0   | 0*) | write data | 4    |

X = don't care

<sup>\*)</sup> 1-pulse latches I/O address.

All registers are directly accessable by their I/O address (see register description).

Except in mode 4 ALE is assumed to be stable after a RESET.

#### 3.3 Register description

In ISA-PC mode all registers are selected by first writing the address into the Control Internal Pointer (CIP) register. This is done by writing the HFC-U on the higher address SA0 = 1. All consecutive read or write data accesses (SA0 = 0) are done with the selected register until the CIP register is changed.

In processor mode all registers can be directly accessed. The registers are selected by SA0 - SA7.

#### **3.3.1 FIFO control registers**

The FIFO control registers are used to select and control the FIFOs of the HFC-U. In processor mode the value is the address which directly selects the corresponding register.

|                                                     | / I/O-addresszzzzdz: 5 bits for D-channel FIFO register control |             |                       |            |                               |            |  |

|-----------------------------------------------------|-----------------------------------------------------------------|-------------|-----------------------|------------|-------------------------------|------------|--|

| yyyff y: 4 bits for B-channel FIFO register control |                                                                 |             |                       |            |                               |            |  |

|                                                     |                                                                 | -           |                       |            |                               |            |  |

| уууу                                                |                                                                 | ZZZZZ       |                       |            |                               |            |  |

| 0000                                                |                                                                 | 01000       | FIFO input co         |            | •                             | r)         |  |

| 0001                                                |                                                                 | 01010       | FIFO input co         |            |                               | r)         |  |

| 0010                                                |                                                                 | 01100       | FIFO output o         |            | -                             | r)         |  |

| 0011                                                |                                                                 | 01110       | FIFO output o         | counter (Z | 2) high byte                  | r)         |  |

| HDLC                                                | C mo                                                            | de:         |                       |            |                               |            |  |

| 1010                                                |                                                                 | 01001       | dummy for in          | crement o  | of frame counter (F1)         | r)         |  |

| 1011                                                |                                                                 | 01011       |                       |            | d increment Z1                | <b>w</b> ) |  |

| 1100                                                |                                                                 | 01101       | FIFO input H          | DLC fram   | ne counter (F1)               | r)         |  |

| 1101                                                |                                                                 | 01111       | FIFO output I         | HDLC fra   | me counter (F2)               | r)         |  |

| 1110                                                |                                                                 | 10001       | dummy for in          | crement o  | of frame counter (F2)         | r)         |  |

| 1111                                                |                                                                 | 10011       | data read out         | of FIFO a  | nd increment Z2               | r)         |  |

| Trans                                               | pare                                                            | ent mode (  | only selectable f     | or B-chai  | nnels):                       |            |  |

| 1010                                                | •                                                               | ```         | •                     |            | side down and increment Z1    | w)         |  |

| 1011                                                |                                                                 |             |                       | ·          | d increment Z1                | <b>w</b> ) |  |

| 1100                                                |                                                                 |             | FIFO input H          | DLC fram   | ne counter (F1)               | r)         |  |

| 1101                                                |                                                                 |             | ·                     |            | me counter (F2)               | r)         |  |

| 1110                                                |                                                                 |             |                       |            | pside down and incremement Z2 | r)         |  |

| 1111                                                |                                                                 |             |                       |            | nd increment Z2               | r)         |  |

|                                                     | f• B                                                            | -channel F  | IFO-No ·              |            |                               |            |  |

|                                                     | 00                                                              |             | B1 transmit           | 10         | channel B2 transmit           |            |  |

|                                                     | 01                                                              |             | 31 receive            | 11         | channel B2 receive            |            |  |

|                                                     | ٩٠٢                                                             | 0-channel F | SIFO-No ·             |            |                               |            |  |

|                                                     | 0                                                               |             | el transmit direction | on         |                               |            |  |

|                                                     | 1                                                               |             | el receive directio   |            |                               |            |  |

w) corresponding data register is write only

### d important!

FIFO change

Changing the FIFO must be the last FIFO operation in a non BUSY phase. The new FIFO is selected after one busy phase.

To select a new FIFO in processor mode a dummy value must be written to the Z1 register address of this FIFO. The Z1 register is not changed by this operation.

#### Incrementation of the frame counters (F1, F2)

If the frame counters (F1, F2) are changed it must be in a seperate non BUSY period. That means writing data to the FIFO or reading data from the FIFO is not allowed during this period. Also selecting a new FIFO is not allowed. Reading the counters Z1, Z2, F1 and F2 is allowed before incrementing the frame counter.

#### Accessability of registers

All operations on the FIFOs and on FIFO control registers and on B- and D-channel data registers of the GCI/IOM bus part are only allowed in the non BUSY period of the HFC-U.

Status, interrupt and control registers can be read/written at any time.

#### 3.3.2 Registers of the GCI/IOM bus section

#### GCI/IOM bus timeslot selection registers

| CIP / I/O-address | Name  | r/w | Function                          |

|-------------------|-------|-----|-----------------------------------|

| 00100000 20h      | B1_SL | w   | B1-slot mode register             |

| 00100001 21h      | B2_SL | w   | B2-slot mode register             |

| 00100010 22h      | C/I   | r/w | C/I command/indication register   |

| 00100011 23h      | TRxR  | r   | Monitor Tx and Rx ready handshake |

#### **GCI/IOM** bus data registers

| CIP / I/O-address                            | Name                                  | r/w             | Function                                                                           |  |

|----------------------------------------------|---------------------------------------|-----------------|------------------------------------------------------------------------------------|--|

| 00101000 28h<br>00101001 29h                 | B1_D*)<br>B2_D*)                      | r/w<br>r/w      | B1 channel data register (slot #0 data)<br>B2 channel data register (slot #1 data) |  |

| 00101010 2Ah<br>00101011 2Bh<br>00101100 2Ch | MON1_D<br>MON2_D<br>D_D <sup>*)</sup> | r/w<br>r/w<br>w | first monitor byte (slot #2 data)<br>second monitor byte (slot #2 data)            |  |

| 00101110 2Eh                                 | MST_MODE                              | w               | mode register for GCI/IOM bus                                                      |  |

\*) These registers are read/written automatically by the HDLC FIFO controller (HFC).

#### 3.3.3 Interrupt and status register

| CIP / I/O address | Name r      | r/w  | Function                                                                           |

|-------------------|-------------|------|------------------------------------------------------------------------------------|

| 00011000 18h      | CIRM v      | W    | interrupt selection and softreset register                                         |

| 00011001 19h      | CTMT v      | W    | transparent mode and time control register                                         |

| 00011010 1Ah      | INT_M1 v    | W    | interrupt mask register 1                                                          |

| 00011011 1Bh      | INT_M2 v    | W    | interrupt mask register 2 and B-channel mode register (64 kbit/s or 56 kbit/s)     |

| 00011110 1Eh      | INT_S1 r    | r    | interrupt status register                                                          |

| 00011100 1Ch      | STATUS r    | r    | common status register                                                             |

| 00011101 1Dh      | STATUS_DISB | BUSY | same as STATUS register but also locks busy-<br>nobusy transition (see also 3.7.1) |

#### 3.4 Watchdog / timer

The watchdog function of the HFC-U has two different modes which can be selected by bit 5 of the CTMT register.

In the first mode the watchdog timer expires after the selected time if the timer has been reset and the INT\_S1 register is not read during the watchdog timer period.

In the second mode the watchdog timer expires after the selected time if no HFC-U register is accessed during the watchdog timer period. In this mode every access to the HFC-U resets the watchdog **and** the timer.

#### 3.5 FIFOs

There are 6 FIFOs with 6 HDLC-Controllers in the HFC-U. The HDLC circuits are located on the GCI/IOM side of the HFC-U. So always plain data is stored in the FIFO. Zero insertion and deletion is done:

- if the data goes to GCI/IOM interface in send FIFOs and

- when the HDLC data comes from GCI/IOM interface in receive operation.

There are a send and a receive FIFO for each of the two B-channels and for the D-channel.

The FIFOs are realized as ring buffers in the external SRAM. To control them there are some counters.

|                         | B-channel | D-channel |

|-------------------------|-----------|-----------|

| Z1: FIFO input counter  | 13 Bit    | 9 Bit     |

| Z2: FIFO output counter | 13 Bit    | 9 Bit     |

Each counter points to a byte position in the SRAM. On a FIFO input operation Z1 is incremented. On an output operation Z2 is incremented.

After every pulse on the F0IO signal the HFC-U goes into busy cycle and two HDLC-bytes are written into the GCI/IOM interface (FIFOs No. 0 and 2) and two HDLC-bytes are read from the GCI/IOM interface (FIFOs No. 1 and 3). D-channel data is handled in a similar way.

If Z1 = Z2 the FIFO is empty.

Additionally there are two counters F1 and F2 for every FIFO channel (5Bit for B-channel, 4Bit for D-channel). They count the HDLC-frames in the FIFOs and form a ring buffer as Z1 and Z2 do, too.

Again F1 is incremented when a complete frame has been received and stored in the FIFO. F2 is incremented when a complete frame has been read from the FIFO.

If F1 = F2 there is no complete frame in the FIFO.

When the RESET line is active or software reset is active Z1, Z2, F1 and F2 are all initialized to all 1s.

#### *d* important!

The counter state 0200h of the Z-counters follows counter state 1FFFh in the B-channel FIFOs. The counter state 000h of the Z-counters follows counter state 1FFh in the D-channel FIFOs.

The counter state 00h of the F-counters follows counter state 1Fh in the B-channel FIFOs. The counter state 10h of the F-counters follows counter state 1Fh in the D-channel FIFOs.

#### 3.5.1 FIFO channel operation

Figure 3: FIFO Organisation (shown for B-channel, similar for D-channel)

#### 3.5.1.1 Send channels (B1, B2 and D transmit)

The send channels send data from the ISA-PC/processor bus interface to the FIFO and the HFC-U converts the data into HDLC code and tranfers it from the FIFO into the GCI/IOM interface write registers.

The HFC-U checks Z1 and Z2. If Z1=Z2 (FIFO empty) the HFC-U generates a HDLC-Flag (0111 1110) and sends it to the GCI/IOM interface. In this case Z2 is not incremented. If also F1=F2 only HDLC flags are sent to the GCI/IOM interface and all counters remain unchanged. If the frame counters are unequal F2 is incremented and the HFC-U tries to send the next frame to the output device. After the end of a frame (Z2 reaches Z1) it automatically generates the 16 bit CRC checksum and adds the ending flag. If there is another frame in the FIFO (F1  $\neq$ F2) the F2 counter is incremented.

With every byte you send to the FIFO via the ISA-PC bus interface Z1 is incremented automatically. If a complete frame has been send F1 must be incremented to send the next frame. If the frame counter F1 is incremented also the Z-counters may change because Z1 and Z2 are functions of F1 and F2. So there are Z1(F1), Z2(F1), Z1(F2) and Z2(F2) (see Figure 3).

Z1(F1) is used for the frame which is just written from the PC-bus side. Z2(F2) is used for the frame which is just beeing transmitted to the GCI/IOM side of the HFC-U. Z1(F2) is the end of frame pointer of the current output frame.

In the send channels F1 is only changed from the PC interface side if the software driver wants to say "end of send frame". Then the current value of Z1 is stored, F1 is incremented and Z1 is used as start address of the next frame. Z1(F2) and Z2(F2) can not be accessed.

#### *d* important!

At the start of the first frame when the FIFO is totally empty at least two bytes must be put into the FIFO before a BUSY condition is initialized by the HFC-U. This is necessary to avoid the initialisation of a CRC sequence after a one-byte frame. To satisfy this condition you should wait for a BUSY / NOBUSY status transition. In this case there is enough time to write more than one byte into the FIFO.

#### **3.5.1.2 FIFO full condition in send channels**

Due to the limited number of registers in the HFC-U the driver software must maintain a list of frame start and end addresses to calculate actual FIFO depth and check FIFO full condition. Because there are a maximum of 32 frame counter values and the start address of a frame is the incremented value of the last frame end address the memory table must have only 32 values of 16 bits (13 bits) instead of 64.

Remember that an increment of Z-value 1FFFh is 0200h in the B-channels!

There are two different FIFO full conditions. The first one is met when the FIFO contents comes up to 31 frames (B-channel) or 15 frames (D-channel). There is no possibility for the HFC-U to manage more frames even if the frames are very small.

The second limitation is the depth of the FIFO which is 512 byte for the D-channel and 7.5 KByte for the B-channel (32KByte external RAM).

#### **3.5.1.3** Receive Channels (B1, B2 and D reiceive)

The receive channels receive data from the GCI/IOM bus interface read registers. The data is converted from HDLC into plain data and send to the FIFO. The data can then be read via the processor interface.

The HFC-U checks the HDLC data coming in. If it finds a flag or more than 5 consecutive 1s it does not generate any output data. In this case Z1 is not incremented. Proper HDLC data being received is converted by the HFC-U into plain data. After the ending flag of a frame the HFC-U checks the HDLC CRC checksum. If it is correct one byte with all 0s is inserted behind the CRC data in the FIFO named STAT. This last byte of a frame in the FIFO is different from all 0s if there is no correct CRC field at the end of the frame.

Figure 4: FIFO Data Organisation

The ending flag of a HDLC-frame can also be the starting flag of the next frame.

After a frame is received completely F1 is incremented by the HFC-U automatically and the next frame can be received.

After reading a frame via the processor bus interface F2 must be incremented. If the frame counter F2 is incremented also the Z-counters may change because Z1 and Z2 are functions of F1 and F2. So there are Z1(F1), Z2(F1), Z1(F2) and Z2(F2) (see Figure 3).

Z1(F1) is used for the frame which is just received from the GCI/IOM side of the HFC. Z2(F2) is used for the frame which is just beeing transmitted to the ISA-PC bus interface. Z1(F2) is the end of frame pointer of the current output frame.

To calculate the length of the current receive frame the software has to evaluate Z1-Z2. When Z2 reaches Z1 the complete frame has been read.

In the receive channels F2 must be incremented from the PC interface side after the software detects an end of receive frame (Z1=Z2) and F1  $\neq$ F2. Then the current value of Z2 is stored, F2 is incremented and Z2 is copied as start address of the next frame. If Z1 = Z2 and F1 = F2 the FIFO is totally empty. Z1(F1) can not be accessed.

#### **3.5.1.4 FIFO full condition in receive channels**

Because the ISDN-B-channels and the ISDN-D-channels have no hardware based flow control there is no possibility to stop input data if a receive FIFO is full.

So there is no FIFO full condition implemented in the HFC-U. The HFC-U assumes that the FIFOs are so deep that the host processor hardware is able to avoid any overflow of the receive FIFOs. Overflow conditions are again more than 31 input frames (15 frames for D-channel) or a real overflow of the FIFO because of excessive data.

Because HDLC procedures only know a window size of 7 frames no more than 7 frames are send without software intervention. Due to the great depth of the FIFOs of the HFC-U it is easy to poll the HFC-U even in large time intervalls without having to fear a FIFO overflow condition.

However to avoid any undetected FIFO overflows the software driver should check the number of frames in the FIFO which is F1-F2. An overflow exists if the number (F1-F2) is less than the number in the last reading even if there was no reading of a frame in between.

After a detected FIFO overflow condition the HFC-U must be reset via the software or hardware RESET!

#### **3.5.1.5 FIFO initialisation**

All counters Z1, Z2, F1 and F2 of all FIFOs are initialized to all 1s after a RESET.

Then the result is Z1 = Z2 = 1FFFh and F1 = F2 = 1Fh for the B-channels and Z1 = Z2 = 1FFh and F1 = F2 = 1Fh for the D-channel.

Please mask bit 4 of D-channel from counter F1, F2.

The same initialisation is done if the bit 3 in the CIRM register is set (soft reset).

#### **3.5.2** Transparent mode of HFC-U

You can switch off HDLC operation for each B-channel independently. There is one bit for each B-channel in the CTMT control register. If this bit is set data in the FIFO is send directly to the GCI/IOM bus interface and data from the GCI/IOM bus interface is send directly to the FIFO.

Be sure to switch into transparent mode only if F1=F2. Being in transparent mode the Fx counters remain unchanged. Z1 and Z2 are the input and output pointers respectively. Because F1=F2 both Z-counters are always accessable and have valid data.

If a send FIFO channel changes to FIFO empty condition no CRC is generated and the last data byte written into the FIFO is repeated until there is new data.

In receive channels there is no check on flags or correct CRCs and no status byte is added.

The byte bounderies are not arbitrary like in HDLC mode where byte synchronisation is achieved with HDLC-flags. The data is just the same as it comes from the GCI/IOM bus interface or is send to this.

Because Fx incrementation dummy registers are not used you can send and receive transparent data in two shapes. The normal and first shape is transporting B-channel data with the LSB first as it is usual in HDLC mode. The second shape is sending the bytes upside down as it is normal for PWM data. So the first bit is the MSB.

#### 3.6 External SRAM

For the FIFO data an 32K x 8 external SRAM is used. A 8K x 8 external RAM is also possible but not recommended.

The required access time is 80 ns or below at 12MHz clock.

1024 Byte of the external SRAM are reserved for internal HFC-U use.

| external SRAM | B-channel FIFO depth per<br>channel and direction | D-channel FIFO depth per<br>direction |

|---------------|---------------------------------------------------|---------------------------------------|

| 8K x 8        | 1536 Byte                                         | 512 Byte                              |

| 32K x 8       | 7680 Byte                                         | 512 Byte                              |

Table 2: SRAM size and FIFO depth

To initialise the HFC-U for 8K x 8 SRAM use:

- write 18h to the CIRM register

- write 10h to the CIRM register

#### For all further accesses to the CIRM register bit 4 must be set.

#### left state in the second state of the second s

If you connect the HFC-U with the SRAM you can simplify PCB layout if you permutate address lines and data lines. If you connect data lines of the SRAM with data lines of the HFC-U and SR-address lines of the HFC-U with address lines of the SRAM you can do this in any order.

#### **3.7** Busy synchronisation

For internal processing of the data channels and HDLC the HFC-U enters a busy phase every  $125\mu s$  on a falling F0IO edge. During this BUSY phase most of the registers must not be accessed (all FIFO registers, B1\_D, B2\_D and D\_D).

The minimum BUSY phase time is 280 clock cycles and the maximum BUSY phase time is 630 clock cycles.

#### **3.7.1** Busy synchronisation with status read

Figure 5: Timing relations and delayed BUSY

The lines BUSY and DIS\_BUSY are internal signals of the HFC-U. If BUSY is high the HFC-U is in a phase when busy critical registers must not be accessed. The signal DIS\_BUSY disables the start of the internal BUSY phase until the next read/write data operation is finished. To avoid loss of data the DIS\_BUSY signal must not disable the BUSY so that the end of BUSY comes after the next F0IO signal (see also: STATUS register bit description).

READ\_STATUS symbolizes a status read operation. The high signal means the status is read. BUSY BIT AT STATUS READ is the value returned from a read status operation (bit 0 in STATUS register). READ/WRITE DATA ACCESS symbolizes a data read/write operation.

#### 3.7.2 Busy synchronisation with IOCHRDY

Figure 6: Function of IOCHRDY

Note 1: The read/write data access is finished by an external processor after release of IOCHRDY.

Repeated status read can be avoided if the IOCHRDY output of the HFC-U is connected to the /WAIT line of the external processor. If the HFC-U is accessed during a BUSY phase the processor waits until the end of the BUSY phase.

### 4 Register bit description

#### 4.1 Register bit description of GCI/IOM bus section

#### **Timeslots for transmit direction**

| Name             | Addr.          | Bits     | r/w        | Function                                                                                                         |

|------------------|----------------|----------|------------|------------------------------------------------------------------------------------------------------------------|

| B1_SL            | (20h)          | 50       | W          | unused                                                                                                           |

|                  |                | б        | W          | select ST bus data lines<br>'0' GCI_IN is input<br>GCI_OUT is output<br>'1' GCI_OUT is input<br>GCI_IN is output |

|                  |                | 7        | W          | transmit channel enable for ST bus<br>'0' disable (default)<br>'1' enable                                        |

| B2_SL            | (21h)          |          |            | see B1_SL                                                                                                        |

| C/I              | (22h)          | 30       | r/w        | on read: indication<br>on write: command                                                                         |

|                  |                | 74       |            | unused                                                                                                           |

| TRxR             | (23h)          | 0        | r          | '1' Monitor receiver ready (2 bytes received)<br>bit is reset after read of second Monitor byte<br>(MON2_D)      |

|                  |                | 1        |            | '1' Monitor transmitter ready<br>write on MON2_D starts transmit and resets this bit                             |

|                  |                | 6        |            | data on input pin INO                                                                                            |

|                  |                | 7        |            | data on input pin IN1                                                                                            |

| B1_D             | (28h)          | 07       | r/w        | read/write register for B1 timeslot data                                                                         |

| B2_D             | (29h)          | 07       | r/w        | read/write register for B2 timeslot data                                                                         |

| MON1_D<br>MON2_D | (2Ah)<br>(2Bh) | 07<br>07 | r/w<br>r/w | 1st monitor data byte<br>2nd monitor data byte                                                                   |

March 1997

| Name    |          | Bits | r/w | Function                                                                                                                                                                                        |

|---------|----------|------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D_D     | (2Ch)    | 6,7  | W   | write data for D timeslot data<br>only bit 6 and 7 valid                                                                                                                                        |

| MST_MOI | DE (2Eh) | 0    | W   | GCI mode<br>'0' slave (default)<br>C4O and F0O are inputs<br>'1' master<br>C4O and F0O are outputs                                                                                              |

|         |          | 1    | W   | <ul> <li>polarity of C4O clock</li> <li>'0' bit cell starts with falling clock (default)</li> <li>'1' bit cell starts with rising clock</li> </ul>                                              |

|         |          | 2    | W   | <ul> <li>polarity of F0 frame sync.</li> <li>'0' positive pulse on F0 (default)</li> <li>'1' negative pulse on F0</li> </ul>                                                                    |

|         |          | 3    | W   | duration of F0 signal'0'F0 active for one C4 clock (244ns) (default)'1'F0 active for two C4 clocks (488ns)                                                                                      |

|         |          | 5, 4 | W   | select time slot for codec-A signal F1_A<br>'00' slot 0 (B1)<br>'01' slot 1 (B2)<br>'10' signal C2O (2.048MHz) to F1_A<br>'11' disable, no pulse                                                |

|         |          | 7, 6 | w   | <ul> <li>select time slot for codec-B signal F1_B</li> <li>'00' slot 0 (B1)</li> <li>'01' slot 1 (B2)</li> <li>'10' slot 4 (ability to cascade HFC-U)</li> <li>'11' disable, no pule</li> </ul> |

The pulseshape of the codec signals is the same as the pulseshape of the F0 signals. The polatity of C2O can be changed by bit 1.

RESET sets register MST\_MODE to '0's.

#### 4.2 Register bit description of interrupt, status and control registers

| Name |       | Bits | r/w | Function                                                                                                                                                                                                                                                     |

|------|-------|------|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CIRM | (18h) | 20   | W   | select IRQ channel in PC mode<br>'000' IRQ disable (reset default)<br>'001' IRQ_A<br>'010' IRQ_B<br>'011' IRQ_C<br>'100' IRQ_D<br>'101' IRQ_E<br>'110' IRQ_F<br>'111' IRQ disable                                                                            |

|      |       | 3    | w   | soft reset, similar as hardware reset; the registers CIP,<br>CIRM and CTMT are not changed so selected I/O address<br>is kept in ISA-PC mode. The reset is active until the bit is<br>cleared.<br>'1' activate reset<br>'0' deactivate reset (reset default) |

|      |       | 4    | W   | select memory<br>'0' 32k x 8 external RAM (reset default)<br>'1' 8k x 8 external RAM                                                                                                                                                                         |

|      |       | 5    | W   | <ul> <li>D-channel idle mode</li> <li>'0' flags are send in D-channel if no data is send<br/>(reset default)</li> <li>'1' continous ones are send in D-channel if no data is<br/>send</li> </ul>                                                             |

|      |       | 6    | W   | clock divider<br>'0' normal clock mode (reset default)<br>'1' master clock is divided by 2<br>This bit should only be changed during soft reset.                                                                                                             |

|      |       | 7    | W   | <ul> <li>GCI/IOM test loop</li> <li>'0' normal operation</li> <li>'1' GCI input data is received from GCI output data GCI output data is not changed</li> </ul>                                                                                              |

| СТМТ | (19h) | 0    | W   | <ul> <li>HDLC/transparent mode for channel B1</li> <li>'0' HDLC mode (reset default)</li> <li>'1' transparent mode</li> </ul>                                                                                                                                |

|      |       | 1    | W   | <ul> <li>HDLC/transparent mode for channel B2</li> <li>'0' HDLC mode (reset default)</li> <li>'1' transparent mode</li> </ul>                                                                                                                                |

March 1997

| Name   |       | Bits | r/w | Function                                                                                                                                                                  |

|--------|-------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| СТМТ   | (19h) | 2    | W   | data output to pin OUT0<br>'0' (reset default)                                                                                                                            |

|        |       | 4, 3 | W   | select timer and watchdog<br>timer watchdog<br>'00' 25ms 50ms (reset default)<br>'01' 50ms 100ms<br>'10' 400ms 800ms<br>'11' 800ms 1600ms                                 |

|        |       | 5    | W   | <ul> <li>timer/watchdog reset mode</li> <li>'0' reset timer/WD by CTMT bit 7 (reset default)</li> <li>'1' automatically reset timer/WD at each access to HFC-U</li> </ul> |

|        |       | 6    | W   | data output to pin OUT1<br>'0' (reset default)                                                                                                                            |

|        |       | 7    | W   | reset timer/WD<br>'1' reset timer/WD<br>The bit is automatically cleared.                                                                                                 |

| INT_M1 | (1Ah) | 0    | W   | interrupt mask for channel B1 in transmit direction                                                                                                                       |

|        |       | 1    | W   | interrupt mask for channel B2 in transmit direction                                                                                                                       |

|        |       | 2    | W   | interrupt mask for channel D in transmit direction                                                                                                                        |

|        |       | 3    | W   | interrupt mask for channel B1 in receive direction                                                                                                                        |

|        |       | 4    | W   | interrupt mask for channel B2 in receive direction                                                                                                                        |

|        |       | 5    | W   | interrupt mask for channel D in receive direction                                                                                                                         |

|        |       | 6    | W   | interrupt mask for receive ready (RxR) of monitor channel                                                                                                                 |

|        |       | 7    | W   | interrupt mask for timer                                                                                                                                                  |

For mask bits a '1' enables and a '0' disables interrupt. RESET clears all bits to '0'.

| Name   |       | Bits | r/w | Function                                                                                                                                |

|--------|-------|------|-----|-----------------------------------------------------------------------------------------------------------------------------------------|

| INT_M2 | (1Bh) | 0    | W   | interrupt mask for BUSY/NOBUSY transition                                                                                               |

|        |       | 1    | W   | interrupt mask for GCI I-change interrupt                                                                                               |

|        |       | 2    | W   | in 64 kbit/s mode: must be '0'<br>in 56 kbit/s mode: value of the LSB in 7-bit mode                                                     |

|        |       | 3    | W   | enable for interrupt output<br>'0' disable (reset default)<br>'1' enable                                                                |

|        |       | 4    | W   | <ul> <li>56 kbit/s mode selection bit for B1-channel</li> <li>'0' 64 kbit/s mode (reset default)</li> <li>'1' 56 kbit/s mode</li> </ul> |

|        |       | 5    | W   | <ul> <li>56 kbit/s mode selection bit for B2-channel</li> <li>'0' 64 kbit/s mode (reset default)</li> <li>'1' 56 kbit/s mode</li> </ul> |

|        |       | 6    | W   | <ul><li>'0' Data not inverted for B1-channel (reset default)</li><li>'1' Data inverted for B1-channel</li></ul>                         |

|        |       | 7    | W   | <ul><li>'0' Data not inverted for B2-channel (reset default)</li><li>'1' Data inverted for B2-channel</li></ul>                         |

For mask bits a '1' enables and a '0' disables interrupt. RESET clears all bits to '0'.

| Name   |       | Bits   | r/w    | Function                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|--------|-------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| INT_S1 | (1Eh) | 0<br>1 | r<br>r | <ul> <li>B1-channel interrupt status in transmit direction</li> <li>B2-channel interrupt status in transmit direction</li> <li>in HDLC mode:</li> <li>'1' a complete frame was transmitted, the frame counter</li> <li>F2 was incremented</li> <li>in transparent mode, external RAM 32K x 8:</li> <li>'1' bit12 in Z2 counter changed from '0' to '1'</li> <li>in transparent mode, external RAM 8K x 8:</li> <li>'1' bit10 in Z2 counter changed from '0' to '1'</li> </ul> |

|        |       | 2      | r      | <ul> <li>D-channel interrupt status in transmit direction</li> <li>'1' a complete frame was transmitted, the framecounter</li> <li>F2 was incremented</li> </ul>                                                                                                                                                                                                                                                                                                              |

|        |       | 3      | r      | B1-channel interrupt status in receive direction                                                                                                                                                                                                                                                                                                                                                                                                                              |

|        |       | 4      | r      | <ul> <li>B2-channel interrupt status in receive direction<br/>in HDLC mode:</li> <li>'1' a complete frame was transmitted, the frame counter<br/>F1 was incremented</li> <li>in transparent mode, external RAM 32K x 8:</li> <li>'1' bit12 in Z1 counter changed from '0' to '1'</li> <li>in transparent mode, external RAM 8K x 8:</li> <li>'1' bit10 in Z1 counter changed from '0' to '1'</li> </ul>                                                                       |

|        |       | 5      | r      | <ul> <li>D-channel interrupt status in receive direction</li> <li>'1' a complete frame was received, the frame counter</li> <li>F1 was incremented</li> </ul>                                                                                                                                                                                                                                                                                                                 |

|        |       | 6      | r      | receiver ready (RxR) of monitor channel<br>'1' 2 monitor bytes have been received                                                                                                                                                                                                                                                                                                                                                                                             |

|        |       | 7      | r      | timer interrupt status<br>'1' timer is elapsed                                                                                                                                                                                                                                                                                                                                                                                                                                |

#### dimportant!

Reading the INT\_S1 register resets all active read interrupts. New interrupts may occur during read. These interrupts are reported at the next read of INT\_S1.

The interrupt output goes inactive during the read of INT\_S1. If interrupts occur during this read the interrupt line goes active immediately after the read is finished. So processors with level or transition triggered interrupt inputs can be connected.

| Name   |       | Bits | r/w | Function                                                                                                                                                                                                      |

|--------|-------|------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STATUS | (1Ch) | 0    | r   | <ul> <li>BUSY/NOBUSY status</li> <li>'1' the HFC-U is in BUSY state</li> <li>'0' the HFC-U is in NOBUSY state, access on all FIFO functions is now possible</li> </ul>                                        |

|        |       | 1    | r   | unused, '0'                                                                                                                                                                                                   |

|        |       | 2    | r   | <ul> <li>BUSY/NOBUSY transition interrupt status</li> <li>'1' the HFC-U has changed from BUSY to NOBUSY state, access on all FIFO functions is now possible This bit is reset by a read of INT_S1.</li> </ul> |

|        |       | 3    | r   | GCI I-change interrupt<br>'1' a different I-value on GCI was detected                                                                                                                                         |

|        |       | 4    | r   | timer status<br>'0' timer not elapsed<br>'1' timer elapsed                                                                                                                                                    |

|        |       | 5    | r   | receiver ready (RxR) of monitor channel<br>'1' 2 monitor bytes have been received                                                                                                                             |

|        |       | 6    | r   | FRAME interrupt has occured (any data channel interrupt) all masked D-channel and B-channel interrupts are "ored"                                                                                             |

|        |       | 7    | r   | ANY interrupt<br>all masked interrupts are "ored"                                                                                                                                                             |

Reading the STATUS register clears no bit.

| STATUS_DISBUSY | (1Dh) | r     | see STATUS register                          |

|----------------|-------|-------|----------------------------------------------|

|                |       | All t | bits are the same as in the STATUS register. |

#### All processor modes:

Reading STATUS\_DISBUSY register delays the transition from nobusy to busy until any other register of the HFC-U is accessed (see Figure 5 on page 26).

This register should be checked for nobusy before accessing any busy-critical register to avoid a transition from nobusy to busy during a FIFO register access, which may destroy register values. Busy-critical register are all FIFO registers, the B-channel data register B1\_D, B2\_D and D\_D of the GCI/IOM bus part.

#### **ISA-PC mode:**

It is possible to read the STATUS\_DISBUSY register in ISA-PC mode directly by a READ operation to the port address with SA0='1', but it is necessary to enable the HFC-U going into busy cycle again after a data port access with SA0='0'.

March 1997

#### **Electrical characteristics** 5

#### Absolute maximum ratings

| Parameter             | Symbol          | Rating                             |

|-----------------------|-----------------|------------------------------------|

| Supply voltage        | V <sub>CC</sub> | -0.3V to +7.0V                     |

| Input voltage         | VI              | -0.3V to V <sub>CC</sub> + 0.3V    |

| Output voltage        | Vo              | -0.3V to V <sub>CC</sub> + 0.3V    |

| Operating temperature | $T_{opr}$       | $-40^{\circ}$ C to $+85^{\circ}$ C |

| Storage temperature   | $T_{stg}$       | -55°C to +150°C                    |

#### **Recommended operating conditions for TTL and CMOS interface**

| Parameter             | Symbol           | Condition               | MIN. | TYP.  | MAX.  |

|-----------------------|------------------|-------------------------|------|-------|-------|

| Supply voltage        | V <sub>CC</sub>  |                         | 3.0V | 5.0V  | 5.25V |

| Supply current        | I <sub>CC</sub>  | f <sub>CLK</sub> =12MHz |      | 18 mA |       |

| Operating temperature | T <sub>opr</sub> |                         | 0°C  |       | +70°C |

#### **Electrical characteristics**

| Electrical characteristics<br>$V_{CC} = 4.75V \text{ to } 5.25V \text{ (TTL)}, V_{CC} = 4.5V \text{ to } 5.5V \text{ (CMOS)}, T_{opr} = -10^{\circ}\text{C to } +70^{\circ}\text{C}$ |                 |                  |       |      |      |       |      |      |  |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|------------------|-------|------|------|-------|------|------|--|