# HFC - SP A ISDN 2BDS0

# ISDN HDLC FIFO controller with S/T interface, Plug and Play, PCMCIA and U-chip support

January 2001

Copyright 1994-2001 Cologne Chip AG All Rights Reserved

The information presented can not be considered as assured characteristics. Data can change without notice. Parts of the information presented may be protected by patent or other rights. Cologne Chip products are not designed, intended, or authorized for use in any application intended to support or sustain life, or for any other application in which the failure of the Cologne Chip product could create a situation where personal injury or death may occur.

# **Revision History**

| Date      | Remarks                                                                              |

|-----------|--------------------------------------------------------------------------------------|

| Jan. 2001 | Information added to section: GCI/IOM2 timing.                                       |

| Oct. 2000 | Changes made on: PCMCIA card sample circuitry.                                       |

| Aug. 2000 | Changes made on: PCMCIA card sample circuitry.                                       |

| Feb. 2000 | Information added to section: DMA access in processor mode, GCI frame structure.     |

| Nov. 1999 | Information added to section: Power down considerations.                             |

| Aug. 1999 | Section added: Configuring test loops.                                               |

|           | Information added to section: Processor interface modes, processor mode, FIFO        |

|           | channel operation: receive channels, STATES register bit description, ISA-PC bus     |

|           | or processor access timing, S/T interface activation/deactivation layer 1 for finite |

|           | state matrix for NT.                                                                 |

| Mar. 1999 | Changes made on: PCMCIA card sample circuitry part list: R27 added.                  |

| Mar. 1999 | Changes made on: S/T modules part numbers and manufacturers.                         |

| Feb. 1999 | Changes made on: CLKDEL register bit description.                                    |

| Aug. 1998 | Changes made on: DMA access in processor mode, Register bit description of           |

|           | GCI/IOM2 bus section: Auxiliary channel handling, B_MODE register bit                |

|           | description.                                                                         |

| July 1998 | PCMCIA card part list: Values of D4, D5, D7 and D8 changed                           |

Cologne Chip AG Eintrachtstrasse 113 D-50668 Köln Germany

Tel.: +49 (0) 221 / 91 24-0 Fax: +49 (0) 221 / 91 24-100 http://www.CologneChip.com http://www.CologneChip.de info@CologneChip.com

# **Contents**

| 1    | General description                                |    |

|------|----------------------------------------------------|----|

| 1.1  | Applications                                       |    |

| 1.2  | Mode description                                   |    |

| 1.   | 2.1 ISA-PC mode                                    |    |

| 1.   | 2.2 ISA Plug and Play mode                         | 8  |

| 1.   | 2.3 Processor interface modes                      |    |

| 1.   | 2.4 PCMCIA mode                                    |    |

| _    |                                                    |    |

| 2    | Pin description                                    |    |

| 2.1  | ISA-PC bus and microprocessor interface            |    |

| 2.2  | S/T interface transmit signals                     |    |

| 2.3  | S/T interface receive signals                      |    |

| 2.4  | SRAM Interface                                     |    |

| 2.5  | Oscillator                                         |    |

| 2.6  | GCI/IOM2 bus interface                             |    |

| 2.7  | GCI/IOM2 Timeslot enable signals                   |    |

| 2.8  | Interrupt outputs                                  |    |

| 2.9  | Miscellaneous pins                                 |    |

| 2.10 | Power supply                                       |    |

| 2.11 | RESET characteristics                              | 16 |

| 3    | Functional description                             | 15 |

| 3.1  | ISA-PC mode                                        |    |

| 3.2  | ISA Plug and Play mode                             |    |

|      | 2.1 IRQ assignment                                 |    |

|      | 2.2 ISA Plug and Play control registers            |    |

| ٥.   | 3.2.2.1 Card level control registers               |    |

|      | · · · · · · · · · · · · · · · · · · ·              |    |

| 2    | 3.2.2.2 Logical device control registers           |    |

| 3.   | 3.2.3.1 I/O port configuration registers           |    |

|      |                                                    |    |

| 2    | 1 6                                                |    |

|      | 2.4 Writing the Plug and Play configuration EEPROM |    |

| 3.3  |                                                    |    |

| 3.4  | Processor mode                                     |    |

|      | 4.1 DMA access in processor mode                   |    |

| 3.5  | PCMCIA mode                                        |    |

|      | 5.1 Internal HFC-SP register selection             |    |

|      | 5.2 Attribute memory                               |    |

|      | 5.3 PCMCIA registers                               |    |

|      | 5.4 CIS programming                                |    |

| 3.6  | Internal HFC-SP register description               |    |

| 3.   | 5.1 FIFO control registers                         |    |

|      | 3.6.1.1 FIFO select register                       |    |

| _    | 3.6.1.2 FIFO registers                             |    |

|      | Registers of the S/T section                       |    |

|      | Registers of the GCI/IOM2 bus section              |    |

|      | 5.4 Interrupt and status registers                 |    |

| 3.7  | Timer                                              |    |

| 3.8  | Watchdog                                           | 33 |

|      |                                                    |    |

#### HFC-SP

| 3.9   | FIFOs                                                                        | 34       |

|-------|------------------------------------------------------------------------------|----------|

| 3.9.1 | FIFO channel operation                                                       | 35       |

| 3.9   | 9.1.1 Send channels (B1, B2 and D transmit)                                  | 36       |

| 3.9   | 9.1.2 Automatically D-channel frame repetition                               | 36       |

| 3.9   | 9.1.3 FIFO full condition in send channels                                   | 36       |

| 3.9   | 9.1.4 Receive Channels (B1, B2 and D receive)                                | 37       |

| 3.9   | 9.1.5 FIFO full condition in receive channels                                | 38       |

| 3.9   | 9.1.6 FIFO reset                                                             | 39       |

| 3.9.2 | Transparent mode of HFC-SP                                                   | 39       |

| 3.10  | External SRAM                                                                |          |

| 3.11  | Connecting an external device to the HFC-SP                                  | 41       |

| 3.12  | Power down considerations                                                    | 41       |

| 3.13  | Configuring test loops                                                       | 42       |

| 4 Re  | egister bit description                                                      | 43       |

|       | Register bit description of the FIFO select register                         |          |

|       | Register bit description of S/T section                                      |          |

|       | Register bit description of GCI/IOM2 bus section                             |          |

|       | Register bit description of CONNECT register                                 |          |

| 4.5   | Register bit description of interrupt, status and control registers          | 51       |

| 5 El  | ectrical characteristics                                                     | 56       |

|       |                                                                              |          |

|       | ming characteristics                                                         |          |

| 6.2   | SRAM access                                                                  |          |

| 6.3   | GCI/IOM2 bus clock and data alignment for Mitel ST <sup>TM</sup> bus         | 00<br>61 |

|       | GCI/IOM2 timing                                                              |          |

| 6.4.1 | e                                                                            |          |

| 6.4.2 |                                                                              |          |

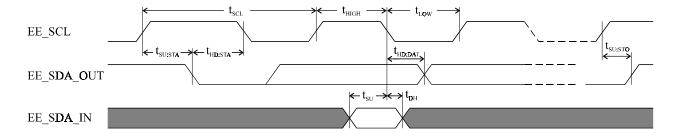

|       | EEPROM access                                                                |          |

| 6.6   | Access to an external device                                                 |          |

|       |                                                                              |          |

|       | T interface circuitry                                                        |          |

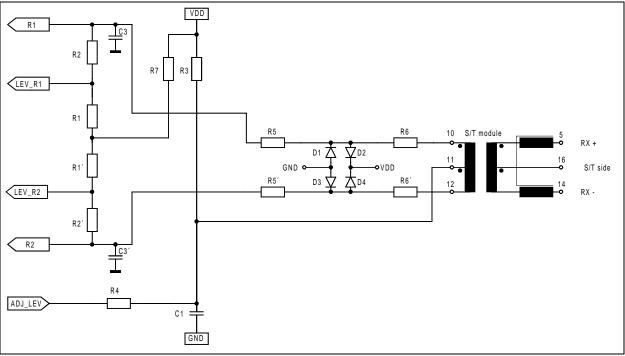

|       | External receiver circuitry                                                  |          |

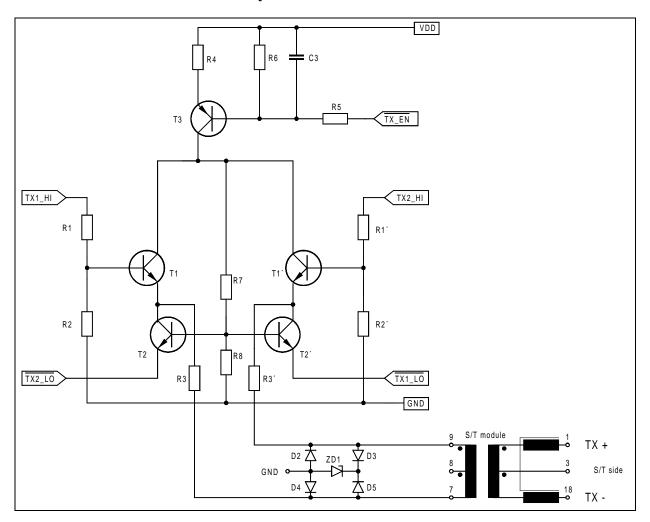

|       | External transmitter circuitry                                               |          |

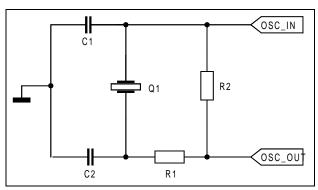

| 7.3   | Oscillator circuitry                                                         |          |

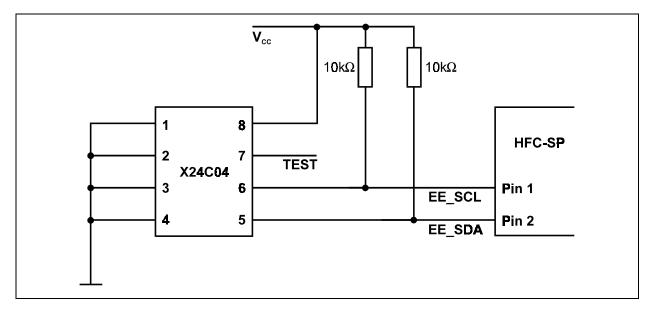

| 7.4   | EEPROM circuitry                                                             | /0       |

|       | ate matrices for NT and TE                                                   |          |

| 8.1   | S/T interface activation/deactivation layer 1 for finite state matrix for NT |          |

| 8.2   | Activation/deactivation layer 1 for finite state matrix for TE               | 72       |

| 9 Bi  | nary organisation of the frames                                              | 73       |

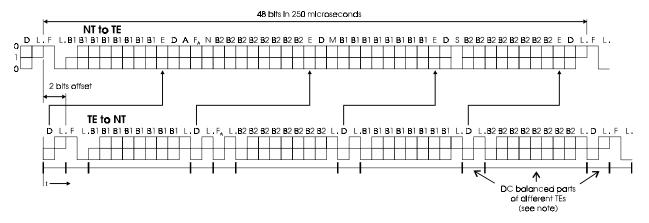

| 9.1   | S/T frame structure                                                          | 73       |

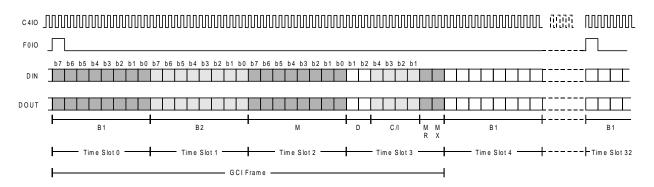

|       | GCI frame structure                                                          |          |

| 10 CI | lock synchronisation                                                         | 75       |

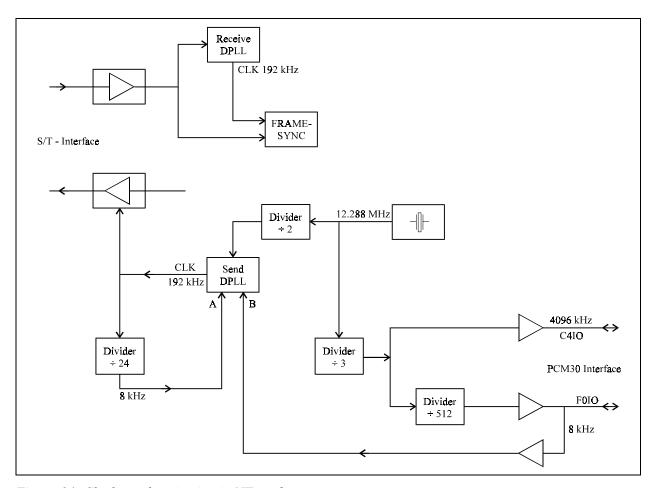

| 10.1  | Clock synchronisation in NT-mode                                             |          |

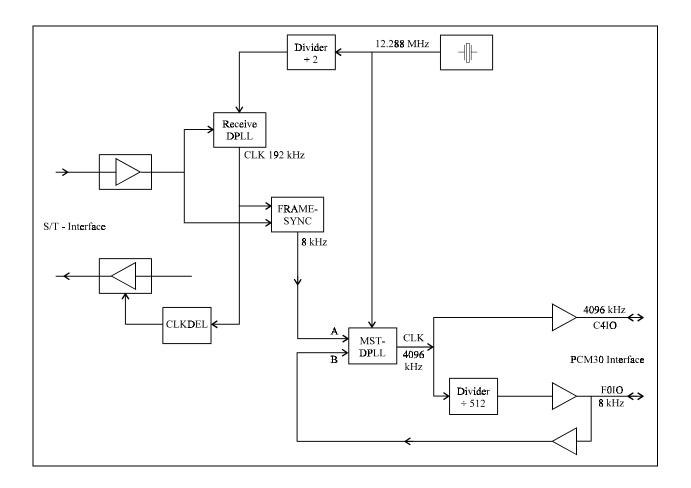

| 10.1  | Clock synchronisation in TE-mode                                             |          |

|       | •                                                                            |          |

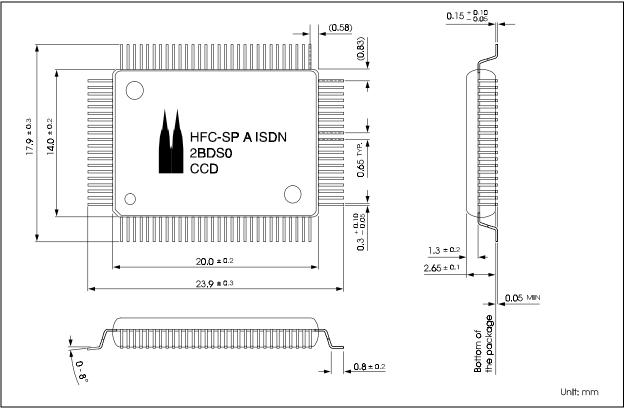

| 11 H  | FC-SP package dimensions                                                     | 77       |

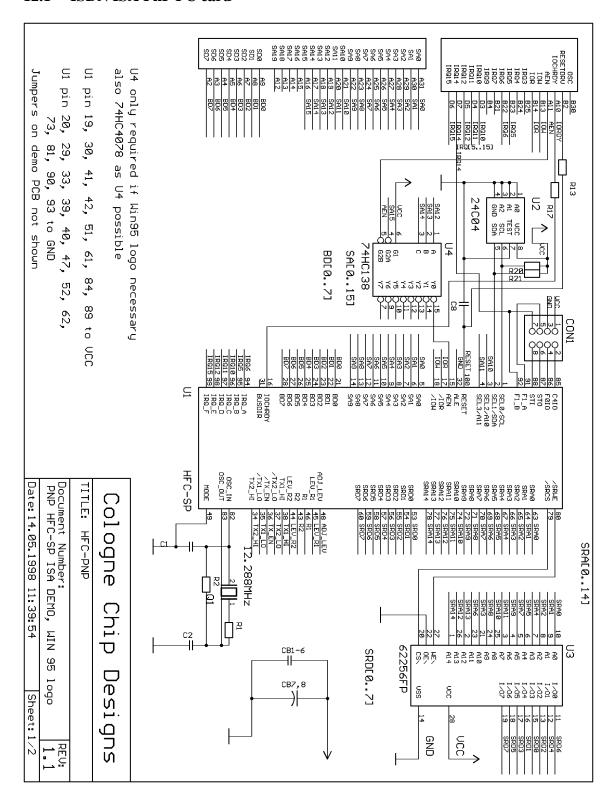

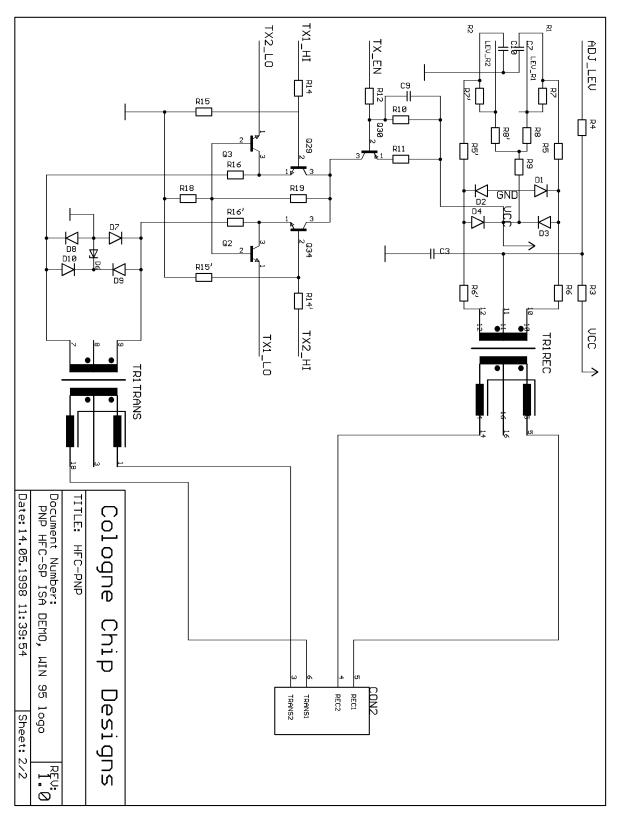

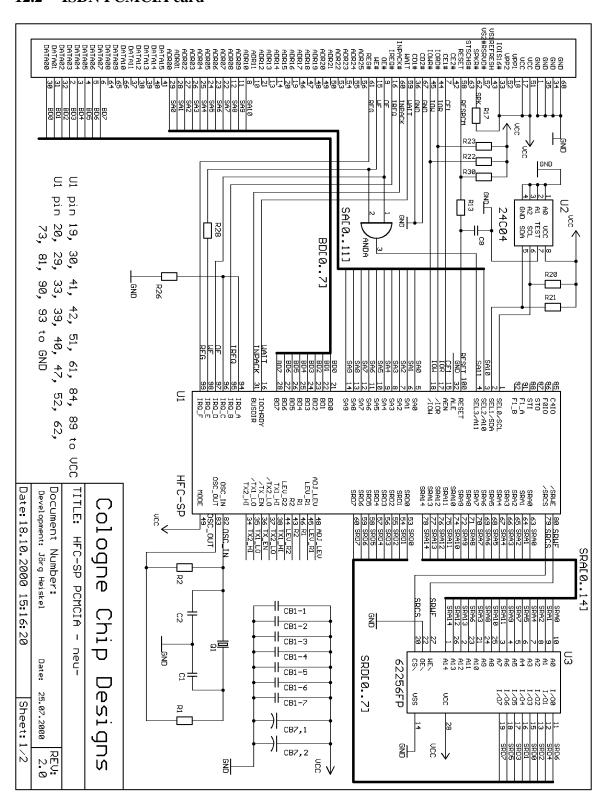

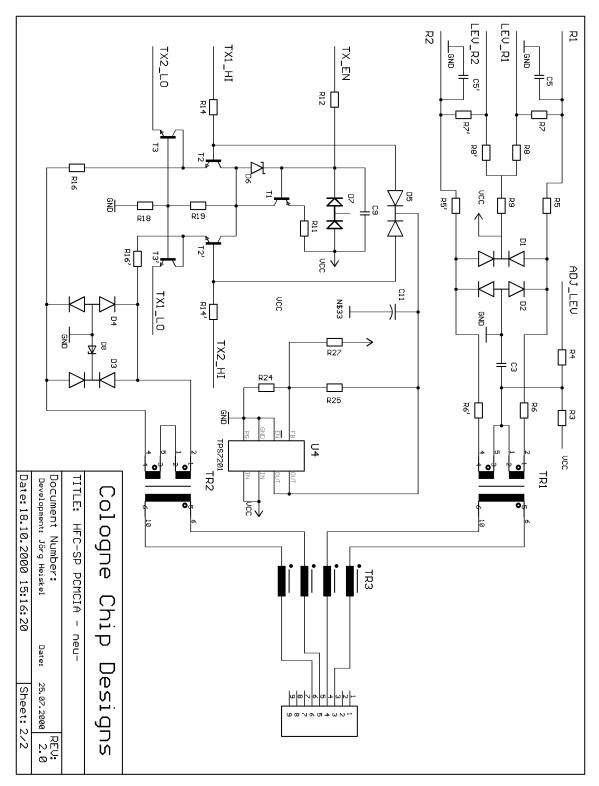

| 12 Sample circuitries with HFC-SP                                        | 78 |

|--------------------------------------------------------------------------|----|

| 12.1 ISDN ISA PnP PC card                                                | 78 |

| 12.2 ISDN PCMCIA card                                                    |    |

| Figures                                                                  |    |

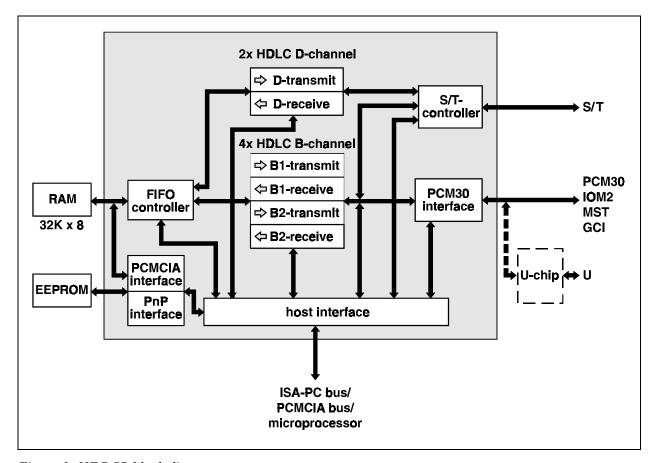

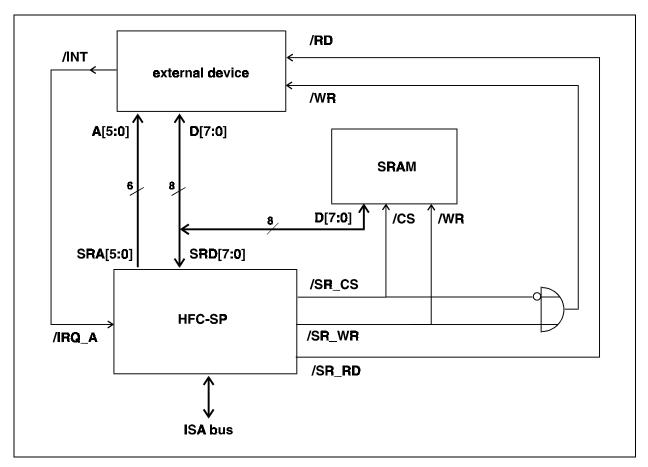

| Figure 1: HFC-SP block diagram                                           | 7  |

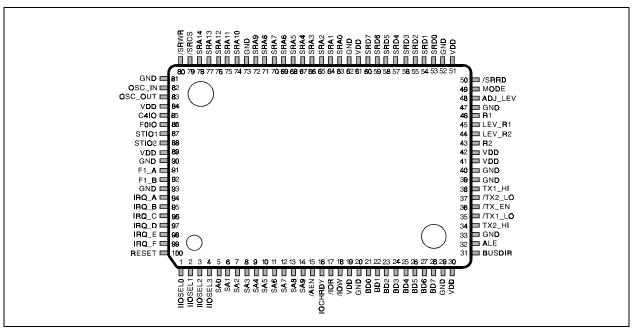

| Figure 2: Pin Connection                                                 |    |

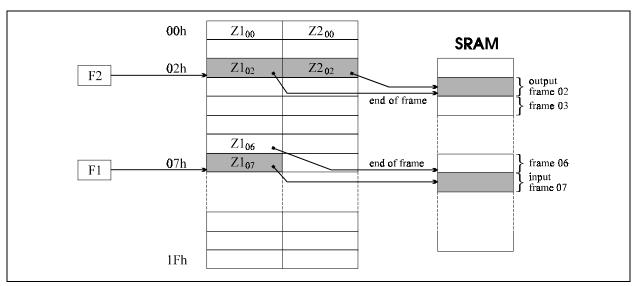

| Figure 3: FIFO Organisation (shown for B-channel, similar for D-channel) |    |

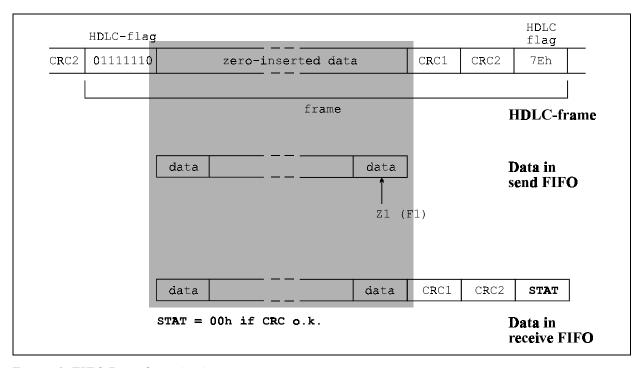

| Figure 4: FIFO Data Organisation                                         |    |

| Figure 5: Connecting an external device to the HFC-SP                    | 41 |

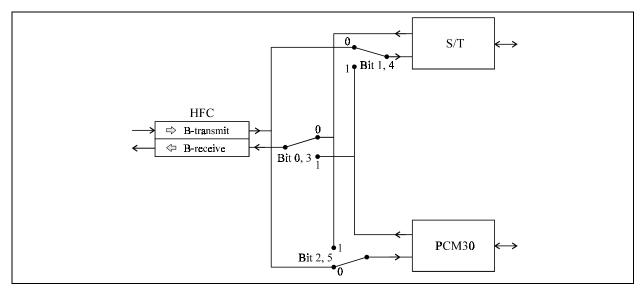

| Figure 6: Function of the CONNECT register bits                          |    |

| Figure 7: GCI/IOM2 bus clock and data alignment                          | 61 |

| Figure 8: External receiver circuitry                                    | 66 |

| Figure 9: External transmitter circuitry                                 | 67 |

| Figure 10: Oscillator Circuitry                                          | 70 |

| Figure 11: EEPROM circuitry                                              | 70 |

| Figure 12: Frame structure at reference point S and T                    | 73 |

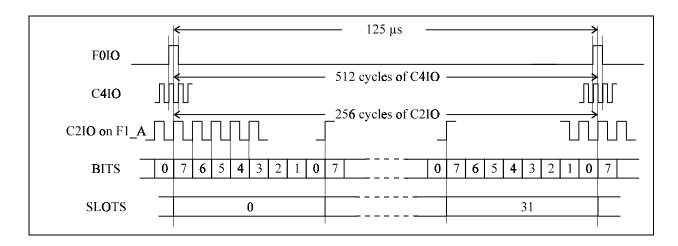

| Figure 13: Single channel GCI format                                     | 74 |

| Figure 14: Clock synchronisation in NT-mode                              | 75 |

| Figure 15: Clock synchronisation in TE-mode                              | 76 |

| Figure 16: HFC-SP package dimensions                                     | 77 |

| Tables                                                                   |    |

| Table 1: Mode selection                                                  | 8  |

| Table 2: Selected I/O address after reset                                | 17 |

| Table 3: DMA access in processor mode                                    | 25 |

| Table 4: SRAM and FIFO size                                              | 40 |

| Table 5: S/T module part numbers and manufacturer                        | 69 |

| Table 6: Activation/deactivation layer 1 for finite state matrix for NT  | 71 |

| Table 7: Activation/deactivation layer 1 for finite state matrix for TE  | 72 |

| Timing Diagrams                                                          |    |

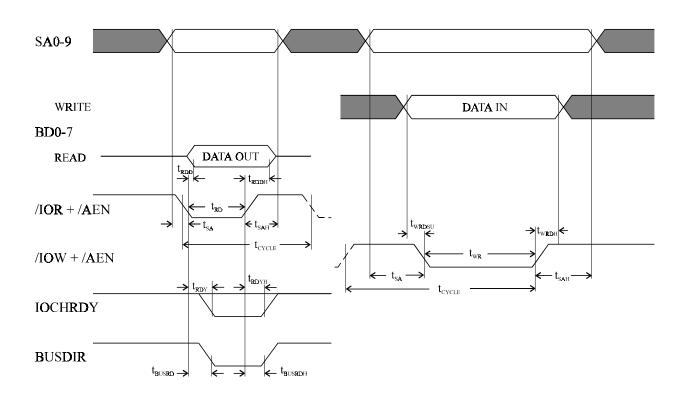

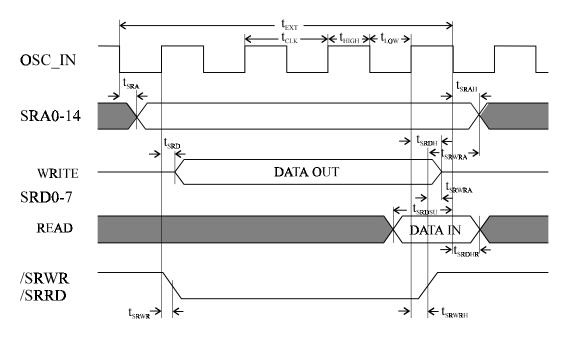

| Timing diagram 1: ISA-PC bus or microprocessor access                    |    |

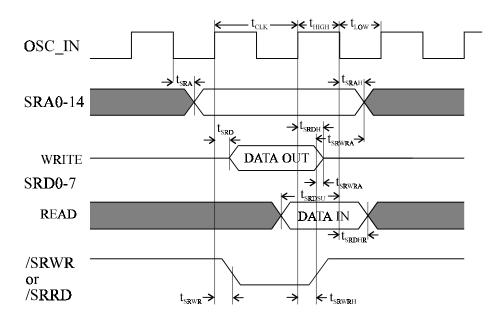

| Timing diagram 2: SRAM access                                            |    |

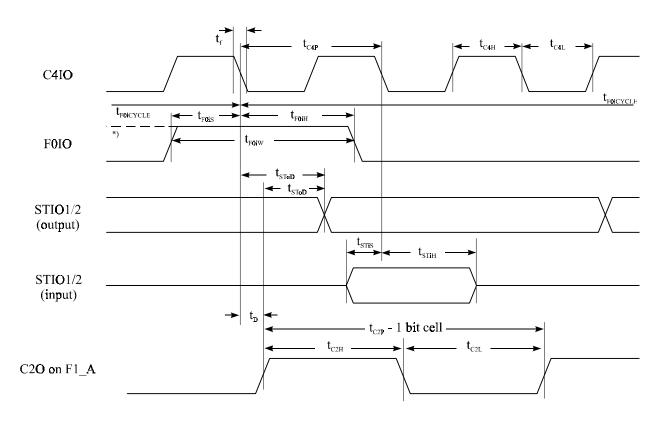

| Timing diagram 3: GCI/IOM2 timing                                        |    |

| Timing diagram 4: EEPROM access                                          |    |

| Timing diagram 5: Access to an external device                           | 65 |

# **Features**

- One chip ISDN-S-controller with B- and D-channel HDLC support

- O Independent Read and Write HDLC-Channels for 2 ISDN B-channels and one ISDN D-channel

- O B1 and B2 transparent mode independently selectable

- O FIFO-size: 4x 7.5 KByte (B-channel) and 2x 512 Byte (D-channel)

- max. 31 HDLC frames (B-channel) and 15 HDLC frames (D-channel) per channel and direction in FIFO

- O 56 kbit/s restricted mode for U.S. ISDN lines selectable

- full I.430 ITU S/T ISDN support in TE and NT mode for 3.3V and 5V supply

- O B1+B2 HDLC mode

- O PCM30 interface configurable to interface MITEL ST<sup>TM</sup> bus (MVIP<sup>TM</sup>), Siemens IOM2<sup>TM</sup> or GCI<sup>TM</sup> for interface to U-chip or external codecs

- O direct 8 bit ISA-PC bus interface with buffers for ISA-databus

- O integrated ISA Plug and Play (Windows 95 Spec.)

- O only 2 I/O addresses used on ISA-PC bus

- O one of 7 interrupt channels on ISA-PC bus selectable by software

- integrated PCMCIA interface

- O microprocessor interface compatible to Motorala bus and Siemens/Intel bus

- O simple access to PCM30 interface for tone synthetisation

- O Timer with interrupt and watchdog capability in processor mode

- O 3-5V supply voltage

- O rectangular QFP 100 case

# 1 General description

The HFC-SP is an ISDN S/T HDLC basic rate controller for so called "passive" ISDN PC cards with integrated S/T interface and PCM30 highway interface. It only needs an external SRAM to form a high performance ISDN PC card. Most problems with passive ISDN PC cards as small FIFOs and massive interrupt load for the host CPU are overcome by the HFC-SP. So we call ISDN cards with the HFC-SP "semi-active".

Additionally the HFC-SP can be used as a microprocessor peripheral in non-PC applications.

The ultra deep FIFOs of the HFC-SP are realized with an external SRAM. Also an industrial standard serial interface for telecom peripheral ICs is implemented. Codecs are normally connected to this interface.

#### 1.1 Applications

- O ISDN PC card

- O ISDN terminal adapter

- O ISDN smart NTs

- O ISDN PABX

- O ISDN modems

Figure 1: HFC-SP block diagram

January 2001 7 of 83

#### 1.2 Mode description

The HFC-SP has 6 different bus modes, which can be selected by the lines MODE, ALE and IIOSEL0-IIOSEL3. Depending on the selected mode the function of several pins is different (see: Pin description).

| MODE | ALE   | IIOSEL03 | Selected mode                   |

|------|-------|----------|---------------------------------|

| NC   | GND   | ≠0       | ISA-PC mode (mode 1)            |

| NC   | VDD   | all 0    | processor mode (mode 2)         |

| NC   | GND   | all 0    | processor mode (mode 3)         |

| NC   | pulse | all 0    | processor mode (mode 4)         |

| GND  | GND   | *)       | ISA Plug and Play mode (mode 5) |

| VDD  | GND   | *)       | PCMCIA mode (mode 6)            |

Table 1: Mode selection

NC = not connected (leave pin open)

\*) IIOSEL0: EE\_SCL Clock of external EEPROM

IIOSEL1: EE\_SDA Serial data of external EEPROM

IIOSEL2: SA10 ISA-bus address bit 10 IIOSEL3: SA11 ISA-bus address bit 11

#### 1.2.1 ISA-PC mode

Mode 1: ALE = GND, IIOSEL3-0  $\neq$  0000, MODE = NC

In mode 1 the HFC-SP is addressed by two successive port addresses on the ISA-PC bus. The port address is selected by the lines SA0 - SA9.

The address with SA0='1' is for register selection and the address with SA0='0' is used for data read/write (see also: 3.1).

#### 1.2.2 ISA Plug and Play mode

Mode 5: ISA Plug and Play mode is selected by: ALE = GND and MODE = GND

In mode 5 the HFC-SP is addressed by two successive port addresses on the ISA-PC bus. The port address is selected by the lines SA0 - SA11.

The address with SA0='1' is for register selection and the address with SA0='0' is used for data read/write (see also: 3.2).

#### 1.2.3 Processor interface modes

The processor modes are selected by IIOSEL3-0 = '0000' and MODE left open. In all processor modes line SA6 must be connected to GND.

Mode 2: Motorola bus with control signals /CS, R/W, /DS is selected by setting ALE to VDD.

Mode 3: Siemens/Intel bus with seperated address bus and databus and control signals /CS, /WR, /RD is selected by setting ALE to GND.

Mode 4: Intel bus with multiplexed address and databus with control signals /CS, /WR, /RD, ALE.

ALE latches the address. The address lines SA0-SA7 must be connected to the data lines BD0-BD7 (except SA6 which must be connected to GND).

The lines SA0-SA7 (except SA6) are used for direct addressing the internal registers of the HFC-SP (see also 3.4).

#### 1.2.4 PCMCIA mode

Mode 6: PCMCIA mode is selected by: ALE = GND and MODE = VDD

In mode 6 the HFC-SP is addressed by two successive port addresses. The port address is selected by the lines SA0 - SA11.

The address with SA0='1' is for register selection and the address with SA0='0' is used for data read/write (see also: 3.5).

January 2001 9 of 83

# 2 Pin description

Figure 2: Pin Connection

#### 2.1 ISA-PC bus and microprocessor interface

| Pin No. | Pin Name | <u>I</u> nput   | Mode    | Function                              |

|---------|----------|-----------------|---------|---------------------------------------|

|         |          | <u>O</u> utput  |         |                                       |

|         |          |                 |         | Mode/initial I/O address select       |

| 1       | IIOSEL0  | I <sup>u)</sup> | 1,2,3,4 | bit 0                                 |

|         | EE_SCL   | O e)            | 5,6     | Clock of external EEPROM              |

| 2       | IIOSEL1  | I               | 1,2,3,4 | Mode/initial I/O address select bit 1 |

|         | EE_SDA   | I/O e)          | 5,6     | Serial data of external EEPROM        |

| 3       | IIOSEL2  | I <sup>u)</sup> | 1,2,3,4 | Mode/initial I/O address select bit 2 |

|         | SA10     |                 | 5,6     | Address bit 10                        |

| 4       | IIOSEL3  | I u)            | 1,2,3,4 | Mode/initial I/O address select bit 3 |

|         | SA11     |                 | 5,6     | Address bit 11                        |

|         |          |                 |         | Register/ISA-PC address bus           |

| 5       | SA0      | I               | all     | Address bit 0                         |

| 6       | SA1      | I               | all     | Address bit 1                         |

| 7       | SA2      | I               | all     | Address bit 2                         |

| 8       | SA3      | I               | all     | Address bit 3                         |

| 9       | SA4      | I               | all     | Address bit 4                         |

u) internal pull up

external pull up resistor required (see Figure 11 on page 70)

| Pin No. | Pin Name | <u>I</u> nput  | Mode  | Function                                         |

|---------|----------|----------------|-------|--------------------------------------------------|

|         |          | <u>O</u> utput |       |                                                  |

| 10      | SA5      | I              | all   | Address bit 5                                    |

| 11      | SA6      | I              | all   | Address bit 6                                    |

|         |          |                |       | (SA6 must be connected to GND in processor mode) |

| 12      | SA7      | I              | all   | Address bit 7                                    |

| 13      | SA8      | I              | 1,5,6 | Address bit 8                                    |

|         | /DMAAK0  | I              | 2,3,4 | DMA acknowledge channel 0                        |

|         |          |                |       | Direct access to GCI/IOM2 bus AUX1 channel data  |

|         |          |                |       | register (low active)                            |

| 14      | SA9      | I              | 1,5,6 | address bit 9                                    |

|         | /DMAAK1  | I              | 2,3,4 | DMA acknowledge channel 1                        |

|         |          |                |       | direct access on GCI/IOM2 bus AUX2 channel       |

|         |          |                |       | dataregister (low active)                        |

# d important!

If DMA acknowledge signals /DMAAK0 and /DMAAK1 are active, the function of the read/write enables is inverted. This means a read command on the controller databus writes the AUX-Channel register and a write command reads the register. The address on the address bus (SA0-SA7) is ignored.

| 15 | /AEN    | I        | 1,5     | PC bus address enable                         |

|----|---------|----------|---------|-----------------------------------------------|

|    | /CE1    | I        | 6       | Card enable (low active)                      |

|    | /CS     | I        | 2,3,4   | chipselect low active                         |

| 16 | IOCHRDY | O 1)     | 1,5     | I/O channel ready                             |

|    | /WAIT   | $O^{1)}$ | 2,3,4   | low active wait signal for external processor |

|    | /WAIT   | $O^{1)}$ | 6       | Extended bus cycle (low active)               |

| 17 | /IOR    | I        | 1,3,4,5 | I/O read enable                               |

|    | /IORD   | I        | 6       | I/O read (low active)                         |

|    | /DS     | I        | 2       | I/O data strobe                               |

| 18 | /IOW    | I        | 1,3,4,5 | I/O write enable                              |

|    | /IOWR   | I        | 6       | I/O write (low active)                        |

|    | R/W     | I        | 2       | Read/Write select (WR='0')                    |

| 21 | BD0     | I/O      | all     | Databus bit 0 (LSB)                           |

| 22 | BD1     | I/O      | all     | Databus bit 1                                 |

| 23 | BD2     | I/O      | all     | Databus bit 2                                 |

| 24 | BD3     | I/O      | all     | Databus bit 3                                 |

| 25 | BD4     | I/O      | all     | Databus bit 4                                 |

| 26 | BD5     | I/O      | all     | Databus bit 5                                 |

| 27 | BD6     | I/O      | all     | Databus bit 6                                 |

| 28 | BD7     | I/O      | all     | Databus bit 7 (MSB)                           |

January 2001 11 of 83

<sup>1)</sup> open drain, external pull up resistor required

| Pin No. | Pin Name | <u>I</u> nput  | Mode      | Function                                           |

|---------|----------|----------------|-----------|----------------------------------------------------|

|         |          | <u>O</u> utput |           |                                                    |

| 31      | BUSDIR   | O              | 1,2,3,4,5 | Databus direction signal for external busdriver    |

|         |          |                |           | '0' BD0-BD7 are outputs                            |

|         | /INPACK  | O              | 6         | Input port acknowledge (low active)                |

| 32      | ALE      | I              |           | Address latch enable                               |

|         |          |                |           | ALE is also used for mode selection of the HFC-SP. |

|         |          |                |           | See Mode selection on page 8 for detailed          |

|         |          |                |           | information.                                       |

| 49      | MODE     | I              |           | Mode selection                                     |

|         |          |                |           | See Mode selection on page 8 for detailed          |

|         |          |                |           | information.                                       |

# 2.2 S/T interface transmit signals

| Pin No. | Pin Name | <u>I</u> nput<br><u>O</u> utput | Function                     |

|---------|----------|---------------------------------|------------------------------|

| 34      | TX2_HI   | 0                               | Transmit output 2            |

| 35      | /TX1_LO  | O                               | GND driver for transmitter 1 |

| 36      | /TX_EN   | O                               | Transmit enable              |

| 37      | /TX2_LO  | O                               | GND driver for transmitter 2 |

| 38      | TX1_HI   | O                               | Transmit output 1            |

See also: 7.2 External transmitter circuitry.

# 2.3 S/T interface receive signals

| 43 | R2      | I | Receive data 2      |

|----|---------|---|---------------------|

| 44 | LEV_R2  | I | Level detect for R2 |

| 45 | LEV_R1  | I | Level detect for R1 |

| 46 | R1      | I | Receive data 1      |

| 48 | ADJ_LEV | 0 | Levelgenerator      |

See also: 7.1 External receiver circuitry.

# 2.4 SRAM Interface

| Pin No. | Pin Name | <u>I</u> nput<br><u>O</u> utput | Function                               |

|---------|----------|---------------------------------|----------------------------------------|

|         |          |                                 | CDANG L                                |

| 53      | SRD0     | I/O                             | SRAM data bit 0 (LSB)                  |

| 54      | SRD1     | I/O                             | SRAM data bit 0 (LSB)                  |

| 55      | SRD2     | I/O                             | SRAM data bit 1<br>SRAM data bit 2     |

| 56      |          | I/O                             | SRAM data bit 2                        |

| 57      | SRD3     |                                 | 11 11 11 11 11 11 11 11 11 11 11 11 11 |

|         | SRD4     | I/O                             | SRAM data bit 4                        |

| 58      | SRD5     | I/O                             | SRAM data bit 5                        |

| 59      | SRD6     | I/O                             | SRAM data bit 6                        |

| 60      | SRD7     | I/O                             | SRAM data bit 7 (MSB)                  |

| -62     | ap . o   |                                 | SRAM address bus                       |

| 63      | SRA0     | 0                               | SRAM address bus bit 0 (LSB)           |

| 64      | SRA1     | 0                               | SRAM address bus bit 1                 |

| 65      | SRA2     | 0                               | SRAM address bus bit 2                 |

| 66      | SRA3     | О                               | SRAM address bus bit 3                 |

| 67      | SRA4     | О                               | SRAM address bus bit 4                 |

| 68      | SRA5     | О                               | SRAM address bus bit 5                 |

| 69      | SRA6     | O                               | SRAM address bus bit 6                 |

| 70      | SRA7     | O                               | SRAM address bus bit 7                 |

| 71      | SRA8     | O                               | SRAM address bus bit 8                 |

| 72      | SRA9     | O                               | SRAM address bus bit 9                 |

| 74      | SRA10    | O                               | SRAM address bus bit 10                |

| 75      | SRA11    | O                               | SRAM address bus bit 11                |

| 76      | SRA12    | О                               | SRAM address bus bit 12                |

| 77      | SRA13    | 0                               | SRAM address bus bit 13                |

| 78      | SRA14    | 0                               | SRAM address bus bit 14 (MSB)          |

|         |          |                                 | SRAM control signals                   |

| 50      | /SRRD    | O                               | Read strobe to external device         |

| 79      | /SRCS    | 0                               | SRAM chip select                       |

| 80      | /SRWR    | O                               | SRAM write enable                      |

# 2.5 Oscillator

|   | 82 | OSC_IN  | I | Oscillator input or quarz connection  |

|---|----|---------|---|---------------------------------------|

|   |    |         |   | 12.288 MHz or 24.576 MHz              |

| ſ | 83 | OSC_OUT | O | Oscillator output or quarz connection |

January 2001 13 of 83

#### 2.6 **GCI/IOM2** bus interface

| Pin No. | Pin Name | <u>I</u> nput  | Mode | Function                                        |

|---------|----------|----------------|------|-------------------------------------------------|

|         |          | <u>O</u> utput |      |                                                 |

| 85      | C4IO     | I/O u)         | all  | 4.096 Mhz clock                                 |

|         |          |                |      | GCI/IOM2 bus clock master: output               |

|         |          |                |      | GCI/IOM2 bus clock slave: input (reset default) |

| 86      | F0IO     | I/O u)         | all  | Frame synchronisation, 8kHz pulse for GCI/IOM2  |

|         |          |                |      | bus frame synchronisation                       |

|         |          |                |      | GCI/IOM2 bus master: output                     |

|         |          |                |      | GCI/IOM2 bus slave: input (reset default)       |

| 87      | STIO1    | I/O u)         | all  | GCI/IOM2 bus databus I                          |

|         |          |                |      | Slotwise programmable as input or output        |

| 88      | STIO2    | I/O u)         | all  | GCI/IOM2 bus databus II                         |

|         |          |                |      | Slotwise programmable as input or output        |

internal pull up

# **2.7 GCI/IOM2 Timeslot enable signals** (e. g. for PCM codecs)

| 91 | F1_A  | O | all       | enable signal for external CODEC A                   |

|----|-------|---|-----------|------------------------------------------------------|

|    |       |   |           | Programmable as positive (reset default) or negative |

|    |       |   |           | pulse.                                               |

| 92 | F1_B  | O | 1,2,3,4,6 | enable signal for external CODEC B                   |

|    |       |   |           | Programmable as positive (reset default) or negative |

|    |       |   |           | pulse.                                               |

|    | IRQ_G | O | 5         | PC bus interrupt request G                           |

# 2.8 Interrupt outputs

| Pin No. | Pin Name | <u>I</u> nput  | Mode  | Function                                             |

|---------|----------|----------------|-------|------------------------------------------------------|

|         |          | <u>O</u> utput |       |                                                      |

| 94      | IRQ_A    | I/O            | 1,5,6 | PC bus interrupt request A or interrupt input from   |

|         |          |                |       | external device (see: CIRM register bit description) |

|         | /IRQ_P   | O 1)           | 2,3,4 | processor interrupt request low active               |

| 95      | IRQ_B    | O              | 1,5   | PC bus interrupt request B                           |

|         | /IREQ    | O              | 6     | Interrupt request (low active)                       |

|         | IRQ_P    | $O^{2)}$       | 2,3,4 | processor interrupt request high active              |

| 96      | IRQ_C    | О              | 1,5,6 | PC bus interrupt request C                           |

|         | /WD_RES  | O 1)           | 2,3,4 | Watchdog expired, external reset low active          |

| 97      | IRQ_D    | О              | 1,5   | PC bus interrupt request D                           |

|         | /OE      | I              | 6     | Output enable (low active)                           |

|         | WD_RES   | $O^{2)}$       | 2,3,4 | Watchdog expired, external reset high active         |

| 98      | IRQ_E    | О              | 1,5   | PC bus interrupt request E                           |

|         | /WE      | I              | 6     | Write enable (low active)                            |

|         | DMARQ0   | O              | 2,3,4 | DMA request AUX1 channel register (high active)      |

| 99      | IRQ_F    | О              | 1,5   | PC bus interrupt request F                           |

|         | /REG     | I              | 6     | Register select and I/O enable (low active)          |

|         | DMARQ1   | O              | 2,3,4 | DMA request AUX2 channel register (high active)      |

open drain, external pull up resistor required

# 2.9 Miscellaneous pins

| 1 | 00 | RESET | I | all | Reset for HFC-SP (high active) |

|---|----|-------|---|-----|--------------------------------|

|---|----|-------|---|-----|--------------------------------|

January 2001 15 of 83

open source, external pull down resistor required

#### 2.10 Power supply

| Pin No.                         | Pin Name | Function         |

|---------------------------------|----------|------------------|

| 19, 30, 41, 42, 51, 61, 84, 89  | VDD      | VDD (+3V to +5V) |

| 20, 29, 33, 39, 40, 47, 52, 62, | GND      | GND              |

| 73, 81, 90, 93                  |          |                  |

#### d important!

All power supply pins VDD must be directly connected to each other. Also all pins GND must be directly connected to each other.

To keep VDD and GND bounce to a minimum a bypass capacitor (10 nF to 100 nF) should be placed between each pair of VDD/GND pins.

#### 2.11 RESET characteristics

The reset signal (hardware reset or software reset) must be active for at least 4 clock cycles.

The GCI/IOM2 bus lines STIO1, STIO2 and the interrupt lines are in tristate mode after a reset.

The HFC-SP is in slave mode after reset. C4IO and F0IO are inputs.

In the processor modes DMARQ1 and DMARQ2 are inactive ('0').

The S/T state machine is stuck to '0' after reset. This means the HFC-SP does not react to any signal on the S/T interface before the S/T state machine is initialised.

The registers' initial values are described in the Register bit description (section 4 of this data sheet).

After RESET the HFC-SP is in an initialisation cycle and is therefor busy for a maximum of 160 clock cycles.

# 3 Functional description

#### 3.1 ISA-PC mode

ISA-PC mode is selected by MODE = NC, ALE = GND and IIOSEL0..3 $\neq$ 0.

The HFC-SP occupies two consecutive addresses in the I/O map of a PC if it is in ISA-PC mode. It decodes only the 10 lower address lines as most slot cards do on the ISA-PC bus. The base I/O address is 2 byte aligned so the lower of both addresses is the one with SA0 = 0 and the higher address is the one with SA0 = 1.

After every hardware reset (RESET = 1) the I/O address select circuit inside the HFC-SP is in hardware mode. In this mode the HFC-SP can not be accessed until it is initialised to an I/O address.

At first one of 15 different I/O addresses must be selected by the 4 inputs IIOSEL0 .. IIOSEL3 as Table 2 shows:

| HOSEL   | Selected I/O address |

|---------|----------------------|

| 3210    |                      |

| 0000    | processor mode       |

| 0001    | 2E0h                 |

| 0010    | 2D0h                 |

| 0 0 1 1 | 210h                 |

| 0100    | 2C0h                 |

| 0 1 0 1 | 200h                 |

| 0110    | 2F8h                 |

| 0 1 1 1 | 2E8h                 |

| 1000    | 2B0h                 |

| 1001    | 3E0h                 |

| 1010    | 320h                 |

| 1011    | 278h                 |

| 1100    | 310h                 |

| 1101    | 330h                 |

| 1110    | 300h                 |

| 1111    | 3E8h                 |

Table 2: Selected I/O address after reset

The hardware selected I/O address might have an address collision with another I/O device in the PC.

After a hardware reset (RESET = 1) you must first write an I/O address into the HFC-SP to set the I/O address for every further access to the device.

#### The procedure is as follows:

First you must write the lower 8 bits of the new I/O address you want into the lower address (SA0 = 0) of the hardware selected I/O address. The LSB of the new address is a don't care bit because the HFC-SP always occupies two I/O addresses.

January 2001 17 of 83

Then the additional 2 bits of the new I/O address have to be written into the higher address (SA0 = 1) of the hardware selected I/O address. The other 6 bits in the byte must have a special pattern to switch over to the software selected address mode. This pattern must be 0101 01aa, whereby aa are the 2 higher address bits.

e.g.: wanted I/O address: 3A4h / 3A5h

IIOSEL(3:0): 0001

then hardware selected I/O address is: **2E0h** = 10 1110 0000 b

write the value A4h or A5h into 2E0h = 1010 010x b write the value 57h into 2E1h = 0101 01 b pattern 11 b address 0101 0111 b

x = don't care

All further accesses to the HFC-SP can only be done on the addresses **3A4h** / **3A5h**. Only a hardware reset will switch back the HFC-SP into hardware selected address mode.

hint:

It's useful to solve a possible address conflict by programming the I/O address as early as possible. It is recommendable to set the address with a simple .SYS driver in a DOS environment.

#### 3.2 ISA Plug and Play mode

To select ISA Plug and Play mode the pins MODE and ALE must both be connected to GND. The HFC-SP needs two consecutive addresses in the I/O map of a PC for operation. Usually also one IRQ line is used. The following section describes how to configure the HFC-SPs interrupts.

#### 3.2.1 IRQ assignment

The IRQ lines are disabled after a hardware reset.

The IRQ assigned by the PnP BIOS can be read from register CHIP\_ID (16h), bits [3:0]. Bits [2:0] of the CIRM register have to be set according to the hardware wiring on the PCB and the IRQ number assigned by the PnP BIOS.

# 3.2.2 ISA Plug and Play control registers

# 3.2.2.1 Card level control regsisters

| Plug and Play<br>control register | Read<br>Write | Accessable in state                              | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|-----------------------------------|---------------|--------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h                               | W             | Isolation state<br>Config state *)               | Set read data port address register. Bits[7:0] become bits[9:2] of the port's I/O address. Bits[11:10] are hardwired to 00b and bits[1:0] are hardwired to 11b.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 01h                               | r             | Isolation state                                  | <b>Serial isolation register</b> . Used to read the serial identifier during the card isolation process.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 02h                               | W             | Sleep state,<br>Isolation state,<br>Config state | Configuration control register. Bits[7:3] are reserved and must be zero. The defined bits are:  O Reset Bit. When set to one, resets all of the card's configuration registers to their default state. The CSN is not affected.  Return to wait for key state. When set to one, all cards return to wait for key state.  Their CSNs and configuration registers are not affected. This command is issued after all cards have been configured and activated.  Reset CSN to zero. When set to one, all cards reset their CSN to zero.  All bits are automatically cleared by the hardware.                                                                     |

| 03h                               | W             | Sleep state, Isolation state, Config state       | <ul> <li>Wake command register. Writing a CSN to this register has the following effects:</li> <li>If the value written is 00h, all cards in the sleep state with a CSN=00h go to the isolation state. Any card in configure state (CSN not 00h) goes to the sleep state.</li> <li>If the value written is not 00h, any card in the sleep state with a matching CSN goes to configure state. Any card in the isolation state goes to sleep state.</li> <li>Any write to a card's wake command register with a match on its CSN causes the pointer to the serial identifier / resource data to be reset to the first byte of the serial identifier.</li> </ul> |

<sup>\*)</sup> This is an extension to the Plug and Play Specification

January 2001 19 of 83

| Plug and Play    | Read          | Accessable in state                             | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|---------------|-------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| control register | <u>W</u> rite |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| address          |               |                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 04h              | r             | Config state                                    | Resource data register. This register is used to read the device's recource data. Each time that a read is performed from this register a byte of the resource data is returned and the resource data pointer is incremented. Prior to reading each byte, the programmer must read from the status register to determine if the next byte is available for reading from the resource data register.  The card's serial identifier and checksum must be read prior to accessing the resource requirement list via this register. |

| 05h              | r             | Config state                                    | <b>Status register.</b> Prior to reading the next byte of the device's resource data, the programmer must read from this register and check bit 0 for a one. This is the resource data byte available bit. Bits[7:1] are reserved.                                                                                                                                                                                                                                                                                              |

| 06h              | r/w           | Isolation state <sup>*)</sup> ,<br>Config state | Card select number (CSN) register. The configuration software uses the CSN register to assign a unique ID to the card. The CSN is then used to wake up the card's configuration logic whenever the configuration program must access its configuration registers.                                                                                                                                                                                                                                                               |

| 07h              | r             | Config state                                    | <b>Logical device number register.</b> The number in this register points to the logical device the next commands will operate on. The HFC-SP only supports one logical device. This register is hardwired to all zeros.                                                                                                                                                                                                                                                                                                        |

<sup>\*)</sup> only if the isolation process is finished; the last card remains in isolation state until a CSN is assigned.

# 3.2.2.2 Logical device control registers

| Plug and Play    | Read          | Accessable in state | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

|------------------|---------------|---------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| control register | <u>W</u> rite |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| address          |               |                     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 30h              | r/w           | Config state        | Activate register. Setting bit 0 to a one activates the card on the ISA bus. When cleared, the card cannot respond to any ISA bus transactions (other than accesses to its Plug and Play configuration ports). Reset clears bit 0. Bits[7:1] are reserved and return zeros when read.  The HFC-SP only supports one logical device, so it is not necessary to write the logical device number into the card's logical device number register prior to writing to this register. |

| 31h              | r/w           | Config state        | I/O range check register.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                  |               | C                   | Bit(s) Description                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

|                  |               |                     | 7:2 Reserved, return zero when read                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|                  |               |                     | 1 When set to one, enables I/O range checking                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  |               |                     | and disables it when cleared to zero. When                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|                  |               |                     | enabled, bit 0 is used to select a pattern for the logical device to return.                                                                                                                                                                                                                                                                                                                                                                                                    |

|                  |               |                     | This bit is only valid if the logical device is                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                  |               |                     | deactivated (see Activate register).                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|                  |               |                     | 0 When set, the logical device returns 55h in                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|                  |               |                     | response to any read from the logical device's                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|                  |               |                     | assigned I/O space. When cleared, AAh is                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                  |               |                     | returned.                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

# 3.2.3 ISA Plug and Play configuration registers

# 3.2.3.1 I/O port configuration registers

| Plug and Play<br>configuration<br>register address | Read<br>Write | Accessable in state | Description                                                                |

|----------------------------------------------------|---------------|---------------------|----------------------------------------------------------------------------|

| 60h                                                | r/w           | Config state        | I/O decoder 0 base address upper byte. I/O port base address bits[15:8].*) |

| 61h                                                | r/w           | Config state        | I/O decoder 0 base address lower byte. I/O port base address bits[7:0]. *) |

<sup>\*)</sup> Only bits[11:0] are checked by the HFC-SP's internal address decoder in PnP mode.

January 2001 21 of 83

#### 3.2.3.2 Interrupt configuration registers

| Plug and Play configuration | Read<br>Write | Accessable in state | Description                                |

|-----------------------------|---------------|---------------------|--------------------------------------------|

| register address            |               |                     |                                            |

| 70h                         | r/w           | Config state        | IRQ select configuration register 0.       |

|                             |               |                     | Bits[3:0] specify the sleceted IRQ number. |

|                             |               |                     | Bits[7:4] are reserved.                    |

| 71h                         | r/w           | Config state        | IRQ type configuration register 0.         |

|                             |               |                     | Bits[1:0] are ignored.                     |

|                             |               |                     | Bits[7:2] are reserved.                    |

## d important!

All registers not implemented return 00h when read except the DMA configuration registers 74h and 75h. These two registers return 04h when read. This means no DMA channel has been selected.

# 3.2.4 Writing the Plug and Play configuration EEPROM

The EEPROM Writing Spec. is only available on special request to avoid destruction of configuration information by not authorized programs or software viruses.

#### 3.3 ISA-PC bus interface

The HFC-SP only uses 2 I/O addresses with SA0 switching between data or control information in ISA-PC mode and ISA Plug and Play mode. As normal only 10 bits of the ISA-PC bus address are used for I/O address selection in ISA-PC mode. In ISA Plug and Play mode 12 bits are decoded by the address decoder.

| SA0 | /IOR | /IOW | /AEN | Operation     |

|-----|------|------|------|---------------|

| X   | X    | X    | 1    | no access     |

| X   | 1    | 1    | X    | no access     |

| 0   | 0    | 1    | 0    | read data     |

| 0   | 1    | 0    | 0    | write data    |

| 1   | 0    | 1    | 0    | read status   |

| 1   | 1    | 0    | 0    | write control |

X = don't care

d important!

ALE must be connected to GND and at least one of the IIOSEL0-3 must be '1' or open!

The HFC-SP has no memory or DMA access to any component on the ISA-PC bus.

Because of its power drive characteristic it needs no external driver for the ISA-PC bus data lines.

If necessary an external bus driver can be added. In this case the output BUSDIR determines the driver direction.

BUSDIR = 1 means that data is driven into the HFC-SP;

BUSDIR = 0 means that the HFC-SP is read and data is driven to the external bus.

January 2001 23 of 83

#### 3.4 Processor mode

Processor mode is selected by MODE = NC and IIOSEL0..3=0.

In the microprocessor mode the HFC-SP uses 256 I/O addresses (SA0 - SA7).

| /IOR | /IOW | /CS | ALE      | Operation  | Mode |

|------|------|-----|----------|------------|------|

| /DS  | R/W  |     |          |            |      |

| X    | X    | 1   | X        | no access  | all  |

| 1    | 1    | X   | X        | no access  | all  |

| 0    | 1    | 0   | 1        | read data  | 2    |

| 0    | 0    | 0   | 1        | write data | 2    |

| 0    | 1    | 0   | 0        | read data  | 3    |

| 1    | 0    | 0   | 0        | write data | 3    |

| 0    | 1    | 0   | $0^{*)}$ | read data  | 4    |

| 1    | 0    | 0   | 0*)      | write data | 4    |

X = don't care

All registers are directly accessable by their I/O address (see register description).

Except in mode 4 ALE is assumed to be stable after a RESET.

# d important!

For write accesses to the HFC-SP the data lines must be stable and valid **before** /IOW or /DS get low (see also: Timing diagram 1 on page 59). With Intel compatible processors it may be neccessary to delay the /IOW or /DS signals.

<sup>\*) 1-</sup>pulse latches I/O address.

#### 3.4.1 DMA access in processor mode

In processor mode a simple DMA access to the auxiliary channels of the GCI/IOM2 interface is possible. This is useful for tone synthetisation or for voice recording. DMAREQ is asserted every  $125\mu s$ . DMAREQ is reset when /DMAAK is active.

#### d note

If DMA acknowledge signals /DMAAK0 and /DMAAK1 are active, the function of the read/write enables is inverted. This means a read command on the controller databus writes the AUX-Channel register and a write command reads the register. The address on the address bus (SA0-SA7) is ignored.

| Mode  | /DMAAK0 | /DMAAK1 | /CS | ALE | /IOR<br>/DS | /IOW<br>R/W | Function       |

|-------|---------|---------|-----|-----|-------------|-------------|----------------|

| 2,3,4 | 1       | 1       | X   | X   | X           | X           | no DMA         |

| 2     | 0       | 1       | X   | 1   | X           | 1           | DMA write AUX1 |

| 2     | 1       | 0       | X   | 1   | X           | 1           | DMA write AUX2 |

| 3     | 0       | 1       | X   | 0   | 0           | 1           | DMA write AUX1 |

| 3     | 1       | 0       | X   | 0   | 0           | 1           | DMA write AUX2 |

| 4     | 0       | 1       | X   | 0*) | 0           | 1           | DMA write AUX1 |

| 4     | 1       | 0       | X   | 0*) | 0           | 1           | DMA write AUX2 |

Table 3: DMA access in processor mode

# d important!

If DMA is not used /DMAAK0 and /DMAAK1 must be connected to VDD.

January 2001 25 of 83

<sup>\*) 1-</sup>pulse latches I/O address.

#### 3.5 PCMCIA mode

#### 3.5.1 Internal HFC-SP register selection

The HFC-SP occupies two consecutive addresses in the I/O map. The base I/O address must be 2 byte aligned so the lower of both addresses is the one with SA0 = 0 and the higher address is the one with SA0 = 1. The lines SA1 to SA11 are don't care. The registers of the HFC-SP are selected by writing the registers' address to the higher I/O address (SA0=1). Registers are read/written by reading/writing the base I/O address (SA0=0).

#### 3.5.2 Attribute memory

After hardware reset the card's information structure (CIS) is copied from the EEPROM to even numbered addresses of the SRAM starting with 0000h (288 byte are occupied for the CIS). To avoid accesses in this phase the /WAIT signal is active.

#### 3.5.3 PCMCIA registers

#### **Configuration Option Register (COR):**

#### Register address: 400h in Configuration Memory

| D7     | D6      | D5                  | D4 | D3 | D2 | D1 | D0 |

|--------|---------|---------------------|----|----|----|----|----|

| SRESET | LevIREQ | Configuration Index |    |    |    |    |    |

|        | 1       |                     |    |    |    |    |    |

#### The fields are as follows:

| SRESET              | SRESET card. Setting this bit to one places the card in the reset state. This bit |

|---------------------|-----------------------------------------------------------------------------------|

|                     | must be cleared to zero by the user.                                              |

| LevIREQ             | This bit is not implemented and returns always 1 when read to indicate usage of   |

|                     | level mode interrupts.                                                            |

| Configuration Index | Configuration Index.                                                              |

|                     | Bit 0 must be set to 1 to enable I/O accesses to the HFC-SP.                      |

|                     | Bit 5 must be set to 1 to write data to the EEPROM.                               |

# Card Configuration and Status Register (CSR): Register address: 402h in Configuration Memory

| D7      | D6     | D5    | D4   | D3    | D2     | D1   | D0   |

|---------|--------|-------|------|-------|--------|------|------|

| Changed | SigChg | IOis8 | Rsvd | Audio | PwrDwn | Intr | Rsvd |

| 0       | 0      | 1     | 0    | 0     | 0      |      | 0    |

The fields are as follows:

| Changed | Unimplemented and return 0 when read.                                |

|---------|----------------------------------------------------------------------|

| SigChg  |                                                                      |

| Rsvd    |                                                                      |

| Audio   |                                                                      |

| PwrDwn  |                                                                      |

| IOis8   | Unimplemented and return 1 when read to indicate an 8 bit data path. |

| Intr    | Internal state of interrupt request (IREQ).                          |

# 3.5.4 CIS programming

The EEPROM Programming Spec. is only available on special request to avoid destruction of configuration information by not authorized programs or software viruses.

January 2001 27 of 83

#### 3.6 Internal HFC-SP register description

In ISA-PC mode, ISA Plug and Play mode and PCMCIA mode all registers are selected by writing the register address into the Control Internal Pointer (CIP) register. This is done by writing the HFC-SP on the higher I/O address (SA0 = 1).

All consecutive read or write data accesses (SA0 = 0) are done with the selected register until the CIP register is changed.

In processor mode all registers can be directly accessed. The registers are selected by SA0 - SA7.

#### 3.6.1 FIFO control registers

The FIFO control registers are used to select and control the FIFOs of the HFC-SP. In processor mode the value is the address which directly selects the corresponding register.

The FIFO register selection is independent of the B- or D-channel FIFO number. The FIFO is selected by the FIFO select register.

#### 3.6.1.1 FIFO select register

| CIP / I/O-address |     | Name    | r/w | Function       |  |

|-------------------|-----|---------|-----|----------------|--|

| 00010000          | 10h | FIF_SEL | w   | FIFO selection |  |

#### 3.6.1.2 FIFO registers

| CIP / I/O-a | ddress | Name         | r/w | Function                                         |

|-------------|--------|--------------|-----|--------------------------------------------------|

| 100000xx    | 80h    | FIF Z1L      | r   | FIFO input counter (Z1) low byte                 |

| 100001xx    | 84h    | FIF_Z1H      | r   | FIFO input counter (Z1) high byte                |

| 100010xx    | 88h    | FIF_Z2L      | r   | FIFO output counter (Z2) low byte                |

| 100011xx    | 8Ch    | FIF_Z2H      | r   | FIFO output counter (Z2) high byte               |

| 101010xx    | A8h    | FIF_INC_F1*) | r   | read this register to increment frame counter F1 |

| 101011xx    | ACh    | FIF_DWR      | W   | data write into FIFO and increment Z1            |

| 101100xx    | B0h    | FIF_F1       | r   | FIFO input HDLC frame counter (F1)               |

| 101101xx    | B4h    | FIF_F2       | r   | FIFO output HDLC frame counter (F2)              |

| 101110xx    | B8h    | FIF_INC_F2*) | r   | read this register to increment frame counter F2 |

| 101111xx    | BCh    | FIF_DRD      | r   | data read out of FIFO and increment Z2           |

<sup>\*)</sup> only in HDLC mode; In transparent mode (see also: 3.9.2) the frame counters F1 and F2 must not be incremented.

# d important!

#### FIFO change, FIFO reset and F1/F2 incrementation

Changing the FIFO, reseting the FIFO or incrementing the frame counters causes a short BUSY period of the HFC-SP. This means an access to FIFO control registers is NOT allowed until BUSY status is reset (bit 0 of STATUS register). This has a maximum duration of 25 clock cycles ( $2\mu s$ ). Status, interrupt and control registers can be read and written at any time.

January 2001 29 of 83

# 3.6.2 Registers of the S/T section

| CIP / I/O-a | address | Name                  | r/w    | Function                                                                                            |

|-------------|---------|-----------------------|--------|-----------------------------------------------------------------------------------------------------|

| 00110000    | 30h     | STATES                | r/w    | State of the TE/NT state machine                                                                    |

| 00110001    | 31h     | SCTRL                 | W      | S/T control register                                                                                |

| 00110010    | 32h     | SCTRL_E               | W      | S/T control register (extended)                                                                     |

| 00110011    | 33h     | SCTRL_R               | W      | receive enable for B-channels                                                                       |

| 00110100    | 34h     | SQ_REC<br>SQ_SEND     | r<br>w | receive register for S/Q bits send register for S/Q bits                                            |

| 00110111    | 37h     | CLKDEL                | W      | setup of the delay time between receive and<br>send direction (TE)<br>receive data sample time (NT) |

| 00111100    | 3Ch     | B1_REC*)<br>B1_SEND*) | r<br>w | B1-channel receive register B1-channel transmit register                                            |

| 00111101    | 3Dh     | B2_REC*)<br>B2_SEND*) | r<br>w | B2-channel receive register<br>B2-channel transmit register                                         |

| 00111110    | 3Eh     | D_REC*) D_SEND*)      | r<br>w | D-channel receive register<br>D-channel transmit register                                           |

| 00111111    | 3Fh     | E_REC*)               | r      | E-channel receive register                                                                          |

<sup>\*)</sup> These registers are read/written automatically by the HDLC FIFO controller (HFC) or GCI/IOM2 bus controller and need not be accessed by the user. To read/write data the FIFO registers should be used.

# 3.6.3 Registers of the GCI/IOM2 bus section

#### GCI/IOM2 bus timeslot selection registers

| CIP / I/O-address |     | Name   | r/w | Function                               |

|-------------------|-----|--------|-----|----------------------------------------|

| 00000010          | 02h | C/I    | r/w | C/I command/indication register        |

| 00000011          | 03h | TRxR   | r   | Monitor Tx ready handshake             |

| 00001010          | 0Ah | MON1_D | r/w | first monitor byte second monitor byte |

| 00001011          | 0Bh | MON2_D | r/w |                                        |

# GCI/IOM2 bus timeslot selection registers

| CIP / I/O-address |     | Name r/w |   | Function                         |  |  |

|-------------------|-----|----------|---|----------------------------------|--|--|

| 00100000          | 20h | B1_SSL   | w | B1-channel transmit slot (031)   |  |  |

| 00100001          | 21h | B2_SSL   | w | B2-channel transmit slot (031)   |  |  |

| 00100010          | 22h | AUX1_SSL | w | AUX1-channel transmit slot (031) |  |  |

| 00100011          | 23h | AUX2_SSL | w | AUX2-channel transmit slot (031) |  |  |

| 00100100          | 24h | B1_RSL   | w | B1-channel receive slot (031)    |  |  |

| 00100101          | 25h | B2_RSL   | w | B2-channel receive slot (031)    |  |  |

| 00100110          | 26h | AUX1_RSL | w | AUX1-channel receive slot (031)  |  |  |

| 00100111          | 27h | AUX2_RSL | w | AUX2-channel receive slot (031)  |  |  |

#### GCI/IOM2 bus data registers

| CIP / I/O-address | Name      | r/w | Function                                                                    |  |

|-------------------|-----------|-----|-----------------------------------------------------------------------------|--|

| 00101000 28h      | B1_D*)    | r/w | GCI/IOM2 bus B1-channel data register GCI/IOM2 bus B2-channel data register |  |

| 00101001 29h      | B2_D*)    | r/w |                                                                             |  |

| 00101010 2Ah      | AUX1_D**) | r/w | AUX1-channel data register AUX2-channel data register                       |  |

| 00101011 2Bh      | AUX2_D**) | r/w |                                                                             |  |

<sup>\*)</sup> These registers are read/written automatically by the HDLC FIFO controller (HFC) or by the S/T controller and need not be accessed by the user.

January 2001 31 of 83

<sup>\*\*)</sup> These registers can also be accessed by DMA

# GCI/IOM2 bus configuration registers

| CIP / I/O-address |          | Name r/w |          | Function |                                          |

|-------------------|----------|----------|----------|----------|------------------------------------------|

|                   | 00101101 | 2Dh      | MST_EMOD | W        | extended mode register for GCI/IOM2 bus  |

|                   | 00101110 | 2Eh      | MST_MODE | w        | mode register for GCI/IOM2 bus           |