### FEATURES

- 20MHz sampling rate

- Low Power, 100mW, max

- 100MHz full power input bandwidth

- Integral sample-and-hold

- Single +3V supply operation

- TTL compatible digital output

- Offset binary output coding

#### **GENERAL DESCRIPTION**

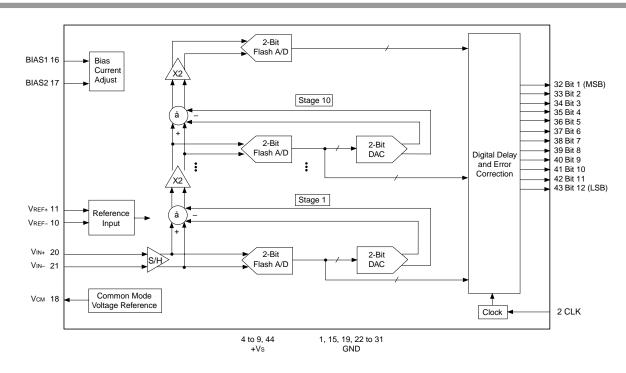

The ADS-238Q is a monolithic, 12-bit, 20MHz, sampling analog-to-digital converter fabricated in a CMOS process. The converter is designed for applications where high speed, wide bandwidth and low power dissipation are essential. These characteristics are provided through the use of a fully differential pipeline A/D architecture with digital error correction logic for the eleven most significant bits.

The ADS-238Q offers excellent dynamic performance while consuming only 79mW, typical. The power dissipation is approximately proportional to the sampling rate, thus the ADS-238Q is ideal for low power applications between 1 and 20 MHz. With low distortion and high dynamic range, this device provides the performance required for imaging, telecommunications, multimedia, and instrumentation applications.

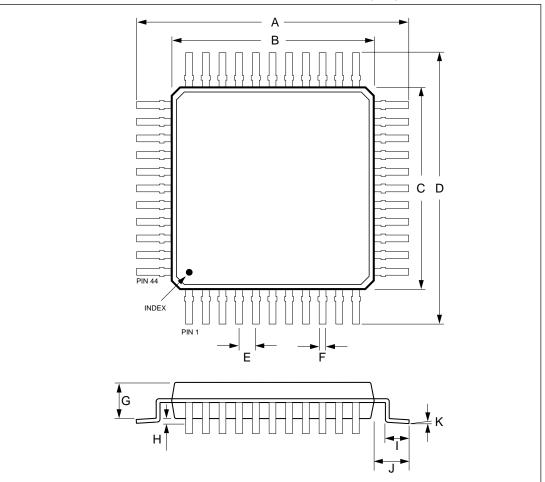

The ADS-238Q is available in a 44-pin (plastic) TQFP package and operates over the commercial 0°C to 70°C temperature range.

## **INPUT/OUTPUT CONNECTIONS**

| PIN | FUNCTION | PIN | FUNCTION     |

|-----|----------|-----|--------------|

| 1   | GND      | 44  | Vs           |

| 2   | CLK      | 43  | BIT 12 (LSB) |

| 3   | N.C.     | 42  | BIT 11       |

| 4   | Vs       | 41  | BIT 10       |

| 5   | Vs       | 40  | BIT 9        |

| 6   | Vs       | 39  | BIT 8        |

| 7   | Vs       | 38  | BIT 7        |

| 8   | Vs       | 37  | BIT 6        |

| 9   | Vs       | 36  | BIT 5        |

| 10  | Vref-    | 35  | BIT 4        |

| 11  | Vref+    | 34  | BIT 3        |

| 12  | N.C.     | 33  | BIT 2        |

| 13  | N.C.     | 32  | BIT 1        |

| 14  | N.C.     | 31  | GND          |

| 15  | GND      | 30  | GND          |

| 16  | BIAS1    | 29  | GND          |

| 17  | BIAS2    | 28  | GND          |

| 18  | Vсм      | 27  | GND          |

| 19  | GND      | 26  | GND          |

| 20  | Vin+     | 25  | GND          |

| 21  | Vin-     | 24  | GND          |

| 22  | GND      | 23  | GND          |

Note: Recommend that N.C. (no connect) pins be connected to analog ground.

Figure 1. ADS-238Q Functional Block Diagram

#

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETERS                                                                      | LIMITS                     | UNITS       |

|---------------------------------------------------------------------------------|----------------------------|-------------|

| Supply Voltage, Vs (Pins 4-9,44)<br>Input Voltages:<br>Analog Input, Vin+, Vin- | -0.5 to +6                 | Volts       |

| (Pin 20, 21)                                                                    | –0.5 to (+Vs +0.5)         | Volts       |

| VREF-, VREF+, (Pin 10, 11)                                                      | -0.5 to (+Vs +0.5)         | Volts       |

| CLK, (Pin 2)<br>Lead Temperature (10 seconds)                                   | –0.5 to (+Vs +0.5)<br>+300 | Volts<br>°C |

# FUNCTIONAL SPECIFICATIONS

(TA = TMIN to TMAX, VS = 3.3V, VREF- = 1.15V, VREF+ = 2.15V, VCM = 1.65V, CLK Frequency = 20MHz, BIAS1 =  $90\mu$ A, BIAS2 =  $9.5\mu$ A, Duty Cycle = 50% and Differential Input, unless otherwise specified.)

| Differential Input, unless otherwise specified.)                                                                                                       |                  |                                         |                         |                                        |

|--------------------------------------------------------------------------------------------------------------------------------------------------------|------------------|-----------------------------------------|-------------------------|----------------------------------------|

| ANALOG INPUTS                                                                                                                                          | MIN.             | TYP.                                    | MAX.                    | UNITS                                  |

| Differential Input Voltage Range<br>Common Mode Input Voltage<br>Input Capacitance<br>Input Bandwidth, Large Signal                                    | ±0.6<br>1.2<br>— | ±1.0<br>1.65<br>1.4<br>120              | ±1.7<br>1.9<br>—        | Volts<br>Volts<br>pF<br>MHz            |

| DIGITAL INPUTS                                                                                                                                         |                  |                                         |                         |                                        |

| Logic Levels<br>Logic "1"<br>Logic "0"<br>Logic Loading "1"<br>Logic Loading "0"<br>Input Capacitance                                                  | 80% Vs<br>       | —<br>—<br>—<br>1.8                      | 20% Vs<br>±1<br>±1<br>— | Volts<br>Volts<br>μΑ<br>μΑ<br>pF       |

| REFERENCE VOLTAGES                                                                                                                                     |                  |                                         |                         |                                        |

| Reference Input Voltage Range<br>(VREF+ - VREF-)<br>Negative Reference Voltage                                                                         | 0.6              | 1.0                                     | 1.7                     | Volts                                  |

| (VREF-)<br>Positive Reference Voltage                                                                                                                  | -                | 1.15<br>2.15                            | _                       | Volts<br>Volts                         |

| (VREF+)<br>Common Mode Output Voltage<br>(VCM)                                                                                                         | 1.3              | 1.65                                    | 1.8                     | Volts                                  |

| STATIC PERFORMANCE                                                                                                                                     |                  |                                         |                         |                                        |

| Resolution<br>Differential Nonlinearity<br>Integral Nonlinearity<br>Common Mode rejection ratio<br>No Missing Codes<br>Offset, Mid-Scale<br>Gain Error | <br><br>12<br>   | 12<br>±0.6<br>±3.0<br>55<br>±1.0<br>0.3 |                         | Bits<br>LSB<br>dB<br>Bits<br>%FSR<br>% |

| DYNAMIC PERFORMANCE                                                                                                                                    |                  |                                         |                         |                                        |

| Peak Harmonics<br>FiN = 5MHz<br>FiN = 10MHz<br>Total Harmonics Distortion                                                                              | 62               | 70<br>61                                |                         | dB<br>dB                               |

| Fin = 5MHz<br>Fin = 10MHz                                                                                                                              | _<br>_           | -68<br>-60                              | -61<br>                 | dB<br>dB                               |

| Signal-to-Noise Ratio   (w/o distortion)   FIN = 5MHz   FIN = 10MHz   Signal-to-Noise Ratio                                                            | 59<br>—          | 62<br>58                                | <br>                    | dB<br>dB                               |

| (and distortion)<br>FเN = 5MHz<br>FเN = 10MHz                                                                                                          | 57<br>—          | 61<br>56                                | _<br>_                  | dB<br>dB                               |

| Effective Number of Bits<br>Fiℕ = 5MHz<br>Fiℕ = 10MHz                                                                                                  | 9.2<br>—         | 9.8<br>9.0                              |                         | Bits<br>Bits                           |

| DYNAMIC PERFORMANCE                                  |        |        |             |         |

|------------------------------------------------------|--------|--------|-------------|---------|

| Differential Phase                                   | _      | 0.2    | _           | Degrees |

| Differential Gain                                    | _      | 0.5    | _           | %       |

| Aperature Uncertainty                                | -      | 10     | _           | ps rms  |

| Aperture Delay Time, tAP                             | -      | 5      | -           | ns      |

| Data Latency                                         | -      | 7.5    | -           | Cycles  |

| A/D Conversion Rate                                  | 20     | —      | -           | MHz     |

| DIGITAL OUTPUTS                                      |        |        |             |         |

| Logic "1"                                            | 80% Vs | 95% Vs | _           | Volts   |

| Logic "0"                                            | _      | 0.1    | 0.4         | Volts   |

| CLK to Output Delay Time, to                         | 4      | 8      | 12          | ns      |

| POWER REQUIREMENTS                                   |        |        |             |         |

| Supply Voltages, VS                                  | 2.8    | 3.3    | 3.6         | Volts   |

| Supply Current, Is                                   | _      | 24     | 30          | mA      |

| Power Dissipation                                    | -      | 79     | 100         | mW      |

| Power Supply Rejection Ratio                         | -      | 63     | —           | dB      |

| PHYSICAL/ENVIRONMENTAL                               |        |        |             |         |

| Operating Temp. Range, Case                          | 0      | _      | +70         | °C      |

| Storage Temperature Range                            | -65    | _      | +125        | °Č      |

| Package Type 44-pin (leaded), plastic thin guad flat |        |        | lat package |         |

| Weight                                               |        |        |             |         |

# **TECHNICAL NOTES**

#### **Differential Analog Input**

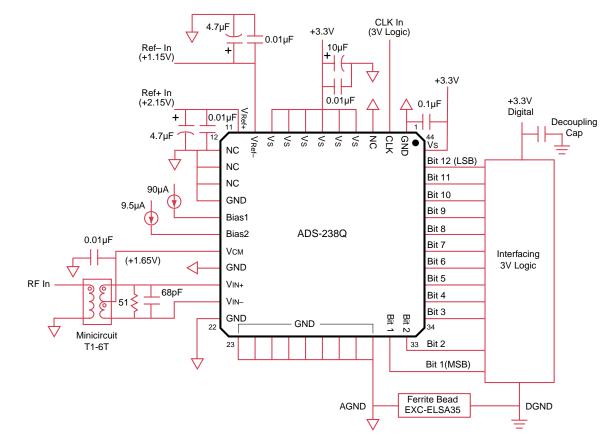

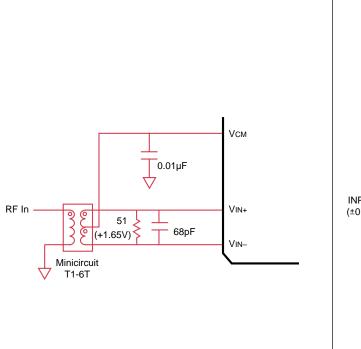

The analog input is a fully differential input that can be configured in various ways depending on whether a singleended or differential, AC or DC coupled input is required. An AC coupled input is most readily implemented using a transformer (1:1 with a center tap on the secondary winding) as illustrated in Figures 2, Typical Connection Diagram, and 3.1, Transformer Coupled Input. To minimize distortion, the core of the transformer must not saturate at full scale input voltage levels. To minimize kickback noise from the internal sample-hold a small capacitor should be connected across the VIN pins (pins 20 and 21).

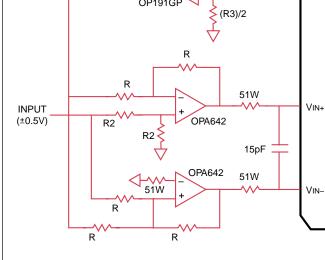

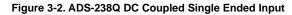

Figure 3.2, DC Coupled Single Ended Input, illustrates a conversion circuit for a DC coupled single-ended input. Power supplies and by-pass capacitors are not shown.

#### **Reference Voltage Inputs**

The ADS-238Q is designed to accept two external reference voltages at the VREF input pins, see Figure 2, Typical Connection Diagram. These reference voltages, applied to VREF+ (pin 11) and VREF– (pin 10), determine the analog input voltage range, which is equal to  $\pm$ (VREF+ - VREF–). This voltage range will be symmetric about the common mode voltage, and for best performance should be symmetrical about the midpoint of the supply voltage.

In order to minimize overall converter noise it is recommended that the VREF pins be adequately bypassed using a 4.7 $\mu$ F tantalum capacitor in parallel with a 0.01 $\mu$ F ceramic capacitor. Locate the bypass capacitors as close to the unit as possible.

OP191GP

R3

R3

Vсм

Figure 3-1. ADS-238Q Transformer Coupled Input

Common Mode Voltage Reference

The ADS-238Q has an internal common mode reference voltage, V<sub>CM</sub> (pin 18). This reference voltage is typically one half of the supply voltage and is capable of driving loads up to 20 $\mu$ A. This reference is used to drive the center tap in the transformer used in fully differential applications, or provide level shifting in single-ended to differential applications.

Table 1. Sample Rate Bias Current Settings

| SAMPLE RATE<br>(MHz) | BIAS1<br>(μΑ) | BIAS2<br>(μΑ) |

|----------------------|---------------|---------------|

| 1                    | 20            | 3.5           |

| 5                    | 50            | 6.5           |

| 10                   | 80            | 8.0           |

| 20                   | 90            | 9.5           |

**Bias Current Inputs**

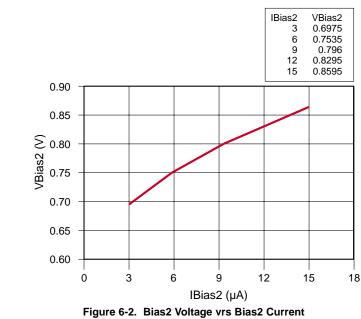

The bias currents shown in Table I, Sample Rate Bias Current Settings, and Figure 4, Suggested Bias Currents vrs Sample Rate, are designed to optimize performance of the ADS-238Q for a given sample rate.

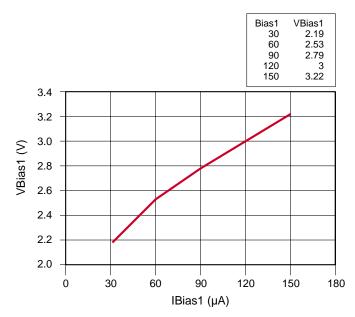

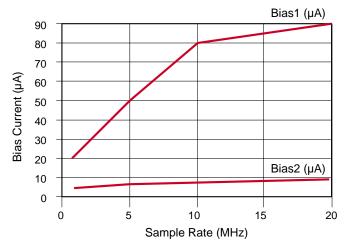

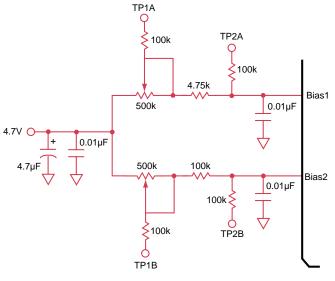

Figure 5, Bias Current Determination and Adjustment, details the suggested circuits for measuring bias voltage drops to calculate the bias currents. Adjustments to the bias currents are made via the trim pots. The Bias1 voltage drop is measured across TP1A and TP1B. The Bias2 voltage drop is measured across TP2A and TP2B. Figures 6-1 and 6-2 show the relationship between the bias currents and voltages when measured in the indicated circuit. The Bias1 and Bias2 pins should be by-passed with  $0.01\mu$ F capacitors.

Figure 4. Suggested Bias Current vrs Sample Rate

Figure 5. Bias Current Determination and Adjustment

#### Clock

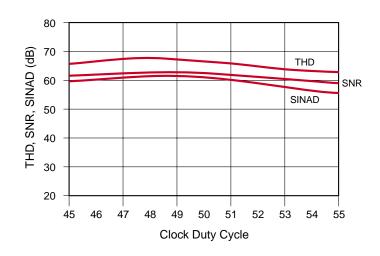

The ADS-238Q accepts a low voltage CMOS logic level at the clock input (CLK, pin 2). The clock duty cycle must be held to within 50% +/-3% because consecutive stages of the A-to-D are clocked in opposite phase. A duty cycle other than this will reduce the settling time available for every other stage, there by degrading dynamic performance.

For optimum performance at high input frequencies the clock must have low jitter, and rise/fall times less than 2ns. Over/undershoot should be avoided. Clock jitter causes the noise floor to increase proportional to the input frequency. To reduce crosstalk, and hence jitter, clock traces on the PC board should be kept as short as possible with transmission line practices employed.

#### **Digital Outputs**

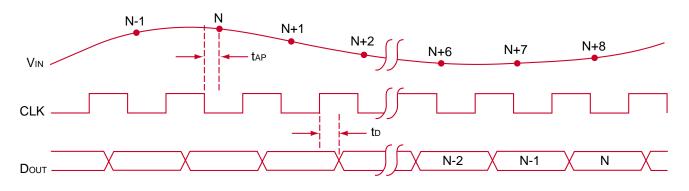

The digital output data is provided in offset binary format, at 3.3V CMOS logic levels, and is available 7.5 clock cycles after the data is sampled. The output data is invalid for the first 20 clock cycles when the ADS-238Q is first powered up.

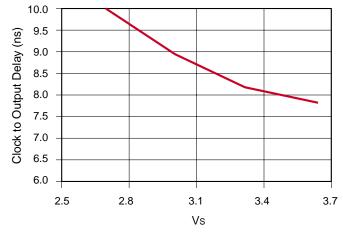

The clock to output delay is typically 8ns, but will change as a function of the supply voltage, Vs. Figure 7, Clock to Output Delay vrs Vs, shows this relationship.

A negative full scale input results in an all zeros output code (0000 0000 0000). A positive full scale input results in an all ones output code (1111 1111 1111).

The input is sampled during the high-to-low transition of the input clock. Output data should be latched during the low-to-high clock transition as shown in Figure 8, Timing Diagram.

Figure 7. Clock to Output Delay vrs Vs

Power Supplies and Grounding

The ADS-238Q is powered from a single 3.3V supply. The converters should be mounted on a board that provides separate low impedance paths for the analog and digital supplies and grounds. For best performance the 3.3V supply should be clean, and linearly regulated. The power supply should be bypassed to ground with a 10 $\mu$ F tantalum capacitor in parallel with a 0.01 $\mu$ F ceramic capacitor. Locate the bypass capacitors as close to the converter as possible. Analog and digital grounds should be isolated with a ferrite bead. See the Typical Connection Diagram, Figure 2.

Figure 8. ADS-238Q Timing Diagram

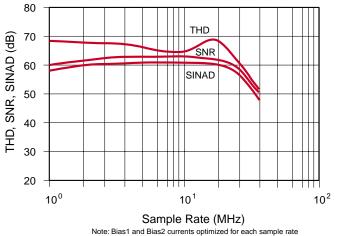

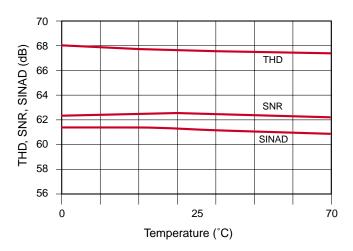

# **TYPICAL PERFORMANCE CHARATERISTICS**

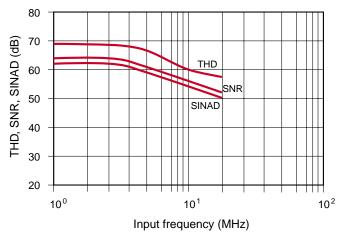

Figure 9-1. THD, SNR, SINAD vrs Input Frequency

Figure 9-2. THD, SNR, SINAD vrs Sample Rate

Figure 9-3. THD, SNR, SINAD vrs Temperature

Figure 9-4. THD, SNR, SINAD vrs Clock Duty Cycle

Figure 9-5. Power Dissipation vrs Sample Rate

#### MECHANICAL DIMENSIONS INCHES (mm)

|        | Inches     |       | Millmeters |       |

|--------|------------|-------|------------|-------|

| Symbol | Min.       | Max.  | Min.       | Max.  |

| Α      | 0.472 Typ. |       | 12.00 Typ. |       |

| В      | 0.394 Typ. |       | 10.00 Typ. |       |

| С      | 0.394 Typ. |       | 10.00 Typ. |       |

| D      | 0.472 Typ. |       | 12.00 Typ. |       |

| E      | 0.031 Typ. |       | 0.80 Typ.  |       |

| F      | 0.012      | 0.018 | 0.300      | 0.45  |

| G      | 0.053      | 0.057 | 1.35       | 1.45  |

| н      | 0.002      | 0.006 | 0.05       | 0.15  |

| I      | 0.018      | 0.030 | 0.450      | 0.750 |

| J      | 0.039 Typ. |       | 1.00 Typ.  |       |

| K      | 0-7°       |       | 0-70       |       |

#### **ORDERING INFORMATION**

| MODEL    | OPERATING TEMP. RANGE | PACKAGE             |

|----------|-----------------------|---------------------|

| ADS-238Q | 0 to +70 °C           | 44-PIN PLASTIC TQFP |

DS-0445 11/99

DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1151 Tel: (508) 339-3000 (800) 233-2765 Fax: (508) 339-6356 Internet: www.datel.com E-mail:sales@datel.com Data Sheet Fax Back: (508) 261-2857 DATEL (UK) LTD. Tadley, England Tel: (01256)-880444 DATEL S.A.R.L. Montigny Le Bretonneux, France Tel: 1-34-60-01-01 DATEL GmbH München, Germany Tel: 89-544334-0 DATEL KK Tokyo, Japan Tel: 3-3779-1031, Osaka Tel: 6-354-2025

DATEL makes no representation that the use of its products in the circuits described herein, or the use of other technical information contained herein, will not infringe upon existing or future patent rights. The descriptions contained herein do not imply the granting of licenses to make, use, or sell equipment constructed in accordance therewith. Specifications are subject to change without notice. The DATEL logo is a registered DATEL, Inc. trademark.