# **ADS-235, ADS-236, ADS-237**

# 12-Bit, 5MHz and 9MHz Sampling A/D Converters

#### **FEATURES**

- 5MHz (ADS-235/236) and 9MHz (ADS-237) sampling rates

- Low power

- · Outstanding dynamic performance

- · Fully differential or single-ended analog input

- · 100MHz full power input bandwidth

- · Integral sample-and-hold

- Single +5V supply operation

- · Internally generated DC bias Voltage

- 3.0/5.0V CMOS compatible digital output

- TTL/CMOS compatible digital inputs/outputs

#### **GENERAL DESCRIPTION**

The ADS-235, ADS-236 and ADS-237 are monolithic, 12-bit, sampling analog-to-digital converters fabricated in a CMOS process. The converters are designed for applications where high speed, wide bandwidth and low power dissipation are essential. These characteristics are provided through the use of a fully differential sampling pipeline A/D architecture with digital error correction logic.

The ADS-235, ADS-236 and ADS-237 offer excellent dynamic performance while consuming only 300mW. The digital output circuit is separate and can be powered from either a 3V or 5V supply allowing the user to interface with 3V logic, if desired.

The ADS-235, ADS-236 and ADS-237 provide the user with an internally generated DC bias voltage output. This DC bias voltage is ideal for AC coupled analog input applications. The units are available in a 28-lead plastic SOIC package and operate over the 0°C to 70°C and -40 to +85°C temperature ranges.

#### INPUT/OUTPUT CONNECTIONS

| PIN | FUNCTION              | PIN | FUNCTION                |

|-----|-----------------------|-----|-------------------------|

| 1   | CLK, CLOCK            | 28  | BIT 12                  |

| 2   | +DVs1, +5V DIG. SUP.  | 27  | BIT 11                  |

| 3   | DGND1                 | 26  | BIT 10                  |

| 4   | +DVs1, +5V DIG. SUP.  | 25  | BIT 9                   |

| 5   | DGND1                 | 24  | BIT 8                   |

| 6   | +AVs, +5V ANALOG SUP. | 23  | BIT 7                   |

| 7   | AGND                  | 22  | +DVs2, DIG. OUTPUT SUP. |

| 8   | VIN+, ANALOG INPUT    | 21  | DGND2                   |

| 9   | VIN-, ANALOG INPUT    | 20  | BIT 6                   |

| 10  | VDC, DC BIAS OUTPUT   | 19  | BIT 5                   |

| 11  | VROUT, REF. OUT       | 18  | BIT 4                   |

| 12  | VRIN, REF. IN         | 17  | BIT 3                   |

| 13  | AGND                  | 16  | BIT 2                   |

| 14  | +AVs, +5V ANALOG SUP. | 15  | BIT 1 (MSB)             |

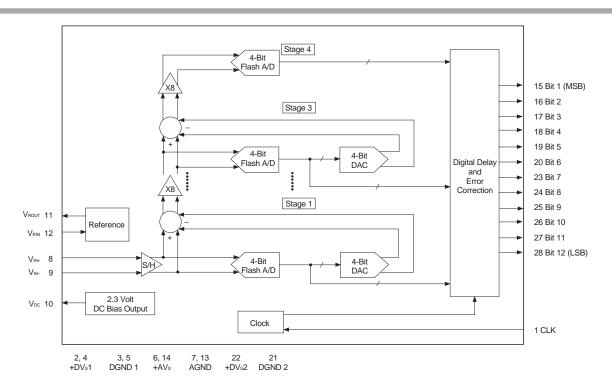

Figure 1. ADS-235, ADS-236 and ADS-237 Functional Block Diagram

# **ABSOLUTE MAXIMUM RATINGS**

| PARAMETERS                                                                            | LIMITS                                                      | UNITS                            |  |

|---------------------------------------------------------------------------------------|-------------------------------------------------------------|----------------------------------|--|

| +AVs, +DVs1 and +DVs2 Supplies<br>DGND to AGND<br>Analog I/O Pins<br>Digital I/O Pins | +6.0<br>0.3<br>AGND to +AV's Supply<br>DGND to +DV's Supply | Volts<br>Volts<br>Volts<br>Volts |  |

| Lead Temperature<br>(10 seconds, Pin Tips Only)                                       | 300                                                         | °C                               |  |

# PHYSICAL/ENVIRONMENTAL

| PARAMETERS                                  | MIN.       | TYP.      | MAX.       | UNITS |

|---------------------------------------------|------------|-----------|------------|-------|

| Operating Temperature Range<br>ADS-235S     | 0          | _         | 70         | °C    |

| ADS-236S/ADS-237S Storage Temperature Range | -40<br>-65 | _         | 85<br>150  | °C    |

| Thermal Resistance, θja ①                   | _          | 75        |            | °C/W  |

| Junction Temperature                        | _          | _         | 150        | °C    |

| Package Type                                |            | 28-Pin Pl | astic SOIC |       |

① Measured mounted on PC board in free air.

# **FUNCTIONAL SPECIFICATIONS**

$(T_A = +25^{\circ}C, (ADS-235), TMIN to TMAX (ADS-236/237), +DVs1 = +DVs2 = +AVs = +5V, VRIN = 3.5V, Fs = 5MHz (ADS-235/236) and 9MHz (ADS-237) at a 50% duty cycle, CL =10pF, and differential analog input unless otherwise specified.)$

| ANALOG INPUTS                                                                                                 | MIN.             | TYP.               | MAX.               | UNITS                              |

|---------------------------------------------------------------------------------------------------------------|------------------|--------------------|--------------------|------------------------------------|

| Max. Peak-to-Peak Diff. Voltage Input Range (VIN+ - VIN-) Max. Peak-to-Peak Single-Ended                      | _                | ±2.0               | _                  | Volts                              |

| Voltage Input Range Analog Input Common Mode                                                                  | _                | 4.0                | _                  | Volts                              |

| Voltage Range (VIN+ + VIN-)/2 ① Input Bias Current, IB+ or IB- ② Differential Input                           | 1.0<br>-10       | 2.3<br>—           | 4.0<br>10          | Volts<br>µA                        |

| Current, (IB+ - IB-) Input Impedance ② Input Capacitance                                                      | 1.0<br>—         | ±0.5<br>—<br>10    | _<br>_             | μA<br>MΩ<br>pF                     |

| INTERNAL VOLTAGE REFEREN                                                                                      | CE               | ı                  |                    |                                    |

| Reference Output Voltage, VROUT<br>Reference Output Current<br>Reference Temperature Coefficient              | _<br>_           | 3.5                | <u>_</u>           | Volts<br>mA                        |

| ADS-235 ® ADS-236 ADS-237                                                                                     |                  |                    | _<br>_<br>_        | ppm/°C<br>ppm/°C<br>ppm/°C         |

| REFERENCE VOLTAGE INPUT                                                                                       |                  |                    |                    |                                    |

| Reference Voltage Input, VRIN<br>Total Reference Resistance, RL<br>Reference Current                          | _<br>_<br>_      | 3.5<br>7.8<br>450  | _<br>_<br>_        | Volts<br>kΩ<br>μA                  |

| PERFORMANCE                                                                                                   |                  |                    |                    |                                    |

| Resolution                                                                                                    | 12               | _                  | _                  | Bits                               |

| Maximum Sample Rate, FCLK ADS-235 ADS-236 ADS-237 Minimum Sample Rate                                         | 5<br>9           | 5<br>—<br>—<br>0.5 | _<br>_<br>_<br>_   | MHz<br>MHz<br>MHz<br>MHz           |

| Integral Nonlinearity, FIN=DC ADS-235 ADS-236, ADS-237 Differential Nonlinearity,                             | _<br>_           | ±2.0<br>±1.0       | <br>±2.0           | LSB<br>LSB                         |

| FIN=DC ④ Input Offset Error, FIN=DC                                                                           | _                | ±0.5               | ±1.0               | LSB                                |

| ADS-235<br>ADS-236, ADS-237<br>Full Scale Error, Fin=DC                                                       | _                | 12<br>19           | _<br>_             | LSB<br>LSB                         |

| ADS-235<br>ADS-236, ADS-237<br>Aperture Delay, tap<br>Aperture Uncertainty, taJ<br>Full Power Input Bandwidth | _<br>_<br>_<br>_ | 24<br>32<br>5<br>5 |                    | LSB<br>LSB<br>ns<br>ps(RMS)<br>MHz |

| Spurious Free Dynamic Range,<br>SFDR, Fin=1MHz<br>ADS-235<br>ADS-236<br>ADS-237                               | _<br>_<br>_      | 73<br>83<br>77     | _<br>_<br>_        | dB<br>dB<br>dB                     |

| Total Harmonic Distortion,<br>THD, FIN=1MHz<br>ADS-235<br>ADS-236<br>ADS-237                                  | _<br>_<br>_      | -70<br>-80<br>-75  | <br> -<br> -<br> - | dB<br>dB<br>dB                     |

| PERFORMANCE (cont.)                                                                                                                                     | MIN.                  | TYP.               | MAX.             | UNITS                      |

|---------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|--------------------|------------------|----------------------------|

| Second Harmonic, FIN=1MHz<br>ADS-235<br>ADS-236<br>ADS-237                                                                                              | _<br>_<br>_           | -73<br>-86<br>-80  | _<br>_<br>_      | dB<br>dB<br>dB             |

| Third Harmonic, Fin=1MHz ADS-235 ADS-236 ADS-237 Effective Number Of Bits,                                                                              | _<br>_<br>_           | -73<br>-83<br>-77  | _<br>_<br>_      | dB<br>dB<br>dB             |

| ENOB, FIN=1MHz ADS-235 ADS-236 ADS-237 Signal to Noise Ratio and                                                                                        | _<br>_<br>_<br>_      | 10.3<br>11<br>10.8 | _<br>_<br>_      | Bits<br>Bits<br>Bits       |

| Distortion, SINAD, FIN=1MHz ADS-235 ADS-236 ADS-237 Signal to Noise Ratio,                                                                              | _<br>_<br>_<br>_      | 64<br>68<br>66.5   | _<br>_<br>_      | dB<br>dB<br>dB             |

| SNR, Fin=1MHz ADS-235 ADS-236 ADS-237 Intermodulation Distortion,                                                                                       | _<br>_<br>_<br>_      | 65<br>68<br>67.3   | _<br>_<br>_<br>_ | dB<br>dB<br>dB             |

| IMD, F1=1MHz F2=1.02MHz ADS-235 ADS-236 ADS-237 Transient Response ® Over-Voltage Recovery,                                                             | _<br>_<br>_<br>_      | -66<br>-68<br>-65  | _<br>_<br>_<br>_ | dB<br>dB<br>dB<br>Cycle    |

| 0.2V Overdrive                                                                                                                                          | _                     | 2                  | _                | Cycle                      |

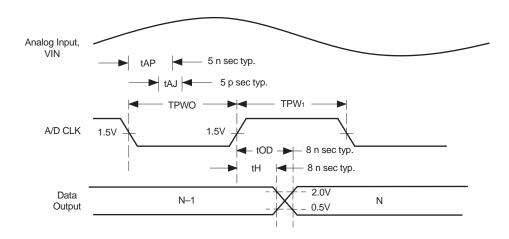

| Data Output Hold, th Data Output Delay, top                                                                                                             |                       | 8 8                |                  | ns<br>ns                   |

| Clock Pulse Width, TPWO, TPW1<br>ADS-235, ADS-236<br>ADS-237<br>Data Latency, tLAT                                                                      | 90<br>106<br>—        | 100<br>111<br>—    | 110<br>116<br>3  | ns<br>ns<br>Cycles         |

| DC BIAS VOLTAGE OUTPUT                                                                                                                                  | I                     |                    |                  |                            |

| DC Bias Voltage Output,VDC<br>DC Bias Voltage Current                                                                                                   | _                     | 2.3                | _<br>1.0         | volts<br>mA                |

| DIGITAL OUTPUTS                                                                                                                                         |                       |                    |                  |                            |

| Logic Levels Logic "1", +DVs2=5V, VoH=2.4V Logic "0", +DVs2=5V, VoL=0.4V Logic "1", +DVs2=3V, VoH=2.4V Logic "0", +DVs2=3V, VoL=0.4V Output Capacitance | -0.2<br>1.6<br>—<br>— |                    | _<br>_<br>_<br>_ | mA<br>mA<br>mA<br>mA<br>pF |

| POWER REQUIREMENTS              | MIN.  | TYP. | MAX.  | UNITS |

|---------------------------------|-------|------|-------|-------|

| Power Supply Ranges             |       |      |       |       |

| +5V Analog Supply, +AVs         | +4.75 | 5    | +5.25 | Volts |

| +5V Digital Supply, +DVs1       | +4.75 | 5    | +5.25 | Volts |

| +3V Digital Supply, +DVs2       | +2.7  | 3    | +3.3  | Volts |

| +5V Digital Supply, +DVs2       | +4.75 | 5    | +5.25 | Volts |

| Power Supply Currents           |       |      |       |       |

| ADS-235, ADS-236                |       |      |       |       |

| +Als                            | _     | 46   | _     | mA    |

| +DIs1                           | _     | 13   | _     | mA    |

| +DIs2                           | _     | 1    | _     | mA    |

| ADS-237                         |       |      |       |       |

| +Als                            | _     | 46   | _     | mA    |

| +DIs1                           | _     | 17   | _     | mA    |

| +DIs2                           | _     | 2    | _     | mA    |

| Power Dissipation               |       |      |       |       |

| ADS-235                         | _     | 300  | _     | mW    |

| ADS-236                         | _     | 300  | 350   | mW    |

| ADS-237                         | _     | 325  | 365   | mW    |

| Offset Error Sensitivity, 5V±5% |       |      |       |       |

| ADS-235                         | _     | ±16  | _     | LSB   |

| ADS-236, ADS-237                | -     | 2    | -     | LSB   |

| Gain Error Sensitivity, 5V±5%   |       |      |       |       |

| ADS-235                         | -     | ±16  | _     | LSB   |

| ADS-236, ADS-237                | -     | 30   | –     | LSB   |

- Footnotes: ① Differential Mode

- @ CLK off and Low

- 3 Not specified

- 4 No missing codes

- ⑤ For Fs step to settle to 12-bits accuracy

#### **FUNCTIONAL DESCRIPTION**

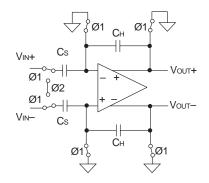

The ADS-235, ADS-236 and ADS-237 are 12-bit fully differential pipeline sampling A/D converters with digital error correction. Referring to the Functional Block Diagram shown in figure 1, figure 3.1 shows the circuit for the front end differential in and out sample-and-hold (S/H). The switches are controlled by an internal sampling clock which is a non-overlapping two phase signal, Ø1 and Ø2, derived from the master sampling clock. During the sampling phase, Ø1, the input signal is

applied to the sampling capacitors, Cs. At the same time the hold capacitors, CH, are discharged to analog ground. At the falling edge of Ø1 the input signal is sampled on the bottom plates of the sampling capacitors. In the next clock phase, Ø2, the two bottom plates of the sampling capacitors are connected together and the holding capacitors are switched to the op-amp output nodes. The charge then redistributes between Cs and CH completing one sample and hold cycle.

The sample and hold output is a fully differential representation of the sampled analog input. The circuit not only performs the sample-hold function but will also convert a single-ended input to a fully differential output. During the sampling phase, the VIN pins see only the on resistance of a switch and Cs. The small values of these components result in a typical full power input bandwidth of 100MHz for the converters.

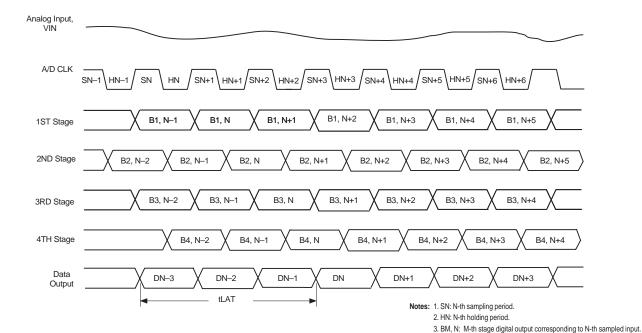

As illustrated in the Functional Block Diagram, figure 1, and the Internal Timing Diagram, figure 2A, three identical pipeline sub-converter stages, each containing a four-bit flash converter and a four-bit multiplying digital-to-analog converter, follow the S/H with the fourth stage being a four-bit flash converter. Each converter stage in the pipeline will be sampling in one clock phase and amplifying in the other clock phase. Each subconverter clock signal is offset by 180 degrees from the previous stage clock signal resulting in alternate stages in the pipeline performing the same operation.

The four-bit output of each of the sub-converter stages is used by the error correction logic. The output of each stage is input to a digital delay line which is controlled by the internal sampling clock. The function of the delay line is to align the digital outputs in time of the three identical stages with the output of the fourth stage flash converter before applying the sixteen bit result to the error correction logic. The error correction logic uses the supplementary bits to correct any error that may exist before generating the final twelve-bit digital data output.

Due to the pipeline nature of this converter, the digital data representing an analog input sample is output to the digital

4. DN: Final data output corresponding to N-th sampled input.

Figure 2A. Internal Timing Diagram

data bus on the third cycle of the clock after the analog sample is taken. After this latency delay, the digital data representing each successive sample of the analog input is output during the following clock cycle. The digital output data is synchronized to the external sampling clock through a double buffered latching circuit. The output of the digital error correction circuit is available in offset binary format.

## **Differential Analog Input**

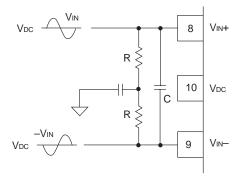

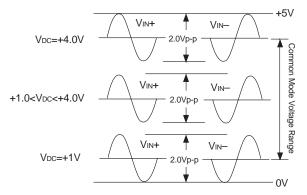

The analog input is a differential input that can be configured in various ways depending on the signal source and the level of performance desired. A fully differential connection as shown in figures 3.2 and 3.3 will give the best performance.

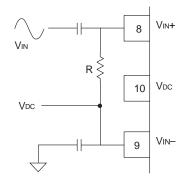

The ADS-235, ADS-236 and ADS-237 are powered by a single +5V analog power supply which limits the analog input to between ground and +5V. For the differential input connection this implies that the analog input common mode voltage can range from 1.0V to 4.0V, see figure 3.6. Performance for the converter does not change significantly with the value of the analog input common mode voltage. A DC voltage source, VDC, equal to 2.3V, typical, is provided to help simplify circuit design when using an AC coupled differential input. This low impedance voltage source is not designed to be a reference voltage but makes an excellent DC bias source. This bias voltage source stays well within the analog input common mode voltage range over temperature.

The difference between the converter's two internal reference voltages is 2V. For the AC coupled differential input, figure 3.2, if Vin is a 2Vp-p sinewave with -Vin 180 degrees out of phase with Vin, then Vin+ is a 2Vp-p sinewave riding on a DC bias voltage equal to Vdc. Consequently, the converter will be at a positive full scale when the Vin+ input is at Vdc+1V and the Vin- input is at Vdc-1V (Vin+ - Vin- = 2V). Conversely, the ADS will be at negative full scale when the Vin+ input is equal to Vdc-1V and Vin- is at Vdc+1V (Vin+ - Vin- = -2V). Thus, the converter has a peak-to-peak differential analog input voltage range of  $\pm$ 2V.

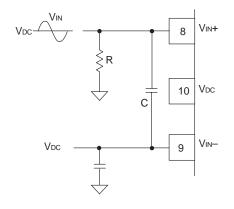

The analog input can be DC coupled, figure 3.3, as long as the inputs are within the analog input common mode voltage range (1.0V  $\leq$  VDC  $\leq$  4.0V). The resistors, R, are not absolutely necessary but may be used as load setting resistors. A capacitor, C, connected from VIN+ to VIN- will help filter high frequency noise. Values of approximately 20pF are normally

sufficient but the actual value must take into account the highest frequency component of the input signal.

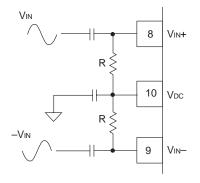

### **Single-Ended Analog Input**

The circuit in figure 3.4 may be used with a single-ended AC coupled input. Assuming again that the difference between the two internal voltage references is 2V and VIN is a 4Vp-p sinewave, then VIN+ is a 4Vp-p sinewave riding on a positive voltage equal to VDC. The converter will be at a positive full scale when VIN+ is at VDC+2V (VIN+ - VIN- = 2V) and will be equal to a negative full scale when VIN+ is equal to VDC-2V (VIN+ - VIN- = -2V). In this case, VDC could range between 2V and 3V without significant change in the converters performance. The simplest way to obtain a VDC voltage is to use the VDC output provided by the converters.

The single-ended analog input can be DC coupled, as shown figure 3.5, as long as the input is within the analog input common mode voltage range. The resistor, R, shown is not absolutely necessary but may be used as a load setting resistor. A capacitor, C, connected between V<sub>IN+</sub> and V<sub>IN-</sub> will help filter high frequency noise. A value of approximately 20pF is normally sufficient but the actual value must take into account the highest frequency component of the input signal.

#### INTERNAL REFERENCE GENERATOR, VROUT VRIN

The ADS-235/236/237 have an internal reference generator, therefore, an external voltage is not required. VROUT must be connected to VRIN when using the internal reference voltage. Two reference voltages are generated internally, 1.3V and 3.3V, for a fully differential input range of ±2V.

An external reference may be used by connecting the external voltage reference to the VRIN pin with VROUT left open. These units are tested with VRIN equal to 3.5V.

In order to minimize overall converter noise it is recommended that adequate high frequency decoupling be provided at the  $V_{\text{RIN}}$  pin.

#### Digital I/O and Clock

The ADS-235, ADS-236 and ADS-237 provide a standard high-speed interface to external TTL/CMOS logic families. In order to ensure rated performance the duty cycle of the clock should be held at 50% ±5%, have low jitter and operate at standard TTL levels. Performance is guaranteed for conversion

Figure 2B. Input-to-Output Timing

rates above 0.5MHz in order to ensure proper performance of the internal dynamic circuits.

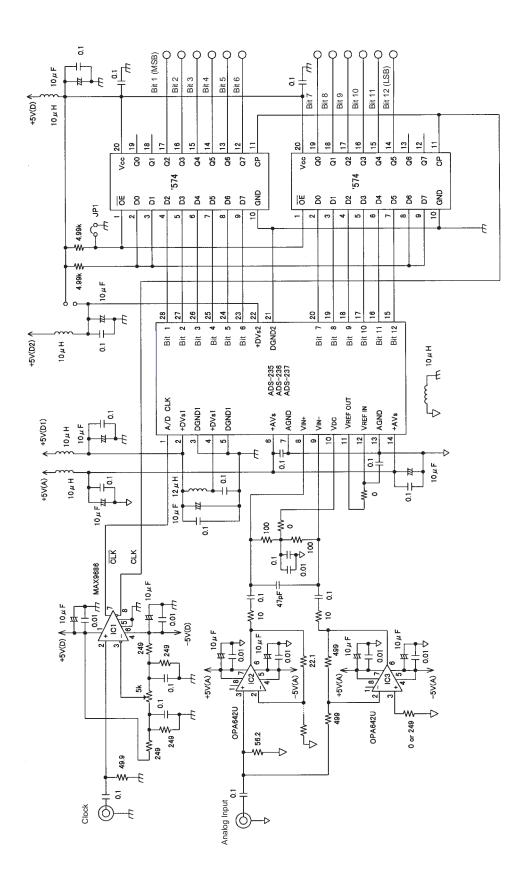

### **Power Supplies and Grounding**

The ADS-235, ADS-236 and ADS-237 have separate digital and analog power supply pins and grounds (refer to the Input/Output Connections table for pin numbers) to reduce digital noise in the analog signal path. The digital data outputs also have a separate supply pin, +DVs2, which can be powered from either a 3.0V or 5.0V supply to allow the user the option of interfacing with 3.0V logic.

The converters should be mounted on a board that provides separate low impedance paths for the analog and digital

supplies and grounds. For best performance the supplies used should be clean, linear regulated supplies. All power supplies should be bypassed to ground with a 10uF tantalum capacitor in parallel with a 0.1uF ceramic capacitor. Locate the bypass capacitors as close to the converter as possible. If the converter is to be powered from one supply then the analog supply and ground pins should be isolated with ferrite beads from the digital supply and ground pins. See the Typical Connection Diagram, Figure 4.

In order to minimize overall converter noise it is recommended that the VRIN pin be bypassed using a 4.7 uF tantalum capacitor in parallel with a 0.01 uF ceramic capacitor. Locate the bypass capacitors as close to the unit as possible.

Figure 3.1 Analog Input Sample-and-Hold

Figure 3.3 DC Coupled Differential Input

Figure 3.5 DC Coupled Single Ended Input

Figure 3.2 AC Coupled Differential Input

Figure 3.4 AC Coupled Single Ended Input

Figure 3.6 Differential Analog Input Common Mode Voltage Range

Figure 3. Analog Input

Figure 4. Typical Connection diagram

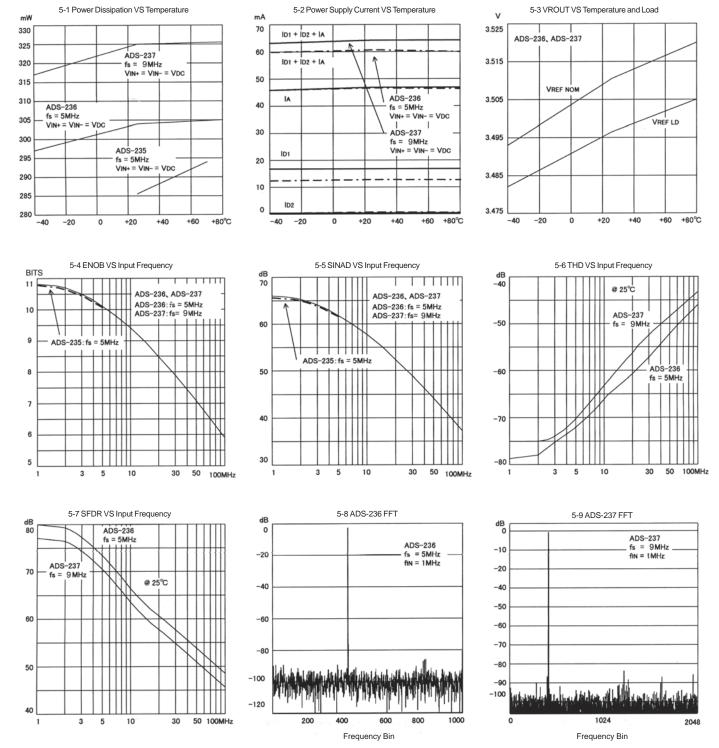

BITS

Figure 5. Typical Performance Curve

Table 1. Output Coding

|                                                                                                           | DIFFERENTIAL                                                             | OFFSET<br>BINARY                             |                                              |                                              |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|----------------------------------------------|----------------------------------------------|----------------------------------------------|

| BIPOLAR<br>SCALE                                                                                          | INPUT VOLTAGE<br>(using internal<br>reference)                           | MS                                           | В                                            | LSB                                          |

| +FS-1/4LSB<br>+FS-1 <sup>1</sup> /4LSB<br>+3/4 LSB<br>-1/4 LSB<br>-FS+1 <sup>3</sup> /4LSB<br>-FS+3/4 LSB | +1.99976V<br>+1.99878V<br>+732.4µV<br>-244.1µV<br>-1.99829V<br>-1.99927V | 1111<br>1111<br>1000<br>0111<br>0000<br>0000 | 1111<br>1111<br>0000<br>1111<br>0000<br>0000 | 1111<br>1110<br>0000<br>1111<br>0001<br>0000 |

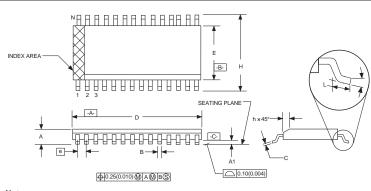

#### **MECHANICAL DIMENSIONS** INCHES (mm)

#### Notes:

- 1. Controlling dimensions: MILLIMETER. Converted inch dimensions

- are not necessarily exact.

2. Dimension "D" does not include mold flash, protrusions or gate burrs. Mold flash, protrusions and gate burrs shall not exceed 0.15mm (0.006 inch) per side

- 3. Dimension "E" does not include interlead flash or protrusions. Interlead flash and protrusions shall not exceed 0.25mm (0.010 inch) per side.

- The chamfer on the body is optional. If it is not present, a visual index feature must be located within the crosshatched area.

- "L" is the length of terminal for soldering to a substrate.

- Terminal numbers are shown for reference only.

The lead width "B", as measured 0.36mm (0.014 inch) or greater above the seating plane, shall not exceed a maximum value of 0.61mm (0.024 inch).

# **ADS-235S ADS-236S ADS-237S** 28 Lead Wide Body Versions SMALL OUTLINE PLASTIC PACKAGES (SOIC)

|        | INCHES |        | MILLI    | METERS |

|--------|--------|--------|----------|--------|

| SYMBOL | MIN.   | MAX.   | MIN.     | MAX.   |

| Α      | 0.0926 | 0.1043 | 2.35     | 2.65   |

| A1     | 0.0040 | 0.0118 | 0.10     | 0.30   |

| В      | 0.013  | 0.0200 | 0.33     | 0.51   |

| С      | 0.0091 | 0.0125 | 0.23     | 0.32   |

| D      | 0.6969 | 0.7125 | 17.70    | 18.10  |

| E      | 0.2914 | 0.2992 | 7.40     | 7.60   |

| е      | 0.0    | 5 BSC  | 1.27 BSC |        |

| Н      | 0.394  | 0.419  | 10.00    | 10.65  |

| h      | 0.01   | 0.029  | 0.25     | 0.75   |

| L      | 0.016  | 0.050  | 0.40     | 1.27   |

| N      | 28     |        | 2        | 28     |

| α      | 0°     | 8°     | 0°       | 8°     |

### ORDERING INFORMATION

| MODEL NUMBER | OPERATING<br>TEMP. RANGE | SAMPLING<br>FREQUENCY |

|--------------|--------------------------|-----------------------|

| ADS-235S     | 0 to +70°C               | 5MHz                  |

| ADS-236S     | -45 to +85°C             | 5MHz                  |

| ADS-237S     | -45 to +85°C             | 9MHz                  |

|              |                          |                       |

DS-0409A

05/01

DATEL, Inc. 11 Cabot Boulevard, Mansfield, MA 02048-1151 Tel: (508) 339-3000 (800) 233-2765 Fax: (508) 339-6356 Internet: www.datel.com Email: sales@datel.com

DATEL (UK) LTD. Tadley, England Tel: (01256)-880444 DATEL S.A.R.L. Montigny Le Bretonneux, France Tel: 01-34-60-01-01 DATEL GmbH München, Germany Tel: 89-544334-0 DATEL KK Tokyo, Japan Tel: 3-3779-1031, Osaka Tel: 6-6354-2025