## **General Description**

The MAX2009 adjustable RF predistorter is designed to improve power amplifier (PA) adjacent-channel power rejection (ACPR) by introducing gain and phase expansion in a PA chain to compensate for the PA's gain and phase compression. With its +23dBm maximum input power level and wide adjustable range, the MAX2009 can provide up to 12dB of ACPR improvement for power amplifiers operating in the 1200MHz to 2500MHz frequency band. Lower frequencies of operation can be achieved with this IC's counterpart, the MAX2010.

The MAX2009 is unique in that it provides up to 7dB of gain expansion and 24° of phase expansion as the input power is increased. The amount of expansion is configurable through two independent sets of control: one set adjusts the gain expansion breakpoint and slope, while the second set controls the same parameters for phase. With these settings in place, the linearization circuit can be run in either a static set-andforget mode, or a more sophisticated closed-loop implementation can be employed with real-time software-controlled distortion correction. Hybrid correction modes are also possible using simple lookup tables to compensate for factors such as PA temperature drift or PA loading.

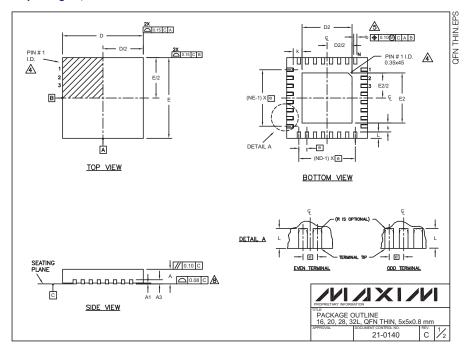

The MAX2009 comes in a 28-pin thin QFN exposed pad (EP) package (5mm x 5mm) and is specified for the extended (-40°C to +85°C) temperature range.

## **Applications**

WCDMA/UMTS, cdma2000, DCS1800, and PCS1900 Base Stations

Feed-Forward PA Architectures

Digital Baseband Predistortion Architectures

Military Applications

**WLAN Applications**

### Features

- ♦ Up to 12dB ACPR Improvement\*

- ♦ Independent Gain and Phase Expansion Controls

- ♦ Gain Expansion Up to 7dB

- ♦ Phase Expansion Up to 24°

- ♦ 1200MHz to 2500MHz Frequency Range

- ♦ Exceptional Gain and Phase Flatness

- ♦ Group Delay <1.3ns (Gain and Phase Sections Combined)

- ♦ ±0.04ns Group Delay Ripple Over a 100MHz Band

- ♦ Capable of Handling Input Drives Up to +23dBm

- ♦ On-Chip Temperature Variation Compensation

- ♦ Single +5V Supply

- **♦** Low Power Consumption: 75mW (typ)

- ♦ Fully Integrated into Small 28-Pin Thin QFN **Package**

## **Ordering Information**

| PART         | TEMP RANGE     | PIN-PACKAGE     |  |  |

|--------------|----------------|-----------------|--|--|

| MAX2009ETI-T | -40°C to +85°C | 28 Thin QFN-EP* |  |  |

<sup>\*</sup>EP = Exposed paddle.

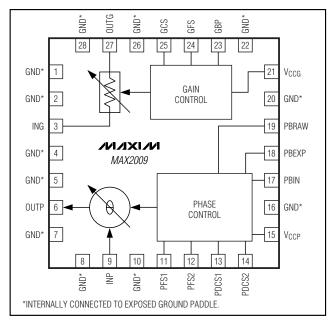

## Functional Diagram/ Pin Configuration

MIXIM

Maxim Integrated Products 1

For pricing, delivery, and ordering information, please contact Maxim/Dallas Direct! at 1-888-629-4642, or visit Maxim's website at www.maxim-ic.com.

<sup>\*</sup>Performance dependent on amplifier, bias, and modulation.

### **ABSOLUTE MAXIMUM RATINGS**

| VCCG, VCCP to GND                    | 0.3V to +5.5V                     |

|--------------------------------------|-----------------------------------|

| ING, OUTG, GCS, GFS, GBP to GND.     | 0.3V to (V <sub>CCG</sub> + 0.3V) |

| INP, OUTP, PFS_, PDCS_, PBRAW,       | , , , , ,                         |

| PBEXP, PBIN to GND                   | 0.3V to (VCCP + 0.3V)             |

| Input (ING, INP, OUTP, OUTG) Level . | +23dBm                            |

| PREXP Output Current                 |                                   |

| Continuous Power Dissipation ( $T_A = +70$ | l°C)          |

|--------------------------------------------|---------------|

| 28-Pin Thin QFN-EP                         |               |

| (derate 21mW/°C above +70°C)               | 1667mW        |

| Operating Temperature Range                | 40°C to +85°C |

| Junction Temperature                       | +150°C        |

| Storage Temperature Range                  |               |

| Lead Temperature (soldering 10s)           | +300°C        |

|                                            |               |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

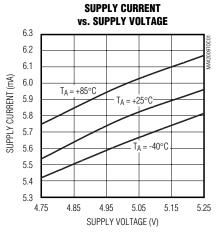

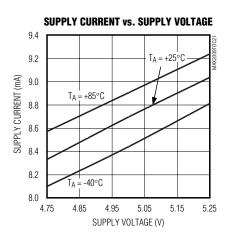

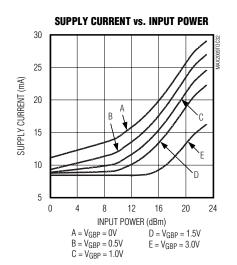

### DC ELECTRICAL CHARACTERISTICS

(MAX2009 EV kit;  $V_{CCG} = V_{CCP} = +4.75V$  to +5.25V; no RF signal applied; INP, ING, OUTP, OUTG are AC-coupled and terminated to  $50\Omega$ ;  $V_{PE\_S1} = open$ ; PBEXP shorted to PBRAW;  $V_{PDCS1} = V_{PDCS2} = 0.8V$ ;  $V_{PBIN} = V_{GBP} = V_{GCS} = GND$ ;  $V_{GFS} = V_{CCG}$ ;  $V_{ABP} = V_{CCG} = V_{CCP} = +5.0V$ ,  $V_{ABP} = V_{CCD} = V_{CCP} = +5.0V$ ;  $V_{ABP} = V_{CCD} = V_{CCP} = V_{CCD} = V_{CCP} = +5.0V$ ;  $V_{ABP} = V_{CCD} = V_{CCP} = V_{CCD} =$

| PARAMETER                  | CONDITIONS                         | MIN  | TYP | MAX  | UNITS |  |  |

|----------------------------|------------------------------------|------|-----|------|-------|--|--|

| Supply Voltage             | VCCG, VCCP                         | 4.75 |     | 5.25 | V     |  |  |

| Supply Current             | VCCP                               |      | 5.8 | 7    | mA    |  |  |

| Supply Current             | Vccg                               |      | 10  | 12.1 | MA    |  |  |

| Analog Innut Valtage Dange | PBIN, PBRAW                        | 0    |     | VCCP | V     |  |  |

| Analog Input Voltage Range | GBP, GFS, GCS                      | 0    |     | Vccg | ¬     |  |  |

|                            | VGFS = VGCS = VPBRAW = 0V          | -2   |     | +2   |       |  |  |

| Analog Input Current       | $V_{GBP} = 0 \text{ to } +5V$ -100 |      |     | +170 | μΑ    |  |  |

|                            | $V_{PBIN} = 0 \text{ to } +5V$     | -100 |     | +220 |       |  |  |

| Logic-Input High Voltage   | PDCS1, PDCS2 (Note 1)              | 2.0  |     |      | V     |  |  |

| Logic-Input Low Voltage    | PDCS1, PDCS2 (Note 1)              |      |     | 0.8  | V     |  |  |

| Logic Input Current        |                                    | -2   |     | +2   | μΑ    |  |  |

### **AC ELECTRICAL CHARACTERISTICS**

$(\text{MAX2009 EV kit, V}_{CCG} = \text{V}_{CCP} = +4.75\text{V to } +5.25\text{V}, 50\Omega \text{ environment, P}_{IN} = -20\text{dBm, f}_{IN} = 1200\text{MHz to } 2500\text{MHz, V}_{GCS} = +1.0\text{V}, \text{V}_{GFS} = +5.0\text{V}, \text{V}_{GBP} = +1.2\text{V}, \text{V}_{PBIN} = \text{V}_{PDCS1} = \text{V}_{PDCS2} = 0\text{V}, \text{V}_{PF\_S1} = +5\text{V}, \text{V}_{PBRAW} = \text{V}_{PBEXP}, \text{T}_{A} = -40^{\circ}\text{C to } +85^{\circ}\text{C}. \text{ Typical values are at f}_{IN} = 2140\text{MHz, V}_{CCG} = \text{V}_{CCP} = +5\text{V}, \text{T}_{A} = +25^{\circ}\text{C}, \text{ unless otherwise noted.}) \text{ (Notes 1, 2)}$

| PARAMETER                                                | CONDITIONS                                                                  | MIN  | TYP   | MAX  | UNITS          |  |

|----------------------------------------------------------|-----------------------------------------------------------------------------|------|-------|------|----------------|--|

| Operating Frequency Range                                |                                                                             | 1200 |       | 2500 | MHz            |  |

| VSWR                                                     | ING, INP, OUTG, OUTP                                                        |      | 1.3:1 |      |                |  |

| PHASE CONTROL SECTION                                    |                                                                             |      |       |      |                |  |

| Nominal Gain                                             |                                                                             |      | -7.5  |      | dB             |  |

| Gain Variation Over Temperature                          | $T_A = -40$ °C to $+85$ °C                                                  |      | -1.4  |      | dB             |  |

| Gain Flatness                                            | Over a 100MHz band                                                          |      | ±0.1  |      | dB             |  |

| Phase-Expansion Breakpoint<br>Maximum                    | V <sub>PBIN</sub> = +5V                                                     |      | 23    |      | dBm            |  |

| Phase-Expansion Breakpoint<br>Minimum                    | V <sub>PBIN</sub> = 0V                                                      |      | 3.7   |      | dBm            |  |

| Phase-Expansion Breakpoint<br>Variation Over Temperature | $T_A = -40^{\circ}C \text{ to } +85^{\circ}C$                               |      | ±1.3  |      | dB             |  |

|                                                          | VPF_S1 = +5V, VPDCS1 = VPDCS2 = 0V,<br>P <sub>IN</sub> = -20 dBm to +23 dBm | 23.7 |       |      | Dograda        |  |

| Dhaga Evranaian                                          | VPDCS1 = 5V, VPDCS2 = 0V, VPF_S1 = +1.5V                                    |      | 14.2  |      |                |  |

| Phase Expansion                                          | VPDCS1 = 0V, VPDCS2 = 5V, VPF_S1 = +1.5V                                    |      | 9.2   |      | Degrees        |  |

|                                                          | VPF_S1 = 0V, VPDCS1 = VPDCS2 = +5V,<br>P <sub>IN</sub> = -20dBm to +23dBm   |      |       |      |                |  |

| Phase-Expansion Slope<br>Maximum                         | $P_{IN} = +15dBm$                                                           |      | 1.2   |      | Degrees<br>/dB |  |

| Phase-Expansion Slope Minimum                            | VPF_S1 = 0V, VPDCS1 = VPDCS2 = +5V,<br>P <sub>IN</sub> = +15dBm             |      | 0.4   |      | Degrees<br>/dB |  |

| Phase Slope Variation Over<br>Temperature                | P <sub>IN</sub> = +15dBm, T <sub>A</sub> = -40°C to +85°C                   |      | -0.1  |      | Degrees<br>/dB |  |

| Phase Ripple                                             | Over a 100MHz band, deviation from linear phase                             |      | ±0.15 |      | Degrees        |  |

| Noise Figure                                             |                                                                             |      | 7.5   |      | dB             |  |

| Absolute Group Delay                                     | Interconnects de-embedded                                                   |      | 0.7   |      | ns             |  |

| Group Delay Ripple                                       | Over a 100MHz band                                                          |      | ±0.03 |      | ns             |  |

| Parasitic Gain Expansion                                 | $P_{IN} = -20$ dBm to $+23$ dBm                                             |      | 0.9   |      | dB             |  |

## **AC ELECTRICAL CHARACTERISTICS (continued)**

$(\text{MAX2009 EV kit, V}_{CCG} = \text{V}_{CCP} = +4.75\text{V to } +5.25\text{V}, 50\Omega \text{ environment, P}_{IN} = -20\text{dBm, f}_{IN} = 1200\text{MHz to } 2500\text{MHz, V}_{GCS} = +1.0\text{V}, \text{V}_{GFS} = +5.0\text{V}, \text{V}_{GBP} = +1.2\text{V}, \text{V}_{PBIN} = \text{V}_{PDCS1} = \text{V}_{PDCS2} = 0\text{V}, \text{V}_{PF}_{S1} = +5\text{V}, \text{V}_{PBRAW} = \text{V}_{PBEXP}, \text{T}_{A} = -40^{\circ}\text{C to } +85^{\circ}\text{C}. \text{ Typical values are at f}_{IN} = 2140\text{MHz, V}_{CCG} = \text{V}_{CCP} = +5\text{V}, \text{T}_{A} = +25^{\circ}\text{C}, \text{ unless otherwise noted.}) \text{ (Notes 1, 2)}$

| PARAMETER                                               | CONDITIONS                                        | MIN TYP MAX | UNITS   |  |  |  |  |  |  |

|---------------------------------------------------------|---------------------------------------------------|-------------|---------|--|--|--|--|--|--|

| GAIN CONTROL SECTION                                    |                                                   |             |         |  |  |  |  |  |  |

|                                                         |                                                   | -16         |         |  |  |  |  |  |  |

| Nominal Gain                                            | $V_{GCS} = 0V$ , $V_{GFS} = +5V$                  | -23         | dB      |  |  |  |  |  |  |

|                                                         | V <sub>GCS</sub> = +5V, V <sub>GFS</sub> = 0V     | -8.5        |         |  |  |  |  |  |  |

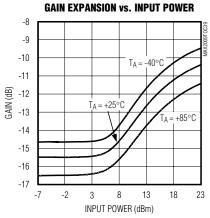

| Gain Variation Over Temperature                         | $T_A = -40$ °C to $+85$ °C                        | -1          | dB      |  |  |  |  |  |  |

| Gain Flatness                                           | Over a 100MHz band                                | ±0.3        | dB      |  |  |  |  |  |  |

| Gain-Expansion Breakpoint<br>Maximum                    | V <sub>GBP</sub> = +5V                            | 23          | dBm     |  |  |  |  |  |  |

| Gain-Expansion Breakpoint<br>Minimum                    | V <sub>GBP</sub> = +0.5V                          | -3          | dBm     |  |  |  |  |  |  |

| Gain-Expansion Breakpoint<br>Variation Over Temperature | $T_A = -40$ °C to +85°C                           | -0.3        | dB      |  |  |  |  |  |  |

| Cain Francian                                           | $V_{GFS} = +5V$ , $P_{IN} = -20$ dBm to $+23$ dBm | 6.6         | ٩D      |  |  |  |  |  |  |

| Gain Expansion                                          | $V_{GFS} = 0V$ , $P_{IN} = -20$ dBm to $+23$ dBm  | 3.6         | dB      |  |  |  |  |  |  |

| Gain-Expansion Slope                                    | $V_{GFS} = +5V$ , $P_{IN} = +15$ dBm              | 0.5         | dB/dB   |  |  |  |  |  |  |

| Gairi-Exparision Slope                                  | $V_{GFS} = +0V$ , $P_{IN} = +15$ dBm              | 0.26        | ub/ub   |  |  |  |  |  |  |

| Gain Slope Variation Over<br>Temperature                | $P_{IN} = +15 dBm$ , $T_A = -40 °C$ to $+85 °C$   | -0.04       | dB/dB   |  |  |  |  |  |  |

| Noise Figure                                            |                                                   | 16          | dB      |  |  |  |  |  |  |

| Absolute Group Delay                                    | Interconnects de-embedded                         | 0.61        | ns      |  |  |  |  |  |  |

| Group Delay Ripple                                      | Over a 100MHz band                                | ±0.01       | ns      |  |  |  |  |  |  |

| Phase Ripple                                            | Over a 100MHz band, deviation from linear phase   | ±0.07       | Degrees |  |  |  |  |  |  |

| Parasitic Phase Expansion                               | $P_{IN} = -20$ dBm to +23dBm                      | 5           | Degrees |  |  |  |  |  |  |

Note 1: Guaranteed by design and characterization.

Note 2: All limits reflect losses and characteristics of external components shown in the *Typical Application Circuit*, unless otherwise noted.

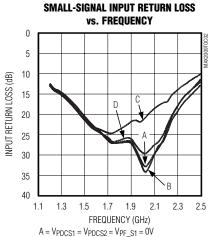

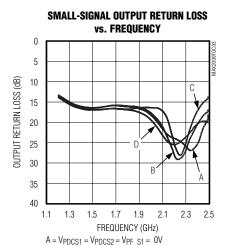

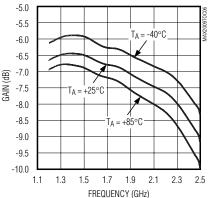

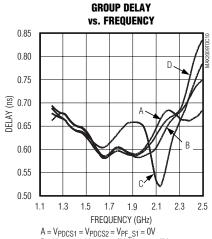

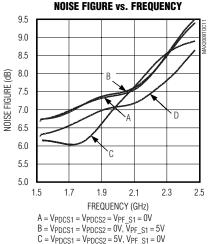

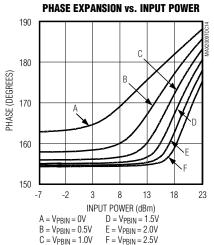

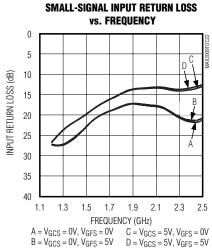

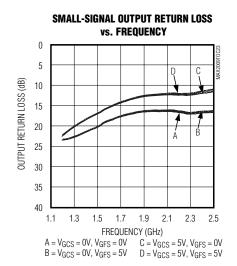

## **Typical Operating Characteristics**

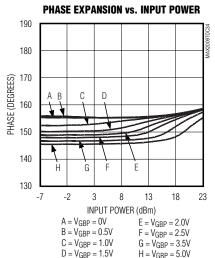

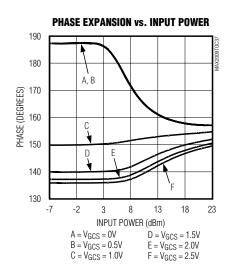

### **Phase Control Section**

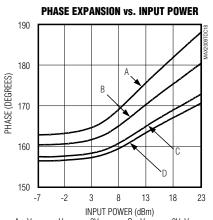

(MAX2009 EV kit, VCCP = +5.0V, PIN = -20dBm, VPBIN = 0V, VPF\_S1 = +5.0V, VPDCS1 = VPDCS2 = 0V, fIN = 2140MHz, TA = +25°C, unless otherwise noted.)

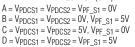

A = V<sub>PDCS1</sub> = V<sub>PDCS2</sub> = V<sub>PF\_S1</sub> = 0V B = V<sub>PDCS1</sub> = V<sub>PDCS2</sub> = 0V, V<sub>PF\_S1</sub> = 5V C = V<sub>PDCS1</sub> = V<sub>PDCS2</sub> = 5V, V<sub>PF\_S1</sub> = 0V D = V<sub>PDCS1</sub> = V<sub>PDCS2</sub> = V<sub>PF\_S1</sub> = 5V

### $B = V_{PDCS1} = V_{PDCS2} = 0V, \overline{V}_{PF S1} = 5V$ $C = V_{PDCS1} = V_{PDCS2} = 5V$ , $V_{PF\_S1} = 0V$ $D = V_{PDCS1} = V_{PDCS2} = V_{PF\_S1} = 5V$

### **LARGE-SIGNAL OUTPUT RETURN LOSS** vs. FREQUENCY

# **SMALL-SIGNAL GAIN** vs. FREQUENCY

## **Typical Operating Characteristics (continued)**

## **Phase Control Section (continued)**

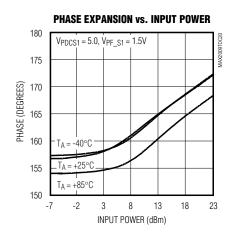

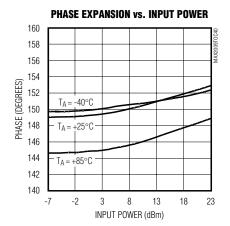

(MAX2009 EV kit,  $V_{CCP} = +5.0V$ ,  $P_{IN} = -20$ dBm,  $V_{PBIN} = 0V$ ,  $V_{PF\_S1} = +5.0V$ ,  $V_{PDCS1} = V_{PDCS2} = 0V$ ,  $f_{IN} = 2140$ MHz,  $T_A = +25$ °C, unless otherwise noted.)

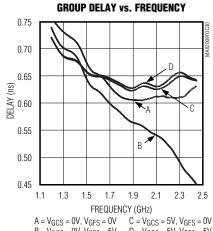

A = V<sub>PDCS1</sub> = V<sub>PDCS2</sub> = V<sub>PF\_S1</sub> = 0V B = V<sub>PDCS1</sub> = V<sub>PDCS2</sub> = 0V, V<sub>PF\_S1</sub> = 5V C = V<sub>PDCS1</sub> = V<sub>PDCS2</sub> = 5V, V<sub>PF\_S1</sub> = 0V D = V<sub>PDCS1</sub> = V<sub>PDCS2</sub> = V<sub>PF\_S1</sub> = 5V

INTERCONNECTS DE-EMBEDDED

C = VPDCS1 = VPDCS2 = 5V, VPF\_S1 = D = VPDCS1 = VPDCS2 = VPF\_S1 = 5V

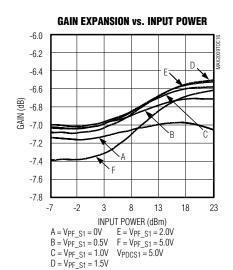

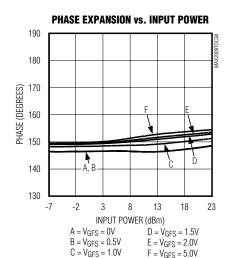

## Typical Operating Characteristics (continued)

## **Phase Control Section (continued)**

(MAX2009 EV kit,  $V_{CCP} = +5.0V$ ,  $P_{IN} = -20$ dBm,  $V_{PBIN} = 0V$ ,  $V_{PF\_S1} = +5.0V$ ,  $V_{PDCS1} = V_{PDCS2} = 0V$ ,  $f_{IN} = 2140$ MHz,  $T_A = +25$ °C, unless otherwise noted.)

$\begin{array}{lll} A = V_{PDCS1} = V_{PDCS2} = 0V & C = V_{PDCS1} = 0V, \ V_{PDCS2} = 5V \\ B = V_{PDCS1} = 5V, \ V_{PDCS2} = 0V & D = V_{PDCS1} = V_{PDCS2} = 5V \end{array}$

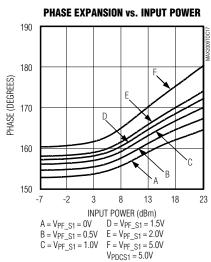

## **Typical Operating Characteristics (continued)**

## **Phase Control Section (continued)**

(MAX2009 EV kit,  $V_{CCP} = +5.0V$ ,  $P_{IN} = -20$ dBm,  $V_{PBIN} = 0V$ ,  $V_{PF\_S1} = +5.0V$ ,  $V_{PDCS1} = V_{PDCS2} = 0V$ ,  $f_{IN} = 2140$ MHz,  $T_A = +25$ °C, unless otherwise noted.)

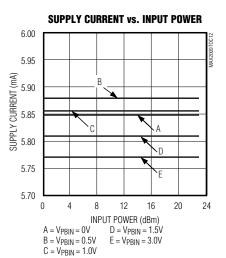

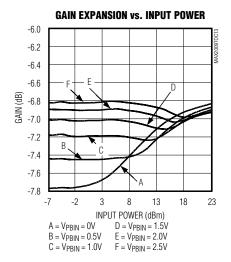

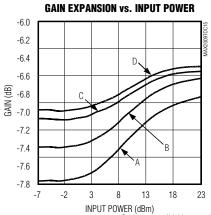

## **Typical Operating Characteristics**

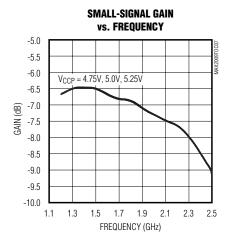

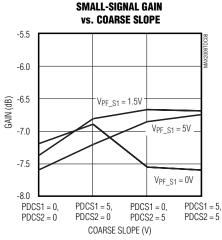

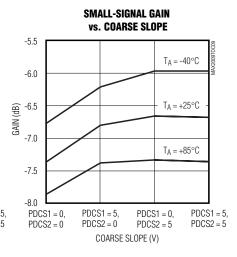

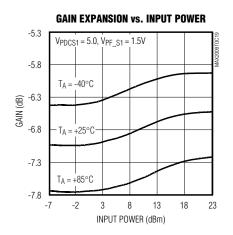

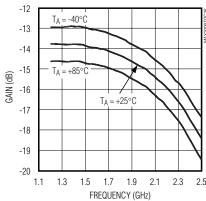

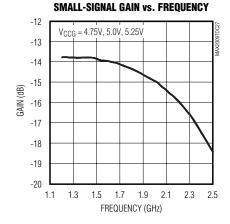

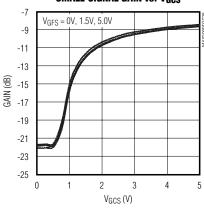

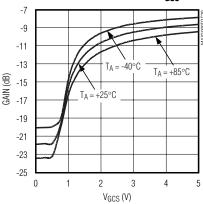

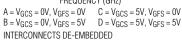

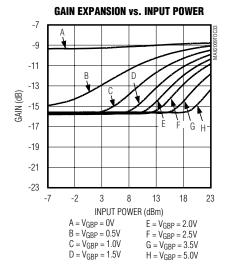

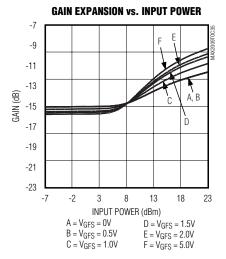

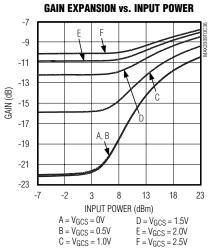

### **Gain Control Section**

(MAX2009 EV kit,  $V_{CCG}$  = +5.0V,  $P_{IN}$  = -20dBm,  $V_{GBP}$  = +1.2V,  $V_{GFS}$  = +5.0V,  $V_{GCS}$  = +1.0V,  $f_{IN}$  = 2140MHz,  $T_A$  = +25°C, unless otherwise noted.)

8 \_\_\_\_\_\_ /N/1XI/N

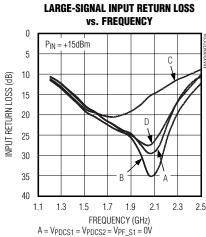

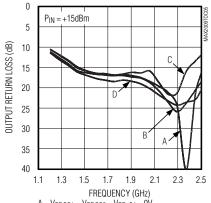

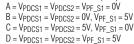

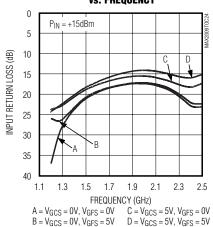

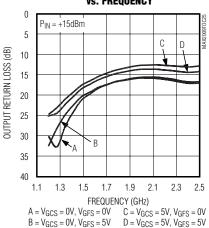

## Typical Operating Characteristics (continued)

## **Gain Control Section (continued)**

(MAX2009 EV kit,  $V_{CCG}$  = +5.0V,  $P_{IN}$  = -20dBm,  $V_{GBP}$  = +1.2V,  $V_{GFS}$  = +5.0V,  $V_{GCS}$  = +1.0V,  $V_{IN}$  = 2140MHz,  $V_{IN}$  = +25°C, unless otherwise noted.)

# LARGE-SIGNAL INPUT RETURN LOSS vs. FREQUENCY

# LARGE-SIGNAL OUTPUT RETURN LOSS vs. FREQUENCY

SMALL-SIGNAL GAIN vs. FREQUENCY

#### SMALL-SIGNAL GAIN vs. V<sub>GCS</sub>

#### SMALL-SIGNAL GAIN vs. V<sub>GCS</sub>

## Typical Operating Characteristics (continued)

## **Gain Control Section (continued)**

$(MAX2009 \text{ EV kit, V}_{CGG} = +5.0\text{V}, P_{IN} = -20 \text{dBm}, V_{GBP} = +1.2\text{V}, V_{GFS} = +5.0\text{V}, V_{GCS} = +1.0\text{V}, f_{IN} = 2140 \text{MHz}, T_A = +25 ^{\circ}\text{C}, unless = -2.0 ^{\circ}\text{C}$ otherwise noted.)

/N/IXI/N 10

## Typical Operating Characteristics (continued)

## **Gain Control Section (continued)**

(MAX2009 EV kit,  $V_{CCG}$  = +5.0V,  $P_{IN}$  = -20dBm,  $V_{GBP}$  = +1.2V,  $V_{GFS}$  = +5.0V,  $V_{GCS}$  = +1.0V,  $f_{IN}$  = 2140MHz,  $T_A$  = +25°C, unless otherwise noted.)

## **Pin Description**

| PIN                                            | NAME  | FUNCTION                                                                                                                                                      |

|------------------------------------------------|-------|---------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2, 4, 5, 7,<br>8, 10, 16, 20,<br>22, 26, 28 | GND   | Ground. Internally connected to the exposed paddle.                                                                                                           |

| 3                                              | ING   | RF Gain Input. Connect ING to a coupling capacitor if it is not connected to OUTP. ING is interchangeable with OUTG.                                          |

| 6                                              | OUTP  | RF Phase Output. Connect OUTP to a coupling capacitor if it is not connected to INP. OUTP is interchangeable with INP.                                        |

| 9                                              | INP   | RF Phase Input. Connect INP to a coupling capacitor. This pin is interchangeable with OUTP.                                                                   |

| 11                                             | PFS1  | Fine Phase-Slope Control Input 1. See the Typical Application Circuit.                                                                                        |

| 12                                             | PFS2  | Fine Phase-Slope Control Input 2. See the Typical Application Circuit.                                                                                        |

| 13                                             | PDCS1 | Digital Coarse Phase-Slope Control Range Input 1. Set to logical zero for the steepest slope.                                                                 |

| 14                                             | PDCS2 | Digital Coarse Phase-Slope Control Range Input 2. Set to logical zero for the steepest slope.                                                                 |

| 15                                             | VCCP  | Phase-Control Supply Voltage. Bypass with a $0.01\mu F$ capacitor to ground as close to the device as possible. Phase section can operate without $V_{CCG}$ . |

| 17                                             | PBIN  | Phase Breakpoint Control Input                                                                                                                                |

| 18                                             | PBEXP | Phase Expansion Output. Connect PBEXP to PBRAW to use PBIN as the breakpoint control voltage.                                                                 |

| 19                                             | PBRAW | Uncompensated Phase Breakpoint Input                                                                                                                          |

| 21                                             | Vccg  | Gain-Control Supply Voltage. Bypass with a 0.01µF capacitor to ground as close to the device as possible. Gain section can operate without V <sub>CCP</sub> . |

| 23                                             | GBP   | Gain Breakpoint Control Input                                                                                                                                 |

| 24                                             | GFS   | Fine Gain-Slope Control Input                                                                                                                                 |

| 25                                             | GCS   | Coarse Gain-Slope Control Input                                                                                                                               |

| 27                                             | OUTG  | RF Gain Output. Connect OUTG to a coupling capacitor. OUTG is interchangeable with ING.                                                                       |

| EP                                             | GND   | Exposed Ground Paddle. Solder EP to the ground plane.                                                                                                         |

## Detailed Description

The MAX2009 adjustable predistorter can provide up to 12dB of ACPR improvement for high-power amplifiers by introducing gain and phase expansion to compensate for the PA's gain and phase compression. The MAX2009 enables real-time software-controlled distortion correction, as well as set-and-forget tuning through the adjustment of the expansion starting point (breakpoint) and the rate of expansion (slope). The gain and phase break-

points can be set over a 20dB input power range. The phase expansion slope is variable from 0.3°/dB to 2.0°/dB and can be adjusted for a maximum of 24° of phase expansion. The gain expansion slope is variable from 0.1dB/dB to 0.6dB/dB and can be adjusted for a maximum of 7dB gain expansion.

The following sections describe the tuning methodology best implemented with a class A amplifier. Other classes of operation may require significantly different settings.

### Phase Expansion Circuitry

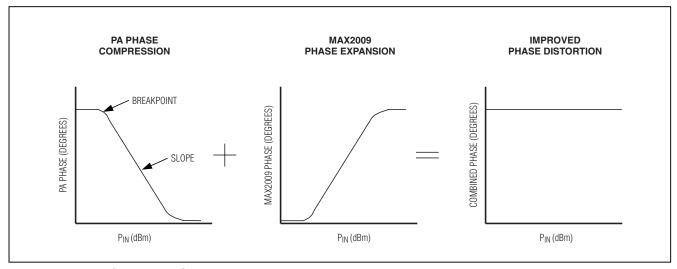

Figure 1 shows a typical PA's phase behavior with respect to input power. For input powers less than the breakpoint level, the phase remains relatively constant. As the input power becomes greater than the breakpoint level, the phase begins to compress and deteriorate the power amplifier's linearity. To compensate for this AM-PM distortion, the MAX2009 provides phase expansion, which occurs at the same breakpoint level but with the opposite slope. The overall result is a flat phase response.

### Phase Expansion Breakpoint

The phase expansion breakpoint is typically controlled by a digital-to-analog converter (DAC) connected through the PBIN pin. The PBIN input voltage range of 0V to VCC corresponds to a breakpoint input power range of 3.7dBm to 23dBm. To achieve optimal performance, the phase expansion breakpoint of the MAX2009 must be set to equal the phase compression breakpoint of the PA.

### Phase Expansion Slope

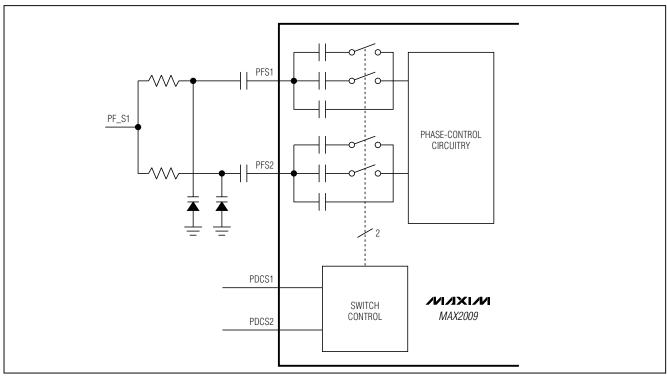

The phase expansion slope of the MAX2009 must also be adjusted to equal the opposite slope of the PA's phase compression curve. The phase expansion slope of the MAX2009 is controlled by the PFS1, PFS2, PDCS1, and PDCS2 pins. With pins PFS1 and PFS2, AC-coupled and connected to a variable capacitor or varactor diode,

the PFS1 and PFS2 pins perform the task of fine tuning the phase expansion slope. Since off-chip varactor diodes are recommended for this function, they must be closely matched and identically biased. A minimum effective capacitance of 2pF to 6pF is required to achieve the full phase slope range as specified in the *Electrical Characteristics* tables.

As shown in Figure 2, the varactors connected to PFS1 and PFS2 are in series with three internal capacitors on each pin. By connecting and disconnecting these internal capacitors, a larger change in phase expansion slope can be achieved through the logic levels presented at the PDCS1 and PDCS2 pins. The phase expansion slope is at its maximum when both VPDCS1 and VPDCS2 equal OV. The phase tuning has a minimal effect on the small-signal gain.

### **Gain Expansion Circuitry**

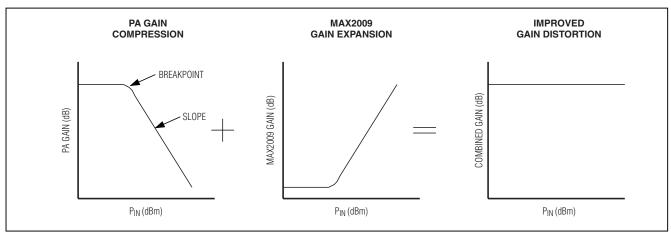

In addition to phase compression, the PA also suffers from gain compression (AM-AM) distortion, as shown in Figure 3. The PA gain curve remains flat for input powers below the breakpoint level, and begins to compress at a given rate (slope) for input powers greater than the breakpoint level. To compensate for such gain compression, the MAX2009 generates a gain expansion, which occurs at the same breakpoint level with the opposite slope. The overall result is a flat gain response at the PA output.

Figure 1. PA Phase Compression Canceled by MAX2009 Phase Expansion

Figure 2. Simplified Phase Slope Internal Circuitry

Figure 3. PA Gain Compression Canceled by MAX2009 Gain Expansion

#### Gain Expansion Breakpoint

The gain expansion breakpoint is usually controlled by a DAC connected through the GBP pin. The GBP input voltage range of 0.5V to 5V corresponds to a breakpoint input power range of 3dBm to 23dBm. To achieve the optimal performance, the gain expansion breakpoint of the MAX2009 must be set to equal the gain compression point of the PA. The GBP control has a minimal effect on the small-signal gain when operated from 0.5V to 5V.

### Gain Expansion Slope

In addition to properly setting the breakpoint, the gain expansion slope of the MAX2009 must also be adjusted to compensate for the PA's gain compression. The slope should be set using the following equation:

$$MAX2009\_SLOPE = \frac{-PA\_SLOPE}{1+PA\_SLOPE}$$

where:

MAX2009\_SLOPE = MAX2009 gain section's slope in dB/dB

PA\_SLOPE = PA's gain slope in dB/dB, a negative number for compressive behavior.

To modify the gain expansion slope, two adjustments must be made to the biases applied on pins GCS and GFS. Both GCS and GFS have an input voltage range of 0V to V<sub>CC</sub>, corresponding to a slope of approximately 0.1dB/dB to 0.6dB/dB. The slope is set to maximum when V<sub>GCS</sub> = 0V and V<sub>GFS</sub> = +5V, and the slope is at its minimum when V<sub>GCS</sub> = +5V and V<sub>GFS</sub> = 0V.

Unlike the GBP pin, modifying the gain expansion slope bias on the GCS pin causes a change in the part's insertion loss and noise figure. For example, a smaller slope caused by GCS results in a better insertion loss and lower noise figure. The GFS does not affect the insertion loss. It can provide up to -30% or +30% total slope variation around the nominal slope set by GCS.

Large amounts of GCS bias adjustment can also lead to an undesired (or residual) phase expansion/compression behavior. There exists an optimal bias voltage that minimizes this parasitic behavior (typically GCS = 1.0V). Control voltages higher than the optimal result in parasitic phase expansion, lower control voltages result in phase compression. GFS does not contribute to the phase behavior and is preferred for slope control.

## Applications Information

The following section describes the tuning methodology best implemented with a class A amplifier. Other classes of operation may require significantly different settings.

### **Gain and Phase Expansion Optimization**

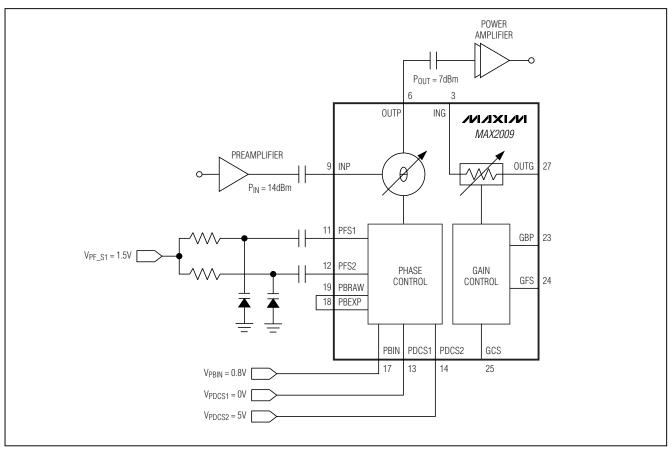

The best approach to improve the ACPR of a PA is to first optimize the AM-PM response of the phase section. For most high-frequency LDMOS amplifiers, improving the AM-PM response provides the bulk of the ACPR improvement. Figure 4 shows a typical configuration of the phase tuning circuit. A power sweep on a network analyzer allows quick real-time tuning of the AM-PM response. First, tune PBIN to achieve the phase expansion starting point (breakpoint) at the same point where the PA's phase compression begins. Next, use control pins PF\_S1, PDCS1, and PDCS2 to obtain the optimal AM-PM response. The typical values for these pins are shown in Figure 4.

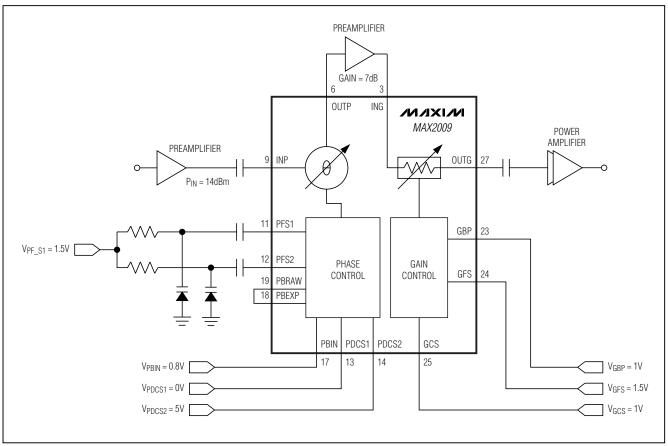

To further improve the ACPR, connect the phase output to the gain input through a preamplifier. The preamplifier is used to compensate for the high insertion loss of the gain section. Figure 5 shows a typical application circuit of the MAX2009 with the phase section cascaded to the gain section for further ACPR optimization. Similar to tuning the phase section, first tune the gain expansion breakpoint through the GBP pin and adjust for the desired gain expansion with pins GCS and GFS. To minimize the effect of GCS on the parasitic phase response, minimize the control voltage to around 1V. Some retuning of the AM-PM response may be necessary.

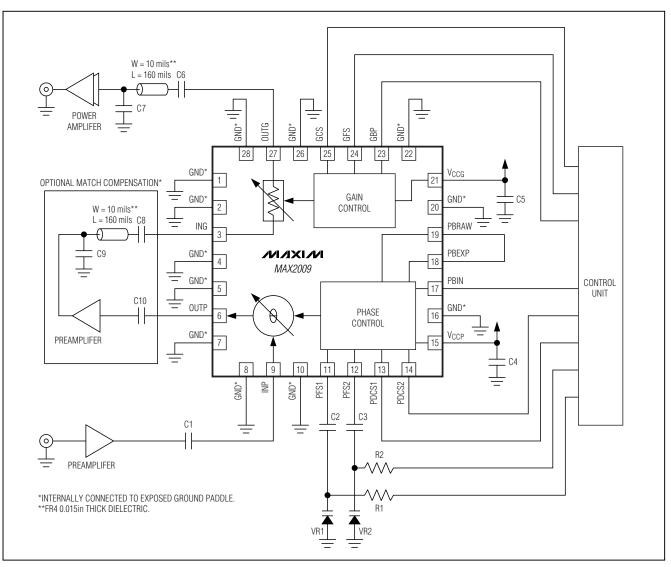

### **Layout Considerations**

A properly designed PC board is an essential part of any high-frequency circuit. To minimize external components, the PC board can be designed to incorporate small values of inductance and capacitance to optimize the input and output VSWR (refer to the MAX2009). The phase section's PFS1 and PFS2 pins are sensitive to external parasitics. Minimize trace lengths and keep varactor diodes close to the pins. Remove the ground plane underneath the traces can further help reduce the parasitic capacitance. For best performance, route the ground pin traces directly to the grounded EP underneath the package. Solder the EP on the bottom of the device package evenly to the board ground plane to provide a heat transfer path along with signal grounding.

Figure 4. AM-PM Response Tuning Circuit

#### **Power-Supply Bypassing**

Bypass each VCC pin with a 0.01µF capacitor.

### **Exposed Pad RF**

The exposed paddle (EP) of the MAX2009's 28-pin thin QFN-EP package provides a low inductance path to ground. It is important that the EP be soldered to the ground plane on the PC board, either directly or through an array of plated via holes.

# **Table 1. Suggested Components of Typical Application Circuit**

| DESIGNATION     | VALUE                   | TYPE                        |  |  |

|-----------------|-------------------------|-----------------------------|--|--|

| C1, C6, C8, C10 | 8.2pF ±0.25pF           | 0402 ceramic capacitors     |  |  |

| C2, C3          | 1.5pF ±0.1pF            | 0402 ceramic capacitors     |  |  |

| C4, C5          | 0.01µF ±10%             | 0603 ceramic capacitors     |  |  |

| C7, C9          | 0.5pF ±0.1pF            | 0402 ceramic capacitors     |  |  |

| R1, R2          | 1kΩ ±5%                 | 0402 resistors              |  |  |

| VR1, VR2        | Skyworks<br>SMV1232-079 | Hyperabrupt varactor diodes |  |  |

Figure 5. MAX2009 Phase and Gain Optimization Circuit

## **Typical Application Circuit**

## Chip Information

TRANSISTOR COUNT:

Bipolar: 160 CMOS: 240

PROCESS: BICMOS

## **Package Information**

(The package drawing(s) in this data sheet may not reflect the most current specifications. For the latest package outline information go to <a href="https://www.maxim-ic.com/packages">www.maxim-ic.com/packages</a>.)

| COMMON DIMENSIONS |        |          |      |           |           |           |           |           |         |           |      |     |

|-------------------|--------|----------|------|-----------|-----------|-----------|-----------|-----------|---------|-----------|------|-----|

| PKG.              |        | 16L 5x5  |      |           | 20L 5x5   |           | 28L 5x5   |           | 32L 5x5 |           |      |     |

| SYMBOL            | MIN.   | NOM.     | MAX. | MIN.      | NOM.      | MAX.      | MIN.      | NOM.      | MAX.    | MIN.      | NOM. | MAX |

| Α                 | 0.70   | 0.75     | 0.80 | 0.70      | 0.75      | 0.80      | 0.70      | 0.75      | 0.80    | 0.70      | 0.75 | 0.8 |

| A1                | 0      | 0.02     | 0.05 | 0         | 0.02      | 0.05      | 0         | 0.02      | 0.05    | 0         | 0.02 | 0.0 |

| A3                |        | 0.20 REF |      | (         | 0.20 REF. |           | 0.20 REF. |           |         | 0.20 REF. |      |     |

| b                 | 0.25   | 0.30     | 0.35 | 0.25      | 0.30      | 0.35      | 0.20      | 0.25      | 0.30    | 0.20      | 0.25 | 0.3 |

| D                 | 4.90   | 5.00     | 5.10 | 4.90      | 5.00      | 5.10      | 4.90      | 5.00      | 5.10    | 4.90      | 5.00 | 5.1 |

| Е                 | 4.90   | 5.00     | 5.10 | 4.90      | 5.00      | 5.10      | 4.90      | 5.00      | 5.10    | 4.90      | 5.00 | 5.1 |

| •                 |        | 0.80 BS  | Э.   | 0.65 BSC. |           | 0.50 BSC. |           | 0.50 BSC. |         |           |      |     |

| k                 | 0.25   | -        | -    | 0.25      | -         | -         | 0.25      | -         | -       | 0.25      | -    | -   |

| L                 | 0.45   | 0.55     | 0.65 | 0.45      | 0.55      | 0.65      | 0.45      | 0.55      | 0.65    | 0.30      | 0.40 | 0.5 |

| N                 |        | 16       |      | 20        |           | 28        |           |           | 32      |           |      |     |

| ND                | 4      |          | 5    |           | 7         |           |           | 8         |         |           |      |     |

| NE                | 4      |          | 5    |           | 7         |           | 8         |           |         |           |      |     |

| JEDEC             | C WHHB |          | WHHC |           | WHHD-1    |           | WHHD-2    |           |         |           |      |     |

| E       | XPOS | ED P | AD V | ARIAT | IONS |      |

|---------|------|------|------|-------|------|------|

| PKG.    |      | D2   |      |       | E2   |      |

| CODES   | MIN. | NOM. | MAX. | MIN.  | NOM. | MAX. |

| T1655-1 | 3.00 | 3.10 | 3.20 | 3.00  | 3.10 | 3.20 |

| T2055-2 | 3.00 | 3.10 | 3.20 | 3.00  | 3.10 | 3.20 |

| T2855-1 | 3.15 | 3.25 | 3.35 | 3.15  | 3.25 | 3.35 |

| T2855-2 | 2.60 | 2.70 | 2.80 | 2.60  | 2.70 | 2.80 |

| T3255-2 | 3.00 | 3.10 | 3.20 | 3.00  | 3.10 | 3.20 |

#### NOTES

- 1. DIMENSIONING & TOLERANCING CONFORM TO ASME Y14.5M-1994

- ALL DIMENSIONS ARE IN MILLIMETERS. ANGLES ARE IN DEGREES.

- 3. N IS THE TOTAL NUMBER OF TERMINALS.

- THE TERMINAL #1 IDENTIFIER AND TERMINAL NUMBERING CONVENTION SHALL CONFORM TO JESD 95-187-012. DETAILS OF TERMINAL #1 IDENTIFIER ARE OPTIONAL, BUT MUST BE LOCATED WITHIN THE SPO-418. DETAILS OF TERMINAL #1 IDENTIFIER ARE DETAILS. BUT MUST BE LOCATED WITHIN THE SPO-418. DETAILS OF MARKED FEATURE.

- DIMENSION & APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.25 mm AND 0.30 mm FROM TERMINAL TIP.

- ND AND NE REFER TO THE NUMBER OF TERMINALS ON EACH D AND E SIDE RESPECTIVELY.

- COPLANARITY APPLIES TO THE EXPOSED HEAT SINK SLUG AS WELL AS THE TERMINALS.

9. DRAWING CONFORMS TO JEDEC MO220.

- 10. WARPAGE SHALL NOT EXCEED 0.10 mm.

Maxim cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim product. No circuit patent licenses are implied. Maxim reserves the right to change the circuitry and specifications without notice at any time.

Maxim Integrated Products, 120 San Gabriel Drive, Sunnyvale, CA 94086 408-737-7600 \_\_\_\_\_

\_ 19

© 2003 Maxim Integrated Products

Printed USA

is a registered trademark of Maxim Integrated Products.