# Contents

| Page     | Section | Title                                        |

|----------|---------|----------------------------------------------|

| 7        | 1.      | Introduction                                 |

| 7        | 1.1.    | Features                                     |

| 9        | 1.2.    | Abbreviations                                |

| 10       | 1.3.    | Block Diagram                                |

| 11       | 2.      | Packages and Pins                            |

| 11       | 2.1.    | Pin Assignment                               |

| 14       | 2.2.    | Package Outline Dimensions                   |

| 15       | 2.3.    | Multiple Function Pins                       |

| 15       | 2.4.    | Pin Function Description                     |

| 19       | 2.5.    | External Components                          |

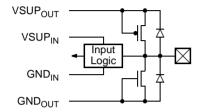

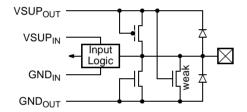

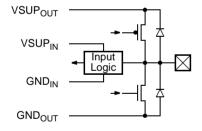

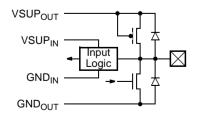

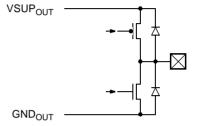

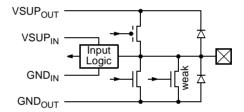

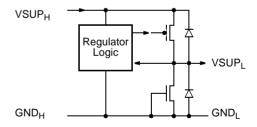

| 20       | 2.6.    | Pin Circuits                                 |

| 23       | 3.      | Electrical Data                              |

| 23       | 3.1.    | Absolute Maximum Ratings                     |

| 24       | 3.2.    | Recommended Operating Conditions             |

| 25       | 3.3.    | Characteristics                              |

| 34       | 3.4.    | Recommended Quartz Crystal Characteristics   |

| 35       | 4.      | CPU and Clock System                         |

| 35       | 4.1.    | ARM7TDMI™ CPU                                |

| 35       | 4.2.    | Operating Modes                              |

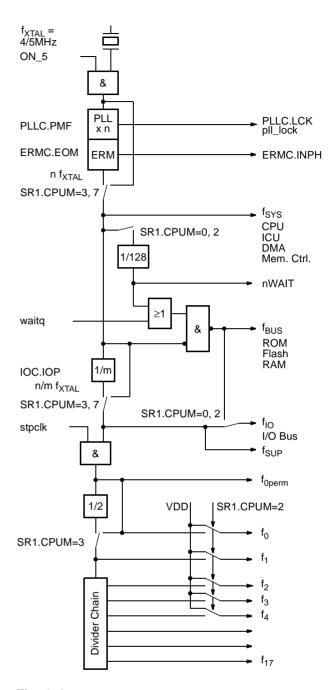

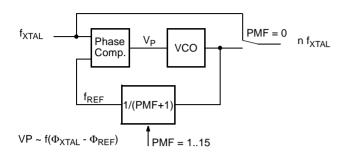

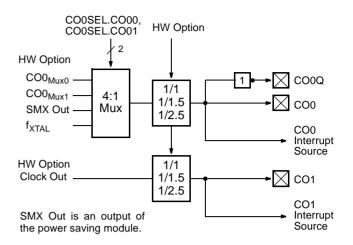

| 39       | 4.3.    | Clock System                                 |

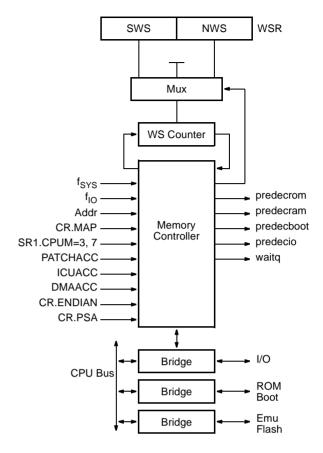

| 41       | 4.4.    | Memory Controller                            |

| 43       | 4.5.    | EMI Reduction Module (ERM)                   |

| 44       | 4.6.    | Registers                                    |

| 46       | 4.7.    | PLL/ERM Application Notes                    |

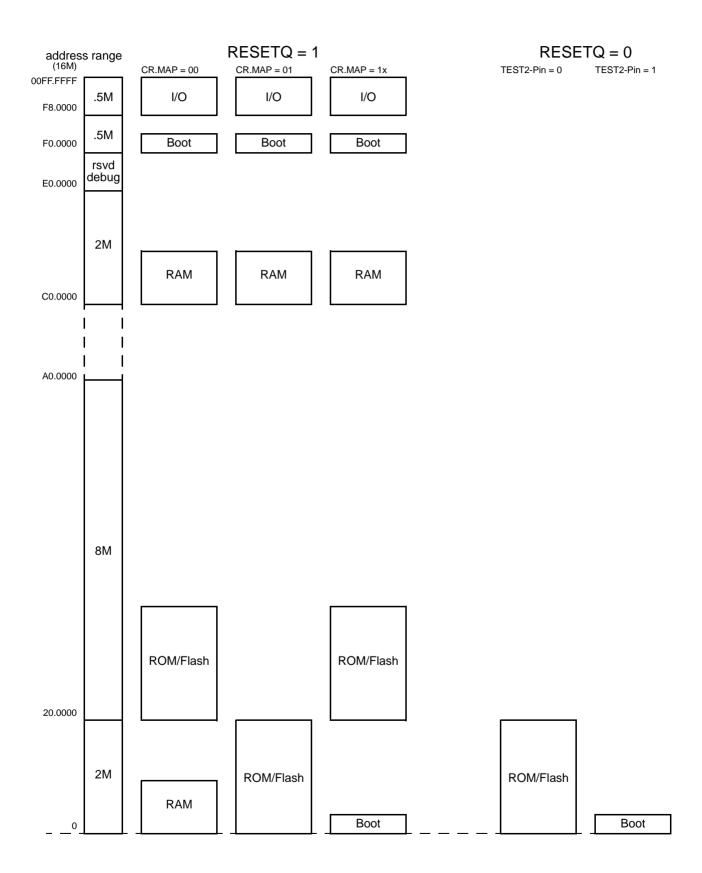

| 49       | 5.      | Memory and Special Function ROM (SFR) System |

| 50       | 5.1.    | RAM and ROM                                  |

| 51       | 5.2.    | I/O Map                                      |

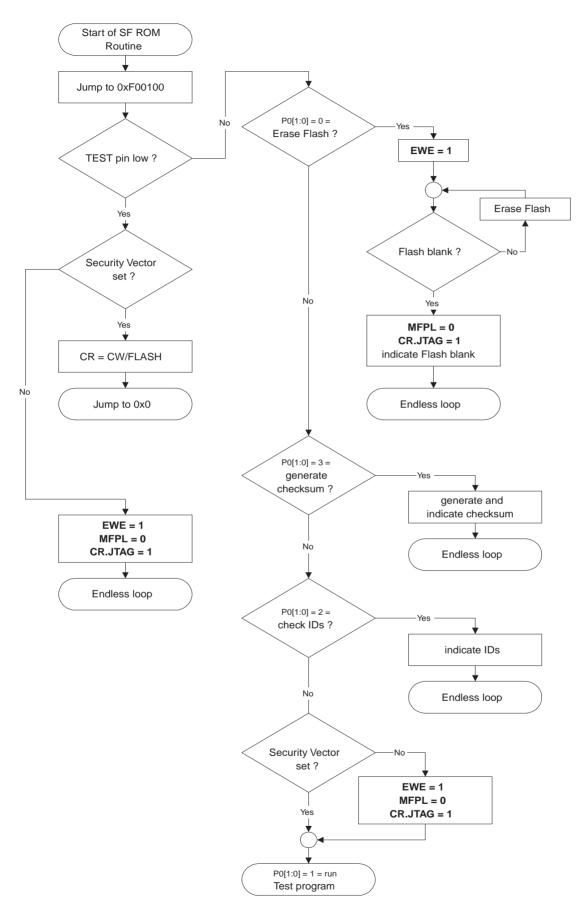

| 52       | 5.3.    | Special Function ROM (SFR)                   |

| 55       | 6.      | Core Logic                                   |

| 55       | 6.1.    | Control Word (CW)                            |

| 56       | 6.2.    | Device Lock Module (DLM)                     |

| 57       | 6.3.    | Standby Registers                            |

| 58       | 6.4.    | UVDD Analog Section                          |

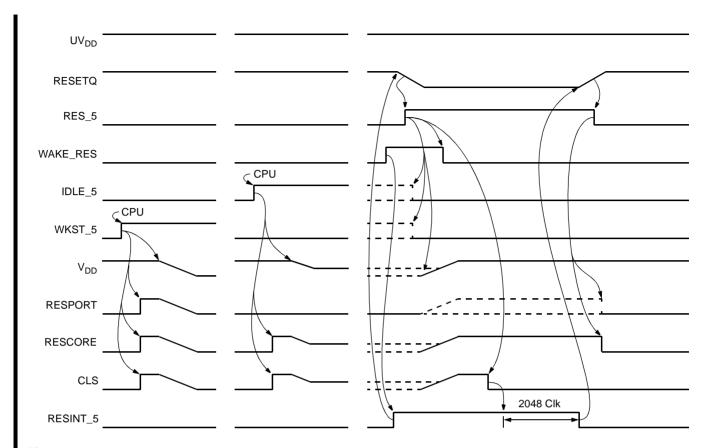

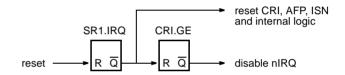

| 60       | 6.5.    | Reset Logic                                  |

| 64       | 6.6.    | Test Registers                               |

| 67       | 7.      | Power Saving Module (PSM)                    |

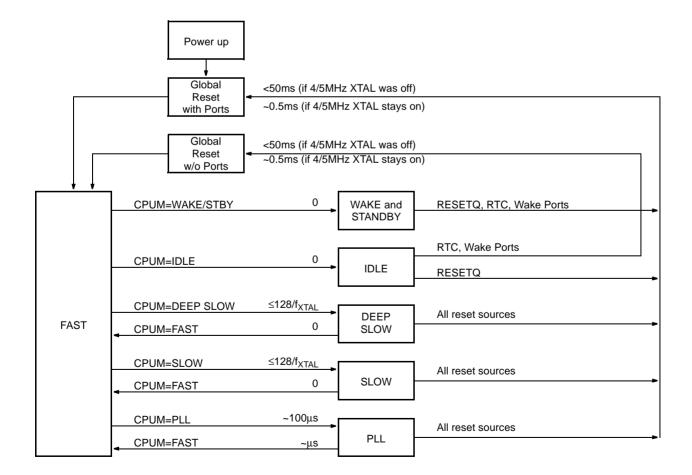

| 68       | 7.1.    | Functional Description                       |

| 69       | 7.2.    | Registers                                    |

| 73<br>75 | 7.3.    | Operation of Power Saving Module             |

| 75<br>70 | 7.4.    | Operation of RTC Module                      |

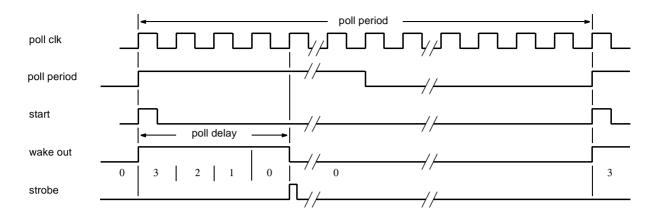

| 76<br>77 | 7.5.    | Operation of Polling Module                  |

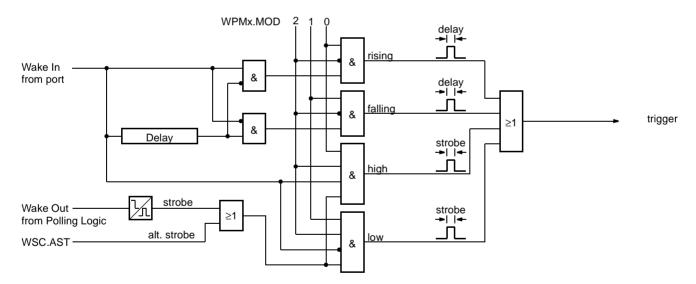

| 77       | 7.6.    | Operation of Port Wake Module                |

| Page | Section | Title                               |

|------|---------|-------------------------------------|

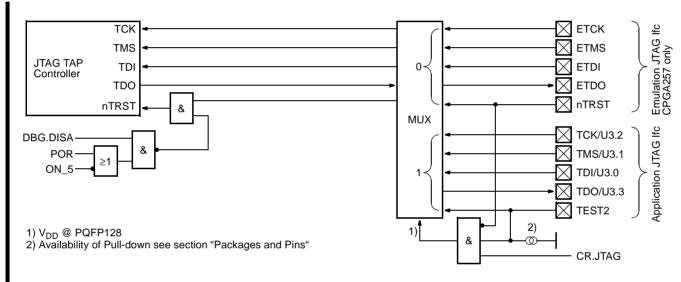

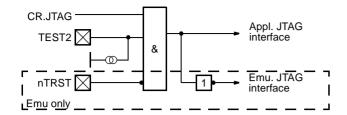

| 79   | 8.      | JTAG Interface                      |

| 79   | 8.1.    | Functional Description              |

| 80   | 8.2.    | Registers                           |

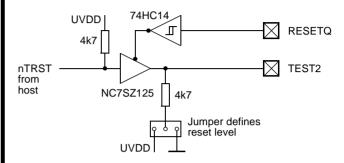

| 80   | 8.3.    | External Circuit Layout             |

| 80   | 8.4.    | JTAG ID                             |

| 83   | 9.      | Embedded Trace Module (ETM)         |

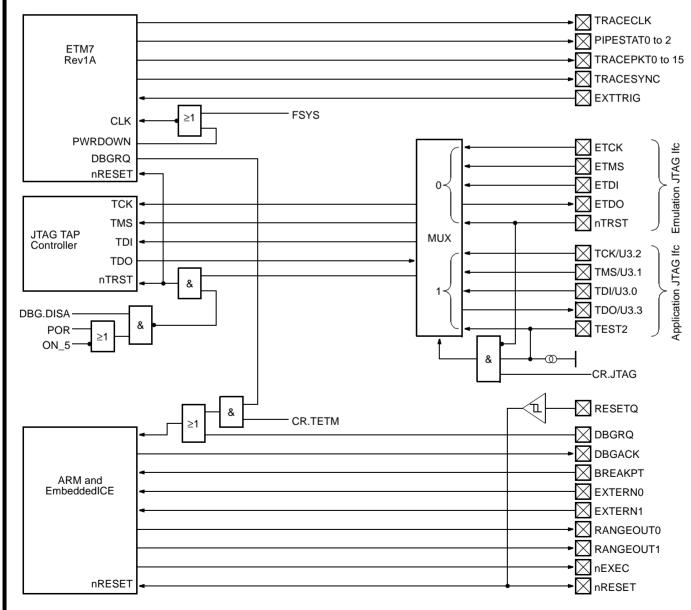

| 83   | 9.1.    | Functional Description              |

| 85   | 10.     | Memory Patch Module V1.0            |

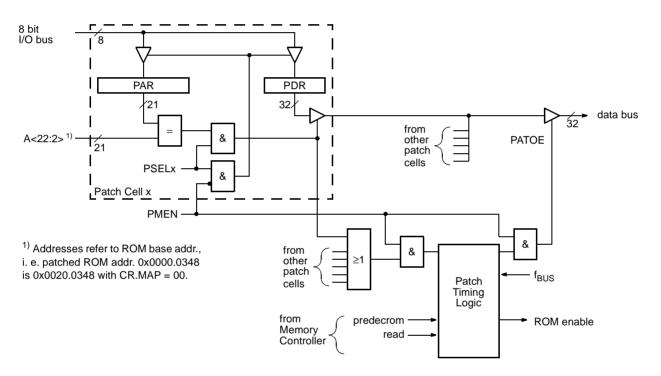

| 85   | 10.1.   | Principle of operation              |

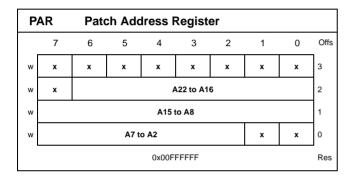

| 86   | 10.2.   | Registers                           |

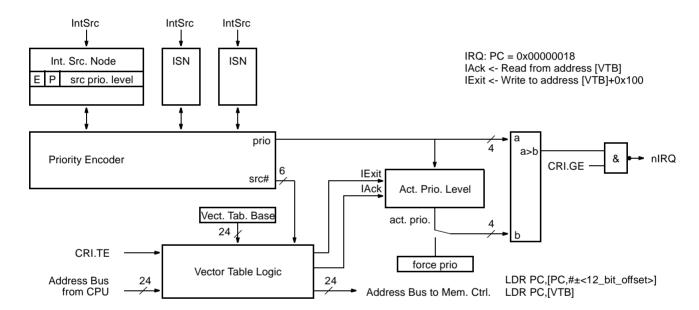

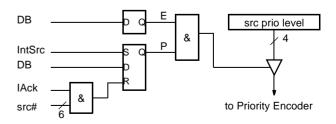

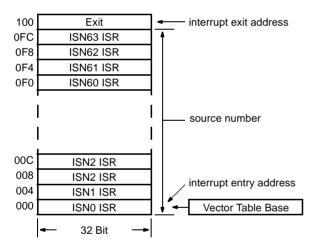

| 87   | 11.     | IRQ Interrupt Controller Unit (ICU) |

| 87   | 11.1.   | Functional Description              |

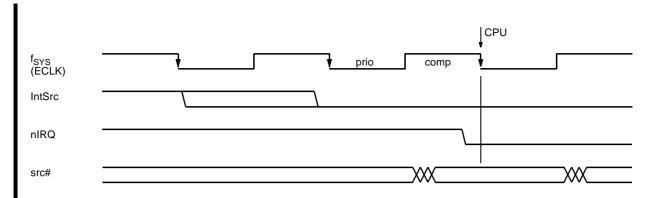

| 90   | 11.2.   | Timing                              |

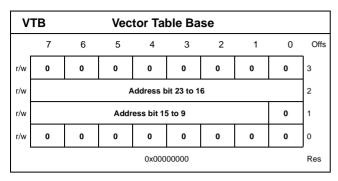

| 90   | 11.3.   | Registers                           |

| 92   | 11.4.   | Principle of Operation              |

| 92   | 11.5.   | Application Hints                   |

| 95   | 12.     | FIQ Interrupt Logic                 |

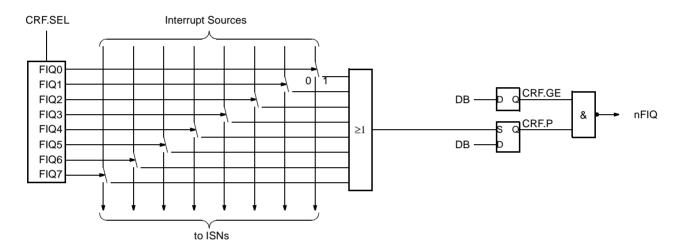

| 95   | 12.1.   | Functional Description              |

| 95   | 12.2.   | Registers                           |

| 96   | 12.3.   | Principle of Operation              |

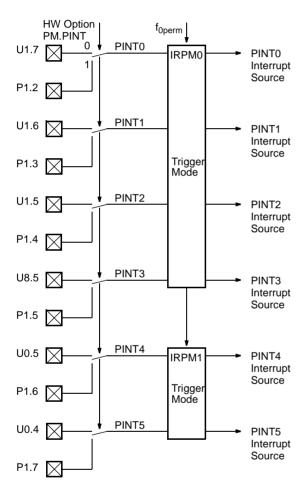

| 97   | 13.     | Port Interrupts                     |

| 99   | 14.     | Ports                               |

| 99   | 14.1.   | Analog Input Port                   |

| 101  | 14.2.   | Universal Ports U0 to U8            |

| 103  | 14.3.   | Universal Port Registers            |

| 105  | 14.4.   | High Current Ports H0 to H7         |

| 106  | 14.5.   | High Current Port Registers         |

| 107  | 15.     | AVDD Analog Section                 |

| 108  | 15.1.   | VREFINT Generator                   |

| 108  | 15.2.   | BVDD Regulator                      |

| 108  | 15.3.   | Wait Comparator                     |

| 108  | 15.4.   | P0.6 Comparator                     |

| 109  | 15.5.   | PLL/ERM                             |

| 109  | 15.6.   | A/D Converter (ADC)                 |

| 111  | 15.7.   | Registers                           |

| 113  | 16.     | Timers (TIMER)                      |

| 113  | 16.1.   | Timer T0                            |

| 115  | 16.2.   | Timer T1 to T4                      |

| 117  | 17.     | Pulse Width Modulator (PWM)         |

| 117  | 17.1.   | Principle of Operation              |

|      |         |                                     |

| Page | Section | Title                                              |

|------|---------|----------------------------------------------------|

| 118  | 17.2.   | Registers                                          |

| 121  | 18.     | Pulse Frequency Modulator (PFM)                    |

| 121  | 18.1.   | Principle of Operation                             |

| 122  | 18.2.   | Registers                                          |

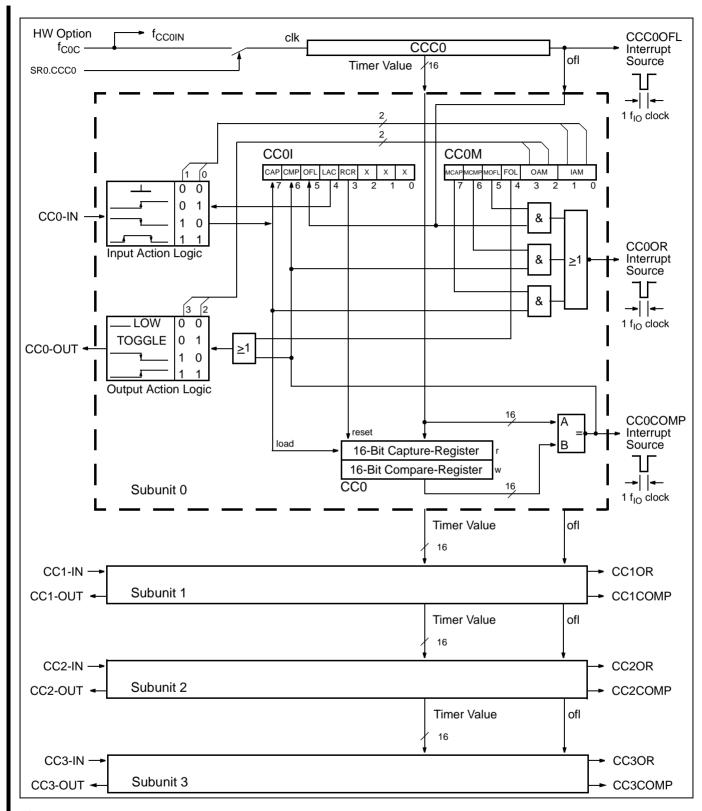

| 123  | 19.     | Capture Compare Module (CAPCOM)                    |

| 125  | 19.1.   | Principle of Operation                             |

| 127  | 19.2.   | Registers                                          |

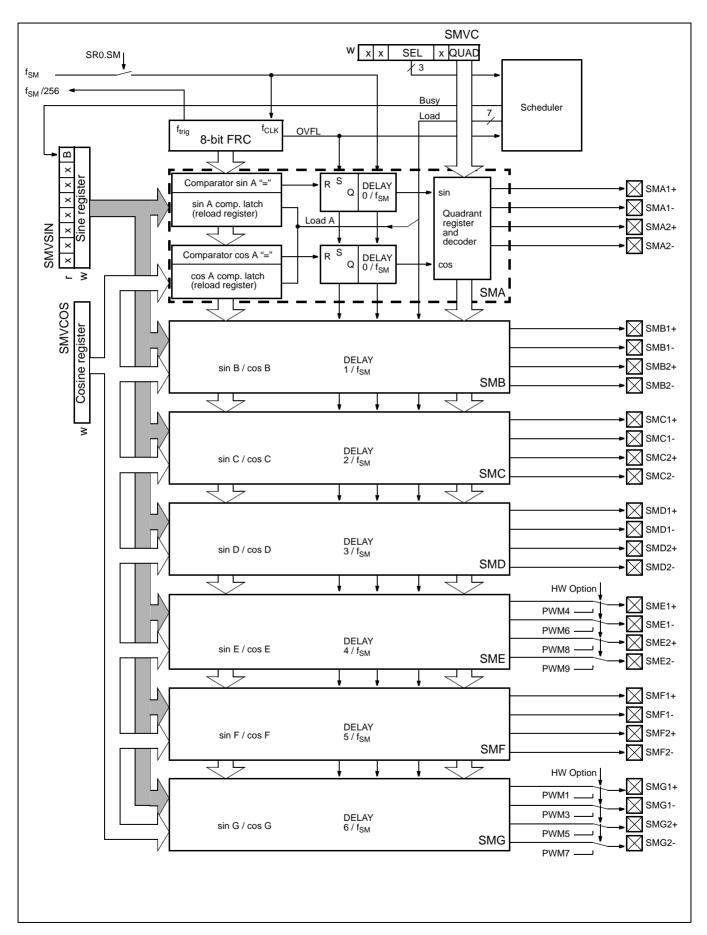

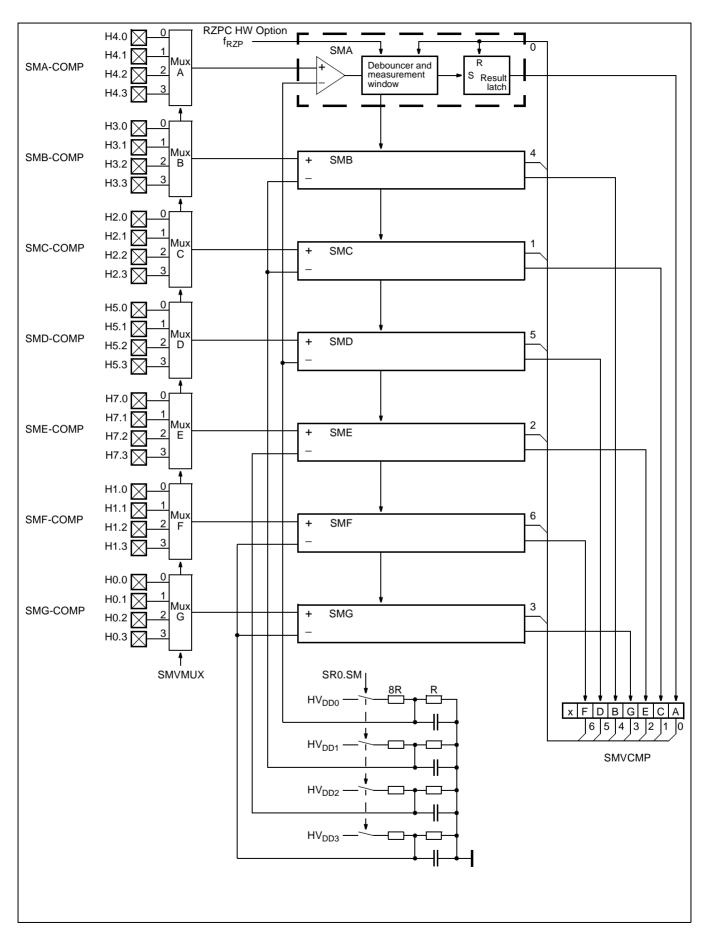

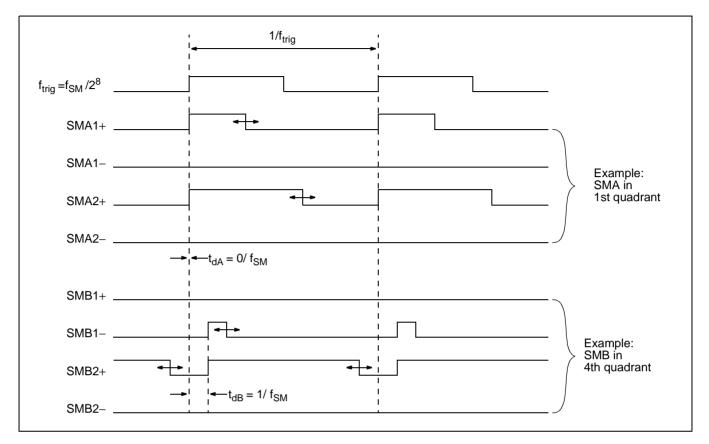

| 129  | 20.     | Stepper Motor Module SV (SMV)                      |

| 129  | 20.1.   | Principle of Operation                             |

| 133  | 20.2.   | Registers                                          |

| 134  | 20.3.   | Timing                                             |

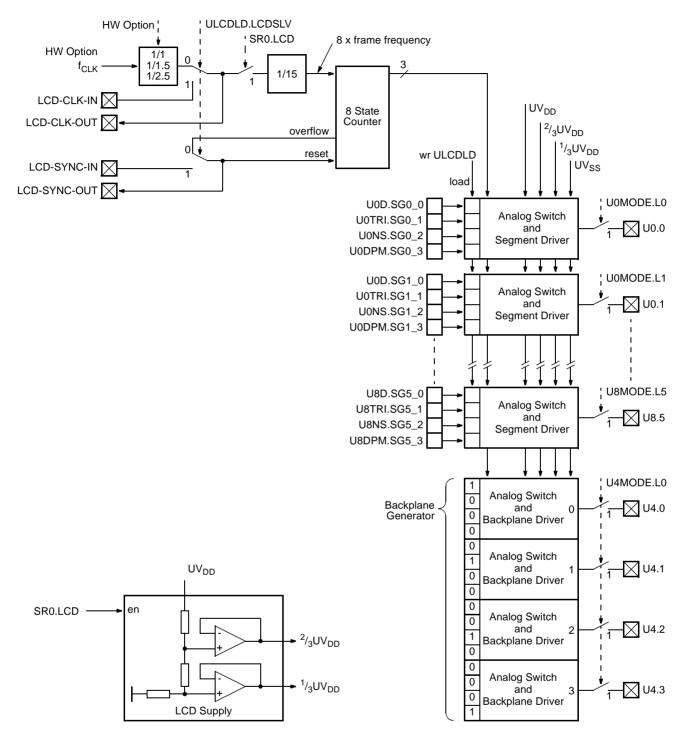

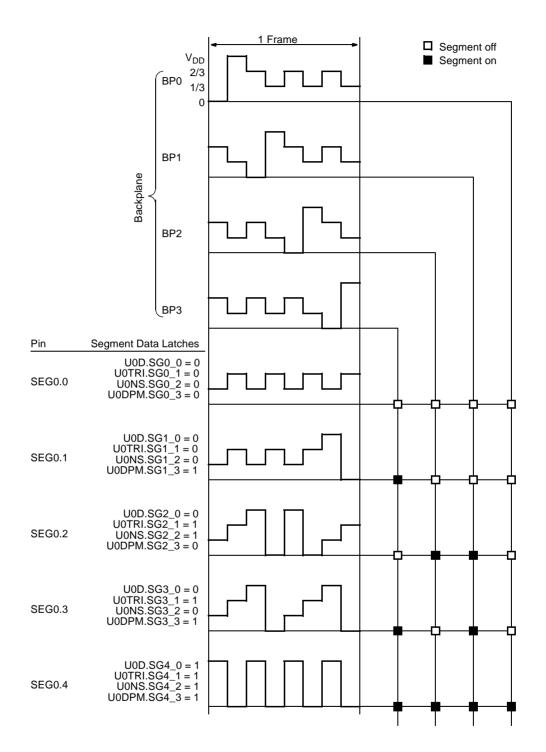

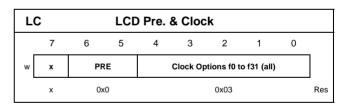

| 135  | 21.     | LCD Module                                         |

| 135  | 21.1.   | Principle of Operation                             |

| 138  | 21.2.   | Registers                                          |

| 138  | 21.3.   | Application Hints for Cascading LCD Modules        |

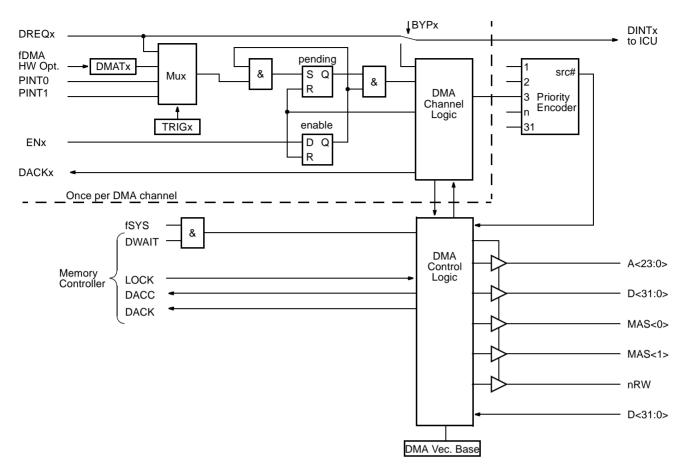

| 139  | 22.     | DMA Controller                                     |

| 139  | 22.1.   | Functions                                          |

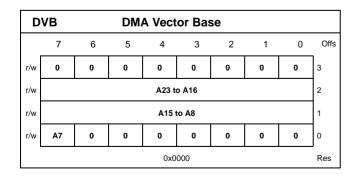

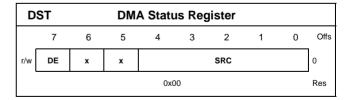

| 141  | 22.2.   | Registers                                          |

| 142  | 22.3.   | Principle of Operation                             |

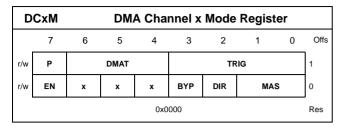

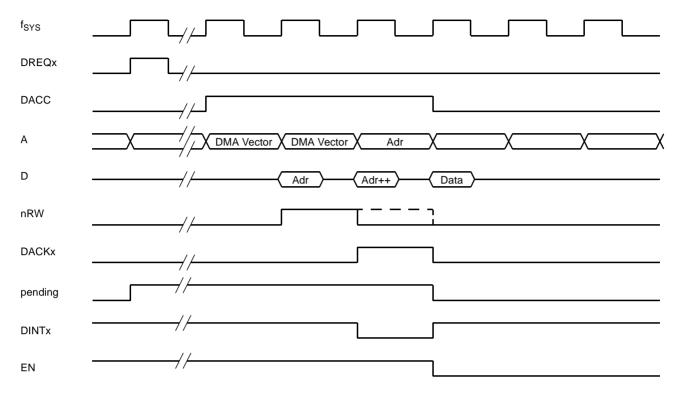

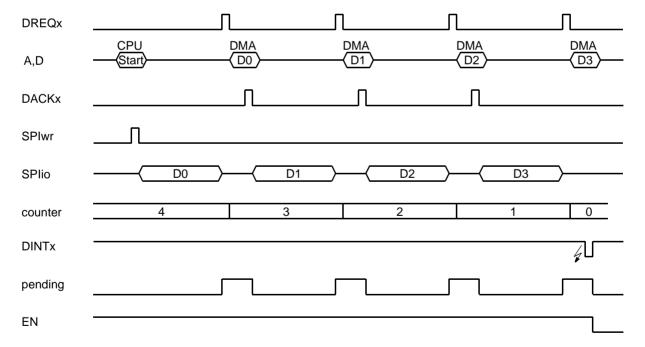

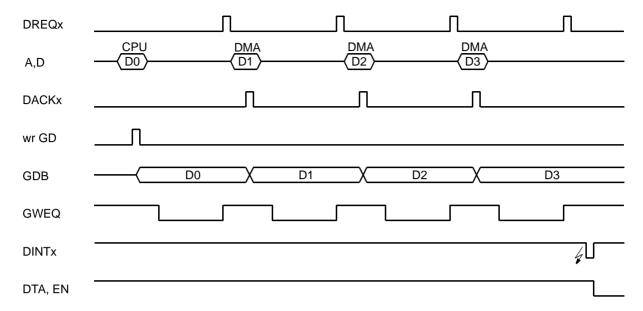

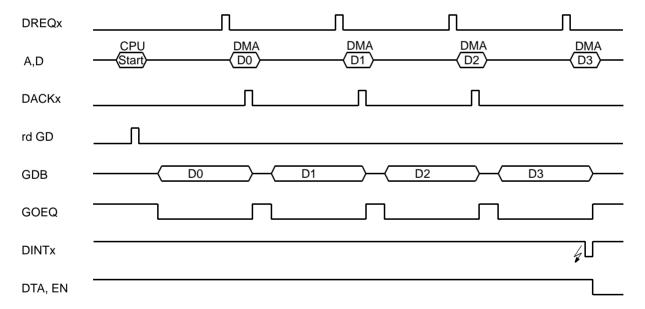

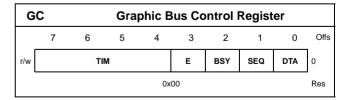

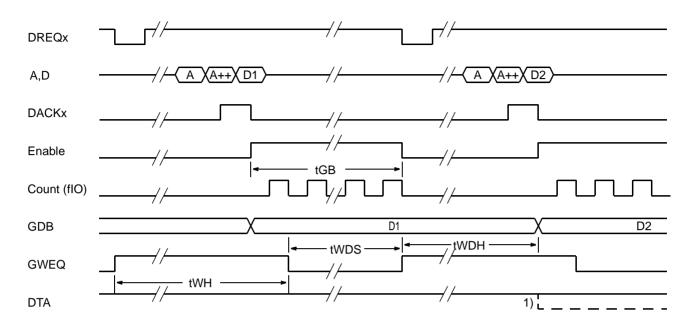

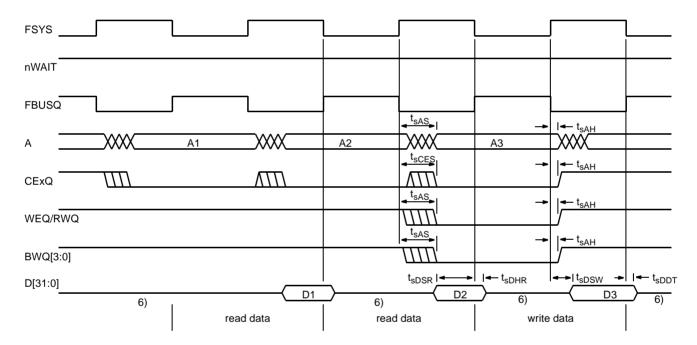

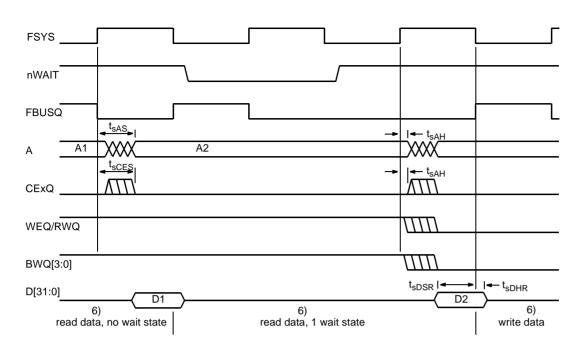

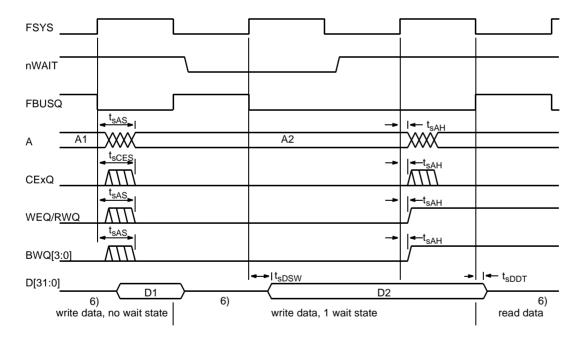

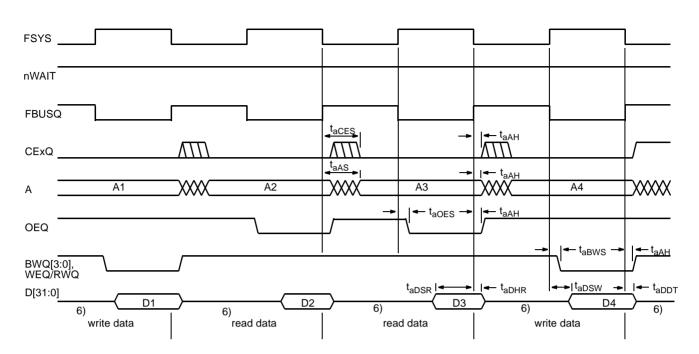

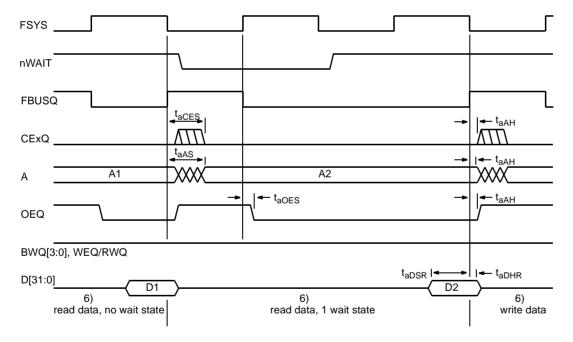

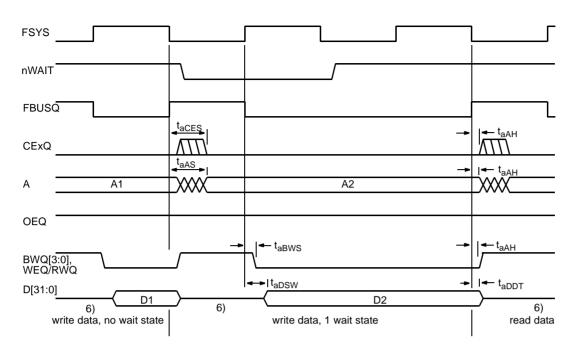

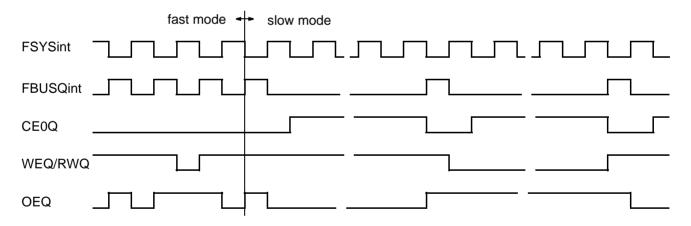

| 144  | 22.4.   | Timing Diagrams                                    |

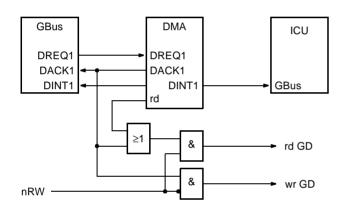

| 147  | 23.     | Graphic Bus Interface                              |

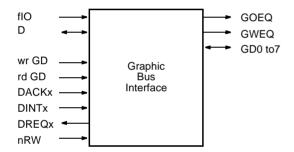

| 147  | 23.1.   | Functions                                          |

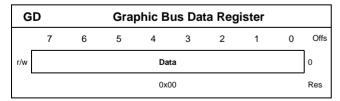

| 147  | 23.2.   | GB Registers                                       |

| 148  | 23.3.   | Principle of Operation                             |

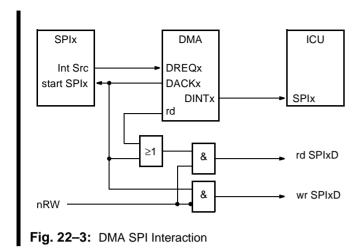

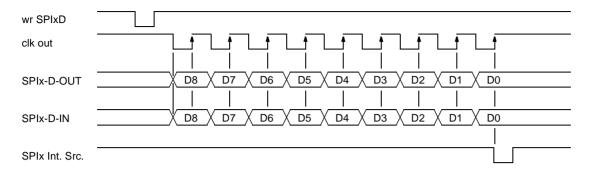

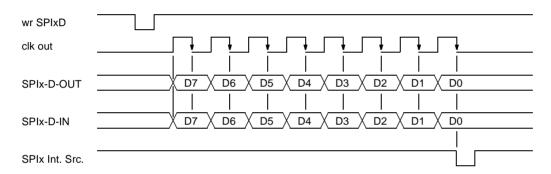

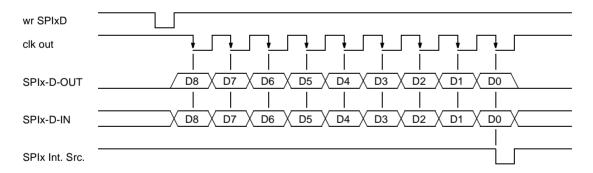

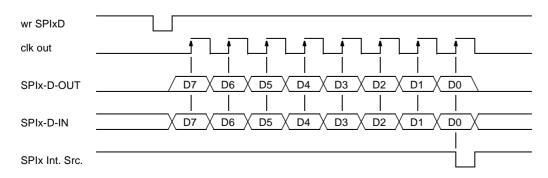

| 151  | 24.     | Serial Synchronous Peripheral Interface (SPI)      |

| 152  | 24.1.   | Principle of Operation                             |

| 153  | 24.2.   | Registers                                          |

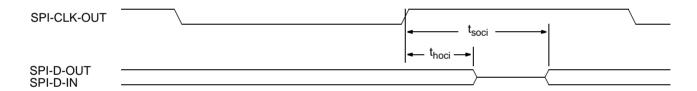

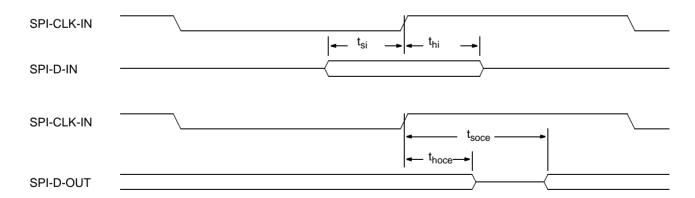

| 154  | 24.3.   | Timing                                             |

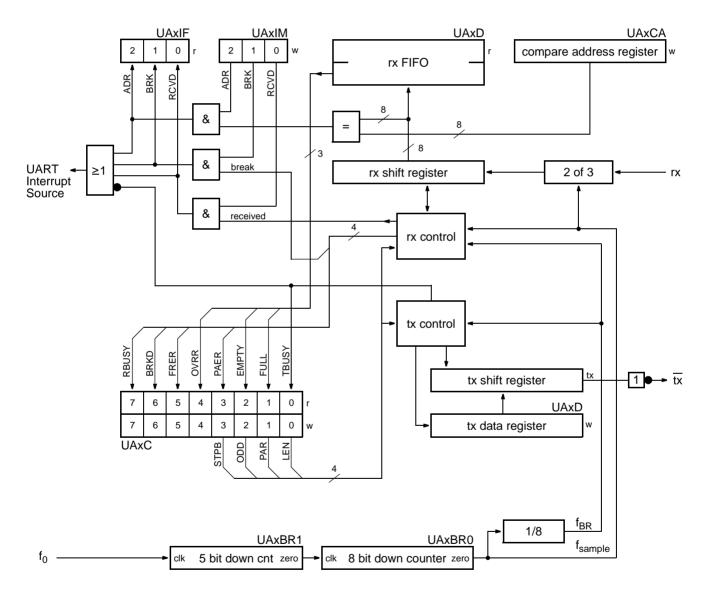

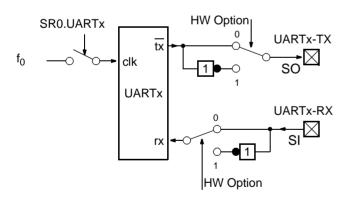

| 155  | 25.     | Universal Asynchronous Receiver Transmitter (UART) |

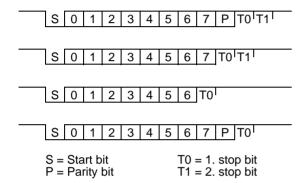

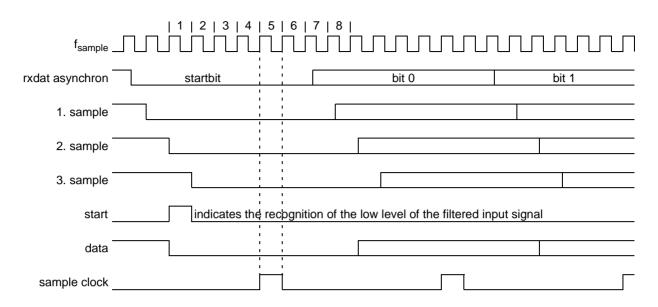

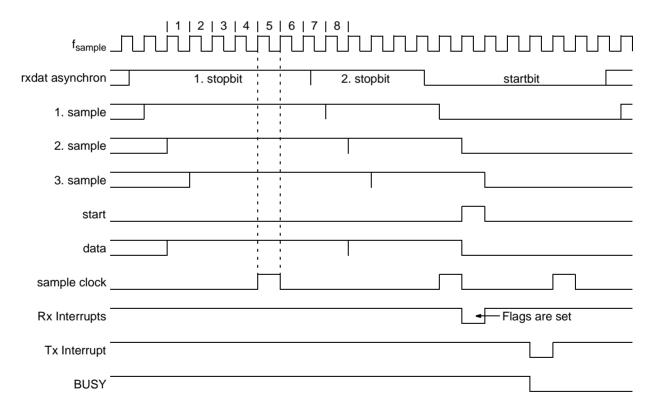

| 156  | 25.1.   | Principle of Operation                             |

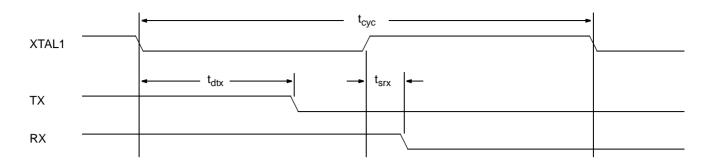

| 158  | 25.2.   | Timing                                             |

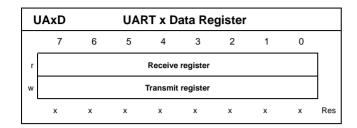

| 160  | 25.3.   | Registers                                          |

| 163  | 26.     | I2C-Bus Master Interface                           |

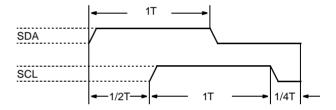

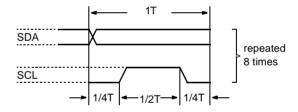

| 164  | 26.1.   | Principle of Operation                             |

| 166  | 26.2.   | Registers                                          |

| 169  | 27.     | CAN Manual                                         |

| 170  | 27.1.   | Abbreviations                                      |

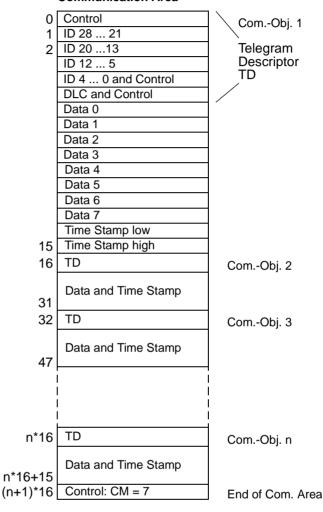

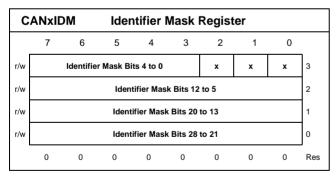

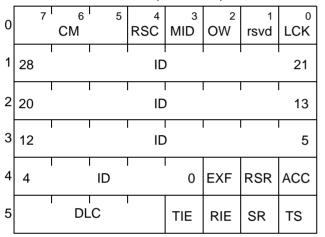

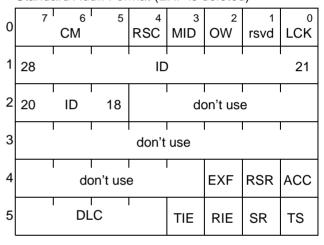

| 170  | 27.2.   | Functional Description                             |

| 176  | 27.3.   | Application Notes                                  |

|      |         |                                                    |

| Page | Section | Title                                                        |

|------|---------|--------------------------------------------------------------|

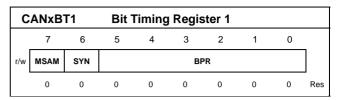

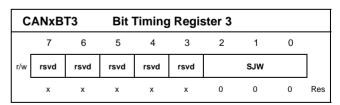

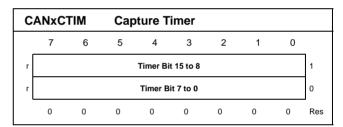

| 182  | 27.4.   | Bit Timing Logic                                             |

| 183  | 27.5.   | Bus Coupling                                                 |

| 185  | 28.     | DIGITbus System Description                                  |

| 185  | 28.1.   | Bus Signal and Protocol                                      |

| 185  | 28.2.   | Other Features                                               |

| 186  | 28.3.   | Standard Functions                                           |

| 187  | 28.4.   | Optional Functions                                           |

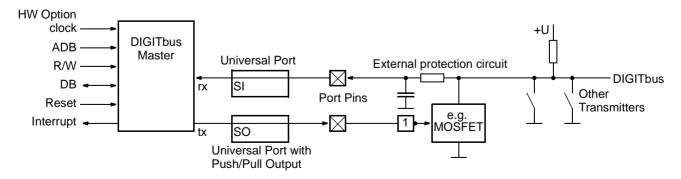

| 189  | 29.     | DIGITbus Master Module                                       |

| 189  | 29.1.   | Context                                                      |

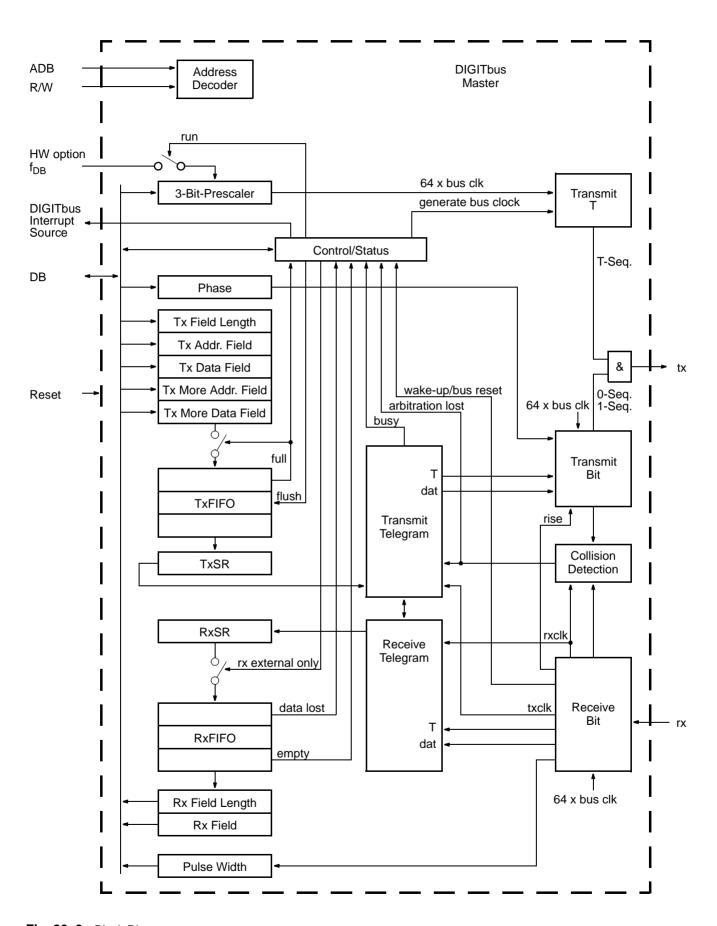

| 190  | 29.2.   | Functional Description                                       |

| 192  | 29.3.   | Registers                                                    |

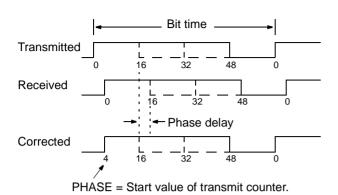

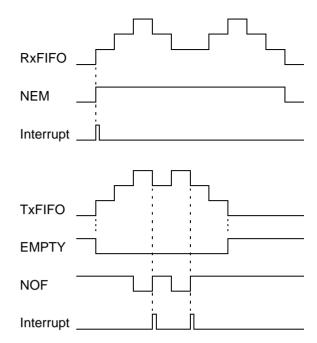

| 195  | 29.4.   | Principle of Operation                                       |

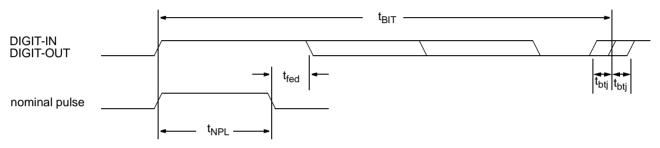

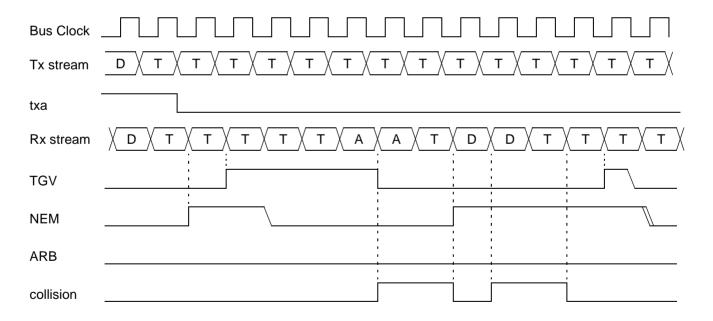

| 198  | 29.5.   | Timings                                                      |

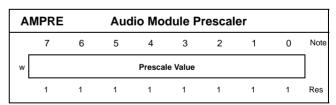

| 199  | 30.     | Audio Module (AM)                                            |

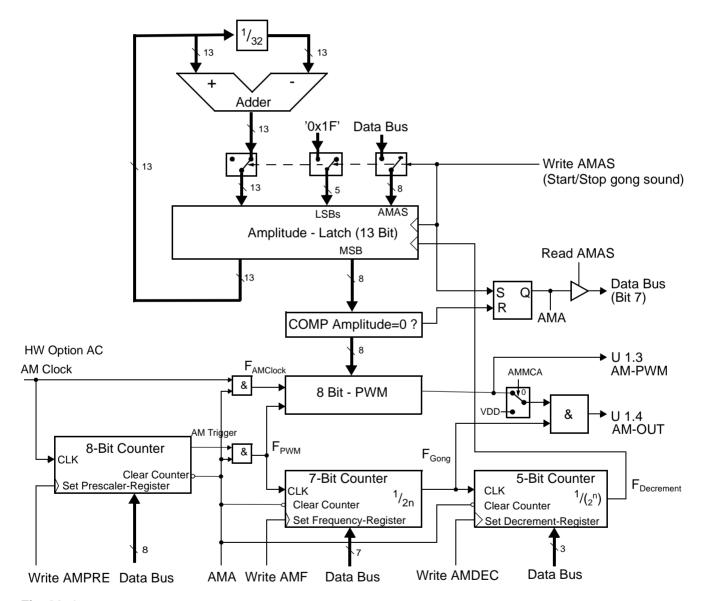

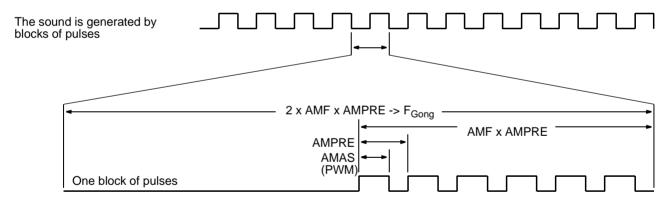

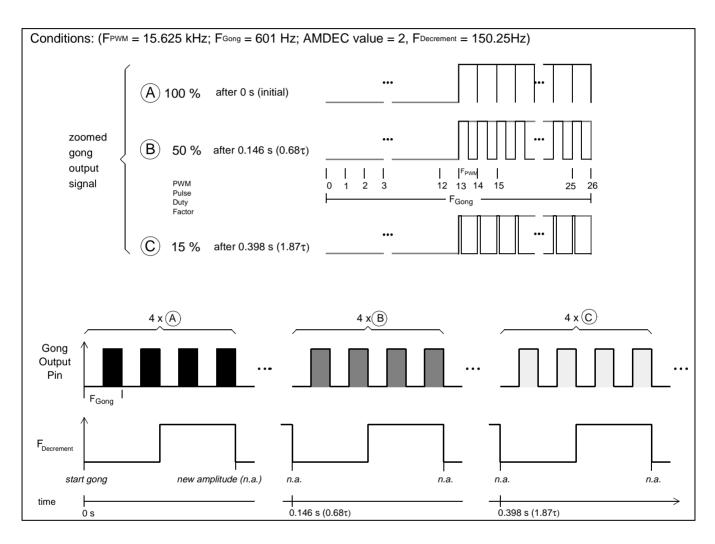

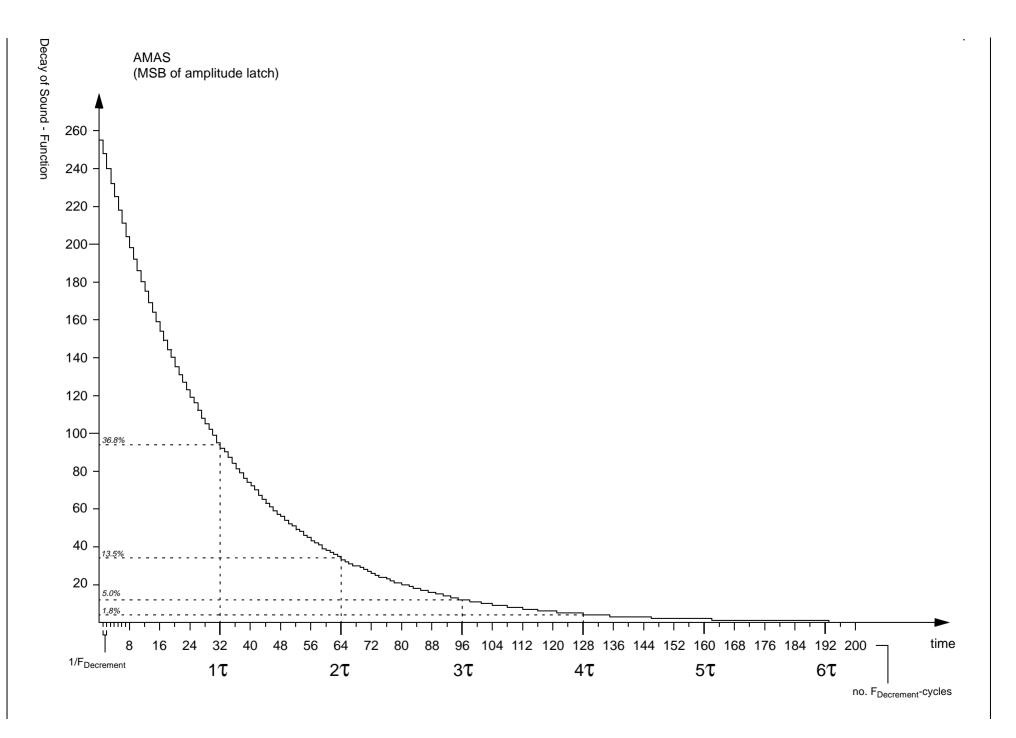

| 200  | 30.1.   | Functional Description                                       |

| 204  | 30.2.   | Registers                                                    |

| 205  | 31.     | Hardware Options                                             |

| 205  | 31.1.   | Functional Description                                       |

| 205  | 31.2.   | Listing of Dedicated Addresses of the Hardware Options Field |

| 206  | 31.3.   | HW Options Registers and Code                                |

| 211  | 32.     | Register Cross Reference Table                               |

| 211  | 32.1.   | 8-Bit I/O Region                                             |

| 217  | 32.2.   | 32-Bit I/O Region                                            |

| 219  | 33.     | Register Quick Reference                                     |

| 245  | 34.     | Control Register and Memory Interface                        |

| 245  | 34.1.   | Control Register CR                                          |

| 248  | 34.2.   | Memory Clock Delay Lines                                     |

| 249  | 34.3.   | External Memory Interface                                    |

| 255  | 35.     | Differences                                                  |

| 258  | 36.     | Data Sheet History                                           |

Page Section Title

6

# 1. Introduction

# Release Note: Revision bars indicate significant changes to the previous edition.

The chip contains timer/counters, interrupt controller, multi channel AD converter, stepper motor and LCD driver, CAN interfaces and PWM outputs and a crystal clock multiplying PLL.

# ■ 1.1. Features

Table 1–1: CDC32xxG-C Family Feature List

# This Device:

| Item                                                  | CDC3205G-C<br>EMU                                                          | CDC3207G-C<br>MCM Flash                                                       | CDC3272G-C<br>Mask ROM               | CDC3231G-C<br>Mask ROM              |  |

|-------------------------------------------------------|----------------------------------------------------------------------------|-------------------------------------------------------------------------------|--------------------------------------|-------------------------------------|--|

| Core                                                  |                                                                            |                                                                               |                                      |                                     |  |

| CPU                                                   | 32-bit ARM7TDM                                                             | II <sup>™</sup>                                                               |                                      |                                     |  |

| CPU-Active Operation Modes                            | DEEP SLOW, SL                                                              | .OW, FAST and PLL                                                             | -                                    |                                     |  |

| Power Saving Modes (CPU Inactive)                     | IDLE, WAKE and                                                             | IDLE, WAKE and STANDBY                                                        |                                      |                                     |  |

| CPU clock multiplication                              | PLL delivering up                                                          | PLL delivering up to 50MHz                                                    |                                      |                                     |  |

| EMI Reduction Mode                                    | selectable in PLL mode                                                     |                                                                               |                                      |                                     |  |

| Oscillators                                           | 4 to 5MHz Quartz                                                           | z and 20 to 50kHz Ir                                                          | nternal RC                           |                                     |  |

| RAM, zero wait state, 32 bit wide                     | 32kByte                                                                    |                                                                               | 16kByte                              | 6kByte                              |  |

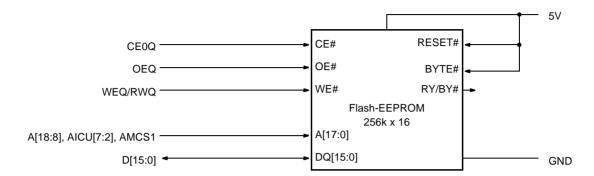

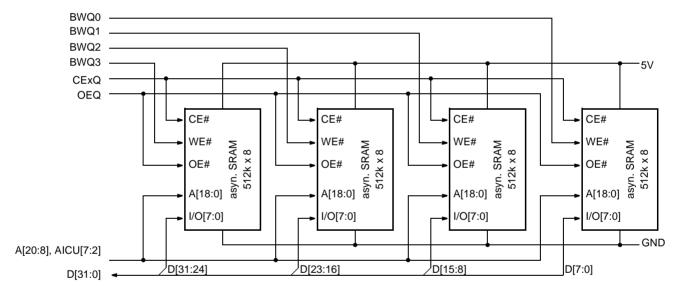

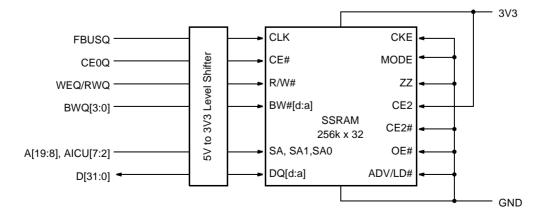

| ROM                                                   | ROMless, ext.<br>up to<br>4M x 32/<br>8M x 16,<br>int. 8-KByte<br>Boot ROM | 512-kByte Flash<br>(256K x 16) top<br>boot conf.,<br>int. 8-KByte<br>Boot ROM | 384kByte<br>(96K x 32/<br>192K x 16) | 128kByte<br>(32K x 32/<br>64K x 16) |  |

| Digital Watchdog                                      | ~                                                                          |                                                                               |                                      |                                     |  |

| Central Clock Divider                                 | V                                                                          |                                                                               |                                      |                                     |  |

| Interrupt Controller expanding IRQ                    | 40 inputs, 16 prio                                                         | ority levels                                                                  |                                      | 26 inputs, 16 priority levels       |  |

| Port Interrupts including Slope Selection             | 6 inputs                                                                   |                                                                               |                                      | 5 inputs                            |  |

| Port Wake-Up Inputs including Slope / Level Selection | 10 inputs                                                                  |                                                                               |                                      |                                     |  |

| Patch Module                                          | 10 ROM locations                                                           | s                                                                             |                                      |                                     |  |

| Boot System                                           | allows in-system downloading of external code to Flash memory via JTAG     |                                                                               |                                      |                                     |  |

| Device Lock Module                                    | Inhibits Access to<br>Lock settable by                                     | internal Firmware,<br>Customer                                                | -                                    |                                     |  |

Table 1-1: CDC32xxG-C Family Feature List, continued

# This Device:

|                                                                                           | Tino Borios.                                   |                                                                              |                          |                                                                     |  |  |

|-------------------------------------------------------------------------------------------|------------------------------------------------|------------------------------------------------------------------------------|--------------------------|---------------------------------------------------------------------|--|--|

| Item                                                                                      | CDC3205G-C<br>EMU                              | CDC3207G-C<br>MCM Flash                                                      | CDC3272G-C<br>Mask ROM   | CDC3231G-C<br>Mask ROM                                              |  |  |

| Analog                                                                                    |                                                |                                                                              |                          |                                                                     |  |  |

| Reset/Alarm                                                                               | Combined Input for Regulator Input Supervision |                                                                              |                          |                                                                     |  |  |

| Clock and Supply Supervision                                                              |                                                |                                                                              |                          |                                                                     |  |  |

| 10-bit ADC, charge balance type                                                           | 16 channels (eac                               | h selectable as digi                                                         | tal input)               |                                                                     |  |  |

| ADC Reference                                                                             | VREF Pin, P1.0 F                               | Pin, P1.1 Pin or VR                                                          | EFINT Internal Band      | lgap selectable                                                     |  |  |

| Comparators                                                                               |                                                | P06COMP with 1/2 AVDD reference,<br>WAITCOMP with Internal Bandgap reference |                          |                                                                     |  |  |

| LCD                                                                                       | Internal processin                             | g of all analog volta                                                        | ages for the LCD dri     | ver                                                                 |  |  |

| Communication                                                                             |                                                |                                                                              |                          |                                                                     |  |  |

| DMA                                                                                       | 3 DMA Channels,<br>Bus interface, SP           | one each for servi<br>10 and SPI1                                            | ng the Graphics          | -                                                                   |  |  |

| UART                                                                                      | 2: UART0 and UA                                | ART1                                                                         |                          | UART0                                                               |  |  |

| Synchronous Serial Peripheral Interfaces                                                  | 2: SPI0 and SPI1                               | , DMA supported                                                              |                          |                                                                     |  |  |

| Full CAN modules V2.0B<br>with 512-byte object RAM each<br>(LCAN000E)                     | 4: CAN0, CAN1, 0                               | CAN2 and CAN3                                                                | 2: CAN0 and<br>CAN1      | 1: CAN0                                                             |  |  |

| DIGITbus                                                                                  | 1 master module                                |                                                                              |                          | -                                                                   |  |  |

| I <sup>2</sup> C                                                                          | 2 master modules: I2C0 and I2C1                |                                                                              |                          | I2C0                                                                |  |  |

| Graphics Bus Interface                                                                    | 8-bit data bus, DN<br>EPSON SED 156            | //A supported, e.g. f<br>0 LCD controller                                    | for connection of        | -                                                                   |  |  |

| Input & Output                                                                            |                                                |                                                                              |                          |                                                                     |  |  |

| Universal Ports selectable as 4:1 mux LCD<br>Segment/Backplane lines or Digital I/O Ports | up to 52 I/O or 48<br>individually config      | LCD segment lines<br>urable as I/O or LC                                     | s (=192 segments),<br>CD | up to 50 I/O or<br>46LCD seg-<br>ment lines<br>(=184 seg-<br>ments) |  |  |

| Universal Port Slew Rate                                                                  | SW selectable                                  |                                                                              |                          |                                                                     |  |  |

| Stepper Motor Control Modules with High-<br>Current Ports                                 | 7 Modules,<br>32 dl/dt controlled              | l ports                                                                      |                          | 4 Modules<br>23 dl/dt con-<br>trolled ports                         |  |  |

| PWM Modules, each configurable as two 8-bit PWMs or one 16-bit PWM                        | 6 Modules: PWMi<br>PWM8/9 and PW               | 0/1, PWM2/3, PWN<br>M10/11                                                   | 14/5, PWM6/7,            | 5 Modules:<br>PWM0/1,<br>PWM2/3,<br>PWM4/5,<br>PWM6/7,<br>PWM8/9    |  |  |

| Phase-Frequency Modulator                                                                 | 2: PFM0 and PFN                                | //1                                                                          |                          | -                                                                   |  |  |

| Audio Module with auto-decay                                                              | <b>v</b>                                       |                                                                              |                          |                                                                     |  |  |

| SW selectable Clock outputs                                                               | 2                                              |                                                                              |                          |                                                                     |  |  |

Table 1-1: CDC32xxG-C Family Feature List, continued

# This Device:

| Item                         | CDC3205G-C                                                | CDC3207G-C | CDC3272G-C | CDC3231G-C |

|------------------------------|-----------------------------------------------------------|------------|------------|------------|

|                              | EMU                                                       | MCM Flash  | Mask ROM   | Mask ROM   |

| Polling / Flash Timer Output | 1 High-Current Port output operable in Power Saving Modes |            |            |            |

Micronas

Table 1-1: CDC32xxG-C Family Feature List, continued

# This Device:

| Item                                                          | CDC3205G-C<br>EMU                                            | CDC3207G-C<br>MCM Flash     | CDC3272G-C<br>Mask ROM | CDC3231G-C<br>Mask ROM |  |  |

|---------------------------------------------------------------|--------------------------------------------------------------|-----------------------------|------------------------|------------------------|--|--|

| Timers & Counters                                             |                                                              |                             |                        |                        |  |  |

| 16-bit free running counters with Capture/<br>Compare modules | CCC0 with 4 CAI<br>CCC1 with 2 CAI                           |                             |                        | CCC0 with 4<br>CAPCOM  |  |  |

| 16-bit timers                                                 | 1: T0                                                        |                             |                        |                        |  |  |

| 8-bit timers                                                  | 4: T1, T2, T3 and                                            | 1 T4                        |                        |                        |  |  |

| Real Time Clock, Delivering Hours, Minutes and Seconds        | V                                                            |                             |                        |                        |  |  |

| Miscellaneous                                                 |                                                              |                             |                        |                        |  |  |

| Scalable layout in CAN, RAM and ROM                           | -                                                            | ~                           |                        |                        |  |  |

| Various randomly selectable HW options                        | Set by copy from user program storage during system start-up |                             |                        |                        |  |  |

| JTAG test interface                                           | ~                                                            | allows Flash<br>programming | ~                      |                        |  |  |

| On Chip Debug Aids                                            | Embedded<br>Trace Module,<br>JTAG                            | JTAG                        |                        |                        |  |  |

| Core Bond-Out                                                 | V                                                            | -                           |                        |                        |  |  |

| Supply Voltage                                                | 3.5 to 5.5V (limite                                          | ed I/O performance          | below 4.5V)            |                        |  |  |

| Case Temperature Range                                        | 0 to +70C                                                    | -40 to +105C                |                        |                        |  |  |

| Package                                                       |                                                              | •                           |                        |                        |  |  |

| Туре                                                          | Ceramic<br>257PGA                                            | PMQFP128-2<br>0.5mm pitch   |                        |                        |  |  |

| Bonded Pins                                                   | 256                                                          | 128                         | 126                    | 111                    |  |  |

$<sup>\</sup>mathsf{ARM}^{\$}$  and  $\mathsf{Thumb}^{\$}$  are the registered trademarks of ARM Limited. ARM7TDMITM is the trademark of ARM Limited.

Serial Synchronous Peripheral Interface

# 1.2. Abbreviations

SM SPI

| ADC<br>AM<br>CAN<br>CAPCOM<br>CCC<br>CPU<br>DMA<br>ERM<br>ETM<br>I2C | Analog-to-Digital Converter Audio Module Controller Area Network Module Capture/Compare Module Capture/Compare Counter Central Processing Unit Direct Memory Access Module EMI Reduction Mode Embedded Trace Module I <sup>2</sup> C Interface Module | T<br>UART<br>WAITCOMP | Timer<br>Universal Asynchronous Receiver Transmitter<br>Wait Comparator |

|----------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------|-------------------------------------------------------------------------|

|                                                                      | 0                                                                                                                                                                                                                                                     |                       |                                                                         |

| LCD                                                                  | Liquid Crystal Display Module                                                                                                                                                                                                                         |                       |                                                                         |

| P06COMP                                                              | P0.6 Alarm Comparator                                                                                                                                                                                                                                 |                       |                                                                         |

| PWM                                                                  | Pulse Width Modulator Module                                                                                                                                                                                                                          |                       |                                                                         |

| SM                                                                   | Stepper Motor Control Module                                                                                                                                                                                                                          |                       |                                                                         |

|                                                                      |                                                                                                                                                                                                                                                       |                       |                                                                         |

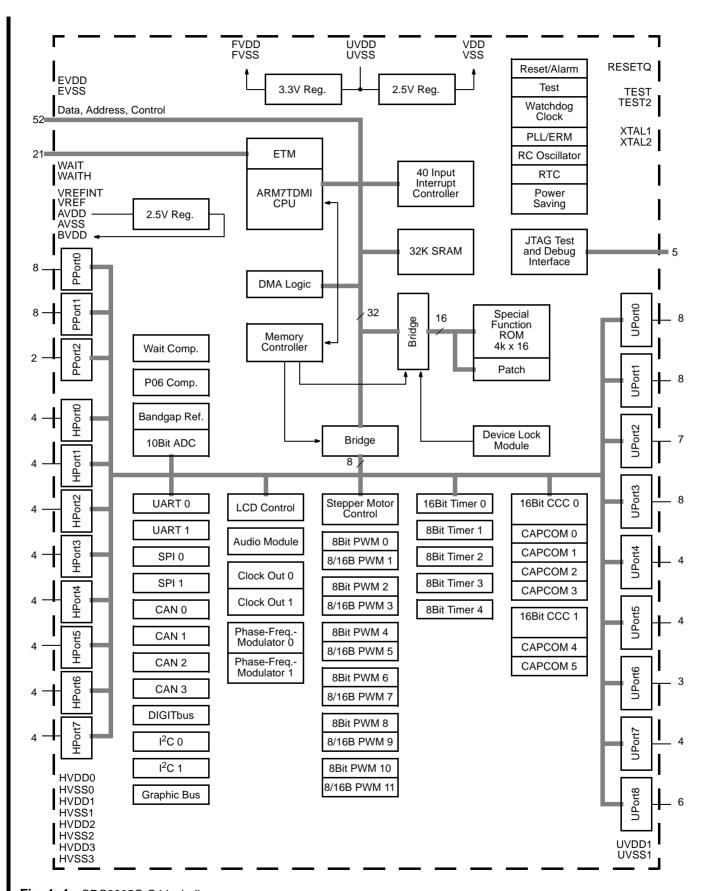

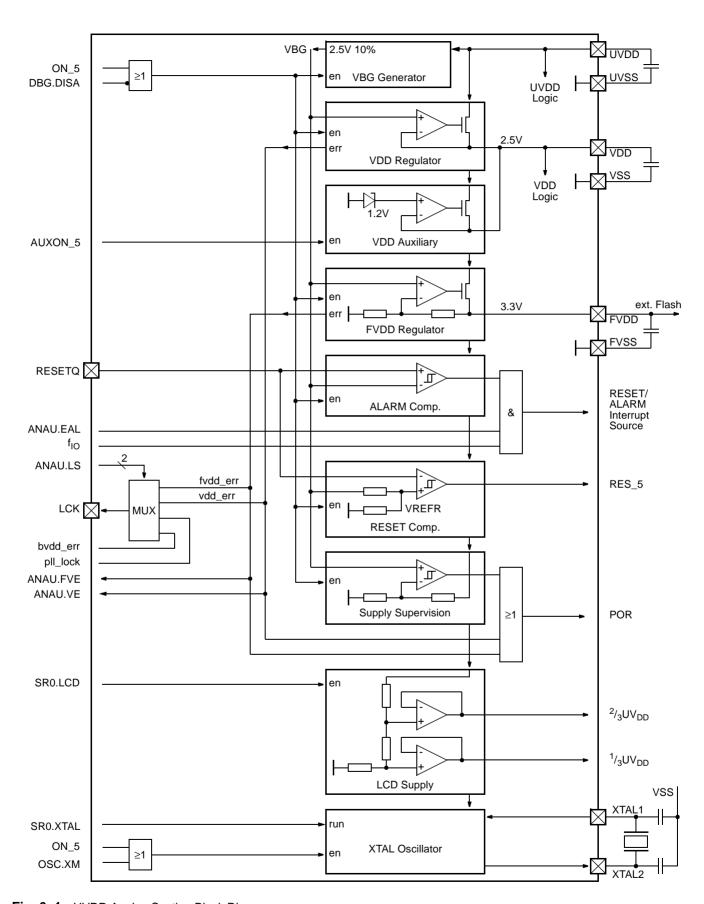

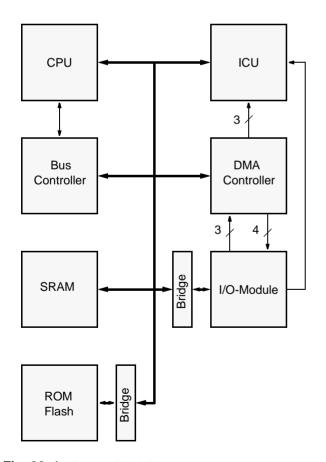

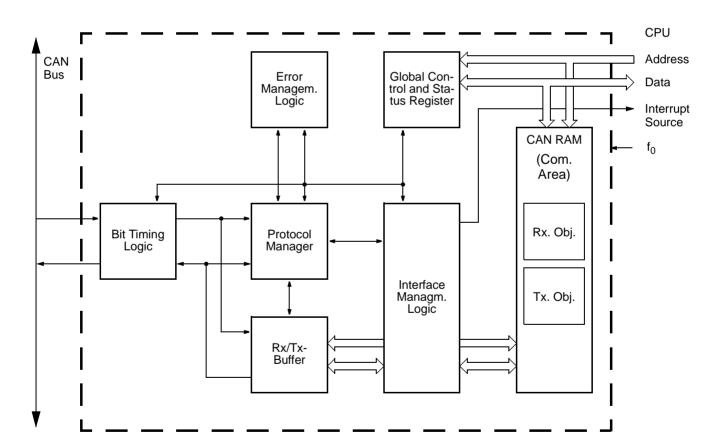

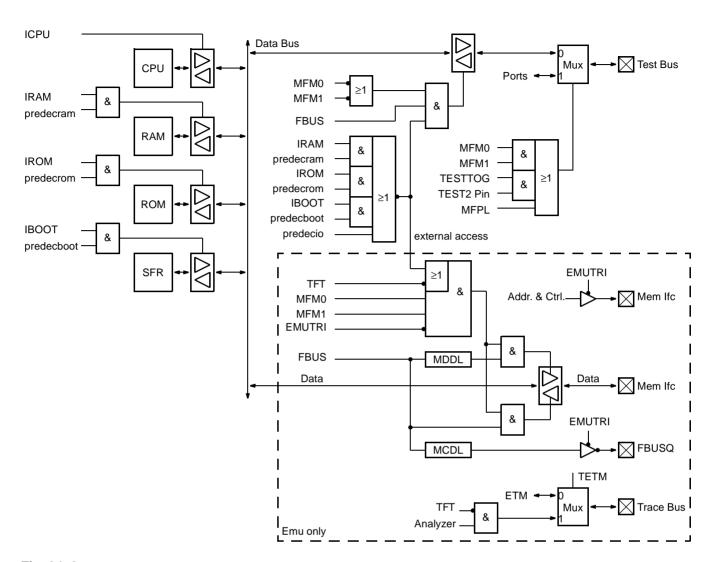

# 1.3. Block Diagram

Fig. 1–1: CDC3205G-C block diagram

# 2. Packages and Pins

# 2.1. Pin Assignment

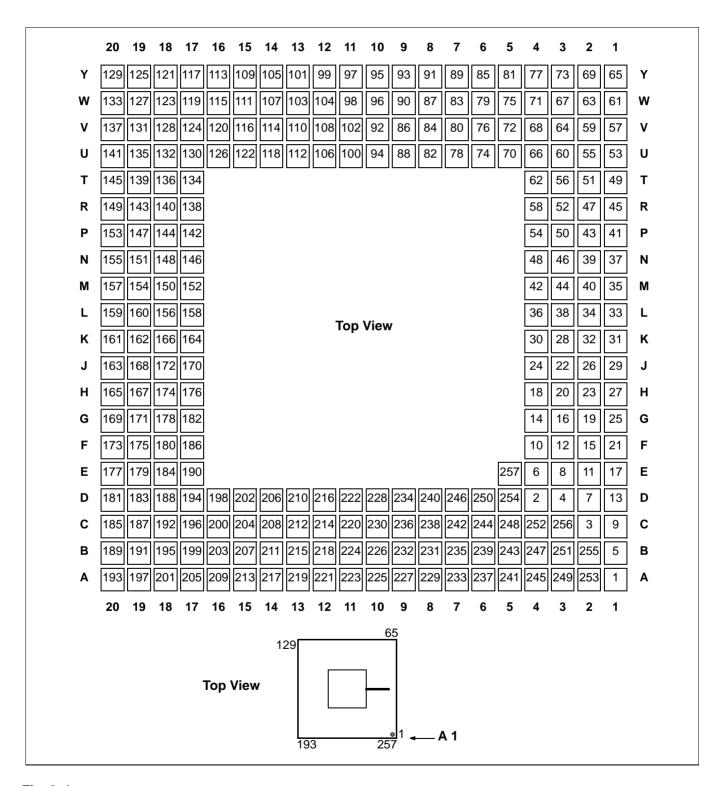

Fig. 2-1: Pin Map of CPGA257 Package

Table 2–1: Pin Assignment for CPGA257 Package

| CPGA257 ∞ |      |     | Pin Functions     |                  |                |        |  |  |  |

|-----------|------|-----|-------------------|------------------|----------------|--------|--|--|--|

| Pin       | Co-  | 0.  | Basic             | Port             | Port           | LCD    |  |  |  |

| No.       | ord. | P P | Basic<br>Function | Special In       | Special Out    | Mode   |  |  |  |

| 1         | A1   | 4   | U5.3/GD3          | CC4-IN           | CC4-OUT        | SEG5.3 |  |  |  |

| 2         | D4   | 5   | U5.2/GD2          | SDA1             | SDA1           | SEG5.2 |  |  |  |

| 3         | C2   | 6   | U5.1/GD1          | SCL1             | SCL1           | SEG5.1 |  |  |  |

| 4         | D3   | 7   | U5.0/GD0          | OOLI             | PFM0           | SEG5.0 |  |  |  |

| 5         | B1   |     | U2.1              | CDAO/CANO DVAVDO | SDA0           | SEG3.0 |  |  |  |

|           |      | 8   | 1                 | SDA0/CAN0-RX/WP6 |                |        |  |  |  |

| 6         | E4   | 9   | U2.0              | SCL0             | SCL0/CAN0-TX   | SEG2.0 |  |  |  |

| 7         | D2   | 10  | U1.7              | PINT0/WP0        | PFM0           | SEG1.7 |  |  |  |

| 8         | E3   | 11  | U1.6              | PINT1            | CO0/INTRES     | SEG1.6 |  |  |  |

| 9         | C1   | 12  | U1.5              | PINT2            | CO0Q/CO1       | SEG1.5 |  |  |  |

| 10        | F4   | 13  | TEST              |                  |                |        |  |  |  |

| 11        | E2   | 14  | RESETQ/AL         | ARMQ             |                |        |  |  |  |

| 12        | F3   | 15  | XTAL2             |                  |                |        |  |  |  |

| 13        | D1   | 16  | XTAL1             |                  |                |        |  |  |  |

| 14        | G4   | 17  | VSS               |                  |                |        |  |  |  |

| 15        | F2   | 18  | VDD               |                  |                |        |  |  |  |

| 16        | G3   | 19  | U1.4              | 1                | ITSTOUT/AM-OUT | SEG1.4 |  |  |  |

| 17        | E1   | 20  | U1.3              | WP3              | MTO/AM-PWM     | SEG1.3 |  |  |  |

| 18        | H4   | 21  | U1.2              | MTI/ITSTIN       | T0-OUT/INTRES  | SEG1.3 |  |  |  |

| 19        |      |     | U1.1              | WITH STIN        | T1-OUT         |        |  |  |  |

|           | G2   | 22  |                   |                  |                | SEG1.1 |  |  |  |

| 20        | H3   | 23  | U1.0              |                  | T2-OUT         | SEG1.0 |  |  |  |

| 21        | F1   | 24  | U0.7              | WP4              | T3-OUT         | SEG0.7 |  |  |  |

| 22        | J3   | 25  | U0.6              | CC3-IN           | T4-OUT/CC3-OUT | SEG0.6 |  |  |  |

| 23        | H2   | 26  | U0.5              | PINT4            | CC3-OUT        | SEG0.5 |  |  |  |

| 24        | J4   | 27  | U0.4              | PINT5            | CO1            | SEG0.4 |  |  |  |

| 25        | G1   | 28  | U0.3              |                  | PWM0           | SEG0.3 |  |  |  |

| 26        | J2   | 29  | U0.2              |                  | PWM1           | SEG0.2 |  |  |  |

| 27        | H1   | 30  | U0.1              | +                | PWM2           | SEG0.1 |  |  |  |

| 28        | КЗ   | 31  | U0.0              | +                | PWM3           | SEG0.0 |  |  |  |

| 29        | J1   | -   | D31               |                  | 1 111110       | 0200.0 |  |  |  |

| 30        | K4   |     | D30               |                  |                |        |  |  |  |

|           |      |     |                   |                  |                |        |  |  |  |

| 31        | K1   |     | D29               |                  |                |        |  |  |  |

| 32        | K2   |     | D28               |                  |                |        |  |  |  |

| 33        | L1   |     | D27               |                  |                |        |  |  |  |

| 34        | L2   |     | D26               |                  |                |        |  |  |  |

| 35        | M1   |     | D25               |                  |                |        |  |  |  |

| 36        | L4   |     | EVDD8             |                  |                |        |  |  |  |

| 37        | N1   |     | EVSS8             |                  |                |        |  |  |  |

| 38        | L3   |     | D24               |                  |                |        |  |  |  |

| 39        | N2   |     | D23               |                  |                |        |  |  |  |

| 40        | M2   |     | D22               |                  |                |        |  |  |  |

| 41        | P1   |     | D21               |                  |                |        |  |  |  |

| 42        | M4   |     | D21               |                  |                |        |  |  |  |

|           |      | -   |                   |                  |                |        |  |  |  |

| 43        | P2   |     | D19               |                  |                |        |  |  |  |

| 44        | M3   |     | D18               |                  |                |        |  |  |  |

| 45        | R1   |     | D17               |                  |                |        |  |  |  |

| 46        | N3   |     | D16               |                  |                |        |  |  |  |

| 47        | R2   |     | D15               |                  |                |        |  |  |  |

| 48        | N4   |     | D7                |                  |                |        |  |  |  |

| 49        | T1   |     | D14               |                  |                |        |  |  |  |

| 50        | P3   |     | EVDD7             |                  |                |        |  |  |  |

| 51        | T2   |     | EVSS7             |                  |                |        |  |  |  |

| 52        | R3   | -   | D6                |                  |                |        |  |  |  |

| 53        | U1   |     | D13               |                  |                |        |  |  |  |

|           |      | -   | 1                 |                  |                |        |  |  |  |

| 54        | P4   |     | D5                |                  |                |        |  |  |  |

| 55        | U2   |     | D12               |                  |                |        |  |  |  |

| 56        | T3   |     | D4                |                  |                |        |  |  |  |

| 57        | V1   |     | D11               |                  |                |        |  |  |  |

| 58        | R4   |     | D3                |                  |                |        |  |  |  |

| 59        | V2   |     | D10               |                  |                |        |  |  |  |

| 60        | U3   |     | D2                |                  |                |        |  |  |  |

| 61        | W1   | -   | D9                |                  |                |        |  |  |  |

| 62        | T4   |     | D1                |                  |                |        |  |  |  |

|           | W2   | -   | D8                |                  |                |        |  |  |  |

|           |      |     | IDO               |                  |                |        |  |  |  |

| 63<br>64  | VV2  | +   | EVDD6             |                  |                |        |  |  |  |

Table 2–1: Pin Assignment for CPGA257 Package

|            | 257         | - 2                | D!-               |                    | Functions           | li on       |

|------------|-------------|--------------------|-------------------|--------------------|---------------------|-------------|

| Pin<br>No. | Co-<br>ord. | PQFP128<br>Pin No. | Basic<br>Function | Port<br>Special In | Port<br>Special Out | LCD<br>Mode |

| 65         | Y1          |                    | EVSS6             |                    | •                   |             |

| 66         | U4          |                    | D0                |                    |                     |             |

| 67         | W3          |                    | OEQ               |                    |                     |             |

| 68         | V4          |                    | CE0Q              |                    |                     |             |

| 69         | Y2          |                    | BWQ3              |                    |                     |             |

| 70         | U5          |                    | BWQ2              |                    |                     |             |

| 71         | W4          |                    | BWQ1              |                    |                     |             |

| 72         | V5          |                    | BWQ0              |                    |                     |             |

| 73         | Y3          |                    | EMUTRI            |                    |                     |             |

| 74         | U6          |                    | ABORT             |                    |                     |             |

| 75         | W5          |                    | EXTERN0           |                    |                     |             |

| 76         | V6          |                    | EXTERN1           |                    |                     |             |

| 77         | Y4          | 32                 | H7.3              | SME-COMP3          | SME1+/PWM4          |             |

| 78         | U7          | 33                 | H7.2              | SME-COMP2          | SME1-/PWM6          |             |

| 79         | W6          | 34                 | H7.1              | SME-COMP1          | SME2+/PWM8          |             |

| 80         | V7          | 35                 | H7.0              | SME-COMP0          | SME2-/PWM9          |             |

| 81         | Y5          | 36                 | HVDD2             |                    | •                   |             |

| 82         | U8          | 37                 | HVSS2             |                    |                     |             |

| 83         | W7          | 38                 | H6.3              |                    | PWM8                |             |

| 84         | V8          | 39                 | H6.2              |                    | PWM9                |             |

| 85         | Y6          | 40                 | H6.1              |                    | PWM10               | 1           |

| 86         | V9          | 41                 | H6.0              |                    | PWM11               | 1           |

| 87         | W8          | 42                 | H5.3              | SMD-COMP3          | SMD1+               | 1           |

| 88         | U9          | 43                 | H5.2              | SMD-COMP2          | SMD1-               | 1           |

| 89         | Y7          | 44                 | HVDD0             | 1                  |                     |             |

| 90         | W9          | 45                 | HVSS0             |                    |                     |             |

| 91         | Y8          | 46                 | H5.1              | SMD-COMP1          | SMD2+               |             |

| 92         | V10         | 47                 | H5.0              | SMD-COMP0          | SMD2-               |             |

| 93         | Y9          | 48                 | H4.3              | SMA-COMP3          | SMA1+               |             |

| 94         | U10         | 49                 | H4.2              | SMA-COMP2          | SMA1-               |             |

| 95         | Y10         | 50                 | H4.1              | SMA-COMP1          | SMA2+               |             |

| 96         | W10         | 51                 | H4.0              | SMA-COMP0          | SMA2-               |             |

| 97         | Y11         | 52                 | H3.3              | SMB-COMP3          | SMB1+               | -           |

| 98         | W11         | 53                 | H3.2              | SMB-COMP2          | SMB1-               | -           |

| 99         | Y12         | 54                 | H3.1              | SMB-COMP1          | SMB2+               | _           |

| 100        | U11         | 55                 | H3.0              | SMB-COMP0          | SMB2-               |             |

| 101        | Y13         | 56                 | H2.3              | SMC-COMP3          | SMC1+               | -           |

| 102        | V11         | 57                 | H2.2              | SMC-COMP2          | SMC1-               |             |

| 103        | W13         | 58                 | HVDD1             | SIVIC-COIVIF2      | SIVIC 1-            |             |

| 103        | W12         | 59                 | HVSS1             |                    |                     |             |

| 105        | Y14         |                    | H2.1              | EMC COMP4          | IcMC2.              | -           |

|            |             | 60                 |                   | SMC-COMP1          | SMC2+               | _           |

| 106        | U12<br>W14  | 61                 | H2.0              | SMC-COMP0          | SMC2-               |             |

| 107        |             | 62                 | H1.3              | SMF-COMP3          | SMF1+               | -           |

| 108        | V12         | 63                 | H1.2              | SMF-COMP2          | SMF1-               |             |

| 109        | Y15         | 64                 | H1.1              | SMF-COMP1          | SMF2+               |             |

| 110        | V13         | 65                 | H1.0              | SMF-COMP0          | SMF2-               |             |

| 111        | W15         | 66                 | HVDD3             |                    |                     |             |

| 112        | U13         | 67                 | HVSS3             | lone oction        | 01404 - /014/144    |             |

| 113        | Y16         | 68                 | H0.3              | SMG-COMP3          | SMG1+/PWM1          | _           |

| 114        | V14         | 69                 | H0.2              | SMG-COMP2          | SMG1-/PWM3/POL      |             |

| 115        | W16         | 70                 | H0.1              | SMG-COMP1          | SMG2+/PWM5          |             |

| 116        | V15         | 71                 | H0.0              | SMG-COMP0          | SMG2-/PWM7          |             |

| 117        | Y17         |                    | nTRST             |                    |                     |             |

| 118        | U14         |                    | ETDI              |                    |                     |             |

| 119        | W17         |                    | ETMS              |                    |                     |             |

| 120        | V16         |                    | ETCK              |                    |                     |             |

| 121        | Y18         |                    | ETDO              |                    |                     |             |

| 122        | U15         |                    | ABE               |                    |                     |             |

| 123        | W18         |                    | CE1Q              |                    |                     |             |

| 124        | V17         |                    | FBUSQ             |                    |                     |             |

| 125        | Y19         |                    | AMCS1             |                    |                     |             |

| 126        | U16         |                    | AICU2             |                    |                     |             |

| 127        | W19         |                    | AICU3             |                    |                     |             |

| 128        | V18         |                    | EVSS5             |                    |                     |             |

**Table 2–1:** Pin Assignment for **CPGA257** Package

| CPGA       | 257         | œ.                                           |                   | Pin Functions      |                     |             |

|------------|-------------|----------------------------------------------|-------------------|--------------------|---------------------|-------------|

| Pin<br>No. | Co-<br>ord. | PQFP128<br>Pin No.                           | Basic<br>Function | Port<br>Special In | Port<br>Special Out | LCD<br>Mode |

| 129        | Y20         |                                              | EVDD5             |                    |                     |             |

| 130        | U17         |                                              | AICU4             |                    |                     |             |

| 131        | V19         |                                              | AICU5             |                    |                     |             |

| 132        | U18         |                                              | AICU6             |                    |                     |             |

| 133        | W20         |                                              | AICU7             |                    |                     |             |

| 134        | T17         |                                              | A8                |                    |                     |             |

| 135        | U19         |                                              | A18               |                    |                     |             |

| 136        | T18         |                                              | A19               |                    |                     |             |

| 137        | V20         | <u> </u>                                     | EVDD4             |                    |                     |             |

| 138        | R17         |                                              | EVSS4             |                    |                     |             |

| 139        | T19         |                                              | WEQ/RWQ           |                    |                     |             |

| 140        | R18         | <u> </u>                                     | A9                |                    |                     |             |

| 141        | U20         | <u> </u>                                     | A10               |                    |                     |             |

| 142        | P17         | <u> </u>                                     | A11               |                    |                     |             |

| 143        | R19         | <u> </u>                                     | A12               |                    |                     |             |

| 144        | P18         | <u> </u>                                     | A13               |                    |                     |             |

| 145        | T20         |                                              | A14               |                    |                     |             |

| 146        | N17         | <u> </u>                                     | A15               |                    |                     |             |

| 147        | P19         | <u> </u>                                     | EVDD3             |                    |                     |             |

| 148        | N18         | <u> </u>                                     | EVSS3             |                    |                     |             |

| 149        | R20         |                                              | A16               |                    |                     |             |

| 150        | M18         | <u> </u>                                     | A17               |                    |                     |             |

| 151        | N19         | <u> </u>                                     | A20               |                    |                     |             |

| 152        | M17         | <u> </u>                                     | A21               |                    |                     |             |

| 153        | P20         | <u> </u>                                     | A22               |                    |                     |             |

| 154        | M19         | <u> </u>                                     | A23               |                    |                     |             |

| 155        | N20         | <u> </u>                                     | AMCM21            |                    |                     |             |

| 156        | L18         | <u> </u>                                     | AMCM22            |                    |                     |             |

| 157        | M20         | <u> </u>                                     | EVDD2             |                    |                     |             |

| 158        | L17         | <u> </u>                                     | EVSS2<br>AMCM23   |                    |                     |             |

| 159        | L20         |                                              |                   |                    |                     |             |

| 160        | L19         | <u> </u>                                     | SEQ               |                    |                     |             |

| 161<br>162 | K20<br>K19  | <u> </u>                                     | nMREQ<br>MAS0     |                    |                     |             |

| 163        | J20         | <u> </u>                                     | MAS1              |                    |                     |             |

| 164        | K17         | <u> </u>                                     | nRESET            |                    |                     |             |

| 165        | H20         | 72                                           | P1.7              | PINT5              |                     |             |

| 166        | K18         | 73                                           | P1.6              | PINT4              |                     |             |

| 167        | H19         | 74                                           | P1.5              | PINT3              |                     | -           |

| 168        | J19         | 75                                           | P1.4              | PINT2              | -                   | +           |

| 169        | G20         | 76                                           | P1.3              | PINT1              |                     | -           |

| 170        | J17         | 77                                           | P1.2              | PINT0              |                     |             |

| 171        | G19         | 78                                           | P1.1              | VREF1/WP2          |                     |             |

| 172        | J18         | 79                                           | P1.0              | VREF0/WP1          |                     |             |

| 173        | F20         | 80                                           | VREF              | 1                  |                     | 1           |

| 174        | H18         | 81                                           | VREFINT           |                    |                     |             |

| 175        | F19         | 82                                           | AVDD              |                    |                     |             |

| 176        | H17         | 83                                           | AVSS              |                    |                     |             |

| 177        | E20         | 84                                           | BVDD              |                    |                     |             |

| 178        | G18         | 85                                           | WAIT              |                    |                     |             |

| 179        | E19         | 86                                           | WAITH             |                    |                     |             |

| 180        | F18         | 87                                           | P0.7              | T                  |                     |             |

| 181        | D20         | 88                                           | P0.6              | P06COMP            |                     |             |

| 182        | G17         | 89                                           | P0.5              | +                  | -                   |             |

| 183        | D19         | 90                                           | P0.4              | +                  |                     |             |

| 184        | E18         | 91                                           | P0.3              | +                  |                     |             |

| 185        | C20         | 92                                           | P0.2              | +                  |                     |             |

| 186        | F17         | 93                                           | P0.1              | +                  |                     |             |

| 187        | C19         | 94                                           | P0.0              | CC4-IN             |                     |             |

| 188        | D18         | 95                                           | P2.1              | 1                  |                     |             |

| 189        | B20         | 96                                           | P2.0              | +                  |                     |             |

| 190        | E17         | 97                                           | U6.2              | +                  | GWEQ                | SEG6.2      |

|            | 1           | <u>.                                    </u> |                   |                    |                     |             |

| 191        | B19         | 98                                           | U6.1              | CAN1-RX/WP7        | GOEQ                | SEG6.1      |

Table 2-1: Pin Assignment for CPGA257 Package

| Pin<br>No.<br>193<br>194<br>195 | Co-<br>ord. | 100<br>Pin No.                                   | Basic<br>Function        | Port<br>Special In   | Port<br>Special Out  | LCD<br>Mode      |  |

|---------------------------------|-------------|--------------------------------------------------|--------------------------|----------------------|----------------------|------------------|--|

| 194                             |             | 100                                              | 110.5                    |                      |                      |                  |  |

|                                 |             |                                                  | U8.5                     | CAN2-RX/PINT3/WP8    | LCD-SYNC-OUT         | SEG8.5           |  |

| 195                             | D17         | 101                                              | U8.4                     | LCD-SYNC-IN          | CAN2-TX              | SEG8.4           |  |

|                                 | B18         | 102                                              | U8.3                     | CAN3-RX/WP9          | LCD-CLK-OUT          | SEG8.3           |  |

| 196                             | C17         | 103                                              | U8.2                     | LCD-CLK-IN           | CAN3-TX              | SEG8.2           |  |

| 197                             | A19         | 104                                              | U8.1                     |                      | CC3-OUT              | SEG8.1           |  |

| 198                             | D16         | 105                                              | U8.0                     |                      | CC4-OUT              | SEG8.0           |  |

| 199                             | B17         | 106                                              | U4.3                     | CAN0-RX/WP5          | TO2                  | BP3              |  |

| 200                             | C16         | 107                                              | U4.2                     |                      | CAN0-TX              | BP2              |  |

| 201                             | A18         | 108                                              | U4.1                     | CC0-IN               | SPI1-D-OUT           | BP1              |  |

| 202                             | D15         | 109                                              | U4.0                     | SPI1-D-IN            | CC0-OUT              | BP0              |  |

| 203                             | B16         | 110                                              | U3.7                     | SPI1-CLK-IN          | SPI1-CLK-OUT         | SEG3.7           |  |

| 204                             | C15         | 111                                              | U3.6                     | ODIO D IN            | SPI0-D-OUT           | SEG3.6           |  |

| 205                             | A17         | 112                                              | U3.5                     | SPI0-D-IN            | TO3                  | SEG3.5           |  |

| 206                             | D14         | 113                                              | U3.4                     | SPI0-CLK-IN          | SPI0-CLK-OUT         | SEG3.4           |  |

| 207                             | B15         | 114                                              | U3.3                     | OOO IN / TOY         | CO0/TDO              | SEG3.3           |  |

| 208                             | C14         | 115                                              | U3.2                     | CC0-IN / TCK         | CC0-OUT              | SEG3.2           |  |

| 209                             | A16         | 116                                              | U3.1                     | CC1-IN / TMS         | CC1-OUT              | SEG3.1           |  |

| 210                             | D13         | 117                                              | U3.0                     | CC2-IN / TDI         | CC2-OUT              | SEG3.0           |  |

| 211                             | B14<br>C13  | 118                                              | TEST2                    |                      |                      |                  |  |

| 212<br>213                      | C13         | 119<br>120                                       | UVDD1<br>UVSS1           |                      |                      |                  |  |

| 213                             | C12         | 120                                              |                          | o / TDIT             |                      |                  |  |

| 214                             | B13         | 1                                                | TRACEPKT                 |                      |                      |                  |  |

| 215                             | D12         |                                                  | TRACEPKT                 |                      |                      |                  |  |

|                                 |             | 1                                                | TRACEPKT                 |                      |                      |                  |  |

| 217<br>218                      | A14<br>B12  | 1                                                | TRACEPKT                 |                      |                      |                  |  |

| 210                             | A13         | 1                                                | TRACEPKT                 |                      |                      |                  |  |

| 219                             | C11         |                                                  | EVDD1                    | 5 / NM4              |                      |                  |  |

| 220                             | A12         | 1                                                | EVSS1                    |                      |                      |                  |  |

| 222                             | D11         | 1                                                | TRACEPKT                 | e / LOCK             |                      |                  |  |

| 223                             | A11         | 1                                                | TRACEPKT                 |                      |                      |                  |  |

| 224                             | B11         | 1                                                | TRACEPKT                 |                      |                      |                  |  |

| 225                             | A10         | 1                                                | TRACEPKT                 |                      |                      |                  |  |

| 226                             | B10         | 1                                                | TRACEPKT                 |                      |                      |                  |  |

|                                 |             | 1                                                | TRACEPKT                 |                      |                      |                  |  |

| 227<br>228                      | A9<br>D10   | 1                                                |                          | 12 / RANGEOUT0       |                      |                  |  |

| 229                             | A8          | 1                                                |                          | 13 / RANGEOUT1       |                      |                  |  |

| 230                             | C10         | 1                                                | TRACEPKT                 |                      |                      |                  |  |

|                                 |             | 1                                                |                          |                      |                      |                  |  |

| 231<br>232                      | B8<br>B9    | 1                                                | PIPESTATO                | 15 / BREAKPT         |                      |                  |  |

| 233                             | A7          | 1                                                | PIPESTAT1                |                      |                      |                  |  |

| 234                             | D9          | 1                                                | PIPESTAT1                |                      |                      |                  |  |

|                                 | D9<br>B7    | 1                                                |                          | / A1                 |                      |                  |  |

| 235                             | C9          | 1                                                | EVDD0<br>EVSS0           |                      |                      |                  |  |

| 236                             |             | 1                                                |                          | 0/40                 |                      |                  |  |

| 237                             | A6          | 1                                                | TRACESYN                 |                      |                      |                  |  |

| 238<br>239                      | C8<br>B6    | <del>                                     </del> | TRACECLK<br>EXTTRIG/A    |                      |                      |                  |  |

| 239                             |             | <del>                                     </del> | FSYS                     | *                    |                      |                  |  |

| 240                             | D8<br>A5    | 1                                                | nWAIT                    |                      |                      |                  |  |

|                                 |             | 1                                                |                          |                      |                      |                  |  |

| 242                             | C7          | 1                                                | DBGACK                   |                      |                      |                  |  |

| 243                             | B5          | 1                                                | DBGRQ                    |                      |                      |                  |  |

| 244<br>245                      | C6<br>A4    | <del>                                     </del> | UVDD                     |                      |                      |                  |  |

|                                 |             | 404                                              |                          | DICITIN              | DIOIT OUT            | locon o          |  |

| 246<br>247                      | D7<br>B4    | 121<br>122                                       | U2.6<br>U2.5             | DIGIT-IN<br>UART0-RX | DIGIT-OUT<br>CC1-OUT | SEG2.6<br>SEG2.5 |  |

|                                 |             |                                                  | U2.5<br>U2.4             | CC1-IN/DIGIT-IN      |                      |                  |  |

| 248                             | C5          | 123                                              |                          |                      | UARTO-TX             | SEG2.4           |  |

| 249<br>250                      | A3          | 124                                              | U2.3<br>U2.2             | UART1-RX             | CC2-OUT              | SEG2.3           |  |

|                                 | D6          | 125                                              |                          | CC2-IN               | UART1-TX             | SEG2.2           |  |

| 251                             | B3          | 126                                              | U7.7/GD7                 |                      | CO0                  | SEG7.7           |  |

|                                 | C4<br>A2    | 127                                              | U7.6/GD6                 |                      | CO1                  | SEG7.6           |  |

| 252                             |             | 128                                              | U7.5/GD5                 |                      | LCK/PFM1             | SEG7.5           |  |

| 253                             |             | 1                                                |                          | 005 111              |                      |                  |  |

| 253<br>254                      | D5          | 1                                                | U7.4/GD4                 | CC5-IN               | CC5-OUT              | SEG7.4           |  |

| 253                             |             | 1                                                | U7.4/GD4<br>FVDD<br>FVSS | CC5-IN               | CC5-OUT              | SEG7.4           |  |

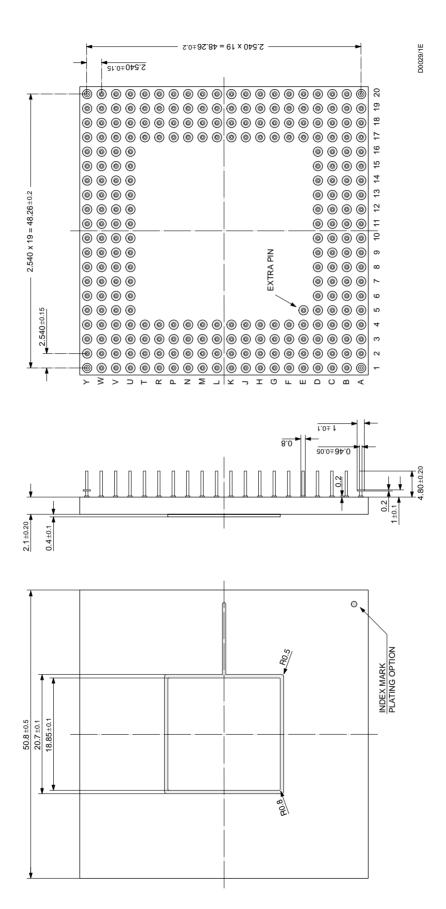

# 2.2. Package Outline Dimensions

Fig. 2-2: CPGA257 Ceramic Pin Grid Array 257-Pin (Weight approx. 32g. Dimensions in mm)

Micronas

# 2.3. Multiple Function Pins

#### 2.3.1. U-Ports

Beside their basic function (digital I/O), Universal Ports (prefix "U") have overlaid alternative functions (see Table 2–1 on page 12).

How to enable Basic Function, Special In and Special Out mode is explained in the functional description of the U-Ports. How to enable LCD mode is explained in the functional descriptions of LCD module and U-Ports.

## 2.3.2. H-Ports

Beside their basic function (digital I/O), High Current Ports (prefix "H") have overlaid alternative functions (see Table 2–1 on page 12).

How to enable Basic Function, Special In and Special Out mode is explained in the functional description of the H-Ports.

### 2.3.3. Emulator Bus

In contrast to the PQFP128 standard package, the CPGA257 package has additional pins (Emulator Bus) which serve as memory interface, Emulation JTAG interface or connection to an external emulation or trace hardware (Trace Bus).

The functionality of the memory interface and the Trace Bus is controlled by register CR. Refer to section "Control Word" for more information.

Some of the following pins are marked as being ARM or ETM signals. For details of the functionality please refer to ARM7TDMI Data sheet (Document Number: ARM DDI 0029) or Embedded Trace Macro Cell (Document Number: ARM IHI 0014 and ARM DDI 0158).

# 2.4. Pin Function Description

### A0 to A7 (ARM) 1)

# A8 to A23 (ARM) 4)

These 24 lines are the original CPU addresses. Some are used for external memory access on the Emulator Bus. The function is controlled by register CR.

#### **ABE** (ARM) 1) 2)

This pin outputs the "Address bus enable" signal of the ARM. It indicates that the CPU does not access the data and address bus when low. It is not possible to influence the CPU via this pin.

# ABORT (ARM) 3)

This is an input which allows the memory system to tell the processor that a requested access is not allowed.

#### AICU2 to AICU7 4)

These pins correspond to the ARM address bus lines A2 to A7 but can be modified by the ICU. In the latter case AICUx and Ax are not equal.

#### **ALARMQ**

This is the second input comparator level on the RESETQ pin.

# AMCM21 to AMCM23 4)

These pins correspond to the ARM address bus lines A21 to A23 but can be modified by the memory controller. In the latter case AMCMx and Ax are not equal.

# **AMCS1** 4)

This pin corresponds to the ARM address bus line A1 but can be modified by the memory controller. In the latter case AMCS1 and A1 are not equal.

### **AM-OUT**

This is the output signal of the Audio Module.

#### AM-PWM

This is the output signal of the 8-bit PWM of the Audio Module. It is intended for testing only.

#### AVDD

This is the positive power supply for ADC, P06COMP, WAIT-COMP and BVDD regulator. AVDD should be kept at UVDD  $\pm 0.5$ V. It must be buffered by an external capacitor to analog ground

#### **AVSS**

This is the negative reference for the ADC and the negative power supply for ADC, P06COMP, WAITCOMP and PLL. Connect to analog ground.

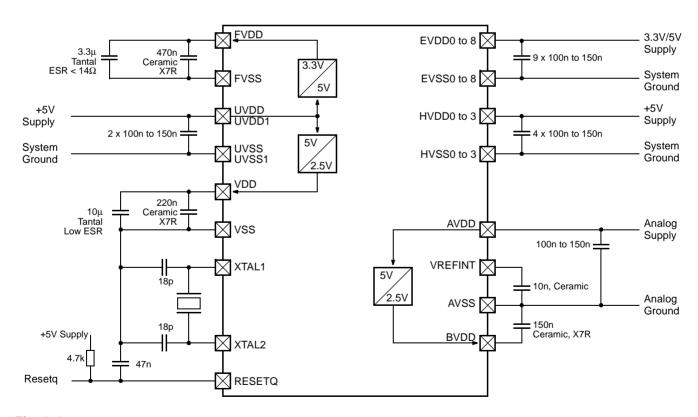

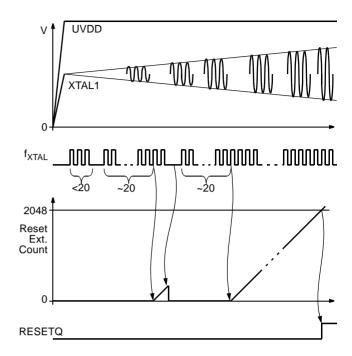

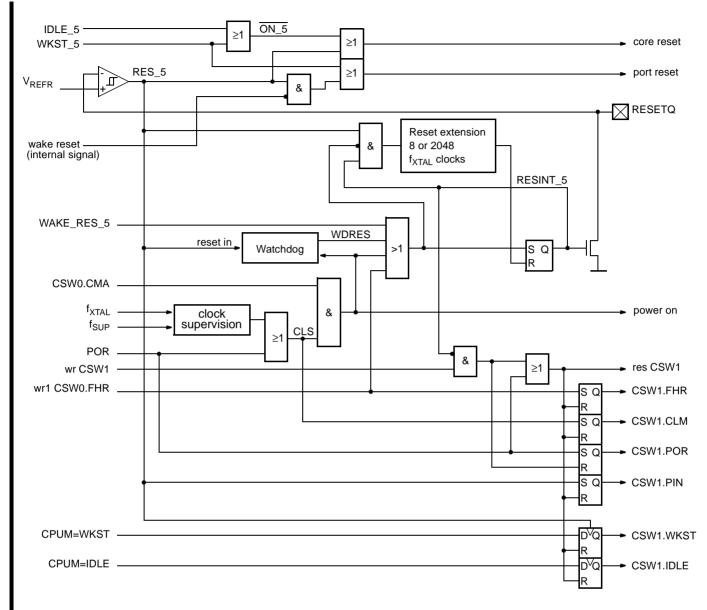

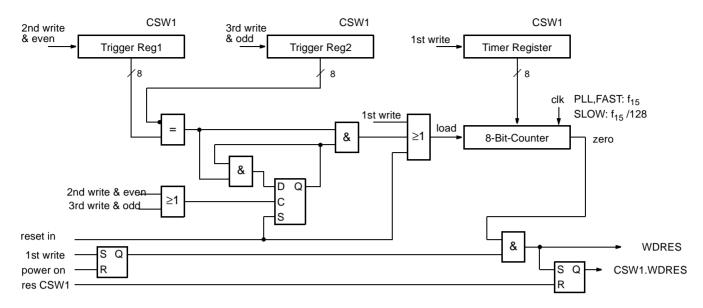

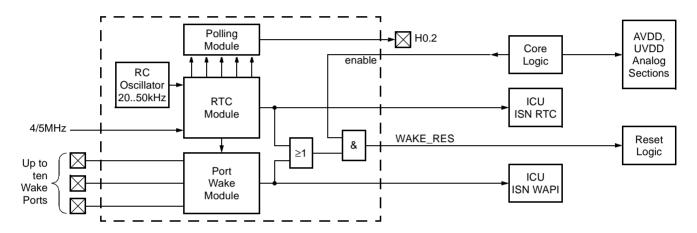

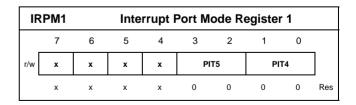

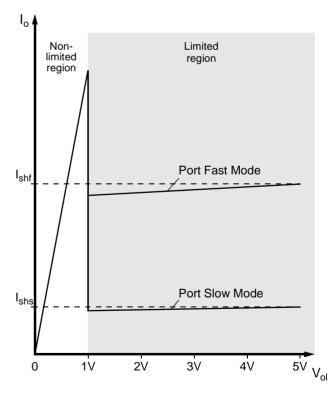

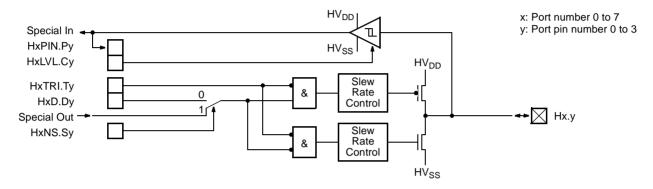

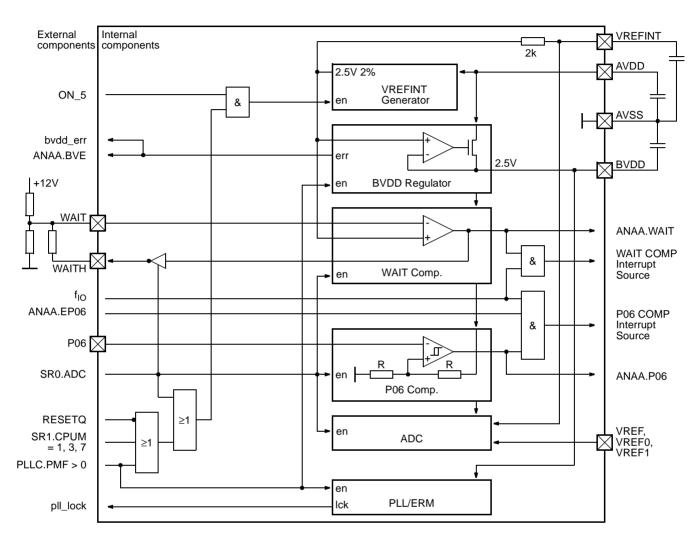

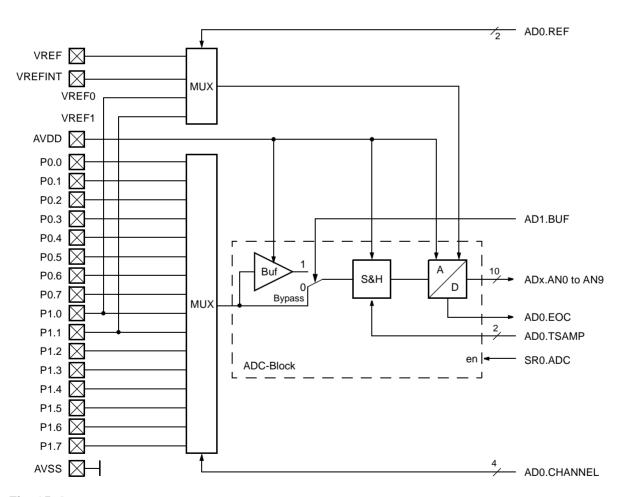

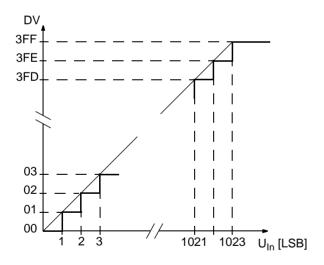

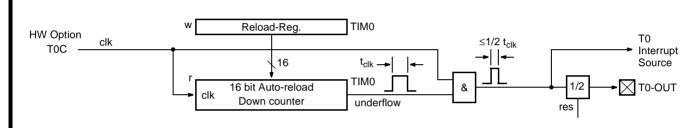

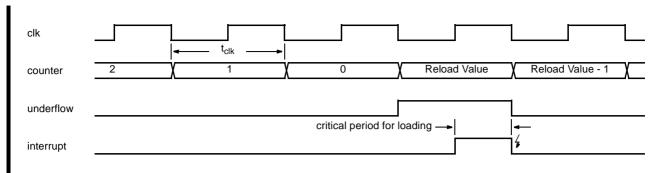

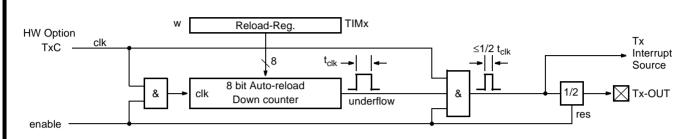

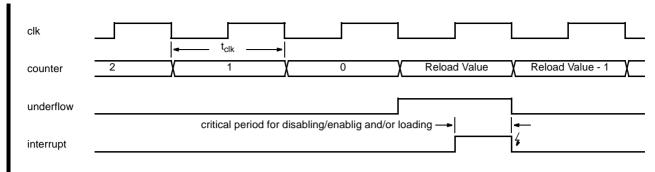

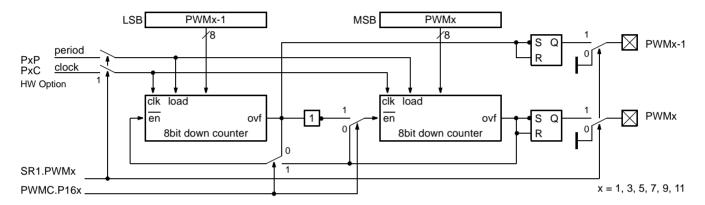

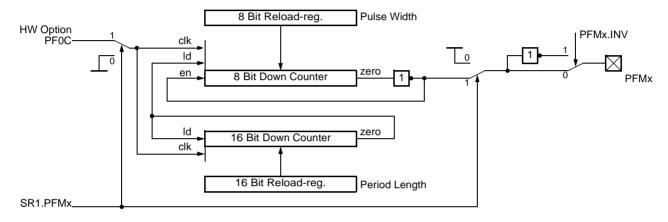

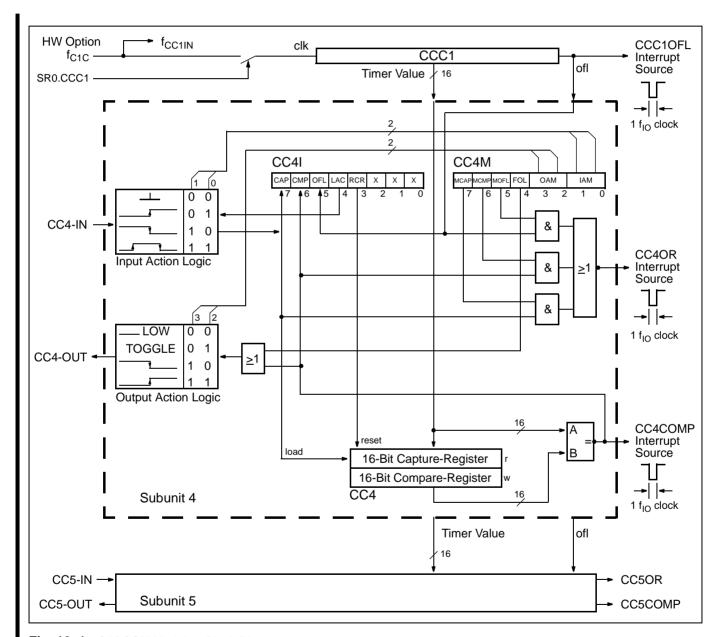

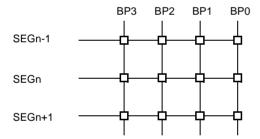

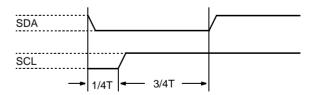

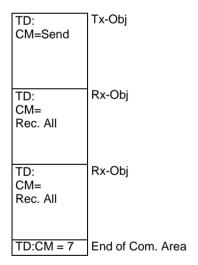

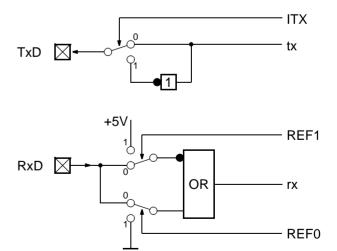

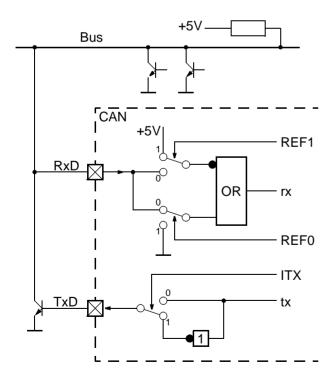

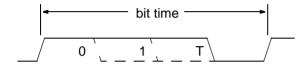

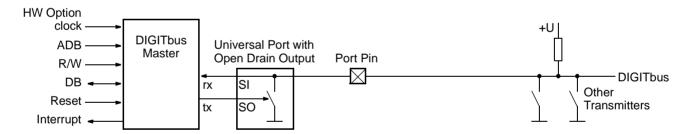

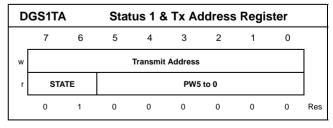

### BP0 to BP3