## 12-Bit, 80 MSPS/105 MSPS A/D Converter

# AD9432

#### **FEATURES**

On-Chip Reference and Track/Hold On-Chip Input Buffer 850 mW Typical Power Dissipation at 105 MSPS 500 MHz Analog Bandwidth SNR = 67 dB @ 49 MHz AIN at 105 MSPS SFDR = 80 dB @ 49 MHz AIN at 105 MSPS 2.0 V p-p Differential Analog Input Range Single 5.0 V Supply Operation 3.3 V CMOS/TTL Outputs Two's Complement Output Format

#### **APPLICATIONS**

Communications Basestations and 'Zero-IF' Subsystems Wireless Local Loop (WLL) Local Multipoint Distribution Service (LMDS) HDTV Broadcast Cameras and Film Scanners

#### **GENERAL INTRODUCTION**

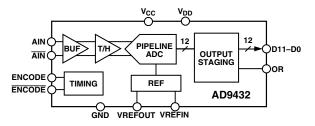

The AD9432 is a 12-bit monolithic sampling analog-to-digital converter with an on-chip track-and-hold circuit and is optimized for high-speed conversion and ease of use. The product operates at a 105 MSPS conversion rate with outstanding dynamic performance over its full operating range.

The ADC requires only a single 5.0 V power supply and a 105 MHz encode clock for full-performance operation. No

#### FUNCTIONAL BLOCK DIAGRAM

external reference or driver components are required for many applications. The digital outputs are TTL/CMOS compatible and a separate output power supply pin supports interfacing with 3.3 V logic. The encode input supports either differential or single-ended and is TTL/CMOS-compatible.

Fabricated on an advanced BiCMOS process, the AD9432 is available in a 52-lead plastic quad flatpack package (LQFP) specified over the industrial temperature range (-40°C to +85°C).

#### REV. E

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

Www.analog.com

Fax: 781/326-8703

© Analog Devices, Inc., 2002

# AD9432-SPECIFICATIONS

| $(V_{DD} = 3.3 \text{ V}, V_{CC} = 5.0 \text{ V};$ external reference; differential encode input, unless |

|----------------------------------------------------------------------------------------------------------|

| otherwise noted.)                                                                                        |

| Parameter                                                                      | Temp         | Test<br>Level | AD943<br>Min      | 2BST/B<br>Typ          | SQ-80<br>Max | AD9432BST/BSQ-105<br>Min Typ Max      |                          |               | Unit       |  |

|--------------------------------------------------------------------------------|--------------|---------------|-------------------|------------------------|--------------|---------------------------------------|--------------------------|---------------|------------|--|

| RESOLUTION                                                                     | remp         |               |                   | 1 <b>ур</b><br>12      | 11107        |                                       | 1 <b>ур</b><br>12        | 11103         | Bits       |  |

|                                                                                |              |               |                   | 12                     |              |                                       | 12                       |               | Dits       |  |

| DC ACCURACY                                                                    | 25%          | T             | 0.75              | 10.05                  | 10.75        | 0.75                                  | 10.05                    | +0.75         | TOD        |  |

| Differential Nonlinearity                                                      | 25°C<br>Full | I<br>VI       | -0.75<br>-1.0     | ±0.25<br>±0.5          | +0.75 +1.0   | -0.75<br>-1.0                         | $_{\pm 0.25}^{\pm 0.25}$ | +0.75<br>+1.0 | LSB<br>LSB |  |

| Integral Nonlinearity                                                          | 25°C         |               | -1.0<br>-1.0      | $\pm 0.5$<br>$\pm 0.5$ | +1.0<br>+1.0 | $  -1.0 \\ -1.0$                      | $\pm 0.5$<br>$\pm 0.5$   | +1.0 $+1.0$   | LSB        |  |

| Integral Noniniearity                                                          | Full         | VI            | -1.5              | $\pm 0.3$<br>$\pm 1.0$ | +1.0 $+1.5$  | -1.0                                  | $\pm 0.3$<br>$\pm 1.0$   | +1.0+1.5      | LSB        |  |

| No Missing Codes                                                               | Full         | VI            |                   | uarantee               |              |                                       | uarantee                 |               | LSD        |  |

| Gain Error <sup>1</sup>                                                        | 25°C         | I             | -5                | +2                     | 4<br>+7      | -5                                    | +2                       | 47 +7         | % FS       |  |

| Gain Tempco <sup>1</sup>                                                       | Full         | V             |                   | 150                    |              |                                       | 150                      |               | ppm/°C     |  |

|                                                                                | 1 un         | •             |                   | 150                    |              |                                       | 150                      |               | ppin/ C    |  |

| ANALOG INPUT                                                                   | <b>T</b> 11  |               |                   | 110                    |              |                                       | 110                      |               | <b>X</b> 7 |  |

| Input Voltage Range (AIN-AIN)                                                  | Full         | V             |                   | $\pm 1.0$              |              |                                       | $\pm 1.0$                |               | V<br>V     |  |

| Common-Mode Voltage                                                            | Full         |               | _                 | 3.0                    |              | _                                     | 3.0                      |               |            |  |

| Input Offset Voltage                                                           | Full<br>Full | VI<br>VI      | -5                | $\pm 0$                | +5           | $\begin{vmatrix} -5\\2 \end{vmatrix}$ | $\frac{\pm 0}{3}$        | +5<br>4       | mV<br>kΩ   |  |

| Input Resistance                                                               | 25°C         | VI<br>V       |                   | 3                      | 4            | 2                                     | 5<br>4                   | 4             |            |  |

| Input Capacitance                                                              | 25°C<br>25°C | VV            |                   | 4<br>500               |              |                                       | 4<br>500                 |               | pF<br>MHz  |  |

| Analog Bandwidth, Full Power                                                   | 2510         | v             |                   | 500                    |              |                                       | 500                      |               | MHZ        |  |

| ANALOG REFERENCE                                                               |              |               |                   |                        |              |                                       |                          |               |            |  |

| Output Voltage                                                                 | Full         | VI            | 2.4               | 2.5                    | 2.6          | 2.4                                   | 2.5                      | 2.6           | V          |  |

| Tempco                                                                         | Full         | V             |                   | 50                     |              |                                       | 50                       |               | ppm/°C     |  |

| Input Bias Current                                                             | Full         | VI            |                   | 15                     | 50           |                                       | 15                       | 50            | μA         |  |

| SWITCHING PERFORMANCE                                                          |              |               |                   |                        |              |                                       |                          |               |            |  |

| Maximum Conversion Rate                                                        | Full         | VI            | 80                |                        |              | 105                                   |                          |               | MSPS       |  |

| Minimum Conversion Rate                                                        | Full         | IV            |                   |                        | 1            |                                       |                          | 1             | MSPS       |  |

| Encode Pulsewidth High (t <sub>EH</sub> )                                      | 25°C         | IV            | 4.0               | 6.2                    |              | 4.0                                   | 4.8                      |               | ns         |  |

| Encode Pulsewidth Low $(t_{EL})$                                               | 25°C         | IV            | 4.0               | 6.2                    |              | 4.0                                   | 4.8                      |               | ns         |  |

| Aperture Delay $(t_A)$                                                         | 25°C         | V             |                   | 2.0                    |              |                                       | 2.0                      |               | ns         |  |

| Aperture Uncertainty (Jitter)                                                  | 25°C         | V             |                   | 0.25                   |              |                                       | 0.25                     |               | ps rms     |  |

| Output Valid Time $(t_V)^2$                                                    | Full         | VI            | 3.0               | 5.3                    |              | 3.0                                   | 5.3                      |               | ns         |  |

| Output Propagation Delay $(t_{PD})^2$                                          | Full         | VI            |                   | 5.5                    | 8.0          |                                       | 5.5                      | 8.0           | ns         |  |

| Output Rise Time $(t_R)^2$                                                     | Full         | V             |                   | 2.1                    |              |                                       | 2.1                      |               | ns         |  |

| Output Fall Time $(t_F)$                                                       | Full         | V             |                   | 1.9                    |              |                                       | 1.9                      |               | ns         |  |

| Out-of-Range Recovery Time                                                     | 25°C         | V             |                   | 2                      |              |                                       | 2                        |               | ns         |  |

| Transient Response Time                                                        | 25°C         | V             |                   | 2                      |              |                                       | 2                        |               | ns         |  |

| Latency                                                                        | Full         | IV            |                   | 10                     |              |                                       | 10                       |               | Cycles     |  |

| DIGITAL INPUTS                                                                 |              |               |                   |                        |              |                                       |                          |               |            |  |

| Encode Input Common Mode                                                       | Full         | v             |                   | 1.6                    |              |                                       | 1.6                      |               | V          |  |

| Differential Input (ENC–ENC)                                                   | Full         | v             |                   | 750                    |              |                                       | 750                      |               | mV         |  |

| Single-Ended                                                                   |              |               |                   |                        |              |                                       |                          |               |            |  |

| Logic "1" Voltage                                                              | Full         | IV            | 2.0               |                        |              | 2.0                                   |                          |               | V          |  |

| Logic "0" Voltage                                                              | Full         | IV            |                   |                        | 0.8          |                                       |                          | 0.8           | V          |  |

| Input Resistance                                                               | Full         | VI            | 3                 | 5                      | 8            | 3                                     | 5                        | 8             | kΩ         |  |

| Input Capacitance                                                              | 25°C         | V             | 5                 | 4.5                    | 0            |                                       | 4.5                      | Ũ             | pF         |  |

| · · · · · · · · · · · · · · · · · · ·                                          | _            |               |                   | -                      |              | -                                     | -                        |               | *          |  |

| DIGITAL OUTPUTS                                                                | Full         | VI            | V <sub>DD</sub> - | 0.05                   |              | V                                     | 0.05                     |               | v          |  |

| Logic "1" Voltage ( $V_{DD}$ = 3.3 V)<br>Logic "0" Voltage ( $V_{DD}$ = 3.3 V) | Full         | VI<br>VI      | v <sub>DD</sub> - | 0.05                   | 0.05         | V <sub>DD</sub> -                     | 0.05                     | 0.05          | v<br>V     |  |

| Output Coding $(v_{DD} - 3.5 v)$                                               | 1. uii       | VI I          | Tura              | 's Compl               |              | Ture                                  | 's Compl                 |               | v          |  |

|                                                                                |              |               | 1 WO              | s Compl                | CITICITE     | 1 1 1 1 1                             | s Compl                  | CHICHL        |            |  |

| POWER SUPPLY                                                                   |              |               |                   |                        |              |                                       |                          |               |            |  |

| Power Dissipation <sup>3</sup>                                                 | Full         | VI            |                   | 790                    | 1000         |                                       | 850                      | 1100          | mW         |  |

| Power Supply Rejection Ratio (PSRR)                                            | 25°C         | I             | -5                | +0.5                   | +5           | -5                                    | +0.5                     | +5            | mV/V       |  |

| I <sub>VCC</sub>                                                               | Full         | VI            |                   | 158                    | 200          |                                       | 170                      | 220           | mA         |  |

| $I_{VDD}$                                                                      | Full         | VI            |                   | 9.5                    | 12.2         |                                       | 12.5                     | 16            | mA         |  |

|                                                          |      | Test  | AD9432BST/BSQ-80 |      | AD9432BST/BSQ-105 |      |      |     |      |

|----------------------------------------------------------|------|-------|------------------|------|-------------------|------|------|-----|------|

| Parameter                                                | Temp | Level | Min              | Тур  | Max               | Min  | Тур  | Max | Unit |

| DYNAMIC PERFORMANCE <sup>4</sup>                         |      |       |                  |      |                   |      |      |     |      |

| Signal-to-Noise Ratio (SNR)                              |      |       |                  |      |                   |      |      |     |      |

| (Without Harmonics)                                      |      |       |                  |      |                   |      |      |     |      |

| $f_{IN} = 10.3 \text{ MHz}$                              | 25°C | Ι     | 65.5             | 67.5 |                   | 65.5 | 67.5 |     | dB   |

| $f_{IN} = 40 \text{ MHz}$                                | 25°C | I     | 65               | 67.2 |                   |      | 67.2 |     | dB   |

| $f_{IN} = 49 \text{ MHz}$                                | 25°C | I     |                  | 67.0 |                   | 64   | 67.0 |     | dB   |

| $f_{IN} = 70 \text{ MHz}$                                | 25°C | V     |                  | 66.1 |                   |      | 66.1 |     | dB   |

| Signal-to-Noise Ratio (SINAD)                            |      |       |                  |      |                   |      |      |     |      |

| (With Harmonics)                                         |      |       |                  |      |                   |      |      |     |      |

| $f_{IN} = 10.3 \text{ MHz}$                              | 25°C | I     | 65               | 67.2 |                   | 65   | 67.2 |     | dB   |

| $f_{IN} = 40 \text{ MHz}$                                | 25°C | I     | 64.5             | 66.9 |                   |      | 66.9 |     | dB   |

| $f_{IN} = 49 \text{ MHz}$                                | 25°C | I     |                  | 66.7 |                   | 63   | 66.7 |     | dB   |

| $f_{IN} = 70 \text{ MHz}$                                | 25°C | V     |                  | 65.8 |                   |      | 65.8 |     | dB   |

| Effective Number of Bits                                 |      |       |                  |      |                   |      |      |     |      |

| $f_{IN} = 10 MHz$                                        | 25°C | V     |                  | 11.0 |                   |      | 11.0 |     | Bits |

| $f_{IN} = 40 \text{ MHz}$                                | 25°C | V     |                  | 10.9 |                   |      | 10.9 |     | Bits |

| $f_{IN} = 49 \text{ MHz}$                                | 25°C | V     |                  | 10.9 |                   |      | 10.9 |     | Bits |

| $f_{IN} = 70 \text{ MHz}$                                | 25°C | V     |                  | 10.7 |                   |      | 10.7 |     | Bits |

| Second and Third Harmonic Distortion                     |      |       |                  |      |                   |      |      |     |      |

| $f_{IN} = 10 MHz$                                        | 25°C | I     | -75              | -85  |                   | -75  | -85  |     | dBc  |

| $f_{IN} = 40 \text{ MHz}$                                | 25°C | I     | -73              | -85  |                   |      | -83  |     | dBc  |

| $f_{IN} = 49 \text{ MHz}$                                | 25°C | I     |                  | -83  |                   | -72  | -80  |     | dBc  |

| $f_{IN} = 70 \text{ MHz}$                                | 25°C | V     |                  | -80  |                   |      | -78  |     | dBc  |

| Worst Harmonic or Spur                                   |      |       |                  |      |                   |      |      |     |      |

| (Excluding Second and Third)                             |      |       |                  |      |                   |      |      |     |      |

| $f_{IN} = 10 \text{ MHz}$                                | 25°C | I     | -80              | -90  |                   | -80  | -90  |     | dBc  |

| $f_{IN} = 40 \text{ MHz}$                                | 25°C | I     | -80              | -90  |                   |      | -90  |     | dBc  |

| $f_{IN} = 49 \text{ MHz}$                                | 25°C | I     |                  | -90  |                   | -80  | -90  |     | dBc  |

| $f_{IN} = 70 \text{ MHz}$                                | 25°C | V     |                  | -90  |                   |      | -90  |     | dBc  |

| Two-Tone Intermod Distortion (IMD)                       |      |       |                  |      |                   |      |      |     |      |

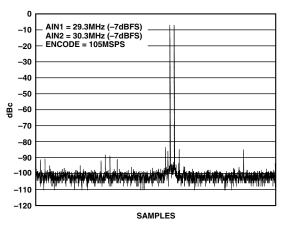

| $f_{IN1} = 29.3 \text{ MHz}; f_{IN2} = 30.3 \text{ MHz}$ | 25°C | V     |                  | -75  |                   |      | -75  |     | dBc  |

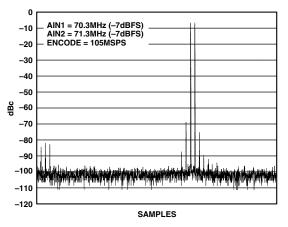

| $f_{IN1} = 70.3 \text{ MHz}; f_{IN2} = 71.3 \text{ MHz}$ | 25°C | V     |                  | -66  |                   |      | -66  |     | dBc  |

NOTES

<sup>1</sup>Gain error and gain temperature coefficients are based on the ADC only (with a fixed 2.5 V external reference and a 2 V p-p differential analog input).

$^{2}$ t<sub>v</sub> and t<sub>PD</sub> are measured from the transition points of the ENCODE input to the 50%/50% levels of the digital outputs swing. The digital output load during test is not to exceed an ac load of 10 pF or a dc current of ±40  $\mu$ A. Rise and fall times measured from 10% to 90%.

<sup>3</sup>Power dissipation measured with encode at rated speed and a dc analog input. (Outputs Static,  $I_{VDD} = 0$ .)

<sup>4</sup>SNR/harmonics based on an analog input voltage of -0.5 dBFS referenced to a 2 V full-scale input range.

Specifications subject to change without notice.

#### **ABSOLUTE MAXIMUM RATINGS\***

| V <sub>DD</sub>                                                                                                                    |

|------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>CC</sub>                                                                                                                    |

| Analog Inputs $\dots \dots \dots$  |

| Digital Inputs $\dots \dots \dots$ |

| VREFIN $-0.5$ V to V <sub>CC</sub> + $0.5$ V                                                                                       |

| Digital Output Current 20 mA                                                                                                       |

| Operating Temperature                                                                                                              |

| Storage Temperature                                                                                                                |

| Maximum Junction Temperature 150°C                                                                                                 |

| Maximum Case Temperature 150°C                                                                                                     |

\*Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions outside of those indicated in the operation sections of this specification is not implied. Exposure to absolute maximum ratings for extended periods may affect device reliability.

#### EXPLANATION OF TEST LEVELS Test Level

- I 100% production tested.

- II 100% production tested at 25°C and sample tested at specified temperatures.

- III Sample tested only.

- IV Parameter is guaranteed by design and characterization testing.

- V Parameter is a typical value only.

- VI 100% production tested at 25°C; guaranteed by design and characterization testing for industrial temperature range.

#### CAUTION

ESD (electrostatic discharge) sensitive device. Electrostatic charges as high as 4000 V readily accumulate on the human body and test equipment and can discharge without detection. Although the AD9432 features proprietary ESD protection circuitry, permanent damage may occur on devices subjected to high-energy electrostatic discharges. Therefore, proper ESD precautions are recommended to avoid performance degradation or loss of functionality.

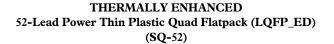

THERMAL CHARACTERISTICS

52-Lead Plastic LQFP (ST-52)  $\theta_{IA} = 50^{\circ}$ C/W, No Airflow

52-lead PowerQuad<sup>®</sup> 4 LQFP (SQ-52)

$\theta_{JA} = 25^{\circ}C/W$ , Soldered Exposed Heat Sink, No Airflow

$\theta_{JA} = 33^{\circ}$ C/W, Unsoldered Exposed Heat Sink, No Airflow  $\theta_{IC} = 2^{\circ}$ C/W, Bottom of package (Exposed Heat Sink)

Simulated Typical performance for 4-layer JEDEC board, horizontal orientation.

**ORDERING GUIDE**

| Model                                | Temperature<br>Ranges  | Package<br>Descriptions                                     | Package<br>Option |

|--------------------------------------|------------------------|-------------------------------------------------------------|-------------------|

| AD9432BSQ<br>-80, -105               | –40°C to +85°C         | 52-Lead Thermally<br>Enhanced Plastic<br>Quad Flatpack      | SQ-52             |

| AD9432BST<br>-80, -105<br>AD9432/PCB | -40°C to +85°C<br>25°C | 52-Lead Plastic Quad<br>Flatpack (LQFP)<br>Evaluation Board | ST-52             |

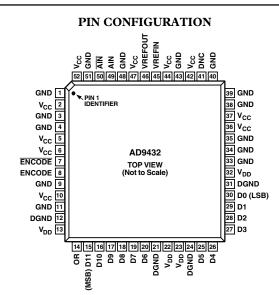

#### PIN FUNCTION DESCRIPTIONS

| Pin Number (AD9432BST)                                 | Mnemonic        | Function                                                               |  |  |

|--------------------------------------------------------|-----------------|------------------------------------------------------------------------|--|--|

| 1, 3, 4, 9, 11, 33, 34, 35, 38, 39, 40, 43, 48, 51 GND |                 | Analog Ground                                                          |  |  |

| 2, 5, 6, 10, 36, 37, 42, 44, 47, 52                    | V <sub>CC</sub> | Analog Supply (5 V)                                                    |  |  |

| 7                                                      | ENCODE          | Encode Clock for ADC–Complementary                                     |  |  |

| 8                                                      | ENCODE          | Encode Clock for ADC–True (ADC samples on rising edge of ENCODE)       |  |  |

| 14 OR                                                  |                 | Out of Range Output                                                    |  |  |

| 15–20, 25–30                                           | D11–D6, D5–D0   | Digital Output                                                         |  |  |

| 12, 21, 24, 31                                         | DGND            | Digital Output Ground                                                  |  |  |

| 13, 22, 23, 32                                         | V <sub>DD</sub> | Digital Output Power Supply (2.7 V to 3.6 V)                           |  |  |

| 41                                                     | DNC             | Do Not Connect                                                         |  |  |

| 45                                                     | VREFIN          | Reference Input for ADC (2.5 V Typical); Bypass with 0.1 µF to Ground. |  |  |

| 46 VREFOUT                                             |                 | Internal Reference Output (2.5 V Typical)                              |  |  |

| 49                                                     | AIN             | Analog Input-True                                                      |  |  |

| 50                                                     | AIN             | Analog Input-Complementary                                             |  |  |

#### DEFINITION OF SPECIFICATIONS Analog Bandwidth (Small Signal)

The analog input frequency at which the spectral power of the fundamental frequency (as determined by the FFT analysis) is reduced by 3 dB.

#### **Aperture Delay**

The delay between a differential crossing of ENCODE and ENCODE and the instant at which the analog input is sampled.

#### Aperture Uncertainty (Jitter)

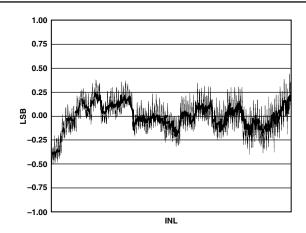

**Differential Nonlinearity**

The sample-to-sample variation in aperture delay.

#### The deviation of any code from an ideal 1 LSB step.

#### Encode Pulsewidth/Duty Cycle

Pulsewidth high is the minimum amount of time that the ENCODE pulse should be left in Logic "1" state to achieve rated performance; pulsewidth low is the minimum time ENCODE pulse should be left in low state. At a given clock rate, these specs define an acceptable Encode duty cycle.

#### **Integral Nonlinearity**

The deviation of the transfer function from a reference line measured in fractions of 1 LSB using a "best straight line" determined by a least square curve fit.

#### REV. E

**Maximum Conversion Rate**

The encode rate at which parametric testing is performed.

The encode rate at which the SNR of the lowest analog signal

frequency drops by no more than 3 dB below the guaranteed limit.

#### **Output Propagation Delay**

**Minimum Conversion Rate**

The delay between a differential crossing of ENCODE and  $\overline{\text{ENCODE}}$  and the time when all output data bits are within valid logic levels.

#### **Power Supply Rejection Ratio**

The ratio of a change in input offset voltage to a change in power supply voltage.

#### Signal-to-Noise Plus Distortion (SINAD)

The ratio of the rms signal amplitude (set at 1 dB below full scale) to the rms value of the sum of all other spectral components, including harmonics but excluding dc.

#### Signal-to-Noise Ratio (SNR)

The ratio of the rms signal amplitude (set at 1 dB below full scale) to the rms value of the sum of all other spectral components, excluding the first five harmonics and dc.

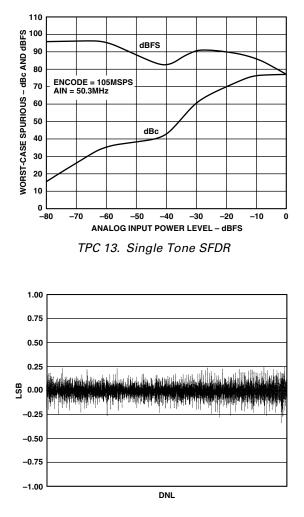

#### Spurious-Free Dynamic Range (SFDR)

The ratio of the rms signal amplitude to the rms value of the peak spurious spectral component. The peak spurious component may or may not be a harmonic. May be reported in dBc (i.e., degrades as signal level is lowered), or in dBFS (always related back to converter full scale).

#### **Two-Tone Intermodulation Distortion Rejection**

The ratio of the rms value of either input tone to the rms value of the worst third order intermodulation product; reported in dBc.

#### **Two-Tone SFDR**

The ratio of the rms value of either input tone to the rms value of the peak spurious component. The peak spurious component may or may not be an IMD product. May be reported in dBc (i.e., degrades as signal level is lowered), or in dBFS (always related back to converter full scale).

#### Worst Harmonic

The ratio of the rms signal amplitude to the rms value of the worst harmonic component, reported in dBc.

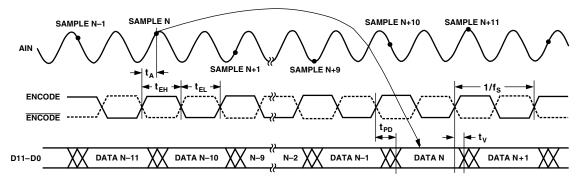

Figure 1. Timing Diagram

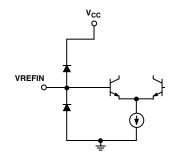

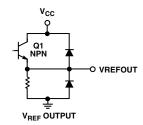

Figure 2. Equivalent Voltage Reference Input Circuit

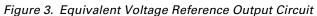

Figure 6. Equivalent Analog Input Circuit

Figure 4. Equivalent Encode Input Circuit

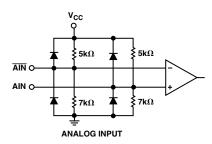

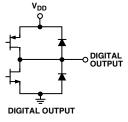

Figure 5. Equivalent Digital Output Circuit

### **Typical Performance Characteristics–AD9432**

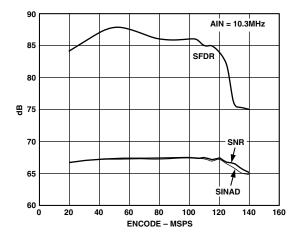

TPC 1. SNR/SINAD/SFDR vs.  $f_S$ :  $f_{IN} = 10.3$  MHz

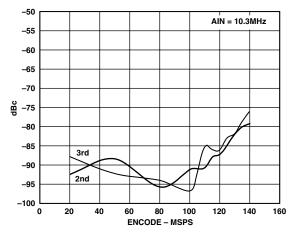

TPC 2. Harmonics vs.  $f_S$ :  $f_{IN} = 10.3 \text{ MHz}$

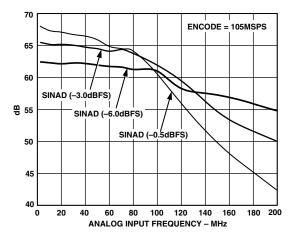

TPC 3. SINAD vs.  $f_{IN}$ :  $f_S = 105 MSPS$

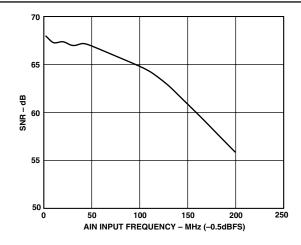

TPC 4. SNR vs. AIN Input Frequency, Encode = 105 MSPS

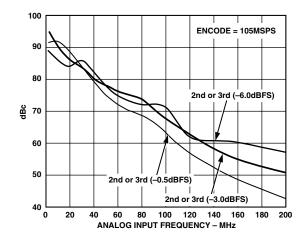

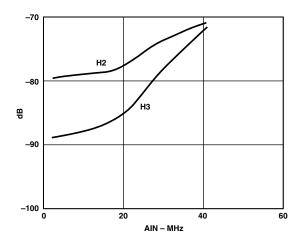

TPC 5. Harmonics vs.  $f_{IN}$ :  $f_S = 105 MSPS$

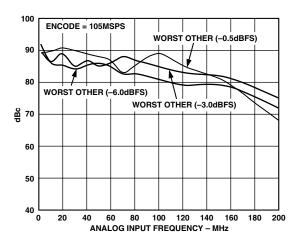

TPC 6. Worst-Case Spur (Other than Second and Third) vs.  $f_{IN}$ :  $f_S = 105$  MSPS

REV. E

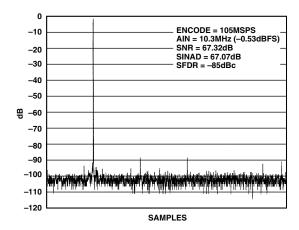

TPC 7. Spectrum:  $f_S = 105$  MSPS,  $f_{IN} = 10.3$  MHz

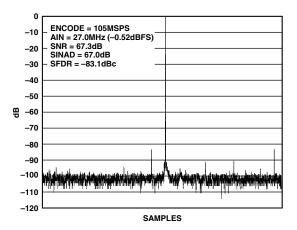

TPC 8. Spectrum:  $f_S = 105$  MSPS,  $f_{IN} = 27$  MHz

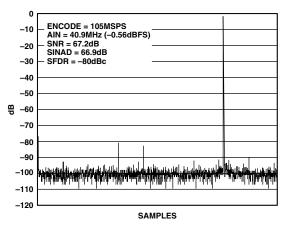

TPC 9. Spectrum:  $f_S = 105$  MSPS,  $f_{IN} = 40.9$  MHz

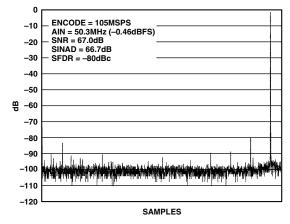

TPC 10. Spectrum:  $f_S = 105$  MSPS,  $f_{IN} = 50.3$  MHz

TPC 11. Two-Tone Spectrum, Wideband:  $f_S = 105$  MSPS, AIN1 = 29.3 MHz, AIN2 = 30.3 MHz

TPC 12. Two-Tone Spectrum, Wideband:  $f_s = 105$  MSPS, AIN1 = 70.3 MHz, AIN2 = 71.3 MHz

TPC 14. Differential Nonlinearity:  $f_S = 105 MSPS$

TPC 15. Integral Nonlinearity:  $f_S = 105 MSPS$

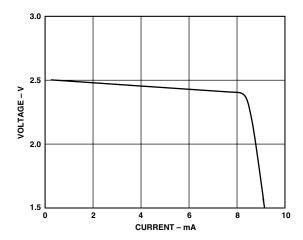

TPC 16. Voltage Reference Output vs. Current Load

#### APPLICATION NOTES

#### **Theory of Operation**

The AD9432 is a multibit pipeline converter that uses a switched capacitor architecture. Optimized for high speed, this converter provides flat dynamic performance up to frequencies near Nyquist. DNL transitional errors are calibrated at final test to a typical accuracy of 0.25 LSB or less.

#### **USING THE AD9432**

#### **Analog Input**

The analog input to the AD9432 is a differential buffer. The input buffer is self-biased by an on-chip resistor divider that sets the dc common-mode voltage to a nominal 3 V (see Equivalent Circuits section). Rated performance is achieved by driving the input differentially. Minimum input offset voltage is obtained when driving from a source with a low differential source impedance such as a transformer in ac applications. Capacitive coupling at the inputs will increase the input offset voltage by as much as  $\pm 25$  mV. Driving the ADC single-endedly will degrade performance. For best dynamic performance, impedances at AIN and  $\overline{\text{AIN}}$ should match.

Special care was taken in the design of the analog input section of the AD9432 to prevent damage and corruption of data when the input is overdriven. The nominal input range is 2 V p-p. Each analog input will be 1 V p-p when driven differentially.

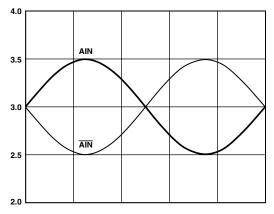

Figure 7. Full-Scale Analog Input Range

#### **ENCODE** Input

Any high speed A/D converter is extremely sensitive to the quality of the sampling clock provided by the user. A track/hold circuit is essentially a mixer, and any noise, distortion, or timing jitter on the clock will be combined with the desired signal at the A/D output. For that reason, considerable care has been taken in the design of the ENCODE input of the AD9432, and the user is advised to give commensurate thought to the clock source. The ENCODE input supports either differential or single-ended and is fully TTL/CMOS compatible.

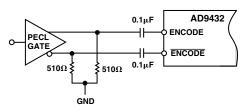

Note that the ENCODE inputs cannot be driven directly from PECL level signals ( $V_{IHD}$  is 3.5 V max). PECL level signals can easily be accommodated by ac coupling as shown in Figure 8. Good performance is obtained using an MC10EL16 in the circuit to drive the encode inputs.

Figure 8. AC Coupling to ENCODE Inputs

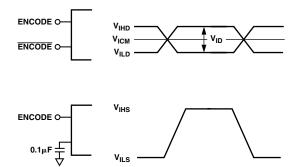

#### **ENCODE** Voltage Level Definition

The voltage level definitions for driving ENCODE and  $\overline{\text{ENCODE}}$  in single-ended and differential mode are shown in Figure 9.

#### ENCODE Inputs

| Differential Signal Amplitude (V <sub>ID</sub> ) 500 mV min        |

|--------------------------------------------------------------------|

|                                                                    |

| High Differential Input Voltage (V <sub>IHD</sub> ) 3.5 V max      |

| Low Differential Input Voltage (V <sub>ILD</sub> ) 0 V min         |

| Common-Mode Input (V <sub>ICM</sub> ) 1.25 V min, 1.6 V nom        |

| High Single-Ended Voltage (V <sub>IHS</sub> ) 2 V min to 3.5 V max |

| Low Single-Ended Voltage ( $V_{ILS}$ ) 0 V min to 0.8 V max        |

Figure 9. Differential and Single-Ended Input Levels

Often, the cleanest clock source is a crystal oscillator producing a pure sine wave. In this configuration, or with any roughly symmetrical clock input, the input can be ac-coupled and biased to a reference voltage that also provides the ENCODE. This ensures that the reference voltage is centered on the encode signal.

#### **Digital Outputs**

The digital outputs are 3.3 V (2.7 V to 3.6 V) TTL/CMOScompatible for lower power consumption. The output data format is Two's Complement, illustrated in Table I. The out of range (OR) output (logic LOW for normal operation) will be HIGH during any clock cycle when the ADC output data (Dx) reach positive or negative full scale (-2048 or +2047). The OR is internally generated each clock cycle, has the same pipeline latency and propagation delay as the ADC output data, and will remain HIGH until the output data reflect an in-range condition. The ADC output bits (Dx) will not roll over, and will therefore remain at positive or negative full scale (+2048 or -2047) while the OR output is HIGH.

| Code  | AIN-AIN (V) | Digital Output |

|-------|-------------|----------------|

| +2047 | 1.000       | 0111 1111 1111 |

| •     | •           | •              |

| •     | •           | •              |

| 0     | 0           | 0000 0000 0000 |

| -1    | -0.00049    | 1111 1111 1111 |

| •     | •           | •              |

| •     | •           | •              |

| -2048 | -1.000      | 1000 0000 0000 |

| Table I. Output Coding | (VREF = 2.5 V) | (Two's Complement) |

|------------------------|----------------|--------------------|

|------------------------|----------------|--------------------|

#### Voltage Reference

A stable and accurate 2.5 V voltage reference is built into the AD9432 (VREFOUT). In normal operation the internal reference is used by strapping Pin 45 to Pin 46 and placing a 0.1  $\mu$ F decoupling capacitor at VREFIN.

The input range can be adjusted by varying the reference voltage applied to the AD9432. No appreciable degradation in performance occurs when the reference is adjusted  $\pm 5\%$ . The full-scale range of the ADC tracks reference voltage changes linearly.

#### Timing

The AD9432 provides latched data outputs, with 10 pipeline delays. Data outputs are included or available one propagation delay  $(t_{PD})$  after the rising edge of the encode command (see Figure 1). The length of the output data lines and loads placed on them should be minimized to reduce transients within the AD9432; these transients can detract from the converter's dynamic performance.

The minimum guaranteed conversion rate of the AD9432 is 1 MSPS. At internal clock rates below 1 MSPS, dynamic performance may degrade. Therefore, input clock rates below 1 MHz should be avoided.

During initial power-up, or whenever the clock to the AD9432 is interrupted, the output data will not be accurate data for 200 ns or 10 clock cycles, whichever is longer.

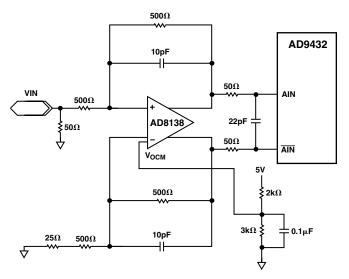

#### Using the AD8138 to Drive the AD9432

A new differential output op amp from Analog Devices, Inc., the AD8138, can be used to drive the AD9432 in dc-coupled applications. The AD8138 was specifically designed for ADC driver applications. Superior SNR performance is maintained up to analog frequencies of 30 MHz. The AD8138 op amp provides single-ended-to-differential conversion, providing for a low-cost option to transformer coupling for ac applications as well.

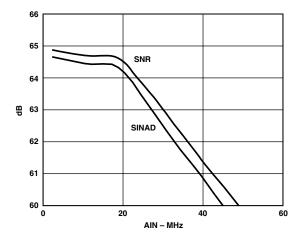

The circuit in Figure 10 was breadboarded and the measured performance is shown in Figures 11 and 12. The figures shown are for  $\pm 5$  V supplies at the AD8138—performance dropped by about 1 dB-2 dB with a single 5 V supply at the AD8138.

Figure 11 shows SNR and SINAD for a -1 dBFS analog input frequency varied from 2 MHz to 40 MHz with an encode rate of 105 MSPS. The measurements are for nominal conditions at room temperature. Figure 12 shows the second and third harmonic distortion performance under the same conditions. The dc common-mode voltage for the AD8138 outputs can be adjusted via input  $V_{OCM}$  to provide the 3 V common-mode voltage the AD9432 inputs require.

Figure 10. AD8138/AD9432 Schematic

Figure 11. Measured SNR and SINAD (Encode = 105 MSPS)

Figure 12. Measured Second and Third Order Harmonic Distortion (Encode = 105 MSPS)

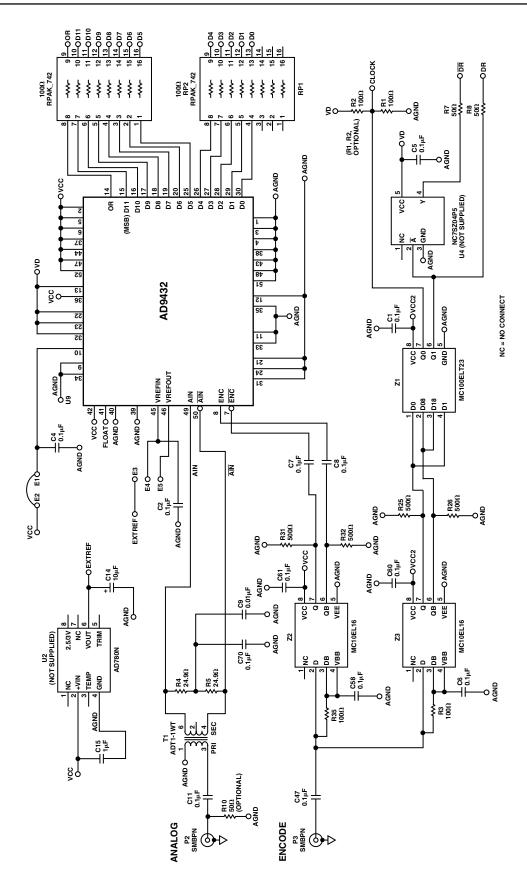

#### **EVALUATION BOARD**

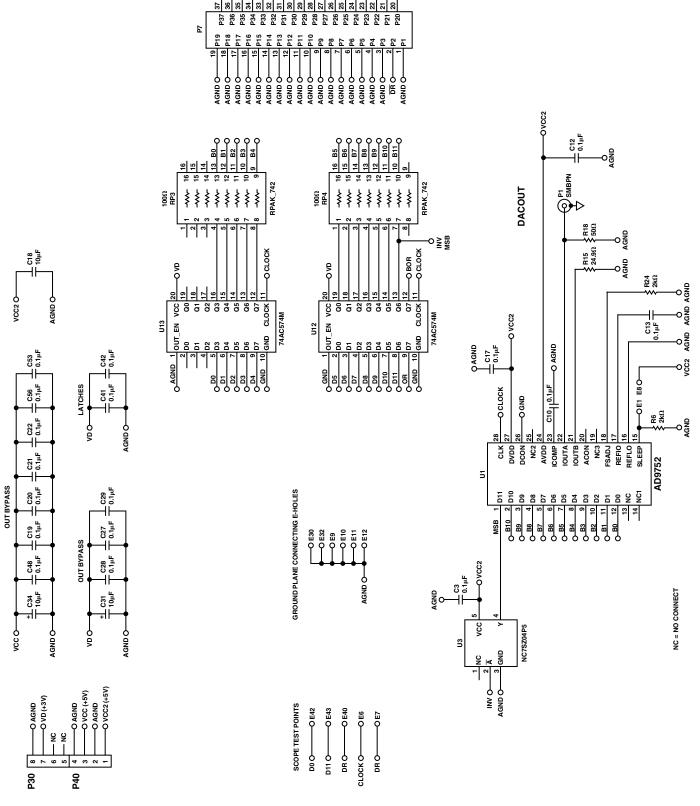

The AD9432 evaluation board offers an easy way to test the AD9432. It requires an analog signal, encode clock, and power supplies as inputs. The clock is buffered on the board to provide the clocks for an on-board DAC and latches. The digital outputs and output clock are available at a standard 37-pin connector P7.

#### **Power Connector**

Power is supplied to the board via two detachable 4-pin power strips P30, P40.

#### P40

| P1 | VCC2 | 5 V/165 mA | DAC Supply        |

|----|------|------------|-------------------|

| P2 | GND  |            |                   |

| P3 | VCC  | 5 V/200 mA | ADC Analog Supply |

| P4 | GND  |            |                   |

#### **P30**

| P5<br>P6<br>P7<br>P8 |     | No Connect<br>No Connect<br>Latch, ADC Digital Output Supply |

|----------------------|-----|--------------------------------------------------------------|

| P8                   | GND |                                                              |

#### **Analog Inputs**

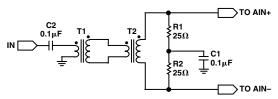

The evaluation board accepts a 2 V p-p analog input signal at SMB connector P2. This single-ended signal is ac-coupled by capacitor C11 and drives a wideband RF transformer T1 (Mini-Circuits ADT1-1WT) that converts the single-ended signal to a differential signal. (*The AD9432 should be driven differentially to provide optimum performance.*) The evaluation board is shipped with termination resistors R4, R5, which provide the effective 50  $\Omega$  termination impedance; input termination resistor R10 is optional. Note: The second harmonic distortion that some RF transformers tend to introduce at high frequencies can be reduced by coupling two transformers in series as shown in Figure 13. (Improvements on the order of 3 dB-4 dB can be realized.)

Figure 13. Improving Second Harmonic Distortion Performance

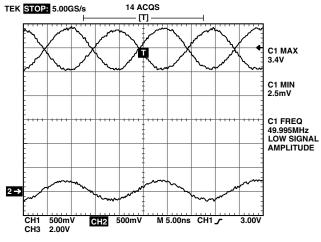

#### Figure 14. Analog Input Levels

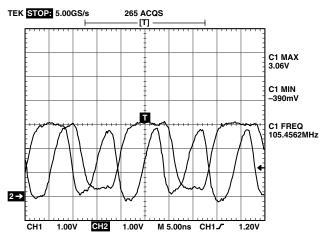

The full-scale analog inputs to the ADC should be two 1 V p-p signals 180 degrees out of phase with each other, as shown in Figure 14. The analog inputs are dc biased by two on-chip resistor dividers that set the common-mode voltage to approximately  $0.6 \times VCC$  ( $0.6 \times 5 = 3$  V). AIN+ and AIN- each vary between 2.5 V and 3.5 V as shown in the two upper traces in Figure 14. The lower trace is the input at SMB P2 (*on a 2 V/div scale*).

#### Encode

The encode input to the board is at SMB connector P3. The (>1 V p-p) input is ac-coupled and drives two high-speed differential line receivers (MC10EL16). These receivers provide subnanosecond rise times at their outputs—a requirement for the ADC clock inputs for optimum performance. The EL16 outputs are PECL levels and must be ac-coupled to meet the common-mode dc levels required at the AD9432 encode inputs. A PECL/TTL translator (MC100ELT23), provides the clocks required at the output latches, DAC, and 37-pin connector.

Note: Jitter performance on the clock source is critical at this performance level; a stable, crystal-controlled signal generator is used to generate all of the ADC performance plots. Figure 15 shows the Encode+ clock at the ADC. The 3 V latch clock generated on the card is also shown in the plot.

Figure 15. Encode+ Clock and Latch Clock

#### DATA OUTPUTS

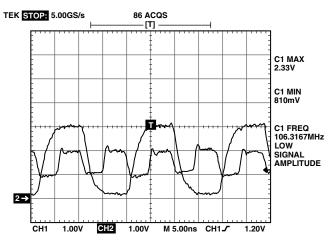

The ADC digital outputs are latched on the board by two 574s; the latch outputs are available at the 37-pin connector at Pins 25–36. A latch output clock (data ready) is available at Pin 21, with the complement at Pin 2. There are series termination resistors on the data and clock outputs. These can be changed if required to accommodate different loading situations. Figure 16 shows a data bit switching and output clock (DR) at the connector.

Figure 16. Data Bit and Clock at 37-Pin Connector

#### REFERENCE

The AD9432 has an on-chip reference of 2.5 V available at VREFOUT (Pin 46). Most applications will simply tie this output to the VREFIN input (Pin 45). This is accomplished jumping E4 to E6 on the board. An external voltage reference can drive the VREFIN pin if desired by strapping E4 to E3 and placing an AD780 voltage reference on the board (not supplied).

#### DAC

The evaluation board has an on-board reconstruction DAC (AD9752). This is placed only to facilitate testing and debug of the board. It should not be used to measure the performance of the ADC, as it will not accurately indicate the ADC performance. The DAC output is available at SMB P1. It will drive a 50  $\Omega$  load. Provision to power down the DAC is at Pin 15 at the DAC.

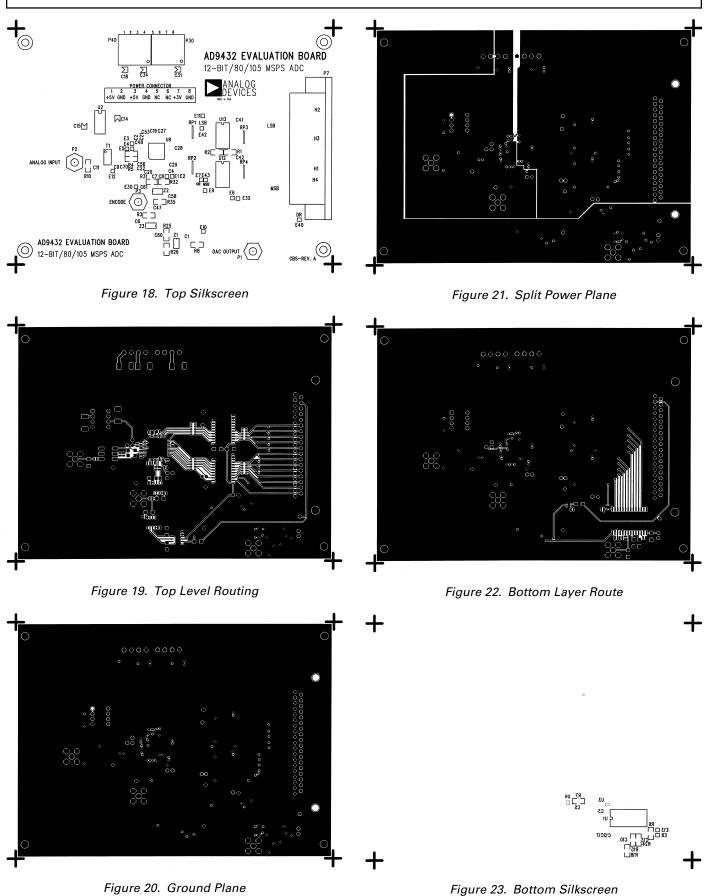

#### PCB LAYOUT

The PCB is designed on a four-layer (1 oz. Cu) board. Components and routing are on the top layer with a ground flood for additional isolation. Test and ground points were judiciously placed to facilitate high-speed probing. A common ground plane exists on the second layer. The third layer has three split power planes, two for the ADC and one for support logic. The DAC, components, and routing are located on the bottom layer.

#### TROUBLESHOOTING

If the board does not seem to be working correctly, try the following:

- Verify power at IC pins.

- Check that all jumpers are in the correct position for the desired mode of operation.

- Verify VREF is at 2.5 V.

- Try running encode clock and analog inputs at low speeds (10 MSPS/1 MHz) and monitor 574 outputs, DAC output, and ADC outputs for toggling.

The AD9432 Evaluation Board is provided as a design example for customers of Analog Devices, Inc. ADI makes no warranties, express, statutory, or implied, regarding merchantability or fitness for a particular purpose.

#### PCB Bill of Materials

| #  | Quantity | REFDES                                                                                        | Device                     | Package    | Value                     |

|----|----------|-----------------------------------------------------------------------------------------------|----------------------------|------------|---------------------------|

| 1  | 30       | C1–C8, C10–C13, C17, C19–C22,<br>C27–C29, C41, C42, C47, C48,<br>C53, C56, C58, C60, C61, C70 | Capacitor                  | 603        | 0.1 µF                    |

| 2  | 1        | C9                                                                                            | Capacitor                  | 603        | 0.01 µF                   |

| 3  | 4        | C14, C18, C31, C34                                                                            | Capacitor                  | CAPTAJD    | 10 µF                     |

| 4  | 1        | C15                                                                                           | Capacitor                  | CAPTAJD    | 1 μF                      |

| 5  | 18       | E1-E13, E30, E32, E40, E42, E43                                                               | E-HOLE                     | Test Point |                           |

| 6  | 3        | P1, P2, P3                                                                                    | Connector                  | SMB        |                           |

| 7  | 1        | P7                                                                                            | 37-Pin Connector           | Female     | AMP 747462-2              |

| 8  | 2        | P30, P40                                                                                      | Power Connector            |            |                           |

| 9  | 6        | R1, R2, R7, R8, R10, R18<br>(R1, R2, R10 Optional)                                            | Resistor                   | 1206       | 50 Ω                      |

| 10 | 2        | R3, R35                                                                                       | Resistor                   | 1206       | 100 Ω                     |

| 11 | 4        | R25, R26, R31, R32                                                                            | Resistor                   | 1206       | 500 Ω                     |

| 12 | 2        | R6, R24                                                                                       | Resistor                   | 1206       | 2 kΩ                      |

| 13 | 4        | RP1–RP4                                                                                       | RES PAK                    |            | 100 Ω                     |

| 14 | 1        | T1                                                                                            | Transformer                |            | Mini-Circuits<br>ADT1-1WT |

| 15 | 1        | U1                                                                                            | DAC                        | SOIC       | AD9752                    |

| 16 | 1        | U2                                                                                            | Reference (Not Supplied)   | SOIC       | AD780N                    |

| 17 | 2        | U3, U4                                                                                        | Inverter (U4 Not Supplied) | SC70       | NC7SZ04P5                 |

| 18 | 1        | U9                                                                                            | ADC                        | 52QFP      | AD9432                    |

| 19 | 2        | U12–U13                                                                                       | Latch                      | SOIC       | 74AC574M                  |

| 20 | 1        | Z1                                                                                            | PECL/TTL Translator        | SOIC       | MC100ELT23                |

| 21 | 2        | Z2, Z3                                                                                        | Differential Receiver      | SOIC       | MC10EL16                  |

| 22 | 3        | R4, R5, R15                                                                                   | Resistor                   | 1206       | 24.9 Ω                    |

Figure 17a. PCB Schematic

Downloaded from **Elcodis.com** electronic components distributor

AD9432

OBOR **OB10** 0B11 0 B9 088 0 B7 0 B6 0 B5 0 B4 OB3 OB2 OBO

ODR

081

Figure 17b. PCB Schematic (Continued)

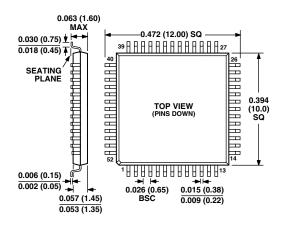

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 52-Lead Plastic Quad Flatpack (LQFP) (ST-52)

CONTROLLING DIMENSIONS ARE IN MILLIMETERS; INCH DIMENSIONS ARE ROUNDED-OFF MILLIMETER EQUIVALENTS FOR REFERENCE ONLY AND ARE NOT APPROPRIATE FOR USE IN DESIGN

2. ALTHOUGH NOT REQUIRED IN ALL APPLICATIONS, THE AD9432 HAS AN EXPOSED METALLIC PAD ON THE PACKAGE BOTTOM WHICH IS INTENDED TO ENHANCE THE HEAT REMOVAL PATH. TO MAXIMIZE THE REMOVAL OF HEAT, A LAND PATTERN WITH CLOSELY SPACED THERMAL VIAS TO THE GROUND PLANE(S) SHOULD BE INCORPORATED ON THE PCB WITHIN THE FOOTPRINT OF THE PACKAGE CORRESPONDING TO THE EXPOSED METAL PAD DIMENSIONS OF THE PACKAGE. THE SOLDERABLE LAND AREA SHOULD BE SOLDER MASK DEFINED AND BE AT LEAST THE SAME SIZE AND SHAPE AS THE EXPOSED PAD AREA ON THE PACKAGE. AT LEAST 0.25 MM CLEARANCE BETWEEN THE OUTER EDGES OF THE LAND PATTERN AND THE INNER EDGES OF THE PAD PATTERN SHOULD BE MAINTAINED TO AVOID ANY SHORTS.

# **Revision History**

| Location                                     | Page |

|----------------------------------------------|------|

| Data Sheet changed from REV. D to REV. E.    |      |

| Edits to SPECIFICATIONS                      | 3    |

| Edits to ABSOLUTE MAXIMUM RATINGS            | 3    |

| Edits to ORDERING GUIDE                      | 3    |

| Addition of text to USING THE AD9432 section | 9    |

| Edits to Figure 17a                          | 13   |

| Edits to Figure 17b                          | 14   |

| Addition of SQ-52 Package Outline            | 16   |

C00587-0-1/02(E)