# Digitally Programmable Delay Generator

AD9500

#### **FEATURES**

10 ps Delay Resolution

2.5 ns to 10 μs Full-Scale Range

Fully Differential Inputs

Separate Trigger and Reset Inputs

Low Power Dissipation—310 mW

MIL-STD-883 Compliant Versions Available

## APPLICATIONS ATE

Pulse Deskewing Arbitrary Waveform Generators High Stability Timing Source Multiple Phase Clock Generators

#### **GENERAL DESCRIPTION**

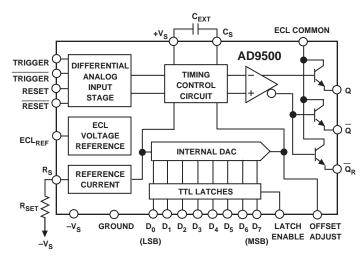

The AD9500 is a digitally programmable delay generator, which provides programmed delays, selected through an 8-bit digital code, in resolutions as small as 10 ps. The AD9500 is constructed in a high performance bipolar process, designed to provide high speed operation for both digital and analog circuits.

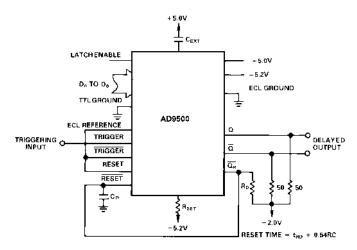

The AD9500 employs differential TRIGGER and RESET inputs which are designed primarily for ECL signal levels but function with analog and TTL input levels. An onboard ECL reference midpoint allows both of the inputs to be driven by either single ended or differential ECL circuits. The AD9500 output is a complementary ECL stage, which also provides a  $\overline{Q}_R$  parallel output circuit to facilitate reset timing implementations.

The digital control data is passed to the AD9500 through a transparent latch controlled by the LATCH ENABLE signal. In the transparent mode, the internal DAC of the AD9500 will attempt to follow changes at the inputs. The LATCH ENABLE is otherwise used to strobe the digital data into the AD9500 latches

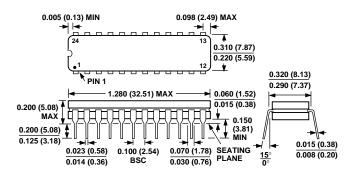

The AD9500 is available as an industrial temperature range device, -25°C to +85°C, and as an extended temperature range device, -55°C to +125°C. Both grades are packaged in a 24-lead cerdip (0.3" package width), as well as 28-leaded and leadless surface mount packages. The AD9500 is available in versions compliant with MIL-STD-883. Refer to the Analog Devices Military Products Databook or current AD9500/883B data sheet for detailed specifications.

#### REV. D

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

#### FUNCTIONAL BLOCK DIAGRAM

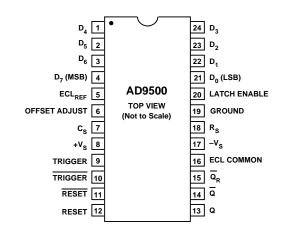

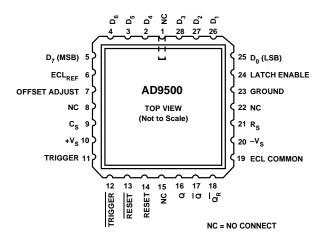

#### PIN CONFIGURATIONS

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A.

Tel: 781/329-4700 World Wide Web Site: http://www.analog.com

Fax: 781/326-8703 © Analog Devices, Inc., 1999

# AD9500-SPECIFICATIONS

# $\textbf{ELECTRICAL CHARACTERISTICS}^{2} \ \ (\text{Supply Voltages } + \text{V}_{\text{S}} = +5.0 \ \text{V}, \ \text{V}_{\text{S}} = -5.2 \ \text{V}; \ \text{C}_{\text{EXT}} = 0 \ \text{pF}; \ \text{R}_{\text{SET}} = 500 \ \Omega \ \text{unless otherwise noted})$

|                                                            | Test  |                | A   | 25°C to +85<br>D9500BP/I |      | A   | 5°C to +12<br>D9500TE/                |            |       |

|------------------------------------------------------------|-------|----------------|-----|--------------------------|------|-----|---------------------------------------|------------|-------|

| Parameter                                                  | Level | Temp           | Min | Тур                      | Max  | Min | Тур                                   | Max        | Units |

| RESOLUTION                                                 |       |                | 8   |                          |      | 8   |                                       |            | Bits  |

| ACCURACY <sup>3</sup>                                      | _     | . 2500         |     |                          | o =  |     |                                       | ^ <b>-</b> | 1.00  |

| Differential Linearity                                     | I     | +25°C          |     |                          | 0.5  |     |                                       | 0.5        | LSB   |

| Integral Linearity                                         | I     | +25°C<br>+25°C | ,   | ~                        | 1.0  | _   | · · · · · · · · · · · · · · · · · · · | 1.0        | LSB   |

| Monotonicity                                               | 1     | +25°C          | ,   | Guaranteed               | [    |     | Guaranteed                            |            |       |

| DIGITAL INPUT                                              |       | F "            |     |                          |      |     |                                       |            |       |

| Logic "1" Voltage                                          | VI    | Full           | 2.0 |                          | 2.0  | 2.0 |                                       |            | V     |

| Logic "0" Voltage                                          | VI    | Full           |     |                          | 0.8  |     |                                       | 0.8        | V.    |

| Logic "1" Current                                          | VI    | Full           |     |                          | 5    |     |                                       | 5          | μΑ    |

| Logic "0" Current                                          | VI    | Full           |     |                          | 5    |     |                                       | 5          | μΑ    |

| Digital Input Capacitance                                  | VI    | +25°C          |     | 2.4                      | 5.5  |     | 2.4                                   | 5.5        | pF    |

| Data Setup Time <sup>4</sup>                               | V     | +25°C          |     | 0.4                      | 0.75 |     | 0.4                                   | 0.75       | ns    |

| Data Hold Time <sup>5</sup>                                | V     | +25°C          |     | 0.4                      | 0.75 |     | 0.4                                   | 0.75       | ns    |

| Latch Pulsewidth (t <sub>LPW</sub> )                       | V     | +25°C          | 3.0 |                          |      | 3.0 |                                       |            | ns    |

| RESET/TRIGGER INPUTS <sup>6</sup>                          |       |                |     |                          |      |     |                                       |            |       |

| TRIGGER Input Voltage Range                                | IV    | Full           |     | -2.5; 4.5                |      |     | -2.5; 4.5                             |            | V     |

| RESET Input Voltage Range                                  | IV    | Full           |     | -2.5; 2.0                |      |     | -2.5; 2.0                             |            | V     |

| Differential Switching Voltage                             | IV    | Full           |     | 40                       | 300  |     | 40                                    | 300        | mV    |

| Input Bias Current                                         | I     | +25°C          |     | 40                       | 50   |     | 40                                    | 50         | μA    |

|                                                            | VI    | Full           |     |                          | 75   |     |                                       | 75         | μA    |

| Input Resistance                                           | IV    | +25°C          |     | 4                        |      |     | 4                                     |            | kΩ    |

| Input Capacitance                                          | IV    | +25°C          |     | 6.5                      | 7.25 |     | 6.5                                   | 7.25       | pF    |

| Minimum Input Pulsewidth                                   |       |                |     |                          |      |     |                                       |            |       |

| $t_{TPW}$ , $t_{RPW}$                                      | V     | +25°C          |     | 2.0                      |      |     | 2.0                                   |            | ns    |

| DYNAMIC PERFORMANCE <sup>7</sup>                           |       |                |     |                          |      |     |                                       |            |       |

| Maximum Trigger Rate                                       | IV    | +25°C          |     | 60                       |      |     | 60                                    |            | MHz   |

| Minimum Propagation Delay $(t_{PD})^8$                     | I     | +25°C          | 5.4 | 6.4                      | 7.4  | 5.4 | 6.4                                   | 7.4        | ns    |

| Minimum Propagation Delay TC                               | V     | Full           |     | 7.5                      |      |     | 7.5                                   |            | ps/°C |

| Full-Scale Range TC <sup>9</sup>                           | V     | Full           |     | 0.5                      |      |     | 0.5                                   |            | ps/°C |

| Delay Uncertainty (Jitter)                                 | V     | +25°C          |     | 10                       |      |     | 10                                    |            | ps    |

| Reset Propagation Delay $(t_{RD})^{10}$                    | I     | +25°C          | 5.4 | 6.4                      | 7.4  | 5.4 | 6.4                                   | 7.4        | ns    |

| Reset-to-Trigger Holdoff $(t_{THO})^{11}$                  | IV    | +25°C          | 0.2 | 0                        |      | 0.2 | 0                                     |            | ns    |

| Trigger-to-Reset Holdoff (t <sub>RHO</sub> ) <sup>12</sup> | IV    | +25°C          | 2.0 | 1.5                      |      | 2.0 | 1.5                                   |            | ns    |

| Minimum Output Pulsewidth                                  | V     | +25°C          |     | 3.3                      |      |     | 3.3                                   |            | ns    |

| Output Rise Time <sup>7</sup>                              | I     | +25°C          |     |                          | 2.0  |     |                                       | 2.0        | ns    |

| Output Fall Time <sup>7</sup>                              | I     | +25°C          |     |                          | 2.0  |     |                                       | 2.0        | ns    |

| Delay Coefficient Settling Time $(t_{DAC})^{13}$           | V     | +25°C          |     | 29                       |      |     | 29                                    |            | ns    |

| Linear Ramp Settling Time (t <sub>LRS</sub> )              | V     | +25°C          |     | 22                       |      |     | 22                                    |            | ns    |

-2- REV. D

|                                                | Test  |       | _    | 5°C to +8<br>D9500BP |      | _    | 5°C to +1<br>D9500TE |      |       |

|------------------------------------------------|-------|-------|------|----------------------|------|------|----------------------|------|-------|

| Parameter                                      | Level | Temp  | Min  | Typ                  | Max  | Min  | Typ                  | Max  | Units |

| SUPPORT FUNCTIONS                              |       |       |      |                      |      |      |                      |      |       |

| $\mathrm{ECL}_{\mathrm{REF}}$                  | IV    | +25°C | -1.4 | -1.3                 | -1.2 | -1.4 | -1.3                 | -1.2 | V     |

| ECL <sub>REF</sub> Voltage Drift <sup>14</sup> | V     | Full  |      | 1.1                  |      |      | 1.1                  |      | mV/°C |

| Offset Adjust Range                            | V     | Full  |      | -2                   |      |      | -2                   |      | mA    |

| DIGITAL OUTPUTS <sup>7</sup>                   |       |       |      |                      |      |      |                      |      |       |

| Logic "1" Voltage                              | VI    | Full  | -1.1 |                      |      | -1.1 |                      |      | V     |

| Logic "0" Voltage                              | VI    | Full  |      |                      | -1.5 |      |                      | -1.5 | V     |

| POWER SUPPLY <sup>15</sup>                     |       |       |      |                      |      |      |                      |      |       |

| Positive Supply Current (+5.0 V)               | I     | +25°C |      | 24                   | 28   |      | 24                   | 28   | mA    |

|                                                | VI    | Full  |      |                      | 30   |      |                      | 30   | mA    |

| Negative Supply Current (-5.2 V)               | I     | +25°C |      | 37                   | 42   |      | 37                   | 42   | mA    |

|                                                | VI    | Full  |      |                      | 44   |      |                      | 44   | mA    |

| Nominal Power Dissipation                      | V     | +25°C |      | 312                  |      |      | 312                  |      | mW    |

| Power Supply Rejection Ratio <sup>16</sup>     |       |       |      |                      |      |      |                      |      |       |

| Full-Scale Range Sensitivity                   | I     | +25°C |      | 70                   | 300  |      | 70                   | 300  | ps/V  |

| Minimum Propagation Delay                      |       |       |      |                      |      |      |                      |      |       |

| Sensitivity                                    | I     | +25°C |      | 150                  | 500  |      | 150                  | 500  | ps/V  |

#### NOTES

<sup>1</sup>Absolute maximum ratings are limiting values, to be applied individually, and beyond which serviceability of the circuit may be impaired. Functional operability under any of these conditions is not necessarily implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

<sup>2</sup>Typical thermal impedance

$\begin{array}{ll} 24\text{-Lead Cerdip} & \theta_{JA} = 56^{\circ}\text{C/W}; \, \theta_{JC} = 16^{\circ}\text{C/W} \\ 28\text{-Leadless PLCC (Plastic)} & \theta_{JA} = 60^{\circ}\text{C/W}; \, \theta_{JC} = 22^{\circ}\text{C/W} \\ 28\text{-Leaded Ceramic LCC} & \theta_{JA} = 69^{\circ}\text{C/W}; \, \theta_{JC} = 25^{\circ}\text{C/W} \\ \end{array}$

Specifications subject to change without notice.

#### **EXPLANATION OF TEST LEVELS**

#### Test Level

- I 100% production tested.

- II 100% production tested at +25°C, and sample tested at specified temperatures.

- III Periodically sample tested.

- IV Parameter is guaranteed by design and characterization testing.

- V Parameter is a typical value only.

- VI All devices are 100% production tested at +25°C. 100% production tested at temperature extremes for extended temperature devices; sample tested at temperature extremes for commercial/industrial devices.

#### ORDERING GUIDE

| Model    | Temperature<br>Ranges | Package<br>Descriptions     | Package<br>Options |

|----------|-----------------------|-----------------------------|--------------------|

| AD9500BP | −25°C to +85°C        | 28-Leadless PLCC (Plastic), |                    |

|          |                       | Industrial Temperature      | P-28A              |

| AD9500BQ | −25°C to +85°C        | 24-Lead Cerdip,             |                    |

|          |                       | Industrial Temperature      | Q-24               |

| AD9500TE | −55°C to +125°C       | 28-Leaded LCC,              |                    |

|          |                       | Extended Temperature        | E-28A              |

| AD9500TQ | –55°C to +125°C       | 24-Lead Cerdip,             |                    |

|          |                       | Extended Temperature        | Q-24               |

REV. D –3–

$<sup>{}^{3}</sup>R_{SET} = 10 \text{ k}\Omega \text{ (Full-scale delay = 100 ns)}.$

<sup>&</sup>lt;sup>4</sup>The digital data inputs must remain stable for the specified time prior to the LATCH ENABLE signal.

<sup>&</sup>lt;sup>5</sup>The digital data inputs must remain stable for the specified time after the LATCH ENABLE signal.

<sup>&</sup>lt;sup>6</sup>The TRIGGER and RESET inputs are differential and must be driven relative to one another. Both of these inputs are ECL compatible, but can also be used with TTL logic families in a limited fashion.

$<sup>^{7}</sup>$ Outputs terminated through 50 Ω resistors to −2.0 V.

<sup>&</sup>lt;sup>8</sup>Program Delay = 0.0 ps (Digital Data = 00<sub>H</sub>). In Operation, any programmed delays are in addition to the Minimum Propagation Delay.

<sup>&</sup>lt;sup>9</sup>Change in total delay through AD9500, exclusive of changes in minimum propagation delay t<sub>PD</sub>.

<sup>&</sup>lt;sup>10</sup>Measured from the 50% transition point of the reset signal input, to the 50% transition point of the resetting output.

$<sup>^{11}</sup>$ Minimum time from falling edge of RESET to triggering input, to ensure a valid output event.

<sup>&</sup>lt;sup>12</sup>Minimum time from triggering event to rising edge of RESET, to ensure a valid output event.

<sup>13</sup>Measured from the LATCH ENABLE input to the point when the AD9500 becomes 8-bit accurate again, after a full-scale change in the programmed delay.

<sup>&</sup>lt;sup>14</sup>Standard 10K and 10KH ECL families operate with a 1.1 mV/°C drift by design.

$<sup>^{15}</sup>$ Supply voltages should remain stable within  $\pm 5\%$  for normal operation.

$<sup>^{16}</sup>$ Measured at  $\pm 5\%$  of  $-V_S$  and  $+V_S$ .

## AD9500

#### PIN FUNCTION DESCRIPTIONS

| Pin Name                             | Description                                                                                                                                                                                                                                                                                                                                                          |

|--------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $D_4$ – $D_6$                        | One of eight digital inputs used to set the programmed delay.                                                                                                                                                                                                                                                                                                        |

| D <sub>7</sub> (MSB)                 | One of eight digital inputs used to set the programmed delay. $D_7$ (MSB) is the most significant bit of the digital input word.                                                                                                                                                                                                                                     |

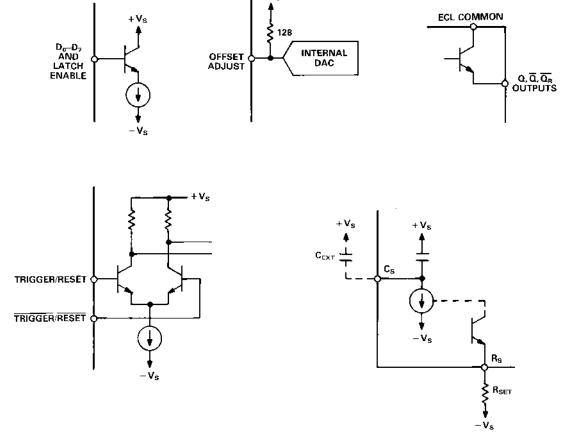

| $ECL_{REF}$                          | ECL midpoint reference, nominally $-1.3$ V. Use of the ECL <sub>REF</sub> allows either of the TRIGGER or RESET inputs to be configured for single-ended ECL inputs.                                                                                                                                                                                                 |

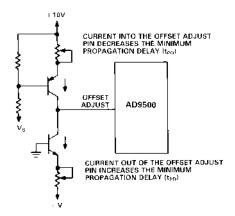

| OFFSET ADJUST                        | The OFFSET ADJUST is used to adjust the minimum propagation delay $(t_{PD})$ , by pulling or pushing a small current out of or into the pin.                                                                                                                                                                                                                         |

| $C_{S}$                              | $C_S$ allows the full-scale range to be extended by using an external timing capacitor. The value of $C_{EXT}$ , connected between $C_S$ and $+V_S$ , may range from no external capacitance to 0.1 $\mu$ F+. See $R_S$ ( $C_{INTERNAL}$ = 10 pF).                                                                                                                   |

| +V <sub>S</sub>                      | Positive supply terminal, nominally +5.0 V.                                                                                                                                                                                                                                                                                                                          |

| TRIGGER                              | Noninverted input of the edge-sensitive differential trigger input stage. The output at Q will be delayed by the programmed delay, after the triggering event. The programmed delay is set by the digital input word. The TRIGGER input must be driven in conjunction with the TRIGGER input.                                                                        |

| TRIGGER                              | Inverted input of the edge-sensitive differential trigger input stage. The output at Q will be delayed by the programmed delay, after the triggering event. The programmed delay is set by the digital input word. The TRIGGER input must be driven in conjunction with the TRIGGER input.                                                                           |

| RESET                                | Inverted input of the level-sensitive differential reset input stage. The output at Q will be reset after a signal is received at the reset inputs. In the "minimum configuration," the minimum output pulsewidth will be equal to the "reset propagation delay," $t_{RD}$ . The RESET input must be driven in conjunction with the RESET input.                     |

| RESET                                | Noninverted input of the level-sensitive differential reset input stage. The output at Q will be reset after a signal is received at the reset inputs. In the "minimum configuration," the minimum output pulsewidth will be equal to the "reset propagation delay," $t_{RD}$ . The $\overline{RESET}$ input must be driven in conjunction with the RESET input.     |

| Q                                    | One of two complementary ECL outputs. A "triggering" event at the inputs will produce a logic HIGH on the Q output. A "resetting" event at the inputs will produce a logic LOW on the Q output.                                                                                                                                                                      |

| $\overline{Q}$                       | One of two complementary ECL outputs. A "triggering" event at the inputs will produce a logic LOW on the $\overline{Q}$ output. A "resetting" event at the inputs will produce a logic HIGH on the $\overline{Q}$ output.                                                                                                                                            |

| $\overline{\mathrm{Q}_{\mathtt{R}}}$ | $\overline{Q_R}$ output is parallel to the $\overline{Q}$ output. The $\overline{Q_R}$ output is typically used to drive delaying circuits for extending output pulsewidths. A "triggering" event at the inputs will produce a logic LOW on the $\overline{Q_R}$ output. A "resetting" event at the inputs will produce a logic HIGH on the $\overline{Q_R}$ output. |

| ECL COMMON                           | The collector common for the ECL output stage. The collector common may be tied to +5.0 V, but normally it is tied to the circuit ground for standard ECL outputs.                                                                                                                                                                                                   |

| $-V_S$                               | Negative supply terminal, nominally –5.2 V.                                                                                                                                                                                                                                                                                                                          |

| $R_S$                                | $R_S$ is the reference current setting terminal. An external setting resistor, $R_{SET}$ , connected between $R_S$ and $-V_S$ determines the internal reference current. See $C_S$ (250 $\Omega \le R_{SET} \le 50$ k $\Omega$ ).                                                                                                                                    |

| GROUND                               | The ground return for the TTL and analog inputs.                                                                                                                                                                                                                                                                                                                     |

| LATCH ENABLE                         | Transparent TTL latch control line. A logic HIGH on the LATCH ENABLE freezes the digital code at the logic inputs. A logic LOW on the LATCH ENABLE allows the internal current levels to be continuously updated through the logic inputs $D_0$ thru $D_7$ .                                                                                                         |

| D <sub>0</sub> (LSB)                 | One of eight digital inputs used to set the programmed delay. $D_0$ (LSB) is the least significant bit of the digital input word.                                                                                                                                                                                                                                    |

| $D_3 - D_1$                          | One of eight digital inputs used to set the programmed delay.                                                                                                                                                                                                                                                                                                        |

-4- REV. D

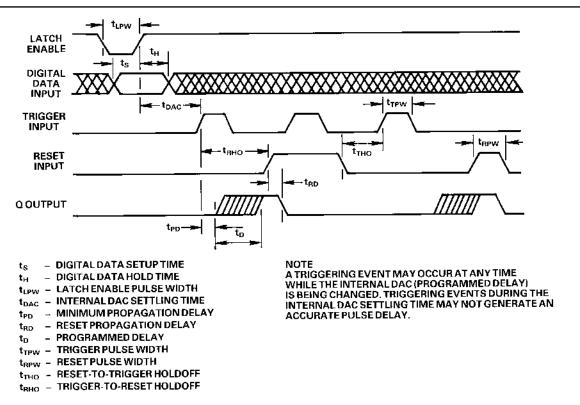

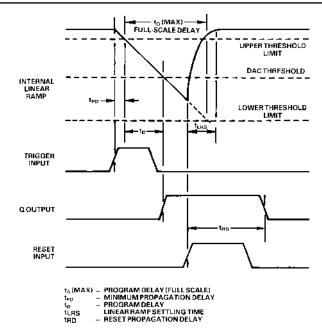

Figure 1. System Timing Diagram

# D<sub>7</sub> (MSB) O<sub>6</sub> D<sub>7</sub> D<sub>8</sub> D<sub>7</sub> D<sub>7</sub> D<sub>7</sub> D<sub>8</sub> ILSB) CFFSET ADJUST C<sub>2</sub> SER PRIGGER RESET RESET Q Q Q<sub>8</sub> TRIGGER

**DIE LAYOUT**

#### MECHANICAL INFORMATION

| Die Dimensions                                   |

|--------------------------------------------------|

| Pad Dimensions                                   |

| Metalization                                     |

| Backing None                                     |

| Substrate PotentialV <sub>S</sub>                |

| Passivation                                      |

| Die Attach                                       |

| Bond Wire 1.25 mil, Aluminum; Ultrasonic Bonding |

| or 1 mil, Gold; Gold Ball Bonding                |

REV. D \_5\_

Figure 2. Input/Output Circuits

#### **INSIDE THE AD9500**

The heart of the AD9500 is the linear ramp generator. A triggering event at the input of the AD9500 initiates the ramp cycle. As the ramp voltage falls, it will eventually go below the threshold set up by the internal DAC (digital-to-analog converter). A comparator monitors both the linear ramp voltage and the DAC threshold level. The output of the comparator serves as the output for the AD9500, and the interval from the trigger until the output switches is the total delay time of the AD9500.

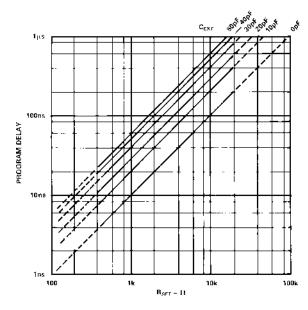

The total delay through the AD9500 is made up of two components. The first is the full-scale programmed delay,  $t_{D~(max)}$ , determined by  $R_{SET}$  and  $C_{EXT}$ . The second component of the total delay is the minimum propagation delay through the AD9500 ( $t_{PD}$ ). The full-scale delay is variable from 2.5 ns to greater than 1 ms. The internal DAC is capable of generating 256 separate programmed delays within the full-scale range (this gives 10 ps increments for a 2.5 ns full-scale setting).

The actual programmed delay is directly related to both the digital control data (digital data to the internal DAC) and the RC time constant established by  $R_{SET}$  and  $C_{EXT}$ . The specific relationship is as follows:

Total Delay = Minimum Propagation Delay + Programmed Delay =  $t_{PD}$  + (digital value/256)  $R_{SET}$  ( $C_{EXT}$  + 10 pF)

Figure 3. Typical Programmed Delay Ranges

The internal DAC determines the programmed delay by way of the threshold level at its output. The LATCH ENABLE control for the onboard latch is active (latches) logic "HIGH." In the logic "LOW" state, the latch is transparent, and the internal DAC will attempt to follow changes at the digital data inputs. Both the LATCH ENABLE control and the data inputs are TTL compatible. The internal DAC may be updated at any time, but full timing accuracy may not be attained unless triggering events are held off until after the DAC settling time (t<sub>DAC</sub>).

Figure 4. Internal Timing Diagram

On resetting, the ramp voltage held in the timing capacitor ( $C_{\rm EXT}$  + 10 pF) is discharged. The AD9500 discharges the bulk of the ramp voltage very quickly, but to maintain absolute accuracy, subsequent triggering events should be held off until after the linear ramp settling time ( $t_{\rm LRS}$ ). Applications which employ high frequency triggering at a constant rate will not be affected by the slight settling errors since they will be constant for fixed reset-to-trigger cycles.

The RESET and TRIGGER inputs of the AD9500 are differential and must be driven relative to one another. Accordingly, the TRIGGER and RESET inputs are ideally suited for analog or complementary input signals. Single-ended ECL input signals can be accommodated by using the ECL midpoint reference (ECL<sub>REF</sub>) to drive one side of the differential inputs.

The output of the AD9500 consists of both Q and  $\overline{Q}$  driver stages, as well as the  $\overline{Q_R}$  output which is used primarily for extending the output pulsewidth. In the most direct reset configuration, either the Q or the  $\overline{Q}$  output is tied to the respective RESET input. This generates a delayed output pulse with a duration equal to the reset delay time  $(t_{RD})$  of approximately 6 ns. Note that the reset delay time  $(t_{RD})$  becomes extended for very small programmed delay settings. The duration of the output pulse can be extended by driving the reset inputs with the  $\overline{Q_R}$  output through an RC network (see "Extended Output Pulsewidth" application). Using the  $\overline{Q_R}$  output to drive the reset circuit avoids loading the Q or  $\overline{Q}$  outputs.

Values in the specification table are based on 5 ns FSR test conditions. Nearly all dynamic specifications degrade for longer full scales. For details of performance change, request the application note "Using Digitally Programmable Delay Generators."

REV. D -7-

#### AD9500

#### APPLICATIONS

The AD9500 is a very versatile device that is not difficult to use. Essentially there are only a few basic configurations which can be extended into a number of applications. The TRIGGER and RESET inputs of the AD9500 can be treated as single ended, or as differential, which allows the AD9500 to operate with a wide range of signal sources. The output pulse from the AD9500 can be reset in one of two ways, either immediately by driving the RESET inputs with the output itself, or in a delayed mode.

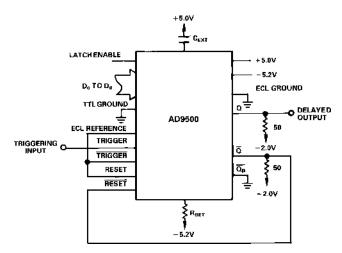

#### MINIMUM CONFIGURATION

The minimum configuration uses only one of the TRIGGER inputs. The other is connected to the ECL reference midpoint, ECL<sub>REF</sub>. This allows the AD9500 to be triggered with standard 10K or 10KH ECL signals. Once a triggering event occurs, the Q output will go into the logic HIGH state, and the  $\overline{Q}$  output will go into the logic LOW state after the programmed delay. The Q output is then used to drive the RESET input, causing the AD9500 to reset itself. The result is a delayed output pulse which is only as wide as the reset propagation delay ( $t_{RD}$ ).

Figure 5. Single Input-Minimum Timing Configuration

#### **EXTENDED OUTPUT PULSEWIDTHS**

The extended pulse configuration is similar to the minimum configuration. The difference here is that the output pulsewidth has been extended. Operation is identical in terms of triggering the AD9500; the functional difference is in the resetting circuit. In this case the  $\overline{Q_R}$  output is used to drive the  $\overline{RESET}$  input through a resistor/capacitor charging network. The charging network will cause the signal at the  $\overline{RESET}$  input to fall more slowly, which will extend the output pulsewidth. An added benefit of the extended pulsewidth configurations is that both

the Q and the  $\overline{Q}$  outputs are completely free for other uses.  $\overline{Q}$  has limited current drive; the minimum resistance for  $R_D$  should be  $4~k\Omega.$

Figure 6. Extended Output Pulsewidth Configuration

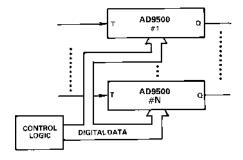

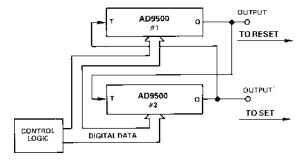

#### **MULTICHANNEL DESKEWING**

Perhaps the most appropriate use of the AD9500 is in multiple delay matching applications. Slight differences in impedance and cable length can create large timing skews within a high-speed system. Much of this skew can be eliminated by running each signal through an AD9500. With one line used as a standard, the programmed delays of the other AD9500s are adjusted to eliminate the timing skews. With the very fine timing adjustments possible from the AD9500 (as small as 10 ps), nearly any high-speed system should be able to automatically adjust itself to extremely tight tolerances.

Figure 7. Multiple Delay Matching

–8– REV. D

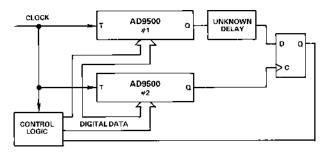

#### **MEASURING UNKNOWN DELAYS**

Two AD9500s can be combined to measure delays with a high degree of precision. One AD9500 is set with little or no programmed delay, and its output is used to drive the unknown delay circuit, which in turn drives the input of a "D" type flipflop. The second AD9500 is triggered along with the first, and its output provides a clocking signal for the flip-flop. The programmed delay of the second AD9500 is then varied to detect the output edge from the unknown delay circuit.

Detecting the output edge is relatively straightforward. If the programmed delay through the second AD9500 is too long, the flip-flop output will be at logic HIGH. If, on the other hand, the programmed delay through the second AD9500 is too short, the flip-flop output will be at logic LOW. When the programmed delay is properly adjusted, the flip-flop will likely bounce between logic HIGH and logic LOW. The digital code value used to create the second programmed delay is a direct indication of the delay through the unknown circuit. The most accurate results can only be attained by calibrating the system without the unknown delay circuit in place.

Figure 8. Measuring Unknown Delays

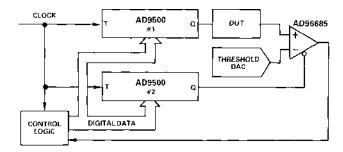

#### MEASURING HIGH SPEED AC WAVEFORMS

The same circuitry used to measure unknown delays can be extended to measure the time response of high speed ac waveforms. With the addition of a digital-to-analog converter and an analog comparator, the circuit functions very much like the previous application. The DAC sets a threshold level which drives one of the differential comparator inputs. The other comparator input is driven by the device under test (DUT). The output of the first AD9500 causes the DUT to produce an output. The second AD9500, which is also triggered along with the first AD9500, strobes the comparator latch enable.

If the DUT output is greater than the DAC threshold when the comparator is latched, the comparator output will be at logic HIGH. If the output is below the DAC threshold, the comparator will be at logic LOW. The programmed delay setting of the second AD9500 is adjusted to the point where the DUT output

equals the DAC threshold. By varying the DAC threshold level and adjusting the second AD9500 programmed delay, a point by point reconstruction of the ac waveform can be created.

Figure 9. Measuring AC Waveforms

#### PROGRAMMABLE OSCILLATOR

Another interesting use of the AD9500 is in a digitally programmable oscillator. The highly accurate delays generated by the AD9500 can be exploited to create a ring oscillator with variable duty cycle. The delayed output of the first AD9500 is used to drive the TRIGGER input of the second AD9500. The output of the second AD9500, in turn, is used to drive the TRIGGER input of the first AD9500. Together the two devices will alternately trigger each other creating two pulse chains on the outputs.

The total delay through both AD9500s combined, determines the period of the oscillation frequency. The duty cycle can be controlled by using the outputs to drive the SET and RESET inputs of a flip-flop. The total delay through the first AD9500 will control the flip-flop logic LOW output pulsewidth, and the second AD9500 will control the flip-flop logic HIGH output pulsewidth.

Figure 10. Ring Oscillator

REV. D \_9\_

#### AD9500

#### LAYOUT CONSIDERATIONS

The AD9500 is a precision timing device, and as such high frequency design techniques must be employed to achieve the best performance. The use of a low impedance ground plane is particularly important. Ideally the ground plane should be on the component side of the layout and extend under the AD9500, to shield it from system timing signals. Sockets pose a special problem for a circuit like the AD9500 because of the additional inter-lead capacitance they create. If sockets must be used, pin sockets are generally preferred. Power supply decoupling is also critical to a high-speed design; a 0.1  $\mu F$  ceramic capacitor and a 0.01  $\mu F$  mica capacitor for both power supplies should be very effective. DAC threshold stability can be improved by decoupling the OFFSET ADJUST pin to +5.0 V (note that this will lengthen the DAC settling time,  $t_{\rm DAC}$ )

#### **DELAY OFFSET ADJUSTMENTS**

As the full-scale delay is increased, a component of the minimum propagation delay also increases. This is caused by the additional time required by the ramp (now with a much "flatter" slope) to fall below the DAC threshold corresponding to the minimum propagation delay ( $t_{\rm PD}$ ). One means of decreasing the minimum propagation delay (when the full-scale delay, set by  $R_{\rm SET}$  and  $C_{\rm EXT}$  is large) is to offset the internal DAC threshold toward the initial ramp levels, thus reducing the time for the internal ramp to cross the threshold once the AD9500 is triggered.

Figure 11. The Offset Adjust Pin Can Be Used to Match Several AD9500s

The DAC levels are offset toward the initial ramp level by injecting a small current into the offset adjust pin. Note, however, that the ramp start-up region is less linear than the later portions of the ramp, which is the primary reason for the built-in offset. If the minimum propagation delay is kept above 5 ns (the linear portion of the ramp), no significant degradation in linearity should result. This concept can be extended to match the actual propagation delays of several AD9500s, by injecting or sinking a small current (<2 mA) into or out of each of the OFFSET ADJUST pins.

#### GENERAL PERFORMANCE ENHANCEMENTS

High speed operation is generally more consistent if  $C_{EXT}$  is kept small (i.e., no external capacitor) to maintain small discharge time constants. Integral linearity, however, benefits from larger values of  $C_{EXT}$  by buffering small system spikes and surges. Another means of improving integral linearity is to draw a small current ( $\approx$ 200  $\mu$ A) out of the OFFSET ADJUST pin with a 47 k $\Omega$  pull-down resistor. This has the effect of moving the internal DAC reference levels into a relatively more linear region of the ramp. This technique is generally only useful for small full-scale delay configurations. Its use with larger full-scale delays will extend the minimum propagation delay ( $t_{PD}$ ). A pull-up resistor to +5.0 V creates the opposite effect by reducing the minimum propagation delay ( $t_{PD}$ ) at the expense of increased reset propagation delay ( $t_{RD}$ ) and degraded linearity (see OFF-SET matching circuit).

Caution should be used when applying high slew rate data at the inputs of the AD9500. For data inputs with slew rates in excess of 1 V/ns, a 100  $\Omega$  series resistor should be utilized in the data path.

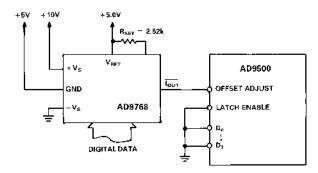

An external DAC can be used with the AD9500 for increased resolution and higher update rates. For the most part, a standard ECL DAC, operating between +5.0 V and ground, should work with the AD9500. The output of the external DAC must be connected to the OFFSET ADJUST pin of the AD9500 with the internal DAC turned off ( $D_0$  thru  $D_7$  at logic LOW). For normal operation, the external DAC output should range from 0 mA to -2 mA (sinking).

Figure 12. Operation with External DAC

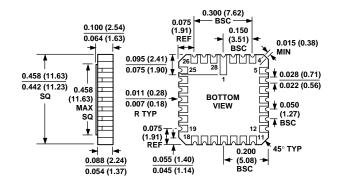

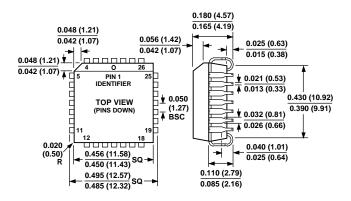

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

#### 24-Lead Cerdip (Q-24)

28-Leaded LCC (E-28A)

28-Leadless PLCC (P-28A)

REV. D –11–