# L64780 DVB-T COFDM Demodulator

## **Technical Manual**

February 2000

Order No. 114027

This document contains proprietary information of LSI Logic Corporation. The information contained herein is not to be used by or disclosed to third parties without the express written permission of an officer of LSI Logic Corporation.

Document DB14-000113-00, First Edition (February 2000)

This document describes LSI Logic Corporation's L64780 DVB-T COFDM

Demodulator and will remain the official reference source for all

revisions/releases of this product until rescinded by an update.

#### To receive product literature, visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

#### TRADEMARK ACKNOWLEDGMENT

The LSI Logic logo design and G10 are registered trademarks of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

Copyright © 1999, 2000 by LSI Logic Corporation. All rights reserved.

#### **Preface**

This book is the primary reference and technical manual for the L64780 DVB-T COFDM Demodulator. It contains a complete functional description as well as complete physical and electrical specifications for the LSI Logic L64780.

#### **Audience**

This document assumes you are familiar with digital video broadcasting, terrestrial television transmission and reception, modulation/demodulation, error control coding, digital signal processing, microprocessors, and related support devices. The people who benefit from this book are:

- engineers and managers evaluating the L64780 for use in a receiver for digital TV or cable data transmissions.

- engineers designing the L64780 into a system.

#### Organization

This document has the following chapters and appendixes:

- Chapter 1, Introduction, provides a brief overview of the L64780 and lists its features and benefits.

- Chapter 2, Architectural Overview, describes the architecture of the L64780 and gives a functional description of its main components.

- Chapter 3, Interfaces, describes the interfaces of the L64780 and gives a functional description of each.

- Chapter 4, Register Descriptions, provides a description of the registers that determine the functionality of the L64780.

Preface

- Chapter 5, **Signal Descriptions**, provides a description of the signals used and generated by the L64780.

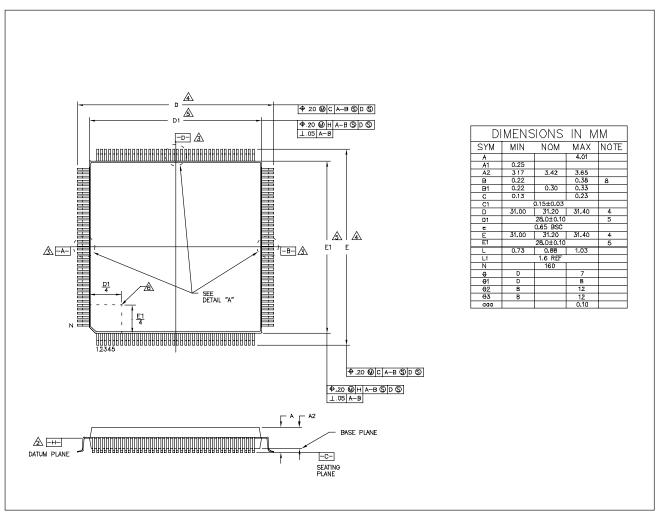

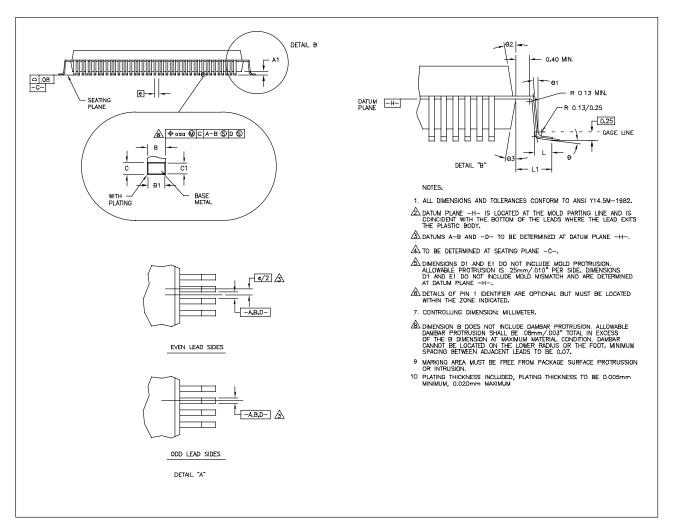

- Chapter 6, Specifications, describes the specifications for the L64780 electrical and mechanical characteristics.

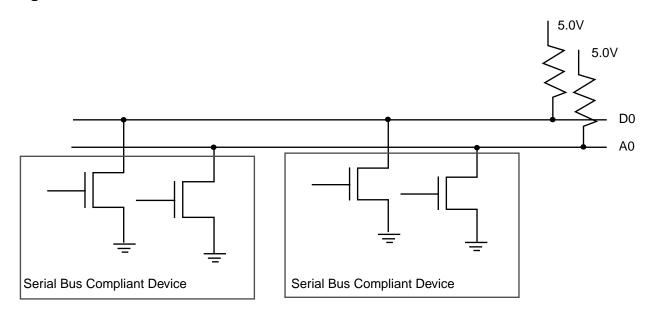

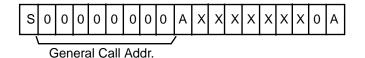

- Appendix A, Programming the L64780 Using The Serial Bus Interface, describes how to program the L64780 using the Serial Bus.

#### **Related Publications**

ETSI Specification ETS 300 744. 1997. "Digital broadcasting systems for television, sound and data services; Framing structure, channel coding and modulation for digital terrestrial television."

Stott, J.H., 1996. *The DVB Terrestrial (DVB-T) Specification and its Implementation In a Practical Modem.* International Broadcasting Convention 1996.

#### **Conventions Used in This Manual**

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x" (for example, 0x32CF). Binary numbers are indicated by the prefix "0b" (for example, 0b0011.0010.1100.1111).

### **Contents**

| Chapter 1 | Introduction |           |                                   |                                                                              |  |

|-----------|--------------|-----------|-----------------------------------|------------------------------------------------------------------------------|--|

| •         | 1.1 Overview |           |                                   | 1-1                                                                          |  |

|           | 1.2          |           |                                   |                                                                              |  |

|           | 1.3          | RF Tur    | ner Block Functions               | 1-4                                                                          |  |

|           | 1.4          | Modes     | of Operation                      | 1-6                                                                          |  |

|           | 1.5          | Feature   | es                                | 1-6                                                                          |  |

|           | 1.6          | Typical   | Performance                       | 1-7                                                                          |  |

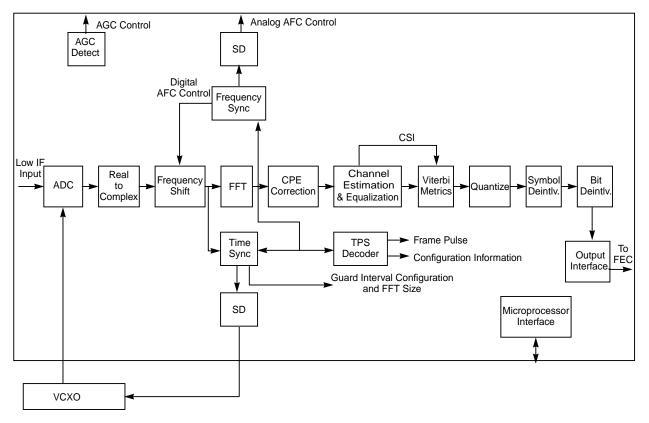

| Chapter 2 | Arch         | nitectura | l Overview                        |                                                                              |  |

|           | 2.1          | Demod     | 2-2                               |                                                                              |  |

|           | 2.2          | Analog    | -to-Digital Converter (ADC)       | 2-4                                                                          |  |

|           | 2.3          | Automa    | atic Gain Control (AGC)           | 2-4                                                                          |  |

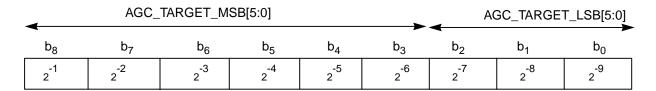

|           |              | 2.3.1     | AGC Target RMS Value              | 2-4                                                                          |  |

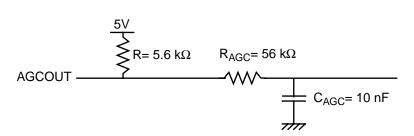

|           |              | 2.3.2     | AGC External Loop Filter          | 2-5                                                                          |  |

|           |              | 2.3.3     | AGC Loop Gain Ks                  | 2-6                                                                          |  |

|           | 2.4          | Real-to   | 2-7                               |                                                                              |  |

|           | 2.5          | Fast Fo   | 2-8                               |                                                                              |  |

|           | 2.6          | Time S    | Synchronization                   | 2-8                                                                          |  |

|           |              | 2.6.1     | Timing Loop Gain                  | 2-8                                                                          |  |

|           |              | 2.6.2     | TIM_CLK_INIT Register Definition  | 2-9                                                                          |  |

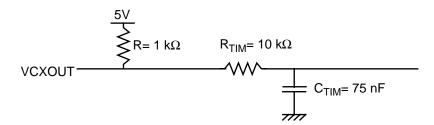

|           |              | 2.6.3     | TIM External Loop Filter          | 2-9                                                                          |  |

|           | 2.7          | Automa    | atic Frequency Control (AFC)      | 2-4<br>2-4<br>2-5<br>2-6<br>2-7<br>2-8<br>2-8<br>2-9<br>2-10<br>2-10<br>2-10 |  |

|           |              | 2.7.1     | Analog Frequency Synchronization  | 2-10                                                                         |  |

|           |              | 2.7.2     | Digital Frequency Synchronization | 2-10                                                                         |  |

|           |              | 2.7.3     | AFC Loop Gain                     | 2-11                                                                         |  |

|           |              | 2.7.4     | AFC_INIT_FREQ Register Definition | 2-12                                                                         |  |

|           |              | 2.7.5     | AFC External Loop Filter          | 2-12                                                                         |  |

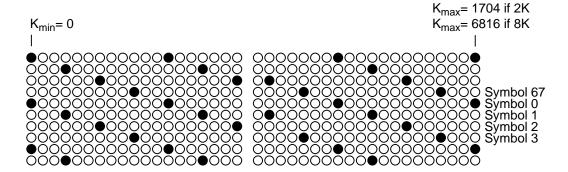

|           | 2.8          | TPS D     | ecoding and Frame Synchronization | 2-13                                                                         |  |

|           | 2.9          | Mode      | Control Logic                     | 2-14                                                                         |  |

Contents

|           | 2.10   | Channel Estimation and Equalization                             |                                            | 2-15 |

|-----------|--------|-----------------------------------------------------------------|--------------------------------------------|------|

|           | 2.11   | Viterbi Metric Assignment and Quantization Symbol Deinterleaver |                                            |      |

|           | 2.12   |                                                                 |                                            |      |

|           | 2.13   | Bit Dei                                                         | Bit Deinterleaver                          |      |

| Chapter 3 | Interf | faces                                                           |                                            |      |

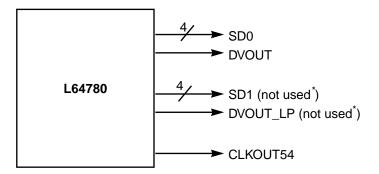

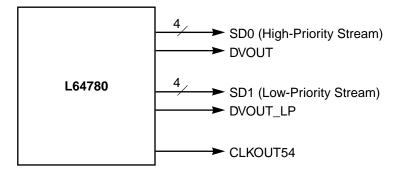

|           | 3.1    | Output                                                          | Interface                                  | 3-1  |

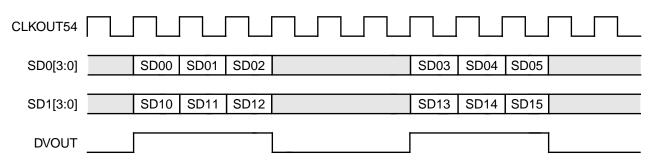

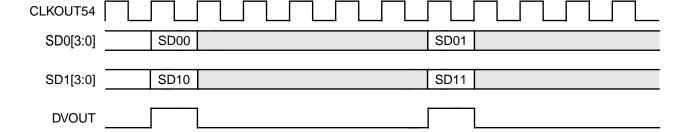

|           |        | 3.1.1                                                           | Output Format in Nonhierarchical Mode      | 3-1  |

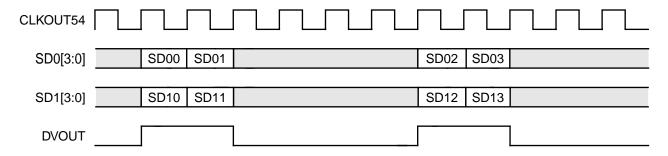

|           |        | 3.1.2                                                           | Output Format in Hierarchical Mode         | 3-5  |

|           | 3.2    | MUXIN                                                           | I Interface                                | 3-8  |

|           |        | 3.2.1                                                           | Access to Timing and DDFS Blocks           | 3-10 |

|           |        | 3.2.2                                                           | Access to the AFC Block                    | 3-10 |

|           |        | 3.2.3                                                           | Access to the FFT Block                    | 3-11 |

|           |        | 3.2.4                                                           | Access to the CSI Block                    | 3-11 |

|           |        | 3.2.5                                                           | Access to the SDI Block                    | 3-12 |

|           | 3.3    | MUXO                                                            | UT Interface                               | 3-13 |

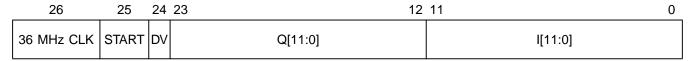

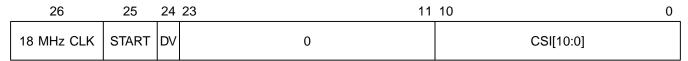

|           |        | 3.3.1                                                           | DDFS Output                                | 3-14 |

|           |        | 3.3.2                                                           | FFT Output                                 | 3-14 |

|           |        | 3.3.3                                                           | AFC Output                                 | 3-14 |

|           |        | 3.3.4                                                           | Channel Equalizer (CE) Output              | 3-15 |

|           |        | 3.3.5                                                           | CSI Output                                 | 3-15 |

|           |        | 3.3.6                                                           | ADC Output                                 | 3-16 |

|           | 3.4    | Microp                                                          | rocessor Interface                         | 3-16 |

| Chapter 4 | Regis  | ster Des                                                        | scriptions                                 |      |

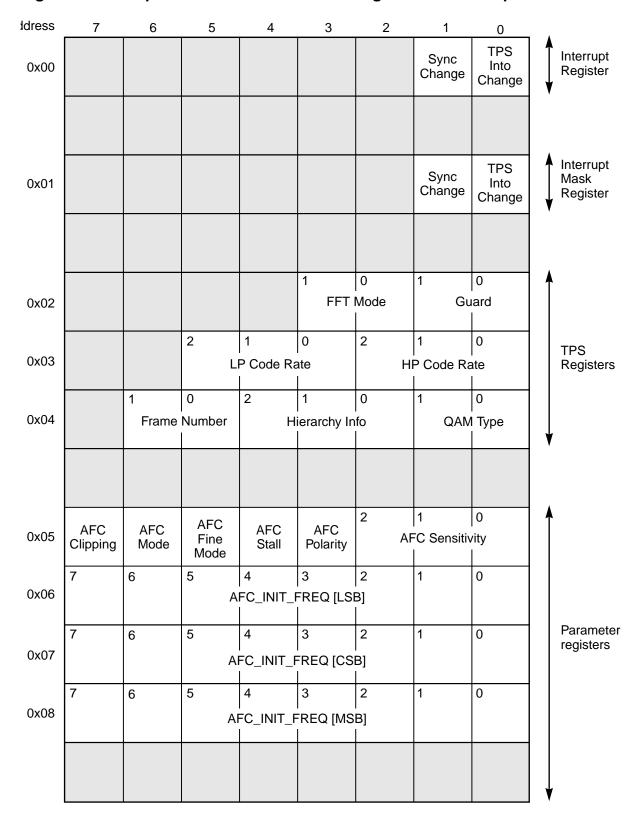

|           | 4.1    | Memory Map                                                      |                                            |      |

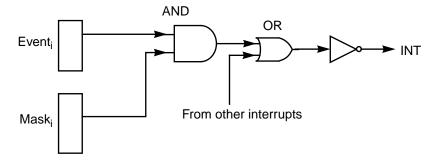

|           | 4.2    | Interrupt Registers                                             |                                            |      |

|           |        | 4.2.1                                                           | Address Line 0x00                          | 4-7  |

|           |        | 4.2.2                                                           | Interrupt Mask Register, Address Line 0x01 | 4-9  |

|           | 4.3    | TPS R                                                           | egisters                                   | 4-11 |

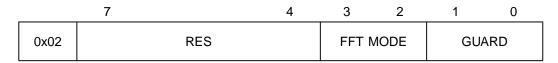

|           |        | 4.3.1                                                           | Address Line 0x02                          | 4-11 |

|           |        | 4.3.2                                                           | Address Line 0x03                          | 4-12 |

|           |        | 4.3.3                                                           | Address Line 0x04                          | 4-14 |

|           | 4.4    | Paramo                                                          | eter Registers                             | 4-16 |

|           |        | 4.4.1                                                           | Address Line 0x05                          | 4-16 |

|           |        | 4.4.2                                                           | Address Lines 0x06, 0x07, 0x08             | 4-19 |

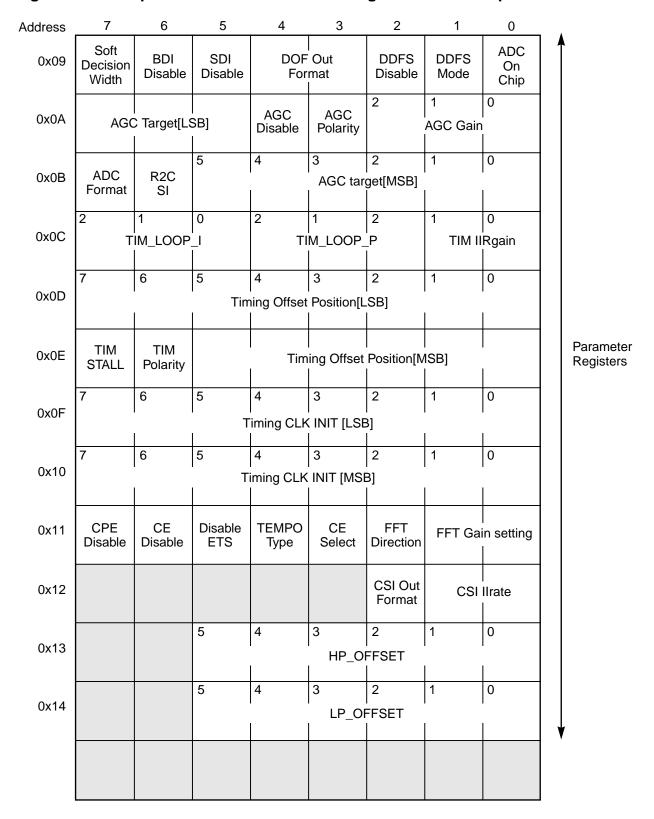

|           |        | 4.4.3                                                           |                                            | 4-20 |

vi Contents

|           |       | 4.4.4 Address Line 0x0A                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          | 4-23 |

|-----------|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------|------|

|           |       | 4.4.5 Address Line 0x0B                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          | 4-24 |

|           |       | 4.4.6 Address Line 0x0C                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          | 4-25 |

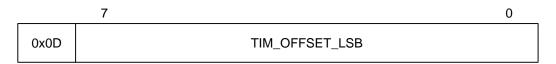

|           |       | 4.4.7 Address Line 0x0D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          | 4-27 |

|           |       | 4.4.8 Address Line 0x0E                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          | 4-27 |

|           |       | 4.4.9 Address Lines 0x0F                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | , 0x10                   | 4-28 |

|           |       | 4.4.10 Address Line 0x11                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          | 4-29 |

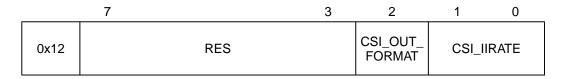

|           |       | 4.4.11 Address Line 0x12                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          | 4-30 |

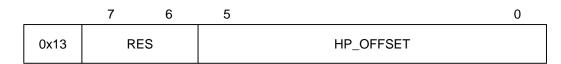

|           |       | 4.4.12 Address Line 0x13                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          | 4-31 |

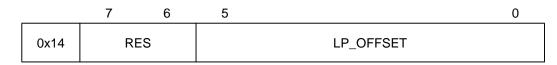

|           |       | 4.4.13 Address Line 0x14                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          | 4-31 |

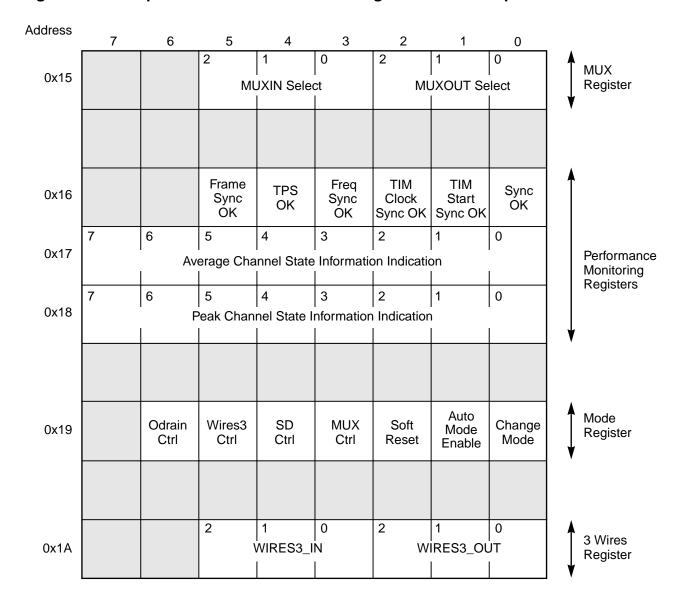

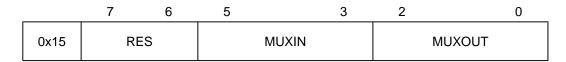

|           | 4.5   | Mux Register Address Line 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | )x15                     | 4-32 |

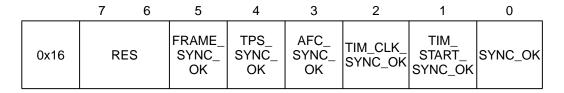

|           | 4.6   | Performance Monitoring Reg                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | isters Address Line 0x16 | 4-34 |

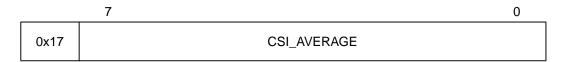

|           |       | 4.6.1 Address Line 0x17                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          | 4-35 |

|           |       | 4.6.2 Address Line 0x18                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                          | 4-35 |

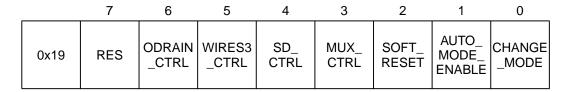

|           | 4.7   | Mode Register Address Line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 0x19                     | 4-36 |

|           | 4.8   | 3-Wires Register Address Lir                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ne 0x1A                  | 4-38 |

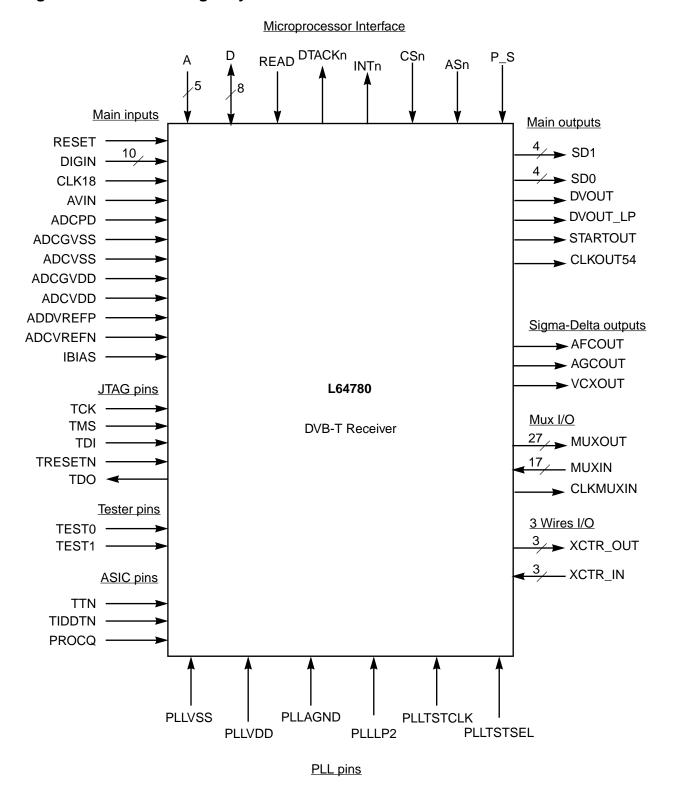

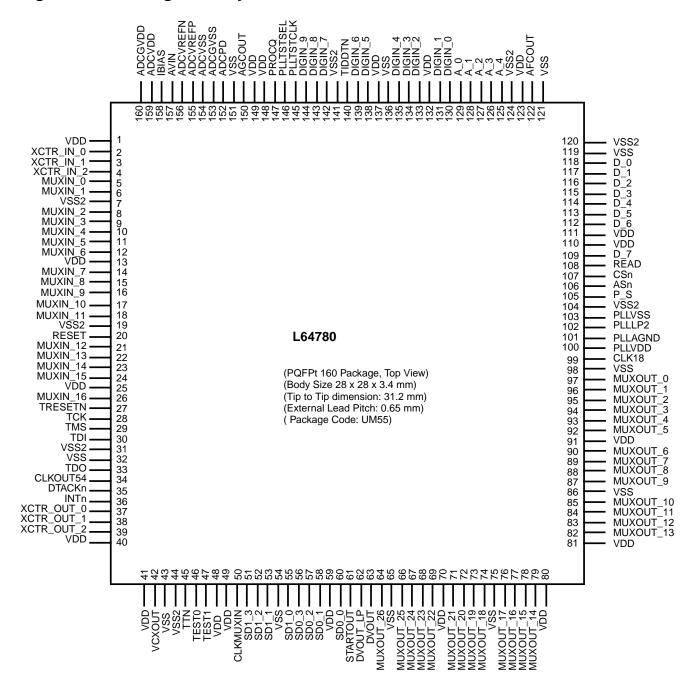

| Chapter 5 | Signa | Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          |      |

| •         | 5.1   | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          | 5-1  |

|           | 5.2   | Microprocessor Interface                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          | 5-3  |

|           | 5.3   | Main Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          | 5-4  |

|           | 5.4   | Sigma-Delta Outputs                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                          | 5-6  |

|           | 5.5   | MUX Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          | 5-6  |

|           | 5.6   | 3-Wires Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                          | 5-7  |

|           | 5.7   | JTAG Signals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                          | 5-7  |

|           | 5.8   | Test Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | 5-8  |

|           | 5.9   | ASIC Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | 5-8  |

|           | 5.10  | PLL Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          | 5-8  |

|           | 5.11  | Tester Pins                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                          | 5-9  |

| Chapter 6 | Spec  | ications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                          |      |

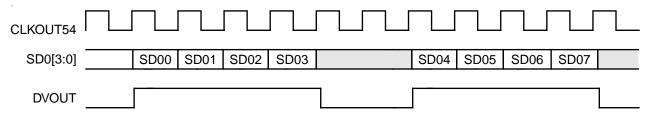

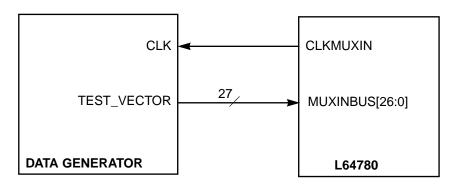

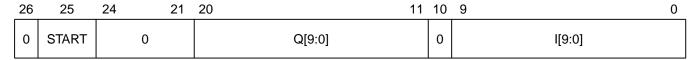

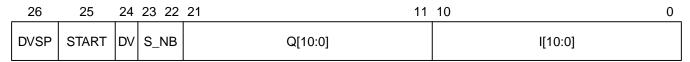

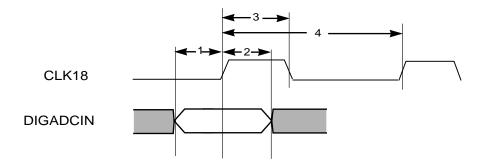

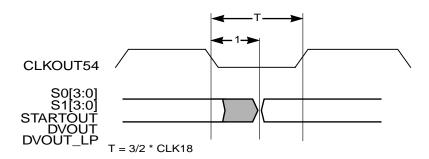

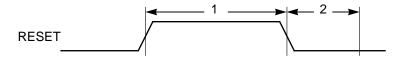

| •         | 6.1   | Electrical Specifications                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                          | 6-1  |