# L64704 Satellite Decoder

# **Technical Manual**

May 1997

Order Number I14010.A

Document DB14-000026-01, Second Edition (May 1997) This document describes Revision A of LSI Logic Corporation's L64704 Satellite Decoder and will remain the official reference source for all revisions of this product until rescinded by an update.

To receive product literature, call us at 1.800.574.4286 (U.S. and Canada); +32.11.300.531 (Europe); 408.433.7700 (outside U.S., Canada, and Europe) and ask for Department JDS; or visit us at http://www.lsilogic.com.

LSI Logic Corporation reserves the right to make changes to any products herein at any time without notice. LSI Logic does not assume any responsibility or liability arising out of the application or use of any product described herein, except as expressly agreed to in writing by LSI Logic; nor does the purchase or use of a product from LSI Logic convey a license under any patent rights, copyrights, trademark rights, or any other of the intellectual property rights of LSI Logic or third parties.

Copyright © 1995, 1996, 1997 by LSI Logic Corporation. All rights reserved.

#### TRADEMARK ACKNOWLEDGMENT

LSI Logic logo design is a registered trademark of LSI Logic Corporation. All other brand and product names may be trademarks of their respective companies.

May 1997

### Contents

| Chapter 1 | Introduction              |                                                    |      |  |  |

|-----------|---------------------------|----------------------------------------------------|------|--|--|

|           | 1.1                       | General Description                                | 1-1  |  |  |

|           | 1.2                       | Typical Application                                | 1-3  |  |  |

|           | 1.3                       | Features Summary                                   | 1-5  |  |  |

| Chapter 2 | L64704 Signal Definitions |                                                    |      |  |  |

|           | 2.1                       | Channel Interface                                  | 2-3  |  |  |

|           | 2.2                       | Channel Clock Recovery                             | 2-3  |  |  |

|           | 2.3                       | Channel Data Output Interface                      | 2-4  |  |  |

|           | 2.4                       | Phase-Locked Loop Interface                        | 2-5  |  |  |

|           | 2.5                       | Carrier Synchronizer Loop Controls                 | 2-6  |  |  |

|           | 2.6                       | Microcontroller Interface                          | 2-7  |  |  |

|           | 2.7                       | Control Signals                                    | 2-9  |  |  |

| Chapter 3 | L64704 Registers          |                                                    |      |  |  |

|           | 3.1                       | L64704 Register Overview                           | 3-2  |  |  |

|           |                           | 3.1.1 Parallel Host Mode Register Operations       | 3-7  |  |  |

|           |                           | 3.1.2 Programming Using the Serial Interface       | 3-9  |  |  |

|           | 3.2                       | Reset and How It Affects Registers                 | 3-9  |  |  |

|           | 3.3                       | Group 0, 1 Address Pointer Register                | 3-10 |  |  |

|           | 3.4                       | Group 2 Registers                                  | 3-11 |  |  |

|           |                           | 3.4.1 System Mode Register (SMR)                   | 3-11 |  |  |

|           |                           | 3.4.2 System Status Register (STS)                 | 3-16 |  |  |

|           | 3.5                       | Group 3 Registers                                  | 3-20 |  |  |

|           |                           | 3.5.1 Group 3, APR 0, 1 RS Corrected Error Count   | 3-21 |  |  |

|           |                           | 3.5.2 Group 3, APR 2, 3 RS Uncorrected Error Count | 3-21 |  |  |

|           |                           | 3.5.3 Group 3, APR 4, 5 Viterbi Bit Error Count    | 3-22 |  |  |

|           |                           | 3.5.4 Group 3, APR 6 Control Input and SNR         | 3-22 |  |  |

|           |                           | 3.5.5 Group 3, APR 6, 7 Measured VCO Frequency     | 3-23 |  |  |

Contents

|     | 3.5.6   | Group 3, APR 8 AGC Loop Voltage Meter                                       | 3-23   |

|-----|---------|-----------------------------------------------------------------------------|--------|

|     | 3.5.7   | Group 3, APR 9 Carrier and FEC Synchronization 3<br>3-23                    | Status |

|     | 3.5.8   | Group 3, APR 10 RI Readback                                                 | 3-25   |

|     | 3.5.9   | Group 3, APR 11 RQ Readback                                                 | 3-26   |

| 3.6 | Group 4 | Registers                                                                   | 3-26   |

|     | 3.6.1   | Group 4, APR 0 PLL Parameter N                                              | 3-28   |

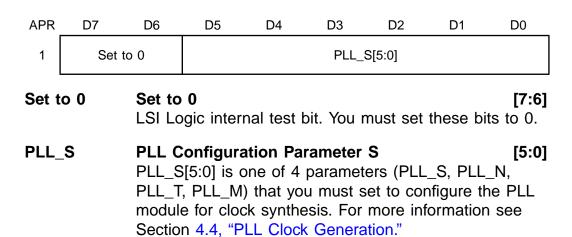

|     | 3.6.2   | Group 4, APR 1 PLL Parameter S                                              | 3-28   |

|     | 3.6.3   | Group 4, APR 2 PLL Parameter T, Demodulator and Symbol Select               | 3-29   |

|     | 3.6.4   | Group 4, APR 3 PLL Parameter M, Transport and Viterbi Code Rate Select      | 3-30   |

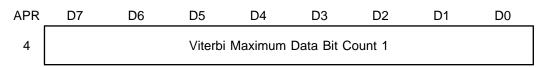

|     | 3.6.5   | Group 4, APR 4 Viterbi Max Data Bit Count 1                                 | 3-31   |

|     | 3.6.6   | Group 4, APR 5, 6, 7 Viterbi Max Data Bit Count 2                           | 3-31   |

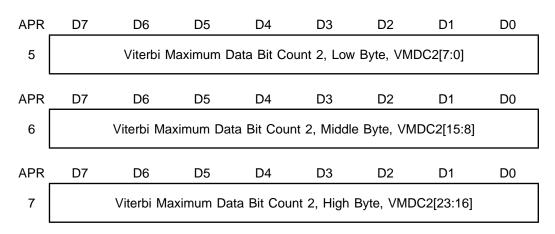

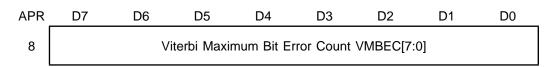

|     | 3.6.7   | Group 4, APR 8 Viterbi Maximum Bit Error Count                              | 3-32   |

|     | 3.6.8   | Group 4, APR 9 Synchronization Word                                         | 3-32   |

|     | 3.6.9   | Group 4, APR 10 BER Monitor and Mismatching<br>Bits in Sync 2 Tracking Mode | 3-33   |

|     | 3.6.10  | Group 4, APR 11 Synchronization States and                                  |        |

|     |         | BCLKOUT Format                                                              | 3-34   |

|     | 3.6.11  | Group 4, APR 12 Output Control                                              | 3-36   |

|     | 3.6.12  | Group 4, APR 13 PLL Reset                                                   | 3-37   |

|     | 3.6.13  | Group 4, APR 14 Clock Loop Control 1                                        | 3-37   |

|     | 3.6.14  | Group 4, APR 15 Clock Loop Control 2                                        | 3-39   |

|     | 3.6.15  | Group 4, APR 16, 17 Nominal Frequency of                                    |        |

|     |         | Clock Input                                                                 | 3-40   |

|     | 3.6.16  | Group 4, APR 18 Clock Ratio                                                 | 3-40   |

|     | 3.6.17  | Group 4, APR 19 Power Reference Level                                       | 3-41   |

|     | 3.6.18  | Group 4, APR 20 Power Estimation Bandwidth and I/Q DC Offset                | 3-41   |

|     | 3.6.19  | Group 4, APR 21 Scale Factor for DEMI and                                   |        |

|     |         | DEMQ Outputs                                                                | 3-42   |

|     | 3.6.20  | Group 4, APR 22 SNR Estimator Threshold                                     | 3-42   |

|     | 3.6.21  | Group 4, APR 23 Carrier Loop DC Offset                                      |        |

|     |         | Compensation Value                                                          | 3-42   |

|     | 3.6.22  | Group 4, APR 24 Carrier Frequency Reference<br>Period                       | 3-42   |

|     | 3.6.23  | Group 4, APR 25, 26 Carrier Loop Filter Gain                                |        |

|     |         | (P and D Terms)                                                             | 3-43   |

Contents Rev. letter

iv

|           |      | 3.6.24           | Group 4, APR 27 Carrier Lock Detector Threshold                                                | 3-43 |

|-----------|------|------------------|------------------------------------------------------------------------------------------------|------|

|           |      | 3.6.25           | Group 4, APR 28 Carrier Synchronizer Sweep<br>Rate                                             | 3-44 |

|           |      | 3.6.26           | Group 4, APR 29, 30 Carrier Synchronizer Sweep<br>Upper Limit                                  | 3-44 |

|           |      | 3.6.27           | Group 4, APR 31, 32 Carrier Synchronizer Sweep Lower Limit                                     | 3-45 |

|           |      | 3.6.28           | Group 4, APR 33 Carrier Loop Configuration Register                                            | 3-45 |

|           |      | 3.6.29           | Group 4, APR 34 Set to 0                                                                       | 3-48 |

|           |      | 3.6.30<br>3.6.31 | Group 4, APR 35 Decoder Configuration Register<br>Group 4, APR 36 External Output Control Bits | 3-49 |

|           |      |                  | and Reset Register                                                                             | 3-50 |

| Chapter 4 | Char | nnel Inter       | faces and Data Control                                                                         |      |

|           | 4.1  | Data Co          | ontrol and Clocking Schemes                                                                    | 4-2  |

|           | 4.2  | Channe           | el Data Input Interface                                                                        | 4-4  |

|           | 4.3  | Channe           | el Data Output Interface                                                                       | 4-5  |

|           | 4.4  | PLL Clo          | ock Generation                                                                                 | 4-5  |

|           | 4.5  | Data Pa          | ath Output Configurations                                                                      | 4-12 |

|           |      | 4.5.1            | Descrambler Output                                                                             | 4-13 |

|           |      | 4.5.2            | Synchronization Stage 3 Output                                                                 | 4-15 |

|           |      | 4.5.3            | Reed-Solomon Decoder Output                                                                    | 4-15 |

|           |      | 4.5.4            | Deinterleaver Output                                                                           | 4-16 |

|           |      | 4.5.5            | Synchronization Stage 2 Output                                                                 | 4-17 |

|           |      | 4.5.6            | Viterbi Decoder Output                                                                         | 4-17 |

|           |      | 4.5.7            | Viterbi Depuncture/Synchronization Output                                                      | 4-18 |

|           |      | 4.5.8            | QPSK Demodulator Output                                                                        | 4-19 |

| Chapter 5 | Dem  | odulator         | Module Functional Description                                                                  |      |

|           | 5.1  | Overvie          | W                                                                                              | 5-1  |

|           | 5.2  | DC Offs          | set Compensation and Coupling to ADC Output                                                    | 5-3  |

|           | 5.3  | Decima           | tion Filters                                                                                   | 5-3  |

|           | 5.4  | Matche           | d Filter                                                                                       | 5-4  |

|           | 5.5  | Channe           | el Clock Recovery                                                                              | 5-4  |

|           |      | 5.5.1            | Input Decimation                                                                               | 5-5  |

|           |      | 5.5.2            | Clock Acquisition and Tracking Modes                                                           | 5-5  |

v

May 1997

|           |                                   | 5.5.3                | Output Symbol Clock                      | 5-8  |

|-----------|-----------------------------------|----------------------|------------------------------------------|------|

|           |                                   | 5.5.4                | Constraints on Data Rates                | 5-8  |

|           |                                   | 5.5.5                | Examples                                 | 5-9  |

|           | 5.6                               | Carrier              | Synchronizer                             | 5-10 |

|           |                                   | 5.6.1                | Carrier Acquisition                      | 5-12 |

|           |                                   | 5.6.2                | Carrier Phase Tracking                   | 5-17 |

|           | 5.7                               | Automa               | atic Gain Control (AGC)                  | 5-22 |

|           |                                   | 5.7.1                | ADC Range and Power Reference            | 5-22 |

|           |                                   | 5.7.2                | Power Control Loop                       | 5-23 |

|           |                                   | 5.7.3                | Power Level                              | 5-24 |

|           | 5.8                               | Output               | Control                                  | 5-24 |

|           | 5.9                               | Other                | Functions                                | 5-26 |

|           |                                   | 5.9.1                | Carrier Loop DC Offset Compensation      | 5-26 |

|           |                                   | 5.9.2                | External Controls                        | 5-27 |

|           |                                   | 5.9.3                | Hi-Z Mode on Functional Outputs          | 5-27 |

| Chapter 6 | Decoding Pipeline Synchronization |                      |                                          |      |

|           | 6.1                               | Synchr               | ronization Scheme                        | 6-1  |

|           | 6.2                               | Viterbi              | Decoder Synchronization                  | 6-2  |

|           | 6.3                               | Reed-S               | Solomon Deinterleaver Synchronization    | 6-5  |

|           | 6.4                               | Descra               | ambler Synchronization                   | 6-10 |

| Chapter 7 | The                               | FEC Decoder Pipeline |                                          |      |

|           | 7.1                               | Viterbi              | Decoder Module                           | 7-1  |

|           |                                   | 7.1.1                | Features                                 | 7-2  |

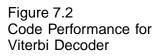

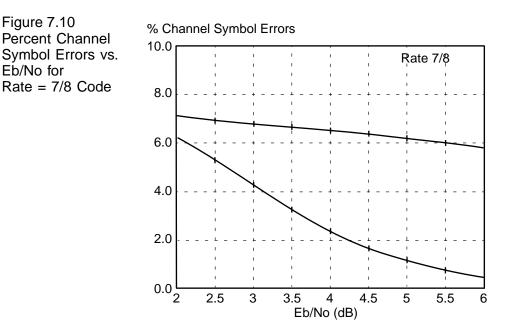

|           |                                   | 7.1.2                | Code Performance                         | 7-3  |

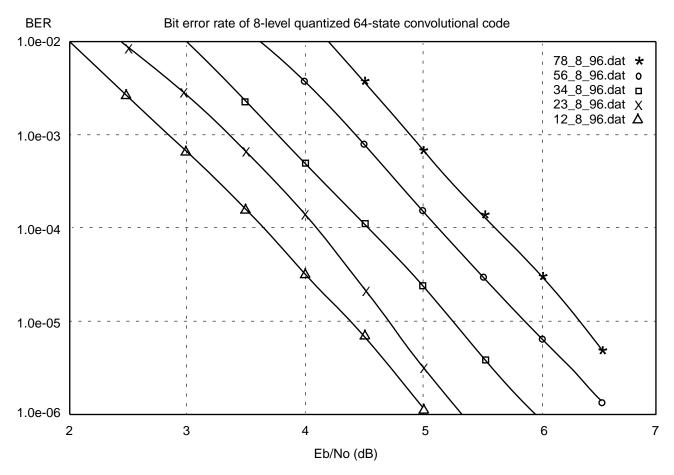

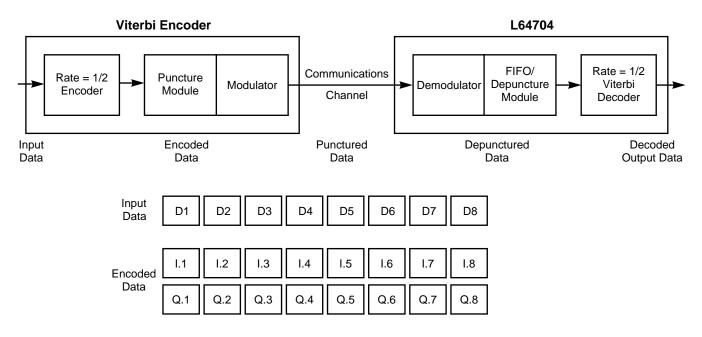

|           |                                   | 7.1.3                | Punctured Codes                          | 7-3  |

|           |                                   | 7.1.4                | Viterbi Bit Error Rate Monitor           | 7-6  |

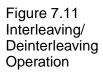

|           | 7.2                               | Deinte               | rleaver Module                           | 7-11 |

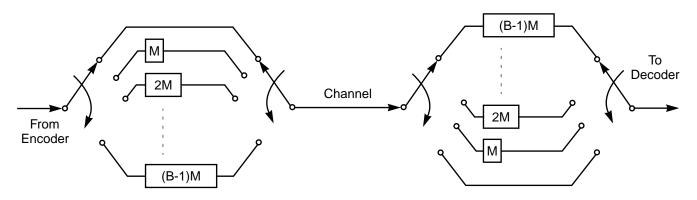

|           |                                   | 7.2.1                | Deinterleaver Block Diagram              | 7-12 |

|           |                                   | 7.2.2                | Deinterleaver Output                     | 7-13 |

|           | 7.3                               | Reed-S               | Solomon Decoder                          | 7-14 |

|           |                                   | 7.3.1                | Terms and Concepts                       | 7-14 |

|           |                                   | 7.3.2                | Features                                 | 7-17 |

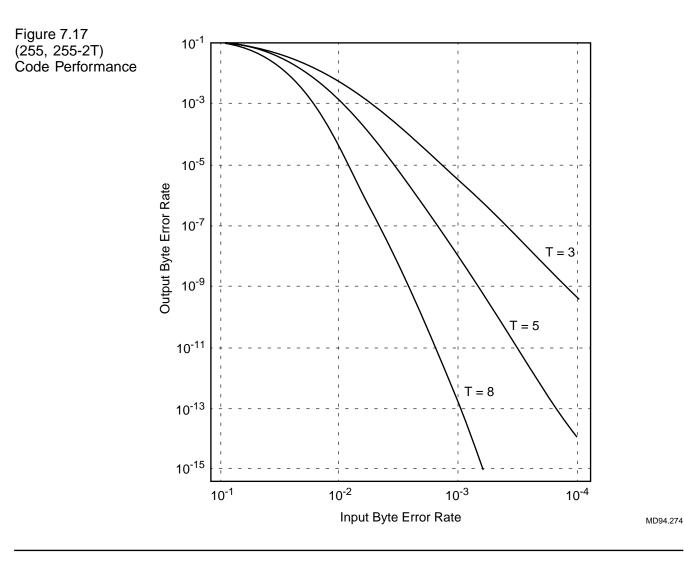

|           |                                   | 7.3.3                | Performance Analysis                     | 7-18 |

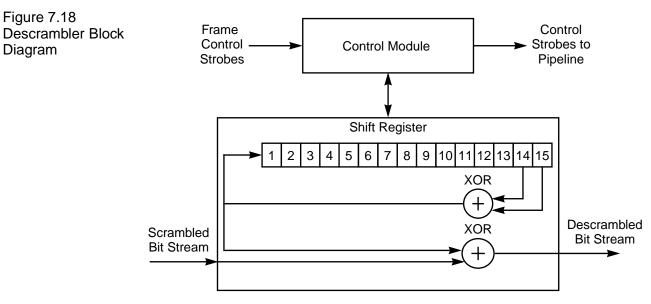

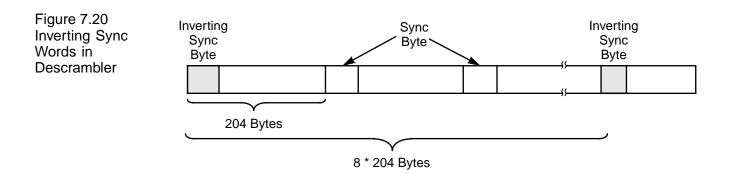

|           | 7.4                               | Descra               | ambler Module Architecture and Operation | 7-19 |

|           | 7.5                               | FEC N                | Iodule Software Reset                    | 7-21 |

vi

| Chapter 8  | L64704 Specifications |                                                      |                                                    |             |  |  |

|------------|-----------------------|------------------------------------------------------|----------------------------------------------------|-------------|--|--|

|            | 8.1                   | Electric                                             | al Requirements                                    | 8-1         |  |  |

|            | 8.2                   | AC Tim                                               | ling                                               | 8-5         |  |  |

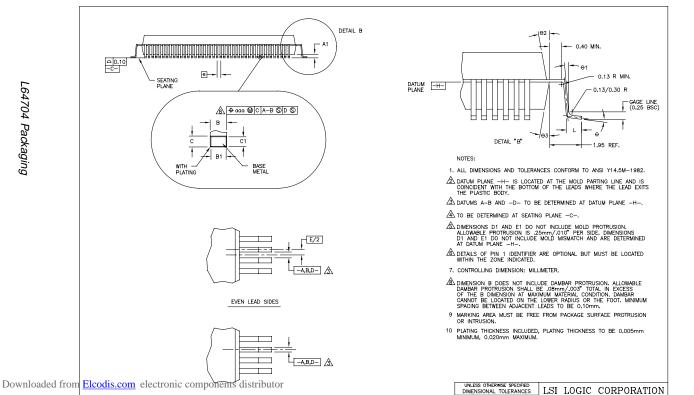

|            | 8.3                   | L64704                                               | Packaging                                          | 8-10        |  |  |

| Appendix A | Prog                  | Programming the L64704 Using the Serial Bus Protocol |                                                    |             |  |  |

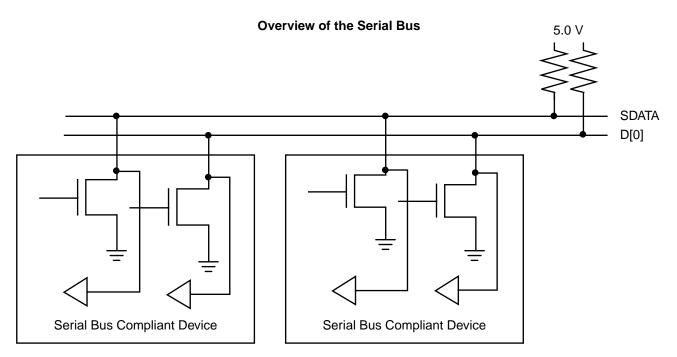

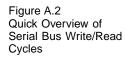

|            | A.1                   | Serial E                                             | Bus Protocol Overview                              | A-1         |  |  |

|            | A.2                   | Program                                              | mming the Slave Address Using the Serial           |             |  |  |

|            |                       | Bus Int                                              | erface                                             | A-4         |  |  |

|            | A.3                   | Write C                                              | Cycle Using the Serial Bus Interface               | A-4         |  |  |

|            | A.4                   | Read C                                               | Cycle Using the Serial Bus Interface               | A-6         |  |  |

| Appendix B | L647                  | '04 Appli                                            | cation Notes                                       |             |  |  |

|            | B.1                   | Control                                              | ling the L64704's BPSK/QPSK Demodulator Loops      | B-1         |  |  |

|            | B.2                   | L64704                                               | QPSK Demodulator Debugging Tips                    | B-4         |  |  |

|            |                       | B.2.1                                                | AGC Loop                                           | B-4         |  |  |

|            |                       | B.2.2                                                | Clock Loop                                         | <b>B-</b> 5 |  |  |

|            |                       | B.2.3                                                | Carrier Loop                                       | <b>B-6</b>  |  |  |

|            |                       | B.2.4                                                | QPSK Demodulator Debugging Summary                 | B-7         |  |  |

|            | B.3                   | QPSK                                                 | Demodulator Configuration Example                  | <b>B-</b> 8 |  |  |

|            |                       | B.3.1                                                | Programming the L64704 QPSK Demodulator Reg<br>B-9 | gisters     |  |  |

|            |                       | B.3.2                                                | RC Values for Clock Loop                           | B-16        |  |  |

|            |                       | B.3.3                                                | VCO Gains                                          | B-16        |  |  |

|            |                       | B.3.4                                                | Low Data Rates                                     | B-17        |  |  |

|            | B.4                   | Configu                                              | uring the L64704 FEC Decoder to the DVB            |             |  |  |

|            |                       | Specific                                             | -                                                  | B-18        |  |  |

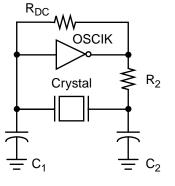

| Appendix C | Osci                  | llator Ce                                            | lls                                                |             |  |  |

|            | C.1                   | Introdu                                              | ction                                              | C-1         |  |  |

|            | C.2                   | Require                                              | ements For Oscillator Circuits                     | C-2         |  |  |

|            | C.3                   | 0 to 20                                              | MHz Crystal Oscillator                             | C-2         |  |  |

|            | C.4                   | Higher                                               | Frequency Oscillators                              | C-4         |  |  |

|            | C.5                   | Low Fr                                               | equency Oscillation (kHz Range)                    | C-5         |  |  |

#### **Customer Feedback**

Contents

| Figures | 1.1  | L64704 Block Diagram                                | 1-2  |

|---------|------|-----------------------------------------------------|------|

|         | 1.2  | Set-Top Decoder Box Block Diagram                   | 1-3  |

|         | 1.3  | Typical Receiver Block Diagram with L64704          | 1-4  |

|         | 1.4  | Concatenated Decoding Performance for L64704        | 1-6  |

|         | 2.1  | L64704 Logic Diagram                                | 2-2  |

|         | 3.1  | Register-File Structure                             | 3-6  |

|         | 3.2  | Issue a Hard Reset                                  | 3-7  |

|         | 3.3  | Initialize APR0 and APR1 to Zero                    | 3-7  |

|         | 3.4  | Write Locations 0 and 1 in Group 4                  | 3-8  |

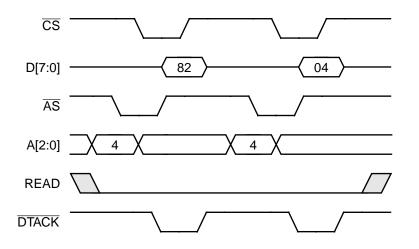

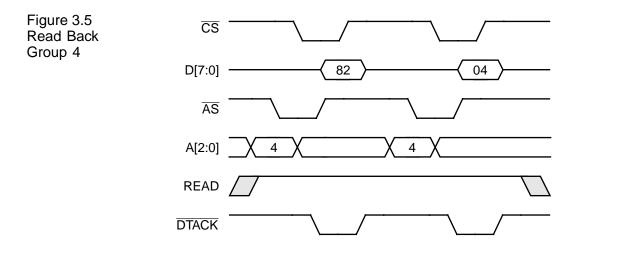

|         | 3.5  | Read Back Group 4                                   | 3-8  |

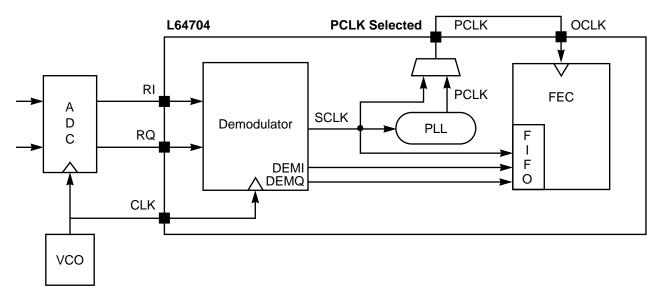

|         | 4.1  | L64704 Clocking: Internal PLL                       | 4-2  |

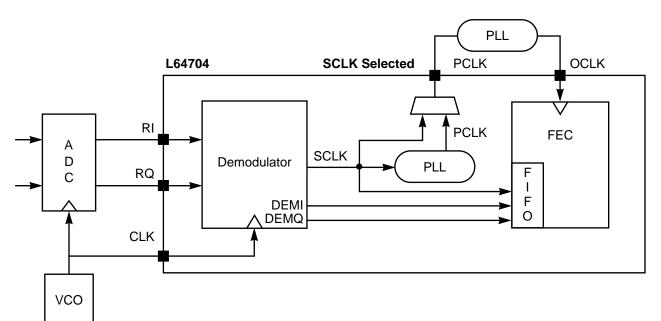

|         | 4.2  | L64704 Clocking: External PLL                       | 4-3  |

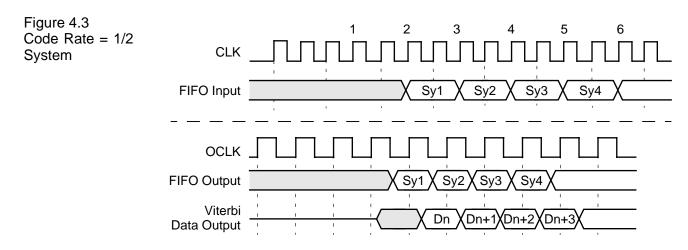

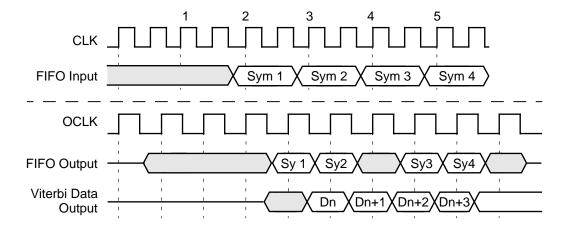

|         | 4.3  | Code Rate = 1/2 System                              | 4-3  |

|         | 4.4  | Code Rate = 3/4 System; Different OCLK and CLK      | 4-4  |

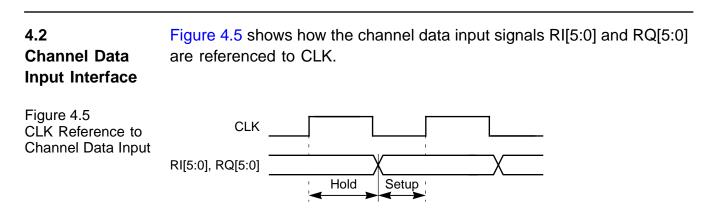

|         | 4.5  | CLK Reference to Channel Data Input                 | 4-4  |

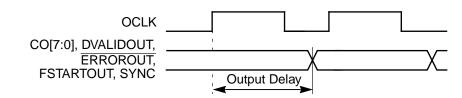

|         | 4.6  | OCLK Reference to Channel Data Output               | 4-5  |

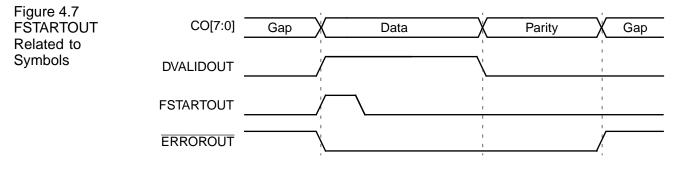

|         | 4.7  | FSTARTOUT Related to Symbols                        | 4-5  |

|         | 4.8  | PLL Clock Generation                                | 4-6  |

|         | 4.9  | PLL Clock Synthesis                                 | 4-7  |

|         | 4.10 | L64704 Functional Blocks in the Decoding Pipeline   | 4-13 |

|         | 4.11 | Descrambler Serial Output Waveforms                 | 4-14 |

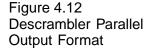

|         | 4.12 | Descrambler Parallel Output Format                  | 4-14 |

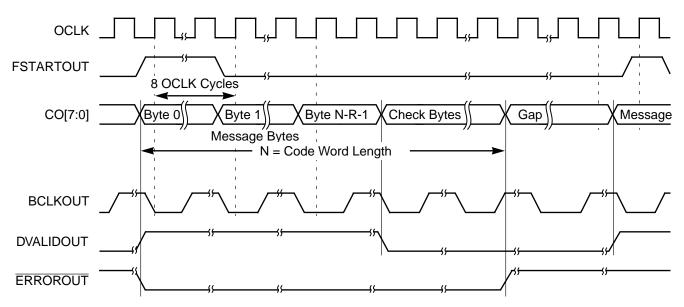

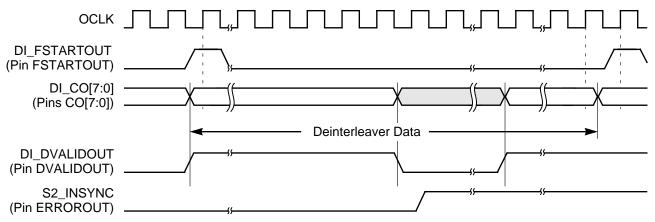

|         | 4.13 | Synchronization Stage 3 Output Waveforms            | 4-15 |

|         | 4.14 | Reed-Solomon Decoder Output Waveforms               | 4-16 |

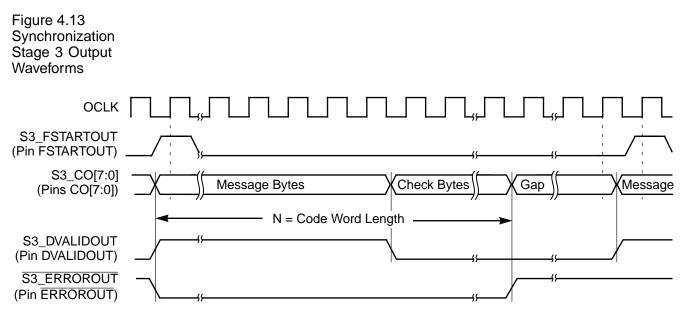

|         | 4.15 | Deinterleaver Output Waveforms                      | 4-16 |

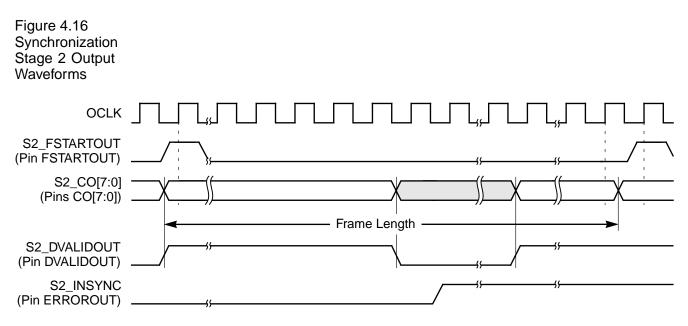

|         | 4.16 | Synchronization Stage 2 Output Waveforms            | 4-17 |

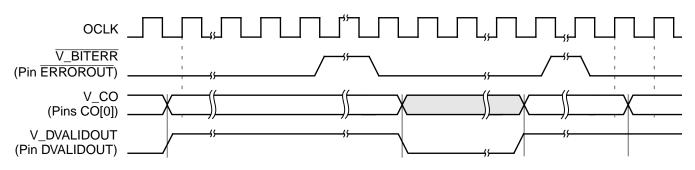

|         | 4.17 | Viterbi Decoder Output Waveforms                    | 4-18 |

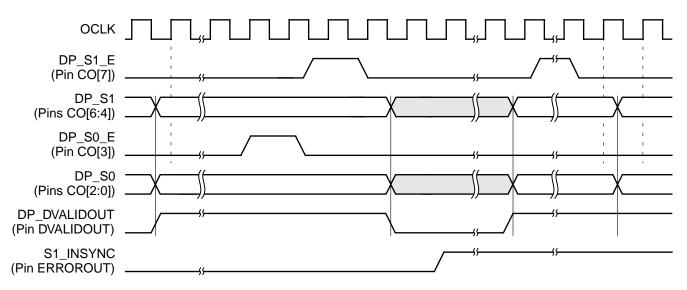

|         | 4.18 | Viterbi Depuncture/Synchronization Output Waveforms | 4-18 |

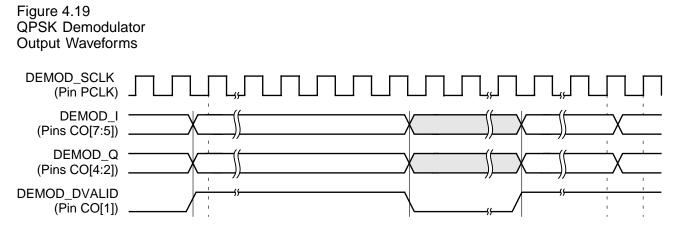

|         | 4.19 | QPSK Demodulator Output Waveforms                   | 4-19 |

|         | 5.1  | Demodulator Module and its Associated Circuitry     | 5-2  |

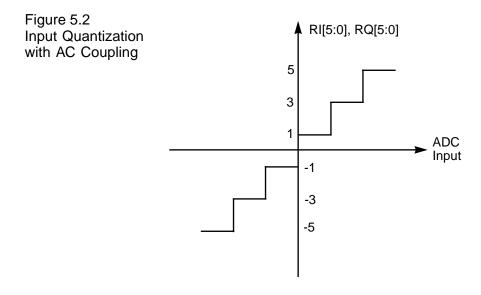

|         | 5.2  | Input Quantization with AC Coupling                 | 5-3  |

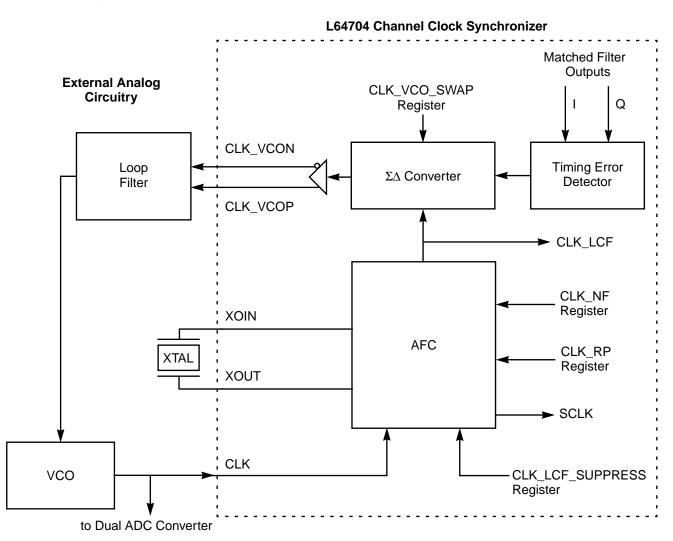

|         | 5.3  | Clock Recovery Loop                                 | 5-4  |

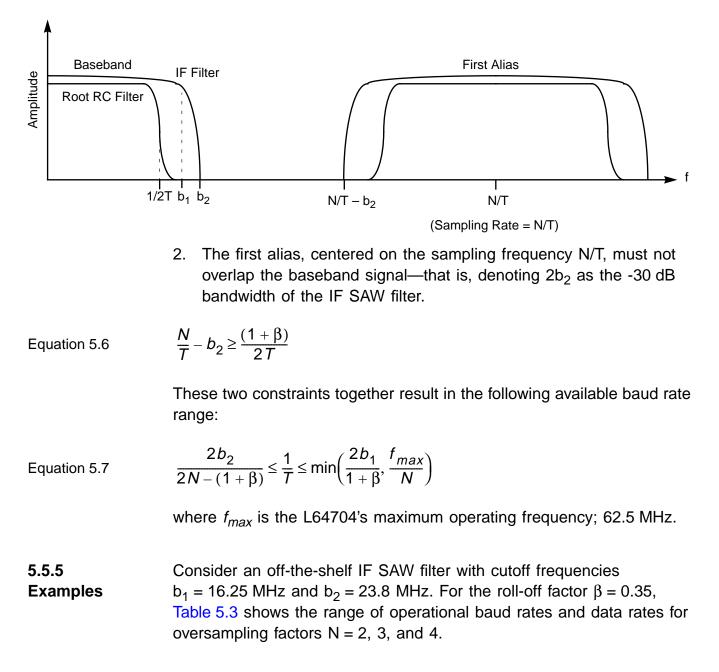

|         | 5.4  | Spectrum of Oversampled Signal                      | 5-9  |

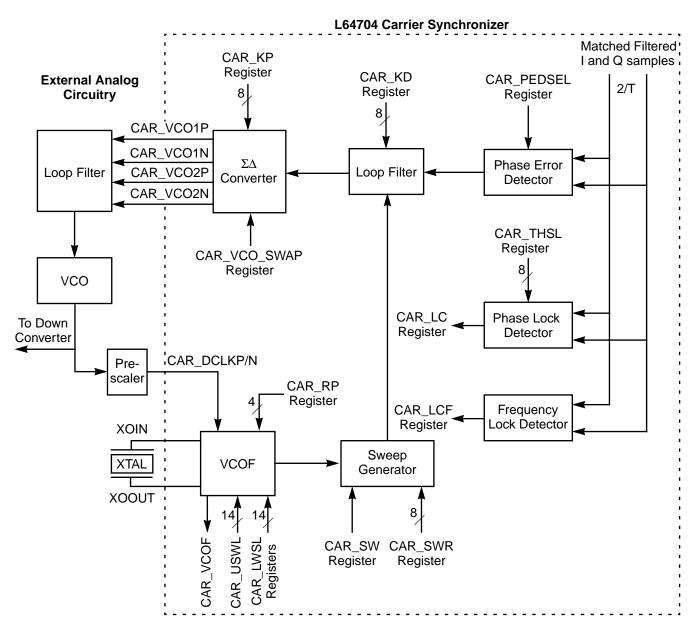

|         | 5.5  | Carrier Recovery Loop                               | 5-11 |

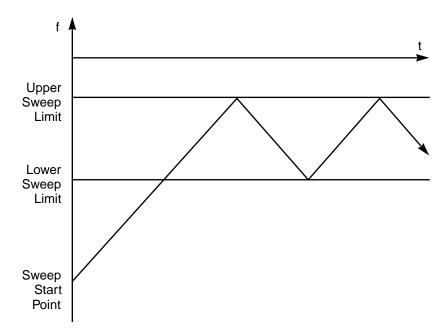

|         | 5.6  | Frequency Sweeping                                  | 5-13 |

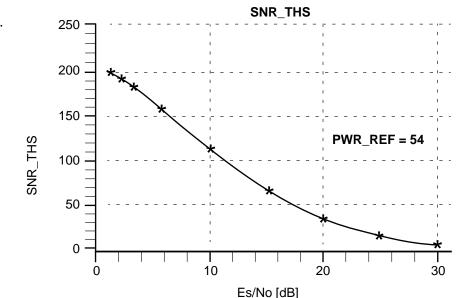

|         | 5.7  | SNR Threshold vs. ES/No                             | 5-17 |

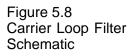

|         | 5.8  | Carrier Loop Filter Schematic                       | 5-18 |

viii

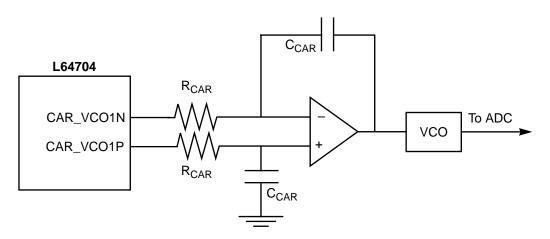

| 5.9  | PED Slope                                                      | 5-19 |

|------|----------------------------------------------------------------|------|

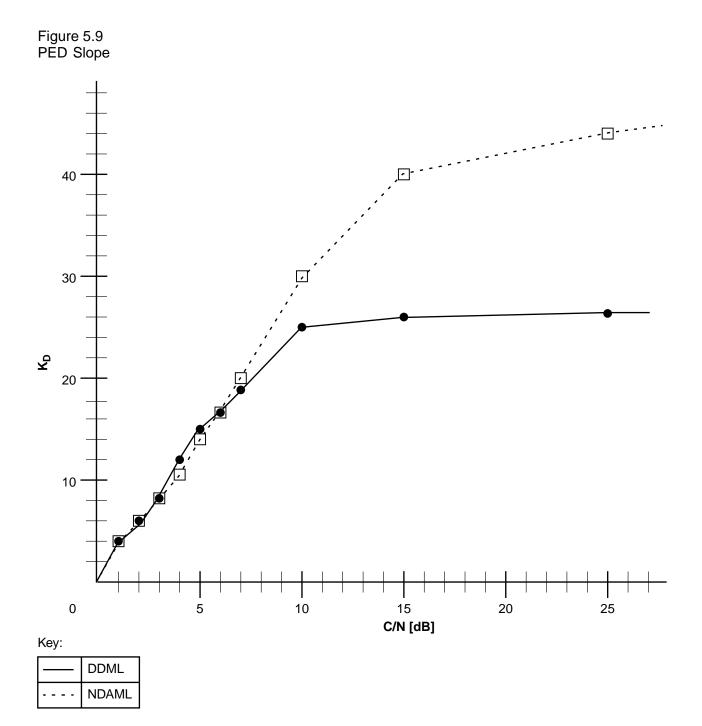

| 5.10 | Using CAR_PED Outputs                                          | 5-21 |

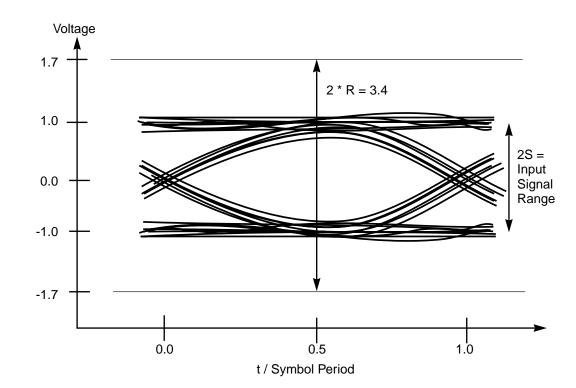

| 5.11 | Eye Pattern and ADC Range                                      | 5-22 |

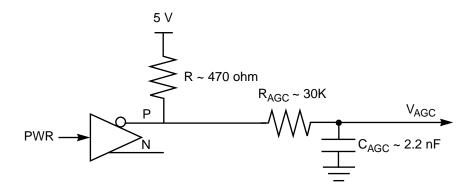

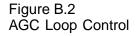

| 5.12 | AGC Loop Control                                               | 5-23 |

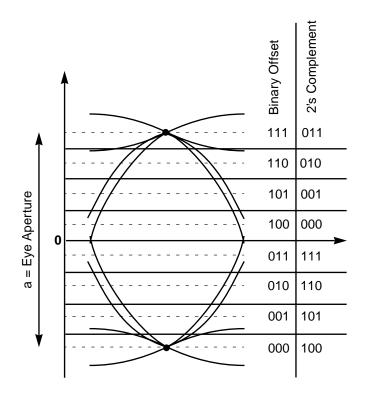

| 5.13 | Eye Pattern and Soft Decision Thresholds                       | 5-25 |

| 6.1  | Synchronization Module                                         | 6-2  |

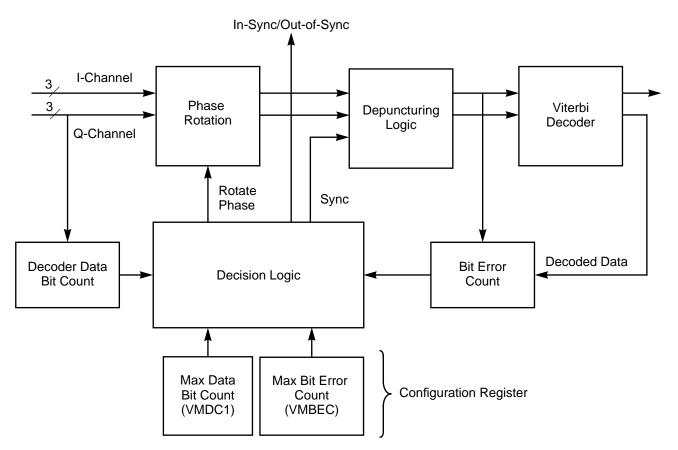

| 6.2  | Viterbi Decoder Synchronization                                | 6-3  |

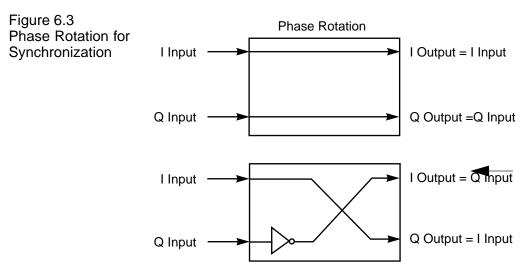

| 6.3  | Phase Rotation for Synchronization                             | 6-4  |

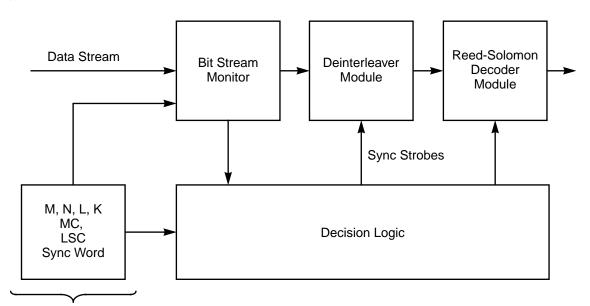

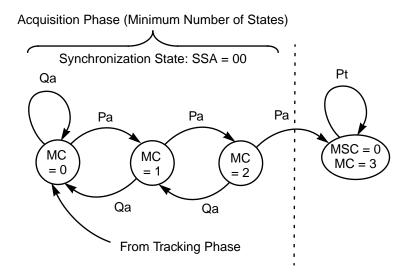

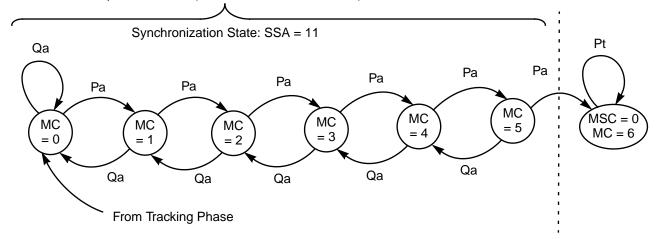

| 6.4  | Reed-Solomon, Deinterleaver Synchronization                    | 6-5  |

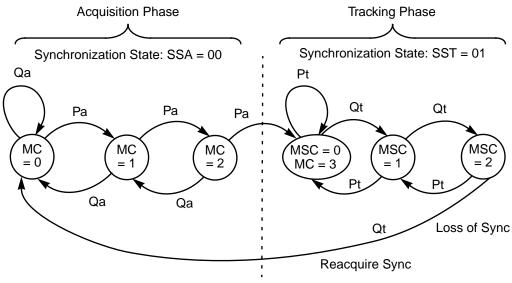

| 6.5  | Synchronization, Tracking, and Loss of Sync for 3              |      |

|      | Missed Sync Words                                              | 6-6  |

| 6.6  | Minimum and Maximum Number of States in the                    |      |

|      | Acquisition Phase                                              | 6-7  |

| 6.7  | Minimum and Maximum Number of States in the                    |      |

|      | Tracking Phase                                                 | 6-8  |

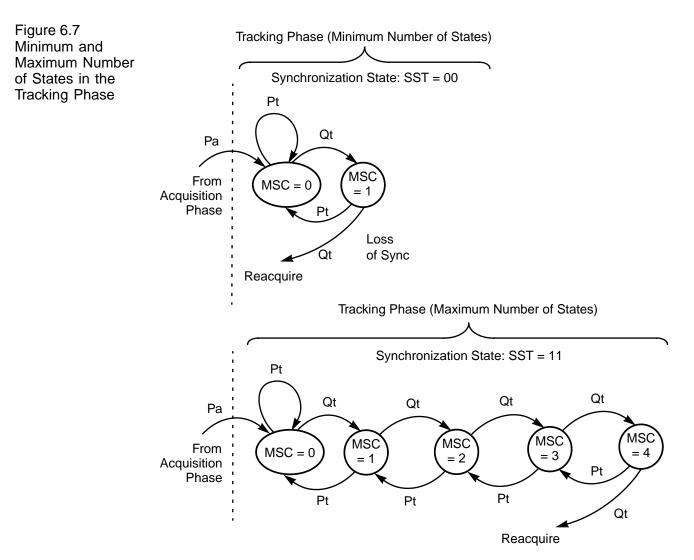

| 6.8  | MPEG-2 Transport Packet                                        | 6-8  |

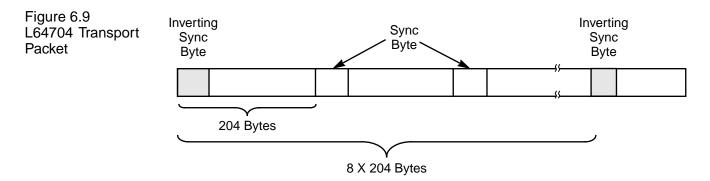

| 6.9  | L64704 Transport Packet                                        | 6-9  |

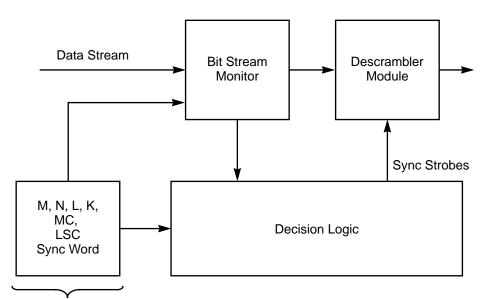

| 6.10 | Descrambler Synchronization                                    | 6-10 |

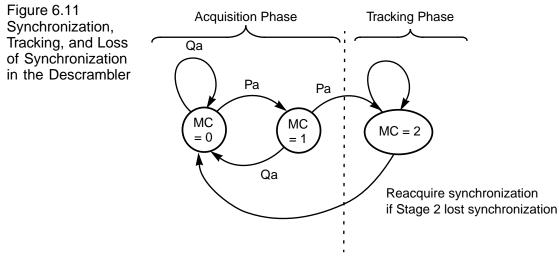

| 6.11 | Synchronization, Tracking, and Loss of Synchronization         |      |

|      | in the Descrambler                                             | 6-11 |

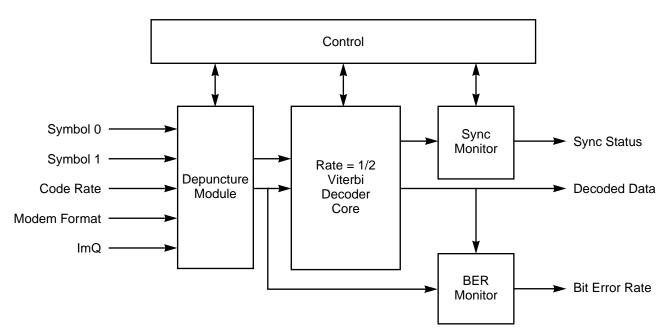

| 7.1  | Block Diagram of Viterbi Decoder Core                          | 7-2  |

| 7.2  | Code Performance for Viterbi Decoder                           | 7-3  |

| 7.3  | Puncturing and Depuncturing Block Diagram                      | 7-4  |

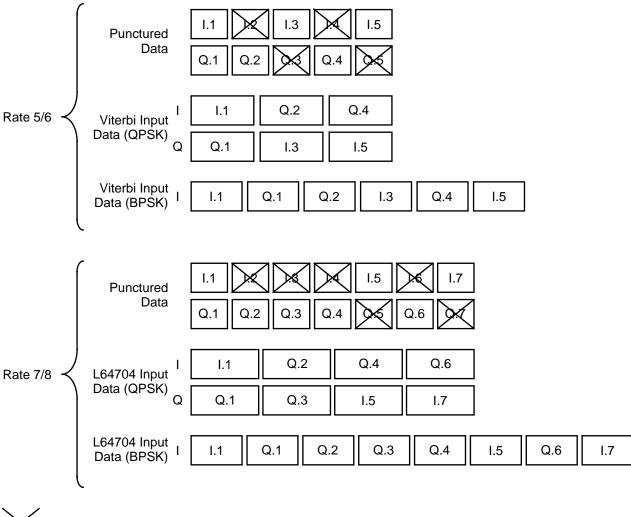

| 7.4  | Puncture Pattern for Different Code Rates                      | 7-5  |

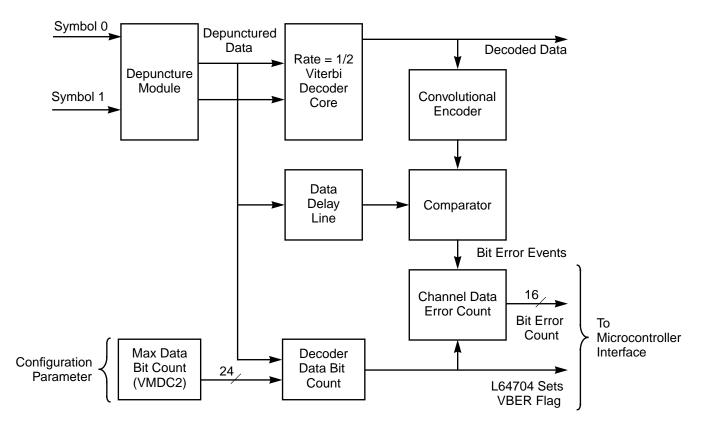

| 7.5  | Block Diagram of Viterbi Bit Error Detection Circuit           | 7-8  |

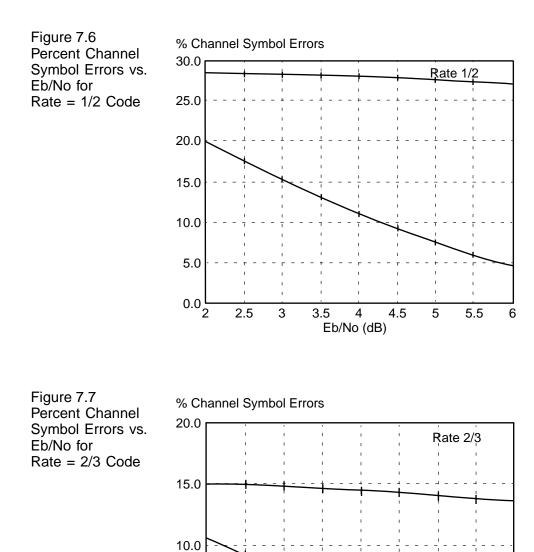

| 7.6  | Percent Channel Symbol Errors vs. Eb/No for                    |      |

|      | Rate = 1/2 Code                                                | 7-9  |

| 7.7  | Percent Channel Symbol Errors vs. Eb/No for<br>Rate = 2/3 Code | 7.0  |

| 70   |                                                                | 7-9  |

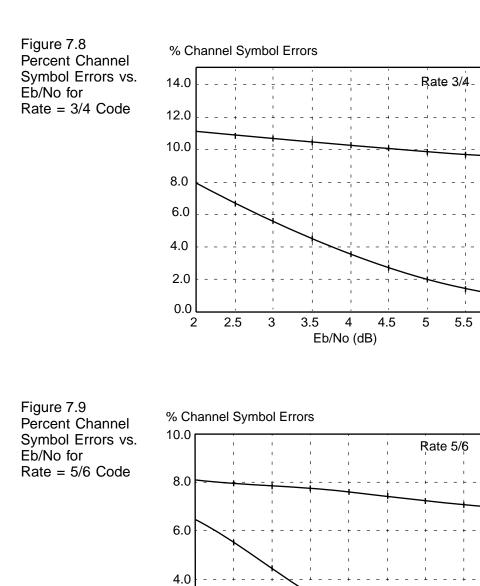

| 7.8  | Percent Channel Symbol Errors vs. Eb/No for<br>Rate = 3/4 Code | 7-10 |

| 7.9  | Percent Channel Symbol Errors vs. Eb/No for                    | 7-10 |

| 1.5  | Rate = $5/6$ Code                                              | 7-10 |

| 7.10 | Percent Channel Symbol Errors vs. Eb/No for                    | 1 10 |

|      | Rate = $7/8$ Code                                              | 7-11 |

| 7.11 | Interleaving/Deinterleaving Operation                          | 7-12 |

| 7.12 | Block Diagram of Deinterleaver Core                            | 7-13 |

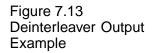

| 7.13 | Deinterleaver Output Example                                   | 7-13 |

| 7.14 | Code Word Structure                                       | 7-15 |

|------|-----------------------------------------------------------|------|

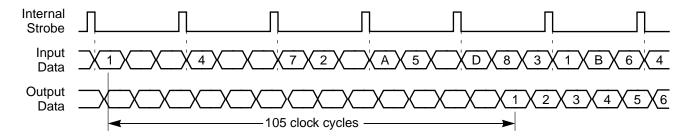

| 7.15 | Forward Error Correction Data Path                        | 7-15 |

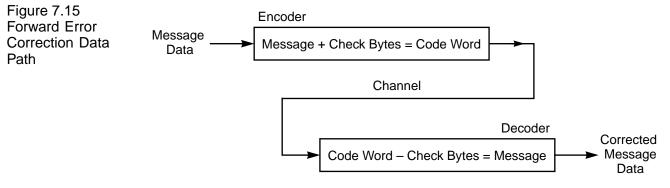

| 7.16 | 122-bit Burst Example                                     | 7-17 |

| 7.17 | (255, 255-2T) Code Performance                            | 7-19 |

| 7.18 | Descrambler Block Diagram                                 | 7-20 |

| 7.19 | 15-bit Shift Register                                     | 7-20 |

| 7.20 | Inverting Sync Words in Descrambler                       | 7-21 |

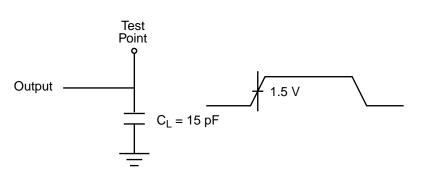

| 8.1  | AC Test Load and Waveform for Standard Outputs            | 8-5  |

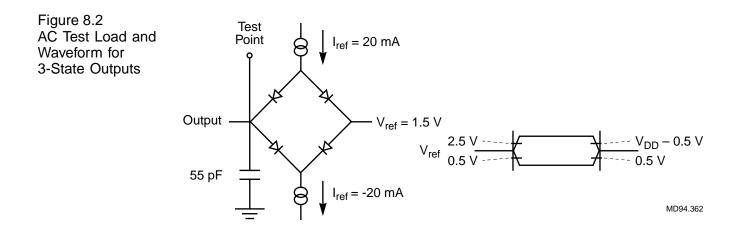

| 8.2  | AC Test Load and Waveform for 3-State Outputs             | 8-6  |

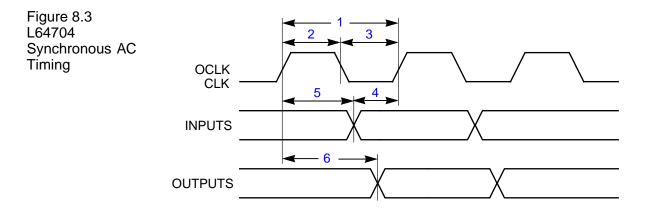

| 8.3  | L64704 Synchronous AC Timing                              | 8-6  |

| 8.4  | L64704 RESET Timing Diagram                               | 8-7  |

| 8.5  | L64704 Bus 3-State Delay Timing                           | 8-7  |

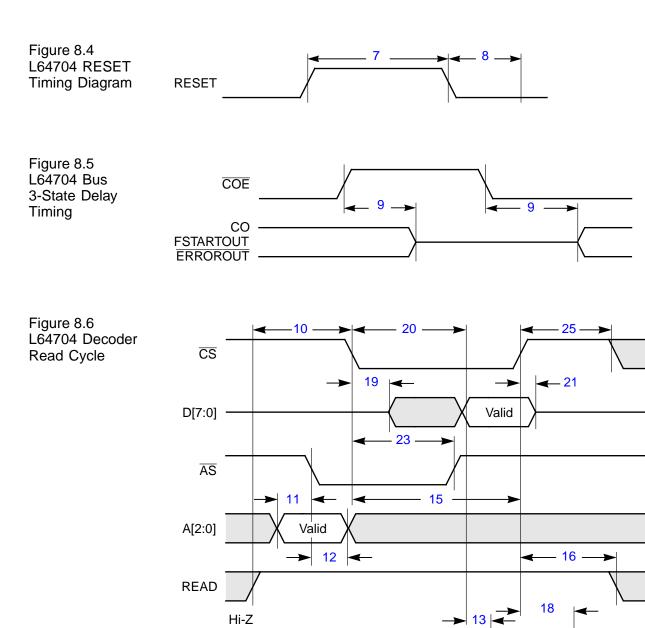

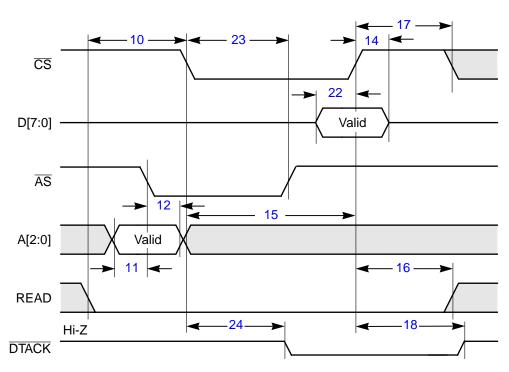

| 8.6  | L64704 Decoder Read Cycle                                 | 8-7  |

| 8.7  | L64704 Decoder Write Cycle                                | 8-8  |

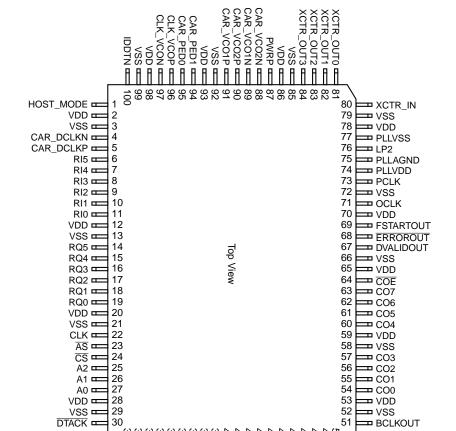

| 8.8  | L64704 100-Pin PQFP Pinout                                | 8-11 |

| 8.9  | 100-Pin PQFP Mechanical Drawing (Sheet 1 of 2)            | 8-12 |

| A.1  | Quick Overview of the Serial Bus                          | A-2  |

| A.2  | Quick Overview of Serial Bus Write/Read Cycles            | A-3  |

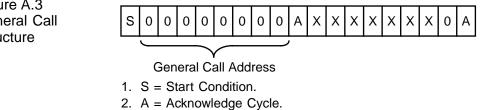

| A.3  | General Call Structure                                    | A-4  |

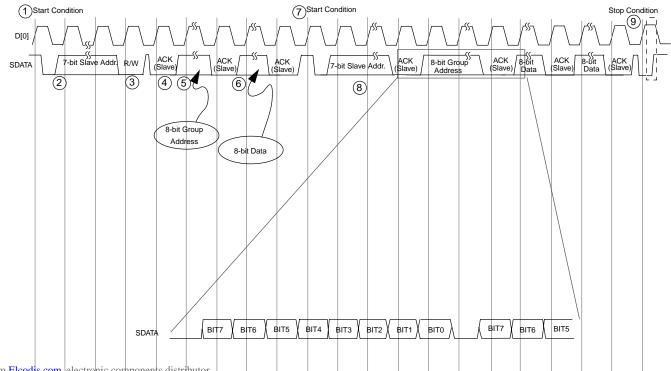

| A.4  | Burst Write to Slave (Master-Transmitter, Slave-Receiver) | A-5  |

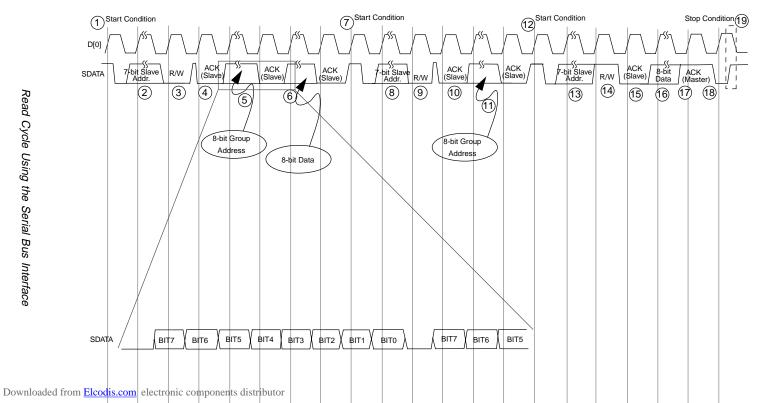

| A.5  | Single Read From Slave                                    | A-7  |

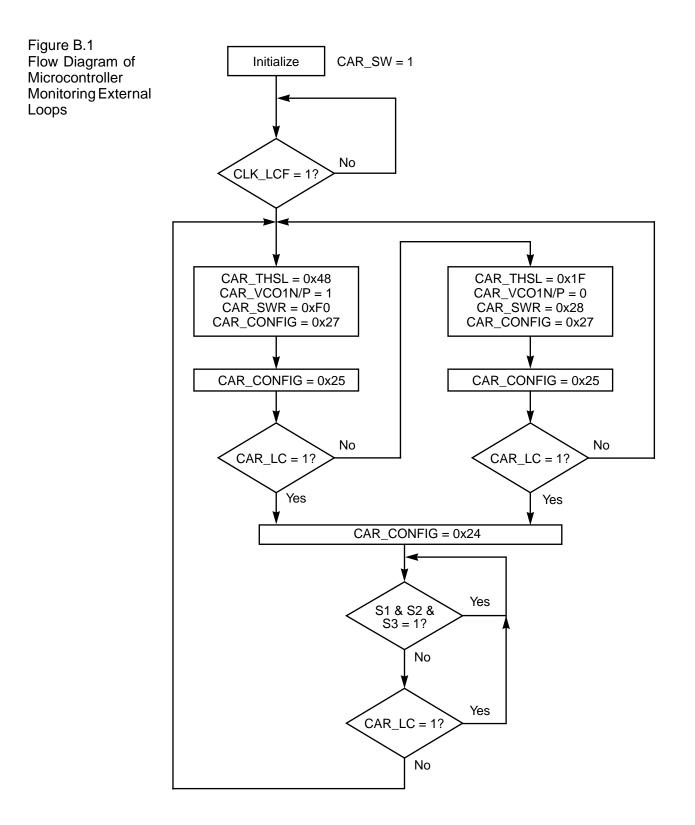

| B.1  | Flow Diagram of Microcontroller Monitoring External Loops | B-3  |

| B.2  | AGC Loop Control                                          | B-5  |

| C.1  | Simplest Oscillator                                       | C-1  |

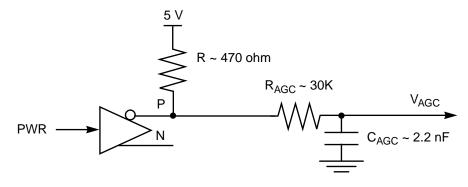

| C.2  | Pierce Crystal Oscillator Circuit                         | C-2  |

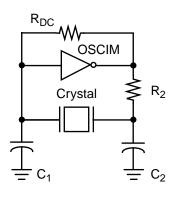

| C.3  | A Third Overtone (Higher Frequency) Oscillator Circuit    | C-4  |

| C.4  | A Low Frequency Range (kHz) Oscillator Circuit            | C-5  |

| 3.1  | Register Overview                                         | 3-2  |

| 3.2  | Register Map                                              | 3-2  |

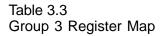

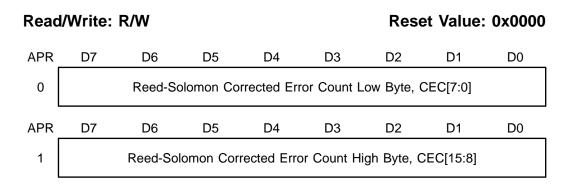

| 3.3  | Group 3 Register Map                                      | 3-20 |

| 3.4  | Group 4 Register Map                                      | 3-27 |

| 4.1  | CLK/SCLK Ratio                                            | 4-7  |

| 4.2  | Values for PLL_S, PLL_N, PLL_T, and PLL_M                 | 4-8  |

| 5.1  | M as a Function of CLK_DR and CLK_RATIO                   | 5-7  |

| 5.2  | Natural Frequency as a Function of M                      | 5-8  |

| 5.3  | Example of Data Rates                                     | 5-10 |

|      |                                                           |      |

Tables

х

| 5.4  | Example of Data Rates for Narrow SAW Filter              | 5-10 |

|------|----------------------------------------------------------|------|

| 5.5  | PWR_BW as a Function of Symbol Rate                      | 5-23 |

| 6.1  | Stage 2 Synchronization Values                           | 6-9  |

| 7.1  | Puncture Patterns for Various Code Rates                 | 7-4  |

| 7.2  | Viterbi Threshold Values                                 | 7-7  |

| 8.1  | L64704 Absolute Maximum Rating (Referenced to $V_{SS}$ ) | 8-2  |

| 8.2  | L64704 Recommended Operating Conditions                  | 8-2  |

| 8.3  | L64704 Capacitance                                       | 8-2  |

| 8.4  | L64704 DC Characteristics                                | 8-3  |

| 8.5  | L64704 Pin Description Summary                           | 8-4  |

| 8.6  | L64704 AC Timing Parameters                              | 8-8  |

| 8.7  | L64704 Ordering Information                              | 8-10 |

| 8.8  | Alphabetical Pin List for the 100-pin PQFP               | 8-10 |

| B.1  | QPSK Demodulator Loop Registers                          | B-2  |

| B.2  | PWR_LVL Register Setting                                 | B-4  |

| B.3  | QPSK Demodulator Loop Registers                          | B-6  |

| B.4  | $\omega_n$ for Fixed Rate Operation (Damping = 1)        | B-11 |

| B.5  | Group 4 Decoder Register Map                             | B-14 |

| B.6  | Group 4 Decoder Registers Actual Configuration           | B-15 |

| B.7  | Typical Clock and Carrier VCO Gains                      | B-16 |

| B.8  | CAR_PED Output Pins                                      | B-17 |

| B.9  | Group 4 Register Map                                     | B-18 |

| B.10 | Group 4 Actual Configuration                             | B-19 |

| C.1  | Component Values for the Circuit Shown in Figure C.2     | C-3  |

| C.2  | Component Values for the Circuit Shown in Figure C.3     | C-4  |

| C.3  | Component Values for the Circuit Shown in Figure C.4     | C-5  |

May 1997

хіі

May 1997

## Preface

|              | This book is the primary reference and technical manual for the L64704<br>Satellite Decoder. It contains a complete functional description for the<br>L64704 and includes complete physical and electrical specifications for<br>the L64704. |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Audience     | This document assumes that you have some familiarity with digital satellite communications, microprocessors, and related support devices. The people who benefit from this book are:                                                         |

|              | <ul> <li>Engineers and managers who are evaluating the L64704 for possible<br/>use in a digital satellite receiver</li> </ul>                                                                                                                |

|              | <ul> <li>Engineers who are designing the L64704 into a digital satellite receiver</li> </ul>                                                                                                                                                 |

| Organization | This document has the following chapters and appendix:                                                                                                                                                                                       |

|              | <ul> <li>Chapter 1, Introduction, defines the general characteristics and<br/>capabilities of the L64704 Satellite Decoder.</li> </ul>                                                                                                       |

|              | <ul> <li>Chapter 2, L64704 Signal Definitions, describes the characteristics<br/>of the L64704 signals that are used to interface with an external<br/>channel and microcontroller.</li> </ul>                                               |

|              | <ul> <li>Chapter 3, L64704 Registers, provides a summary of the registers<br/>and tables in the L64704.</li> </ul>                                                                                                                           |

|              | <ul> <li>Chapter 4, Channel Interfaces and Data Control, discusses the<br/>Input Channel and Output Channel interfaces and the circuitry that<br/>supports them.</li> </ul>                                                                  |

|              | <ul> <li>Chapter 5, Demodulator Module Functional Description,<br/>describes the operation of the Demodulator portion of the Satellite<br/>Decoder.</li> </ul>                                                                               |

|                         | <ul> <li>Chapter 6, Decoding Pipeline Synchronization, discusses the<br/>mechanism for synchronizing the internal decoder modules to the<br/>incoming data stream.</li> </ul>        |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                         | <ul> <li>Chapter 7, The FEC Decoder Pipeline, describes the various logic<br/>modules that comprise the FEC decoding pipeline.</li> </ul>                                            |

|                         | <ul> <li>Chapter 8, L64704 Specifications, describes the electrical and<br/>mechanical characteristics of the L64704.</li> </ul>                                                     |

|                         | <ul> <li>Appendix A, Programming the L64704 Using the Serial Bus<br/>Protocol, provides information on how to program the L64704 using<br/>its Serial Bus protocol.</li> </ul>       |

|                         | <ul> <li>Appendix B, L64704 Application Notes, provides application infor-<br/>mation on connecting the L64704 in your circuit and programming it<br/>to meet your needs.</li> </ul> |

|                         | <ul> <li>Appendix C, Oscillator Cells, provides information on the oscillator<br/>cells used in the L64704, and how to design oscillators using these<br/>cells.</li> </ul>          |

| Related<br>Publications | L64002 MPEG-2 Audio/Video Decoder Technical Manual,<br>Order No. I14011                                                                                                              |

|                         | L64007 MPEG-2, DVB and TSAT Transport Demultiplexer Technical Manual, Document No. DB14-000007-00                                                                                    |

|                         | European Digital Video Broadcast Standard, DTVB 1110 Revision 7.<br>This document is available from:                                                                                 |

|                         | DVB Project Office<br>European Broadcasting Union<br>Ancienne Route, 17A<br>Grand Saconnex<br>Geneva, Switzerland                                                                    |

|                         |                                                                                                                                                                                      |

xiv

| Conventions            | The first time a word or phrase is defined in this manual, it is italicized. |

|------------------------|------------------------------------------------------------------------------|

| Used in This<br>Manual | The following signal naming conventions are used throughout this manual:     |

|                        | A local circuition of the tic true or wall durk on the circuit is I OW       |

- A level-significant signal that is true or valid when the signal is LOW always has an overbar ( ) over its name.

- An edge-significant signal that initiates actions on a HIGH-to-LOW transition always has an overbar ( ) over its name.

The word *assert* means to drive a signal true or active. The word *deassert* means to drive a signal false or inactive.

Hexadecimal numbers are indicated by the prefix "0x" before the number—for example, 0x32CF. Binary numbers are indicated by a subscripted "2" following the number—for example, 0011.0010.1100.1111<sub>2</sub>.

Operations on registers are referred to using the binary numbers 0 and 1. Output signal levels are referred to by the designations HIGH and LOW. Example: Set the XCTR0 register bit to 1 to force the XCTR\_OUT0 pin HIGH.

May 1997

xvi

## Chapter 1 Introduction

|                | This chapter introduces the L64704 Satellite Decoder from LSI Logic.<br>The L64704 is designed specifically to meet the needs of satellite broad-<br>cast digital TV.                                                                                                                                                                                                     |  |  |  |  |  |  |

|----------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

|                | The sections in this chapter are:                                                                                                                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                | <ul> <li>Section 1.1, "General Description," provides an overview of the architecture of the L64704 Satellite Decoder.</li> </ul>                                                                                                                                                                                                                                         |  |  |  |  |  |  |

|                | <ul> <li>Section 1.2, "Typical Application," describes how the L64704 is used<br/>in a typical satellite decoder system.</li> </ul>                                                                                                                                                                                                                                       |  |  |  |  |  |  |

|                | <ul> <li>Section 1.3, "Features Summary," summarizes the main features of<br/>the L64704.</li> </ul>                                                                                                                                                                                                                                                                      |  |  |  |  |  |  |

| 1.1<br>General | The L64704 Satellite Decoder contains two main blocks: a BPSK/QPSK Demodulator and a Concatenated FEC decoder.                                                                                                                                                                                                                                                            |  |  |  |  |  |  |

| Description    | The BPSK/QPSK module performs binary and quadrature phase-shift keying (BPSK/QPSK) demodulation, a method of extracting a digital signal from a phase-modulated analog signal. The BPSK/QPSK module is designed specifically for a satellite broadcast digital TV receiver, and is compliant with the European digital video broadcast (DVB) standard (DTVB 1110 Rev. 7). |  |  |  |  |  |  |

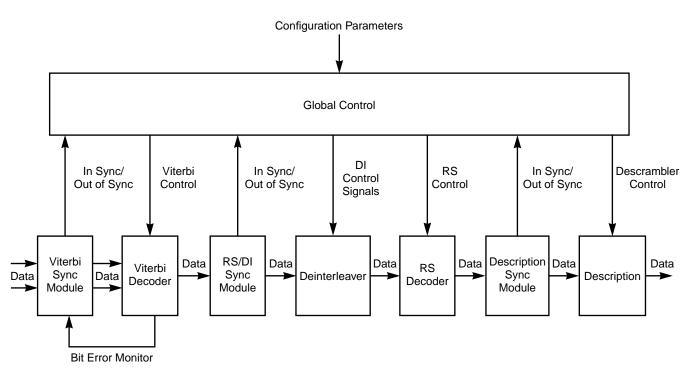

|                | The FEC Decoder pipeline is a complete concatenated Forward Error<br>Correction decoder that utilizes a Viterbi inner code and a Reed-Solomon<br>outer code. The FEC decoding pipeline also contains all of the necessary<br>synchronization, deinterleaving, and scrambling functions for a complete<br>decoding solution.                                               |  |  |  |  |  |  |

|                | The L64704 is compliant with specifications of the "Baseline<br>Modulation/Channel Coding System" by the Digital Video Broadcast                                                                                                                                                                                                                                          |  |  |  |  |  |  |

(DVB) Association. LSI Logic fabricates the L64704 using its LCB500K, 3.3-volt, 0.5-micron, HCMOS process technology.

The L64704 provides maximum integration and flexibility for system designers at a minimum cost. The number of external components required to build a system is minimal; only a dual operational amplifier and passive resistors and capacitors are needed for the implementation of the clock and carrier loop filters.

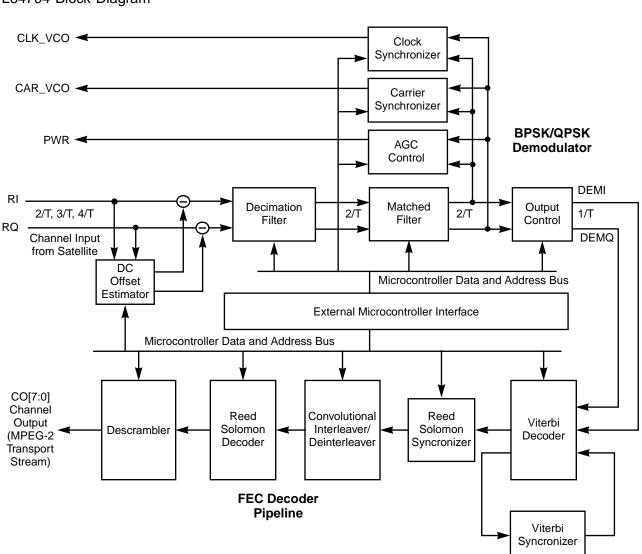

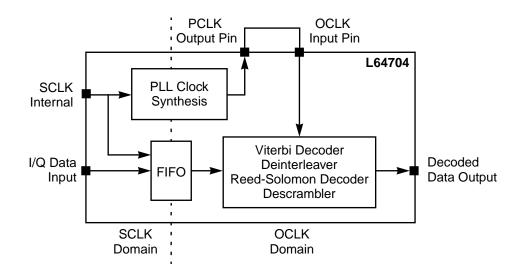

Figure 1.1 shows a block diagram of the L64704.

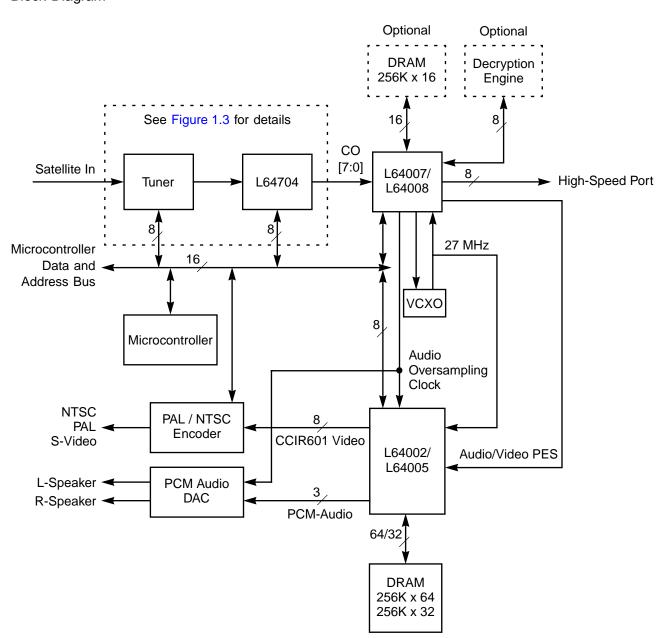

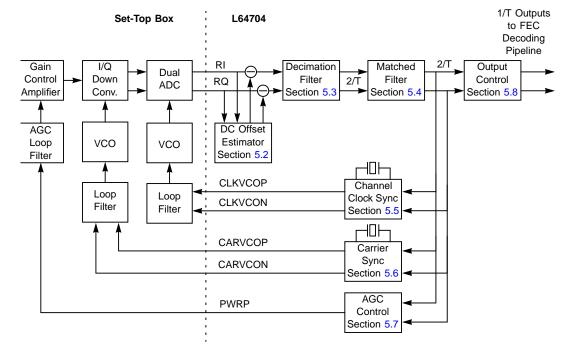

Figure 1.1 L64704 Block Diagram 1.2A typical application of the L64704 is satellite digital TV reception accord-Typicaling to the DVB 1110 Rev. 7 standard. Figure 1.2 shows the L64704 Sat-Applicationellite Decoder in a typical Satellite Receiver Set-Top Decoder box.

Figure 1.2 Set-Top Decoder Box Block Diagram

Typical Application

LSI Logic offers circuits that make up the most complex portions of the logic found in a Set-Top Decoder box. These circuits include the:

- ♦ L64704 Satellite Decoder

- ♦ L64007 MPEG-2 Transport Demultiplexer

- ♦ L64002 MPEG-2 Audio/Video Decoder

For more information on the other integrated circuits in the Set-Top Decoder box, see their associated manuals.

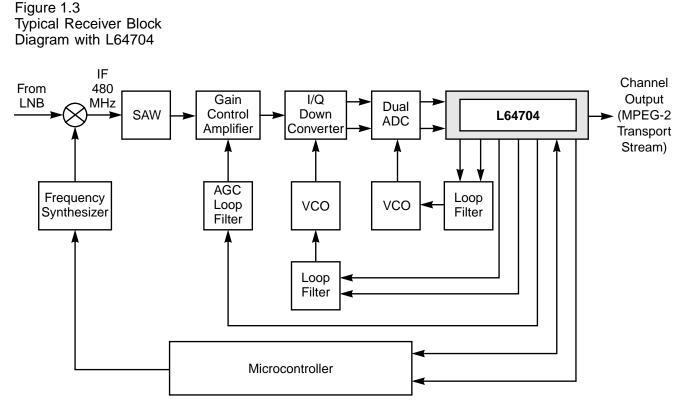

Figure 1.3 shows a block diagram of a satellite tuner that includes the L64704.

The receiver block receives the microwave channel data from the satellite dish, demodulates and decodes it, and outputs an MPEG-2 transport stream.

# **1.3**This section summarizes the main features of the L64704. Subsequent**Features**chapters describe these features in more detail.**Summary**

- Variable BPSK/QPSK demodulation from 2 to 62.5 Mbit/s

- Matched filter (square root raised cosine filter, roll-off factor of 35%)

- Decimation filters for input oversampling ratios of 2/T, 3/T, and 4/T

- Clock synchronization

- Carrier synchronization featuring a frequency sweep capability for signal acquisition

- Power estimation for AGC control

- Internal DC offset control

- Programmable Viterbi decoder module for rates 1/2, 2/3, 3/4, 5/6, 7/8

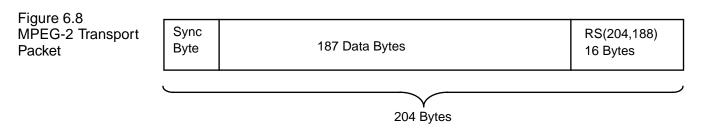

- ♦ (204/188) Reed-Solomon decoder

- Auto synchronization for Viterbi decoder

- Programmable synchronization for Deinterleaver, Reed-Solomon Decoder, and Descrambler

- FEC module flags uncorrectable frames by setting the ninth bit of the MPEG Transport packet.

- Bit Error monitoring for channel performance measurements

- Depth 12 deinterleaver

- Serial host interface compatible with the LSI Logic Serial Control bus interface

- Power down mode

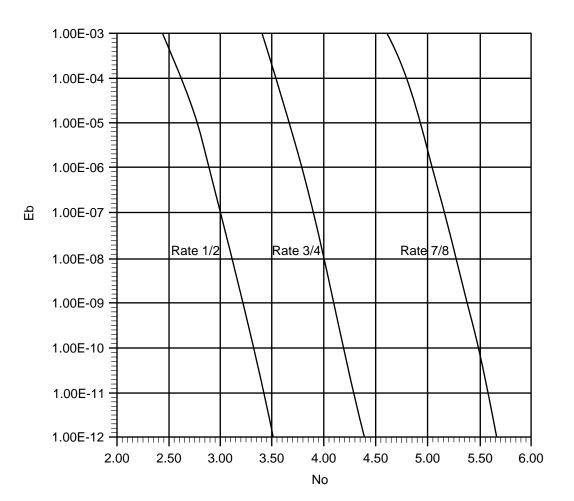

Figure 1.4 shows a performance graph for the L64704 Satellite Decoder.

Downloaded from Elcodis.com electronic components distributor

## Chapter 2 L64704 Signal Definitions

This chapter describes the signals that comprise the L64704 Satellite Decoder's interface to other components. This chapter is divided into seven sections that describe the various buses:

- Section 2.1, "Channel Interface," describes the input channel interface to the L64704.

- Section 2.2, "Channel Clock Recovery," lists the signals that make up the input channel clock recovery circuitry.

- Section 2.3, "Channel Data Output Interface," describes the signals that connect the channel data outputs to the MPEG demultiplexer.

- Section 2.4, "Phase-Locked Loop Interface," lists the signals that are used to connect the L64704 to an external Phase-Locked Loop.

- Section 2.5, "Carrier Synchronizer Loop Controls," provides a list of the signals that are used to synchronize the I/Q Down Converter circuitry.

- Section 2.6, "Microcontroller Interface," shows the signals that are used to connect the L64704 to an external microcontroller.

- Section 2.7, "Control Signals," describes the various signals that are necessary for the operation of the L64704, but do not fit into any of the categories above.

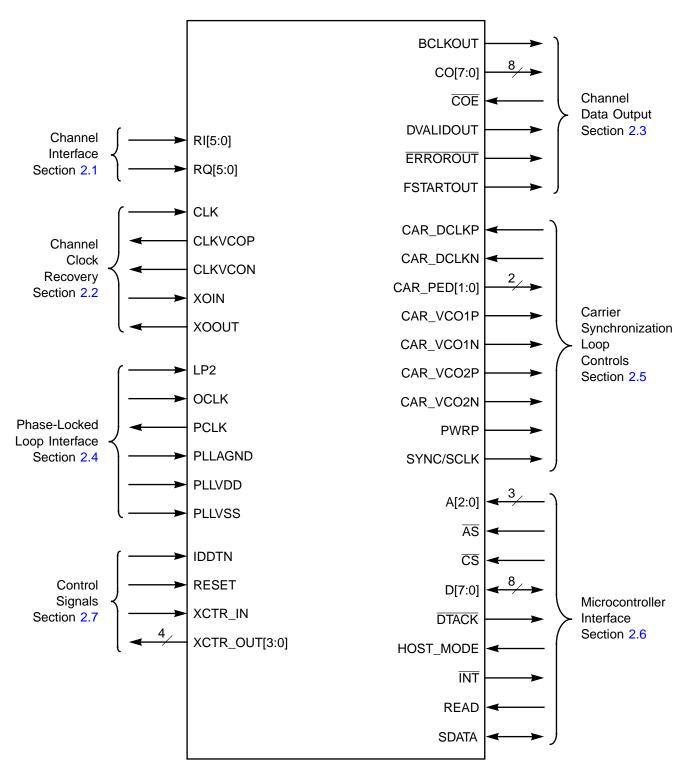

Figure 2.1 shows the logic symbol for the L64704.

Figure 2.1 L64704 Logic Diagram

L64704 Signal Definitions

2-2

| 2.1<br>Channel<br>Interface      | The two signal<br>the satellite tur<br>Recovery sect | The Channel Interface is the input path to the L64704 Satellite Decoder.<br>The two signal buses RI[5:0] and RQ[5:0] are the I and Q streams from<br>the satellite tuner circuit. The CLK signal discussed in the Channel Clock<br>Recovery section is used to strobe in the data signals. The Channel<br>Interface is discussed in Section 4.2, "Channel Data Input Interface." |                 |  |  |

|----------------------------------|------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|--|--|

|                                  | RI[5:0]                                              | I Channel Data<br>Received I Channel data input bus.                                                                                                                                                                                                                                                                                                                             | Input           |  |  |

|                                  | RQ[5:0]                                              | <b>Q Channel Data</b><br>Received Q Channel data input bus.                                                                                                                                                                                                                                                                                                                      | Input           |  |  |

| 2.2<br>Channel Clock<br>Recovery | the Channel Ir                                       | The Channel Clock Recovery logic is the logic that recovers the clock for<br>the Channel Interface. Channel Clock recovery is discussed in<br>Section 5.5, "Channel Clock Recovery."                                                                                                                                                                                             |                 |  |  |

|                                  | CLK                                                  | CLK RI/Q Input Clock Input<br>CLK is a positive, edge-triggered clock that is used to<br>strobe in input data. It is not used anywhere else in the<br>L64704, and does not propagate past the Channel<br>Interface.                                                                                                                                                              |                 |  |  |

|                                  | CLK_VCOP/N                                           | <b>Clock Loop VCO Control</b><br>These two differential signals are the Positive and tive Sigma Delta ( $\Sigma\Delta$ ) modulated output used to a the Channel Clock VCO frequency.                                                                                                                                                                                             | 0               |  |  |

|                                  | XOIN                                                 | <b>Crystal Oscillator In</b><br>The XOIN pin is the crystal oscillator or external<br>ence clock input.                                                                                                                                                                                                                                                                          | Input<br>refer- |  |  |

|                                  | XOOUT                                                | <b>Crystal Oscillator Out</b><br>The XOOUT pin is the crystal oscillator output pin                                                                                                                                                                                                                                                                                              | Output          |  |  |

2.3 The Channel Data Output Interface is the output path from the L64704. **Channel Data** It is typically connected to the input of the Transport Demultiplexer in a **Output Interface** set-top decoder application. The Channel Data Output Interface is discussed in Section 4.3, "Channel Data Output Interface."

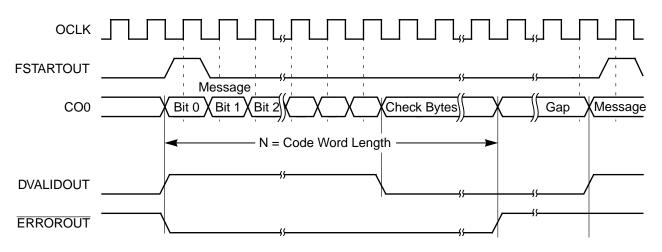

#### BCLKOUT **Byte Clock Out** Output The BCLKOUT output signal is a strobe that indicates valid data bytes on the CO[7:0] bus when the L64704 is in Parallel Channel Output mode. The BCLKOUT signal cycles once per every valid output data byte and is used by the Transport Demultiplexer to latch output data from the L64704 at the BCLKOUT rate (rather than at the OCLK rate). BCLKOUT must be disregarded in Serial Channel Output mode.

#### CO[7:0] **Channel Data Out**

These signals form the decoded output data port. In Parallel Channel Output mode (OF = 1, Group 4, APR 12) the L64704 outputs the channel data as 8-bit wide parallel data on CO[7:0]. In Serial Channel Output mode (OF = 0) the L64704 outputs the channel data as serial data on CO0. It is latched on every byte or bit clock cycle. The chronological ordering in Serial Channel output mode is MSB oldest, LSB newest.

#### COE Channel Output Enable Input When asserted, COE enables the CO[7:0], ERROROUT, and FSTARTOUT pins. DVALIDOUT is unaffected by the COE pin and operation of the decoder continues regardless of the state of this pin.

#### Valid Data Out DVALIDOUT DVALIDOUT indicates that CO[7:0] contains the cor-

rected channel data. New data is valid on the output when DVALIDOUT is HIGH. DVALIDOUT is not asserted during the propagated check and GAP bytes. This pin is set LOW after the FEC RST register bit (Group 4, APR 36) is asserted.

#### ERROROUT **Error Detection Flag** Output The L64704 asserts the ERROROUT pin to flag uncorrectable errors. The L64704 asserts the ERROROUT signal at the beginning of any frame that contains an uncorrectable error, and deasserts it at the end of the

#### Output

Output

frame (if the error condition is removed). ERROROUT is exactly aligned with the output data stream. This pin is set HIGH after the FEC\_RST register bit (Group 4, APR 36) is asserted.

# FSTARTOUTFrame Start OutputOutputThe L64704 asserts FSTARTOUT during the first bit of<br/>every frame with valid data in Serial Channel Output<br/>mode and during the first byte in Parallel Channel Output<br/>mode. FSTARTOUT is valid only when DVALIDOUT is<br/>HIGH. This pin is set LOW after the FEC\_RST register<br/>bit (Group 4, APR 36) is asserted.

| 2.4<br>Phase-Locked<br>Loop Interface | Recovery circ<br>on the Viterbi<br>into the L647 | ocked Loop (PLL) circuitry multiplies the Channel Clock<br>cuit SCLK signal by 2, 3, or 4 times the symbol rate, based<br>code rate. The output from the PLL (PCLK) is brought back<br>704 on the OCLK pin to clock the FEC Decoder logic. Use<br>discussed in Section 4.4, "PLL Clock Generation."                                                       |

|---------------------------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                                       | LP2                                              | Input to VCO Input<br>This pin is the input to the internal voltage controlled<br>oscillator. It is normally connected to the output of an<br>external RC timing circuit.                                                                                                                                                                                 |

|                                       | OCLK                                             | Decoder ClockInputThe positive edge of OCLK is a positive, edge-triggered<br>clock. The L64704 internally processes data (Viterbi<br>decoder, Synchronization, Descrambler, Deinterleaver,<br>Reed-Solomon Decoder) based on OCLK. All data out-<br>puts (DVALIDOUT, ERROROUT, FSTARTOUT, CO[7:0])<br>are referenced to OCLK. OCLK is independent of CLK. |

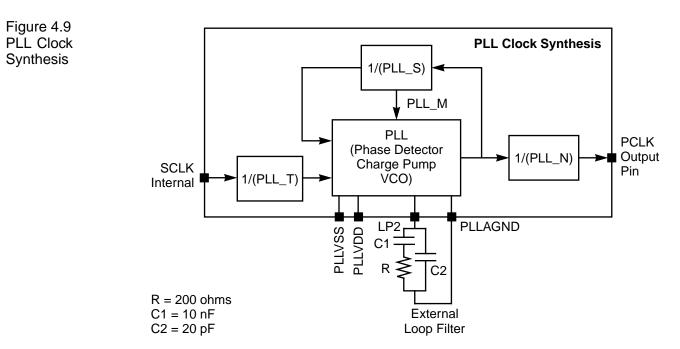

|                                       | PCLK                                             | PLL Clock OutputOutputThe L64704's internal PLL clock synthesis module gener-<br>ates the clock signal PCLK. The PLL is driven by the<br>SCLK internal signal (QPSK symbol clock). The PLL<br>clock synthesis module can be configured to generate a<br>PCLK rate that is appropriate for all Viterbi code rates<br>specified under the DVB standard.     |

|                                       | PLLAGND                                          | PLL Analog GroundInputAnalog ground pin for the PLL module. This pin is nor-<br>mally connected to the system ground plane.                                                                                                                                                                                                                               |

| PLLVDD | PLL Power                                               | Input |

|--------|---------------------------------------------------------|-------|

|        | Power supply pin for the PLL module. This pin is nor    | mally |

|        | connected to the system power (V <sub>DD</sub> ) plane. |       |

PLLVSS PLL Ground Input Power supply pin for the PLL module. This pin is normally connected to the system ground plane.

2.5 Carrier Synchronizer

**Loop Controls**

Carrier Synchronizer Loop controls are used to synchronize the I/Q Down Converter circuitry. Carrier Synchronizer Loop controls are discussed in Section 5.6, "Carrier Synchronizer."

#### CAR\_DCLKP/N

#### VCO Prescaler Input

Input

Output

The CAR\_DCLK pins are differential inputs for the prescaled (divided) Carrier VCO clock (typically = VCO frequency / 32).

#### CAR\_PED[1:0]

#### **Carrier Phase Error Detector**

Output These pins are the 2-bit outputs from the Phase Error Detector. You use the CAR\_PED outputs for carrier loop implementation in combination with an external digital to analog converter. It should be used when operating at rates less than 5 Mbaud.

#### CAR VCO1P/N

#### Carrier Loop VCO Control 1

When CAR\_OUT\_SEL (Group 4, APR 33) is set to 0, these pins are the Positive/Negative  $\Sigma\Delta$  modulated outputs that control the carrier VCO frequency. CAR VCO1P/N feed external RC circuit number 1. A LOW output decreases the carrier VCO frequency. A HIGH output increases the carrier VCO frequency. A high impedance level maintains the carrier VCO frequency. When CAR\_OUT\_SEL is set to 1, these pins carry the CAR\_PED.2 and CAR\_PED.3 signals.

#### CAR\_VCO2P/N

#### **Carrier Loop VCO Control 2**

Output When CAR\_OUT\_SEL (Group 4, APR 33) is set to 0, these pins are the Positive/Negative  $\Sigma\Delta$  modulated outputs that control the carrier VCO frequency. CAR\_VCO2P/N feed external RC circuit number 2. A LOW output decreases the carrier VCO frequency. A

2-6

HIGH output increases the carrier VCO frequency. A high impedance level maintains the carrier VCO frequency. When CAR\_OUT\_SEL is set to 1, these pins carry the CAR\_PED.4 and CAR\_PED.5 signals.

# PWRPPower ControlOutputThe power control signal is the positive $\Sigma\Delta$ modulated<br/>output used for power control. This signal can drive an<br/>external passive RC filter that feeds the gain control<br/>stage.

#### SYNC/SCLK Synchronization Status Flag Output

When the SYNC/SCLK bit (Group 4, APR 14) is set to 0, the SYNC/SCLK pin indicates the synchronization status for one of three synchronization modules in the L64704 (Viterbi Decoder sync, DI/RS sync, Descrambler sync). When HIGH the SYNC/SCLK output indicates the synchronization has been achieved for the chosen sync module. When LOW, the SYNC/SCLK output indicates an out-of-synchronization condition.

When the SYNC/SCLK bit is set to 1, the SYNC/SCLK pin carries the SCLK signal that is used to clock the external DAC during low baud rate operation. See Section 5.6.2.3, "Low Baud Rate Operation" for more information.

| 2.6                          | The Microcontroller Interface connects the L64704 to a microcontroller. |                                                                                                                                                                                                                                                                                        |  |  |  |

|------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Microcontroller<br>Interface | A[2:0]                                                                  | AddressInputA[2:0] comprise the decoder address bus. The addressbus is used in conjunction with an eight-bit data busD[7:0], a read/write strobe (READ), a chip select strobe $(\overline{CS})$ , and an address strobe $(\overline{AS})$ to select, read andwrite internal registers. |  |  |  |

|                              | ĀS                                                                      | Address StrobeInput $\overline{AS}$ is an active-LOW address strobe input. The L64704latches the address on A[2:0] on the falling edge of $\overline{AS}$ .                                                                                                                            |  |  |  |

|                              | CS                                                                      | $\begin{array}{llllllllllllllllllllllllllllllllllll$                                                                                                                                                                                                                                   |  |  |  |

latch the data from the L64704 on the rising edge of  $\overline{CS}$ . During a write cycle,  $\overline{CS}$  must go LOW prior to data being valid from the controller to the L64704. After the data has met the minimum setup time, the microcontroller takes  $\overline{CS}$  HIGH to strobe the data. There is a minimum write time to allow for internal synchronization. Setup and hold times are measured with respect to the falling edge of  $\overline{CS}$ .

- D[7:0]Data BusBidirectionalD[7:0] is the bidirectional data bus; it is the input data bus<br/>when data is written to the chip and the data output bus<br/>when the chip is read in Parallel Host Interface mode<br/>(HOST\_MODE pin is HIGH). The data lines are 3-stated<br/>when not being read or written. When Serial Host Inter-<br/>face mode is selected (HOST\_MODE pin is LOW), D0 is<br/>used as the Serial Clock signal to synchronize the trans-<br/>fer of serial data on the SDATA pin. The remaining seven<br/>bits of the data bus function as the slave address.

- DTACKData AcknowledgeOutputData Acknowledge is an active-LOW output indicating<br/>that the transaction on the D[7:0] bus has been<br/>completed.

- HOST\_MODE Serial or Parallel Host Interface Select Input When HOST\_MODE is LOW, it selects the Serial Host Interface mode; when HIGH, it selects the Parallel Host Interface mode.

- INT

Interrupt

Output

The L64704 asserts INT LOW when an internal unmasked interrupt flag is set. INT remains asserted as long as the interrupt condition persists and the interrupt flag is not masked.

INT

READ

Read/Write Strobe Input The microcontroller drives READ HIGH to indicate that

#### The microcontroller drives READ HIGH to indicate that the current transaction is a read from the L64704, and LOW to indicate that it is a write to the L64704.

SDATASerial Host Interface DataBidirectionalThis bidirectional pin is the data input or output pin when<br/>Serial Host Interface mode is selected (HOST\_MODE is<br/>LOW).

2-8

These signals control the operation of the L64704. They are not associ-2.7 **Control Signals** ated with any particular interface.

| IDDTN   | Test PinInputIDDTN is an LSI Logic internal test pin. Connect this pinLOW for normal operation.                                                                                                                                                                                                                                              |

|---------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET   | Reset Input<br>This active-HIGH signal resets all internal data paths.<br>Reset timing is asynchronous to the device clocks. Reset<br>does not affect the configuration registers. It performs the<br>same operation as the reset bits specified in Section<br>3.6.31, "Group 4, APR 36 External Output Control Bits<br>and Reset Register." |

| XCTR_IN | Control Input PinInputThe XCTR_IN pin is an external input control pin. It is                                                                                                                                                                                                                                                                |

sensed by reading the corresponding bit in the Group 3, APR 6 register.

#### XCTR\_OUT[3:0]

#### **Control Output Pins**

#### Output The XCTR\_OUT[3:0] pins are external output control pins. They are set by programming the corresponding bits in the Group 4, APR 36 register.

## Chapter 3 L64704 Registers

This chapter discusses the L64704 internal registers. It also provides a description of the internal memory mapping and describes how to access these registers from the system interface. This chapter is intended primarily for system programmers who are developing software drivers.

This chapter contains the following sections:

- Section 3.1, "L64704 Register Overview," provides an overview of the registers contained within the L64704.

- Section 3.2, "Reset and How It Affects Registers," describes the three separate methods of resetting the L64704 and how each method affects the registers.

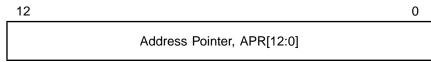

- Section 3.3, "Group 0, 1 Address Pointer Register," describes how to address and use the Address Pointer Register.

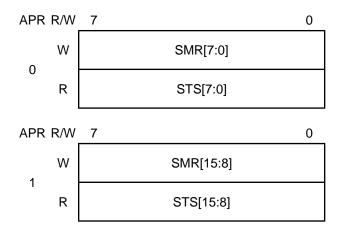

- Section 3.4, "Group 2 Registers," provides information on the use of the System Mode and System Status Registers.

- Section 3.5, "Group 3 Registers," describes how to read and use the Status Registers.

- Section 3.6, "Group 4 Registers" provides information on programming and using the L64704's Configuration Registers.

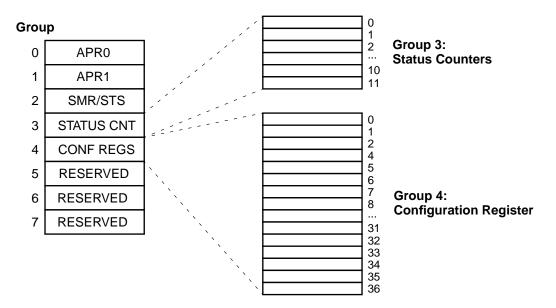

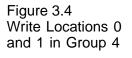

This chapter provides complete information on how to use these registers, but does not provide information on how to program the registers for a specific application. See Appendix B, "L64704 Application Notes" for applications information. 3.1 The L64704 registers and memory resources are divided into five groups: Group 0 through Group 4. Group 0 and 1 contain the Address Pointer Register. This pointer is used to address the registers in Groups 2, 3 and 4. Group 2 addresses the System Status Register when read and the System Mode Register when written. Group 3 contains the status counters, and Group 4 contains the configuration registers (See Table 3.1).

Table 3.1 Register Overvie

| Group | Function                      | Page |

|-------|-------------------------------|------|

| 0     | Address Pointer Register, LSB | 3-10 |

| 1     | Address Pointer Register, MSB | 3-10 |

| 2     | System Mode/Status Registers  | 3-11 |

| 3     | Status Registers              | 3-20 |

| 4     | Configuration Registers       | 3-26 |

| 5     | Reserved                      |      |

| 6     | Reserved                      |      |

| 7     | Reserved                      |      |

Table 3.2 shows the complete Register Map for the L64704 Satellite Decoder.

Table 3.2 Register Map

| Group          | APR | Bit(s) | R/W | Description                            | Acronym     | Page |  |

|----------------|-----|--------|-----|----------------------------------------|-------------|------|--|

| 0              | N/A | 7:0    | W   | Address Pointer Register LSB           | APR         | 3-10 |  |

| 1              | N/A | 7:0    | W   | Address Pointer Register MSB           | APR         | 3-10 |  |

| 2              | 0   | 7:0    | R   | System Status Register [7:0]           | STS         | 3-16 |  |

|                |     | 7:0    | W   | System Mode Register [7:0]             | SMR         | 3-11 |  |

|                | 1   | 7:0    | R   | System Status Register [15:8]          | STS         | 3-16 |  |

|                |     | 7:0    | W   | System Mode Register [15:8]            | SMR         | 3-11 |  |

| 3              | 0   | 7:0    | R   | Reed-Solomon Corrected Error Count     | CEC[7:0]    | 3-21 |  |

|                | 1   | 7:0    | R   | Reed-Solomon Corrected Error Count     | CEC[15:8]   | 3-21 |  |

|                | 2   | 7:0    | R   | Reed-Solomon Uncorrected Error Count   | UEC[7:0]    | 3-21 |  |

|                | 3   | 7:0    | R   | Reed-Solomon Uncorrected Error Count   | UEC[15:8]   | 3-21 |  |

|                | 4   | 7:0    | R   | Viterbi Bit Error Rate Count Low Byte  | VBERC[7:0]  | 3-22 |  |

|                | 5   | 7:0    | R   | Viterbi Bit Error Rate Count High Byte | VBERC[15:8] | 3-22 |  |

| (Sheet 1 of 4) |     |        |     |                                        |             |      |  |

3-2

#### Table 3.2 (Cont.) Register Map

| Group    | APR     | Bit(s) | R/W | Description                              | Acronym        | Page |

|----------|---------|--------|-----|------------------------------------------|----------------|------|

| 3        | 6       | 7      | R   | Demodulator Signal to Noise Ratio        | Demod_SNR      | 3-22 |

|          |         | 6      | R   | External Control Bit Input               | XCTR_IN        | 3-22 |

|          |         | 5:0    | R   | Measured VCO Frequency, Upper Bits       | CAR_VCOF[13:8] | 3-22 |

|          | 7       | 7:0    | R   | Measured VCO Frequency, Lower Byte       | CAR_VCOF[7:0]  | 3-23 |

|          | 8       | 7:0    | R   | AGC Loop Voltage Meter                   | PWR_LVL[7:0]   | 3-23 |

|          | 9       | 5      | R   | Carrier Frequency Lock Flag              | CAR_LCF        | 3-23 |

|          |         | 4      | R   | Carrier Phase Lock Flag                  | CAR_LC         | 3-23 |

|          |         | 3      | R   | Clock Frequency Lock Flag                | CLK_LCF        | 3-23 |

|          |         | 2      | R   | Stage 3 Synchronization Flag             | S3             | 3-23 |

|          |         | 1      | R   | Stage 2 Synchronization Flag             | S2             | 3-23 |

|          |         | 0      | R   | Stage 1 Synchronization Flag             | S1             | 3-23 |

|          | 10      | 5:0    | R   | RI Input Readback                        | RI             | 3-25 |

|          | 11      | 5:0    | R   | RQ Input Readback                        | RQ             | 3-26 |

| 4        | 0       | 5:0    | R/W | Phase-Locked Loop Config. Param. N       | PLL_N[5:0]     | 3-28 |

|          | 1       | 5:0    | R/W | Phase-Locked Loop Config. Param. S       | PLL_S[5:0]     | 3-28 |

|          | 2       | 7      | R/W | (I, -Q) Symbol Format                    | IMQ            | 3-29 |

|          |         | 5      | R/W | QPSK/BPSK Format Select                  | QB             | 3-29 |

|          |         | 4:0    | R/W | Phase-Locked Loop Config. Param. T       | PLL_T[4:0]     | 3-29 |

|          | 3       | 7:5    | R/W | Viterbi Code Rate                        | VCR[2:0]       | 3-30 |

|          |         | 4      | R/W | Transport Error Indicator Select         | TEI            | 3-30 |

|          |         | 3      | R/W | Select SYNC 2 Modified Algorithm         | SYNC2_MOD      | 3-30 |

|          |         | 1:0    | R/W | VCO Frequency Range for PLL Module       | PLL_M[1:0]     | 3-30 |

|          | 4       | 7:0    | R/W | Viterbi Maximum Data Bit Count 1         | VMDC1[7:0]     | 3-31 |

|          | 5       | 7:0    | R/W | Viterbi Maximum Data Bit Count 2, Low    | VMDC2[7:0]     | 3-31 |

|          | 6       | 7:0    | R/W | Viterbi Maximum Data Bit Count 2, Middle | VMDC2[15:8]    | 3-31 |

|          | 7       | 7:0    | R/W | Viterbi Maximum Data Bit Count 2, High   | VMDC2[23:16]   | 3-31 |

|          | 8       | 7:0    | R/W | Viterbi Maximum Bit Error Count          | VMBEC[7:0]     | 3-32 |

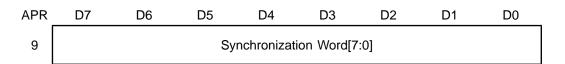

|          | 9       | 7:0    | R/W | Synchronization Word                     | Sync[7:0]      | 3-32 |

|          | 10      | 7      | R/W | Bit Error Rate Monitor                   | BER            | 3-33 |

|          |         | 1:0    | R/W | Mismatching Bits, Tracking Mode, Sync2   | L[1:0]         | 3-33 |

| (Sheet 2 | 2 of 4) |        |     |                                          |                |      |

#### Table 3.2 (Cont.) Register Map

| Group    | APR     | Bit(s) | R/W | Description                                                      | Acronym              | Page |

|----------|---------|--------|-----|------------------------------------------------------------------|----------------------|------|

| 4        | 11      | 7      | R/W | BCLKOUT Format                                                   | BF                   | 3-34 |

|          |         | 5:4    | R/W | Synchronization Status Select                                    | SSS[1:0]             | 3-34 |

|          |         | 3:2    | R/W | Synchronization States, Acquisition Mode                         | SSA[1:0]             | 3-34 |

|          |         | 1:0    | R/W | Synchronization States, Tracking Mode                            | SST[1:0]             | 3-34 |

|          | 12      | 7:5    | R/W | Symbol Size for Viterbi Bypass Mode                              | BPS[2:0]             | 3-36 |

|          |         | 3      | R/W | Descrambler Output Format                                        | OF                   | 3-36 |

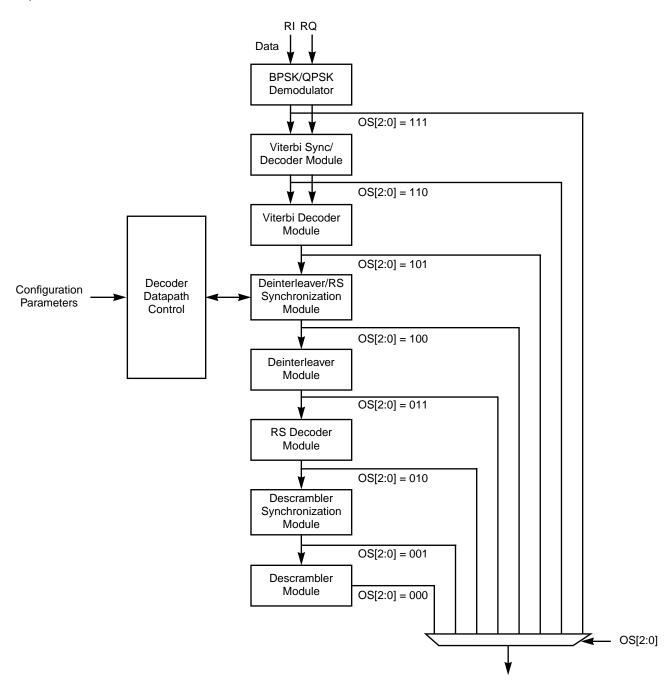

|          |         | 2:0    | R/W | Output Selector, OS[2:0]                                         | OS[2:0]              | 3-36 |

|          | 13      | 7:0    | W   | Reset for PLL Module                                             | PLL_RESET            | 3-37 |

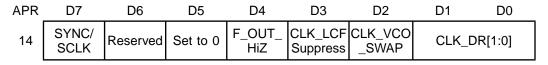

|          | 14      | 7      | R/W | SYNC/SCLK Selector Bit                                           | SYNC/SCLK            | 3-37 |

|          |         | 4      | R/W | Functional Outputs 3-stated                                      | F_OUT_HiZ            | 3-37 |

|          |         | 3      | R/W | CLK_LCF_Suppress in Timing Error<br>Detector                     | CLK_LCF_<br>Suppress | 3-37 |

|          |         | 2      | R/W | Clock Outputs Polarity Swap                                      | CLK_VCO_SWAP         | 3-37 |

|          |         | 1:0    | R/W | Decimation Filter Select                                         | CLK_DR[1:0]          | 3-37 |

|          | 15      | 6      | R/W | PCLK Bypass                                                      | PCLK_BP              | 3-39 |

|          |         | 4      | R/W | Power-Down                                                       | PD                   | 3-39 |

|          |         | 3:0    | R/W | Reference Period for Clock AFC                                   | CLK_RP[3:0]          | 3-39 |

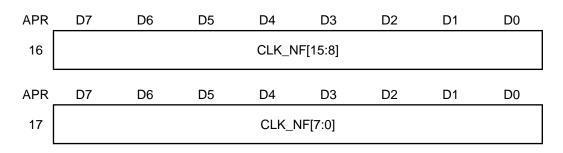

|          | 16      | 7:0    | R/W | CLK Input Nominal Frequency, Upper                               | CLK_NF[15:8]         | 3-40 |

|          | 17      | 7:0    | R/W | CLK Input Nominal Frequency, Lower                               | CLK_NF[7:0]          | 3-40 |

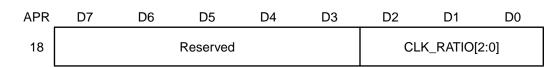

|          | 18      | 2:0    | R/W | Input Decimation Factor for RI & RQ<br>Inputs                    | CLK_RATIO[2:0]       | 3-40 |

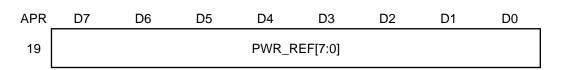

|          | 19      | 7:0    | R/W | Reference Power Level                                            | PWR_REF[7:0]         | 3-41 |