# ACS630MS

# Radiation Hardened EDAC (Error Detection and Correction Circuit)

January 1996

# Features

- Devices QML Qualified in Accordance with MIL-PRF-38535

- Detailed Electrical and Screening Requirements are Contained in SMD# 5962-96711 and Intersil' QM Plan

- 1.25 Micron Radiation Hardened SOS CMOS

- Latch-Up Free Under Any Conditions

- Military Temperature Range .....-55°C to +125°C

- Significant Power Reduction Compared to ALSTTL Logic

- DC Operating Voltage Range ..... 4.5V to 5.5V

- Input Logic Levels

- VIL = 30% of VCC Max

- VIH = 70% of VCC Min

- Input Current  $\leq$  1 $\mu\text{A}$  at VOL, VOH

- Fast Propagation Delay ...... 37ns (Max), 24ns (Typ)

# Description

The Intersil ACS630MS is a Radiation Hardened 16-bit parallel error detection and correction circuit. It uses a modified Hamming code to generate a 6-bit check word from each 16-bit data word. The check word is stored with the data word during a memory write cycle; during a memory read cycle a 22-bit word is taken form memory and checked for errors. Single bit errors in the data words are flagged and corrected. Single bit errors in check words are flagged but not corrected. The position of the incorrect bit is pinpointed, in both cases, by the 6-bit error syndrome code which is output during the error correction cycle.

The ACS630MS utilizes advanced CMOS/SOS technology to achieve high-speed operation. This device is a member of a radiation hardened, high-speed, CMOS/SOS Logic Family.

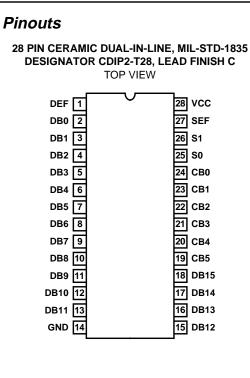

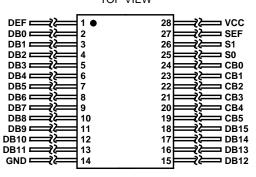

The ACS630MS is supplied in a 28 lead Ceramic Flatpack (K suffix) or a 28 Lead Ceramic Dual-In-Line Package (D suffix).

#### 28 PIN CERAMIC FLATPACK, MIL-STD-1835 DESIGNATOR CDFP3-F28, LEAD FINISH C TOP VIEW

| PART NUMBER     | TEMPERATURE RANGE | SCREENING LEVEL       | PACKAGE                  |

|-----------------|-------------------|-----------------------|--------------------------|

| 5962F9671101VXC | -55°C to +125°C   | MIL-PRF-38535 Class V | 28 Lead SBDIP            |

| 5962F9671101VYC | -55°C to +125°C   | MIL-PRF-38535 Class V | 28 Lead Ceramic Flatpack |

| ACS630D/Sample  | 25°C              | Sample                | 28 Lead SBDIP            |

| ACS630K/Sample  | 25°C              | Sample                | 28 Lead Ceramic Flatpack |

| ACS630HMSR      | 25°C              | Die                   | Die                      |

CAUTION: These devices are sensitive to electrostatic discharge; follow proper IC Handling Procedures. http://www.intersil.com or 407-727-9207 | Copyright © Intersil Corporation 1999 Spec Number 518781 File Number 3199.1

Ordering Information

1

# Function Tables

## **Control Functions**

| MEMORY | CONTROL |      |                                                 |                          |                         | ERROR   | FLAGS   |  |

|--------|---------|------|-------------------------------------------------|--------------------------|-------------------------|---------|---------|--|

| CYCLE  | S1      | S0   | EDAC FUNCTION                                   | DATA I/O                 | CHECKWORD               | SEF     | DEF     |  |

| WRITE  | Low     | Low  | Generates Checkword                             | Input Data               | Output Checkword        | Low     | Low     |  |

| READ   | Low     | High | Read Data and Check-<br>word                    | Input Data               | Input Checkword         | Low     | Low     |  |

| READ   | High    | High | Latch and Flag Error                            | Latch Data               | Latch Checkword         | Enabled | Enabled |  |

| READ   | High    | Low  | Correct Data Word and<br>Generate Syndrome Bits | Output Corrected<br>Data | Output Syndrome<br>Bits | Enabled | Enabled |  |

## **Check Word Generation**

|               |   | 16-BIT DATA WORD |   |   |   |   |   |   |   |   |    |    |    |    |    |    |

|---------------|---|------------------|---|---|---|---|---|---|---|---|----|----|----|----|----|----|

| CHECKWORD BIT | 0 | 1                | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 |

| CB0           | Х | Х                |   | Х | Х |   |   |   | Х | Х | Х  |    |    | Х  |    |    |

| CB1           | X |                  | Х | Х |   | Х | Х |   | Х |   |    | Х  |    |    | Х  |    |

| CB2           |   | х                | х |   | Х | Х |   | х |   | х |    |    | х  |    |    | Х  |

| CB3           | Х | Х                | Х |   |   |   | Х | Х |   |   | Х  | Х  | Х  |    |    |    |

| CB4           |   |                  |   | Х | Х | Х | Х | Х |   |   |    |    |    | х  | Х  | Х  |

| CB5           |   |                  |   |   |   |   |   |   | Х | Х | Х  | Х  | Х  | Х  | Х  | Х  |

NOTE: The six check bits are parity bits derived from the matrix of data bits as indicated by "x" for each bit

# **Error Syndrome Codes**

|          |   | ERROR LOCATIONS |   |   |   |   |   |   |   |   |    |    |    |    |    |    |   |   |   |   |   |   |       |

|----------|---|-----------------|---|---|---|---|---|---|---|---|----|----|----|----|----|----|---|---|---|---|---|---|-------|

| SYNDROME |   | DB              |   |   |   |   |   |   |   |   |    | NO |    |    |    |    |   |   |   |   |   |   |       |

| CODE     | 0 | 1               | 2 | 3 | 4 | 5 | 6 | 7 | 8 | 9 | 10 | 11 | 12 | 13 | 14 | 15 | 0 | 1 | 2 | 3 | 4 | 5 | ERROR |

| CB0      | L | L               | Н | L | L | Н | Н | н | L | L | L  | н  | н  | L  | Н  | Н  | L | Н | Н | Н | Н | Н | н     |

| CB1      | L | Н               | L | L | Н | L | L | н | L | н | н  | L  | н  | н  | L  | Н  | н | L | Н | Н | Н | Н | Н     |

| CB2      | Н | L               | L | Н | L | L | Н | L | н | L | н  | н  | L  | н  | н  | L  | н | Н | L | Н | Н | Н | н     |

| CB3      | L | L               | L | Н | Н | Н | L | L | н | н | L  | L  | L  | н  | н  | н  | н | Н | Н | L | Н | Н | Н     |

| CB4      | Н | Н               | Н | L | L | L | L | L | н | н | н  | н  | н  | L  | L  | L  | н | Н | Н | Н | L | Н | Н     |

| CB5      | Н | Н               | Н | Н | Н | Н | Н | Н | L | L | L  | L  | L  | L  | L  | L  | Н | Н | Н | Н | Н | L | Н     |

# **Error Functions**

| TOTAL NUME  | BER OF ERRORS   | ERROR F |      |                 |

|-------------|-----------------|---------|------|-----------------|

| 16-BIT DATA | 6-BIT CHECKWORD | SEF     | DEF  | DATA CORRECTION |

| 0           | 0               | Low     | Low  | Not Applicable  |

| 1           | 0               | High    | Low  | Correction      |

| 0           | 1               | High    | Low  | Correction      |

| 1           | 1               | High    | High | Interrupt       |

| 2           | 0               | High    | High | Interrupt       |

| 0           | 2               | High    | High | Interrupt       |

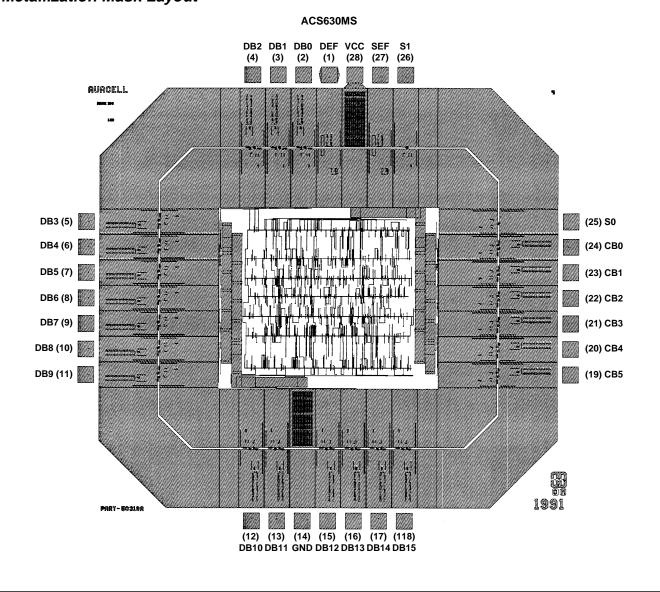

# **Die Characteristics**

#### **DIE DIMENSIONS:**

171 mils x 159 mils 4340mm x 4040mm

#### **METALLIZATION:**

Type: AISi Metal 1 Thickness: 7.125kÅ ±1.125kÅ Metal 2 Thickness: 9kÅ ±1kÅ

### **GLASSIVATION:**

Type: SiO<sub>2</sub> Thickness: 8kÅ ±1kÅ

#### WORST CASE CURRENT DENSITY: <2.0 x 10<sup>5</sup>A/cm<sup>2</sup>

## BOND PAD SIZE:

110µm x 110µm 4.4 mils x 4.4 mils

# Metallization Mask Layout

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site http://www.intersil.com

# Sales Office Headquarters

#### NORTH AMERICA

Intersil Corporation P. O. Box 883, Mail Stop 53-204 Melbourne, FL 32902 TEL: (407) 724-7000 FAX: (407) 724-7240

#### EUROPE

Intersil SA Mercure Center 100, Rue de la Fusee 1130 Brussels, Belgium TEL: (32) 2.724.2111 FAX: (32) 2.724.22.05

#### ASIA

Intersil (Taiwan) Ltd. Taiwan Limited 7F-6, No. 101 Fu Hsing North Road Taipei, Taiwan Republic of China TEL: (886) 2 2716 9310 FAX: (886) 2 2715 3029