## SINGLE CHIP READ & WRITE CHANNEL

**ADVANCE DATA**

- SUPPORTS 9-32Mbit/s DATA RATE OPERATION IN RLL [1,7] CONSTRAINT

- Data Rate is Programmable

- SUPPORTS ZONED BIT RECORDING AP-PLICATIONS

- LOW POWER OPERATION (500mW TYPI-CAL @ 5V @ 32Mbits/Sec

- PROVIDES PROGRAMMABILITY THROUGH SERIAL MICROPROCESSOR INTERFACE AND INTERNAL REGISTERS

- Bi-directional access to internal registers of pulse detector, filter, servo demodulator, frequency synthesizer and data separator.

- PROGRAMMABLE POWER DOWN MODES Full power-down mode (5mW max.)

- POWER SUPPLY RANGE 4.3 to 5.5V

#### **DESCRIPTION**

The L6000 is a 5V single chip read channel IC. It contains all the functions needed to implement a high performance read channel including the

pulse detector, programmable active filter, servo demodulator, frequency sinthesizer, and data separator, at data rates up to 32 Mbit/s. A single external resistor sets the reference current for the internal DAC which, in turn, fixes the data rate.

This device is programmed through a serial port and banks of internal registers. It is fully compatible with zoned bit recording applications. External components do not need to be changed when switching between zones. The L6000 is manufactured using an advanced BiCMOS technology.

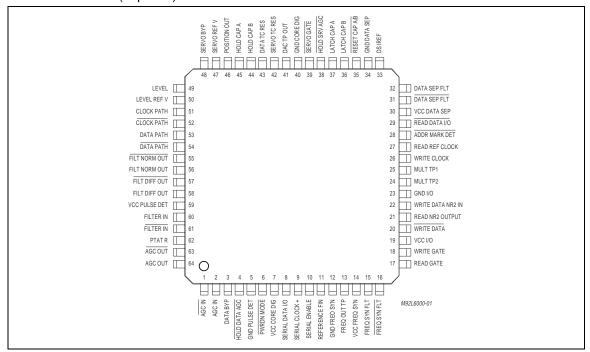

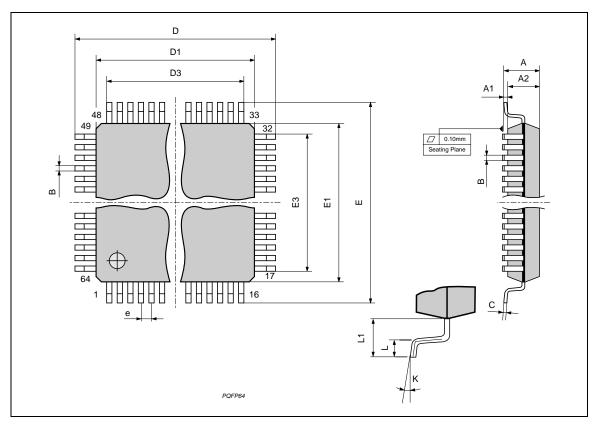

#### PIN CONNECTION (Top view)

August 1993 1/24

This is advanced information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

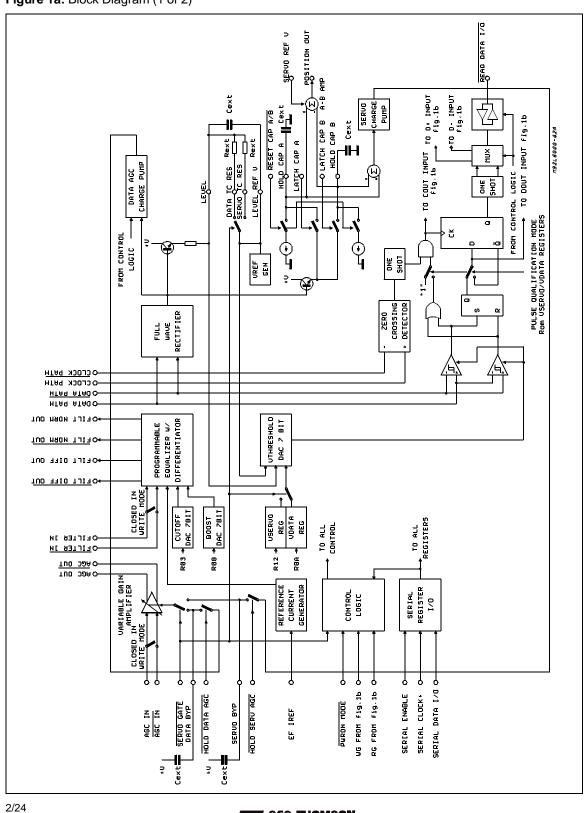

Figure 1a: Block Diagram (1 of 2)

SGS-THOMSON MICROELECTRONICS

READ NRZ OUTPUT READ REF CLOCK ADDR MARK DET URITE DATA UG fig.1a RG fig.1a MULT TP2 171 NUX & DEGLITCH LOGIC CLOCK BUFFER Š DATA SEP UCO ROC DATA SEPARATOR PHASE COMPARATOR DIVIDE BY 2 CHARGE PUMP TJT 932 ATAO O URITE PRECOMP LOGIC AND ONE-SHOT + AOOR NARK • DETECTOR Σ 114 938 A1A0 O ž (1.7) RLL DECODER WP DAC 3 BITS ž R1A 9T TUD 0393 D 4 (1,7) URITE ENCODER DATA SYNCHRON. DIVIDE BY 2 53 50 ADDR MARK GENERATOR SYNTHESIZER PHASE COMPARATOR OFREQ SYN FLT CHARGE PUMP 1/3 CELL DELAY OFREQ SYN FLT DATA SEPARATOR MODE CONTROL LOGIC SYNC UINDOW DIVIDE BY M+1 PLL CONTROL DAC 7 BIT 01010E BY N+1 us RIUARIOUS ROE + B BITS N REG RB4 WRITE CLOCK O-WRT DATA O-NRZ IN D\* fig.18 + 0- fig.18 + COUT fig.18 + URITE GATE ( READ GATE ( DOUT fig.1a REFERENCE OS IREF Z.I

Figure 1b: Block Diagram (2 of 2)

## **ABSOLUTE MAXIMUM RATINGS**

| Symbol | Parameter                         | Value               | Unit |

|--------|-----------------------------------|---------------------|------|

| Vcc    | Positive Supply Voltage           | - 0.5 to 7          | V    |

|        | Voltage Applied to Logic Inputs   | - 0.5 to Vccs + 0.5 | V    |

|        | Voltage Applied to All Other Pins | - 0.5 to Vccs +0.5  | V    |

| Tstg   | Storage Temperature               | - 65 to +150        | °C   |

| Tj     | Junction Temperature              | 130                 | °C   |

# L6000

## **PIN DESCRIPTION**

| Pin#   | Symbol                           | Туре | Description                                                                                                                                                                                                                                                                                                     |

|--------|----------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER  | R SUPPLY                         |      |                                                                                                                                                                                                                                                                                                                 |

| 30     | Vcc DATA SEP                     |      | DATA SEPARATOR: PLL analog 5V supply.                                                                                                                                                                                                                                                                           |

| 14     | Vcc FREQ. SYNTH                  | _    | FREQUENCY SYNTHESIZER: PLL analog 5V supply.                                                                                                                                                                                                                                                                    |

| 7      | Vcc CORE DIG                     | -    | Internal ECL, CMOS logic digital supply.                                                                                                                                                                                                                                                                        |

| 19     | Vcc I/O                          |      | TTL BUFFER I/O 5V SUPPLY.                                                                                                                                                                                                                                                                                       |

| 59     | Vcc PULSE DET                    | -    | Pulse Detector/Servo Demodulator/Filter analog 5V supply.                                                                                                                                                                                                                                                       |

| 34     | GND DATA SEP                     | -    | DATA SEPARATOR: PLL analog 5V ground.                                                                                                                                                                                                                                                                           |

| 12     | GND FREQ SYN                     | -    | FREQUENCY SYNTHESIZERI: PLL analog 5Vground.                                                                                                                                                                                                                                                                    |

| 40     | GND CORE DIG                     | -    | Internal ECL, CMOS logic digital ground.                                                                                                                                                                                                                                                                        |

| 23     | GND I/O                          | _    | TTL Buffer I/O digital ground.                                                                                                                                                                                                                                                                                  |

| 5      | GND PULSE DET                    | -    | Pulse Detector/Servo Demodulator/Filter analog circuit ground.                                                                                                                                                                                                                                                  |

| INPUT  |                                  |      |                                                                                                                                                                                                                                                                                                                 |

| 2, 1   | AGC IN.<br>AGC IN                | _    | AGC AMPLIFIER INPUTS: Differential AGC amplifier input pins.                                                                                                                                                                                                                                                    |

| 53, 54 | <u>DATA PATH,</u><br>DATA PATH   | I    | ANALOG INPUTS FOR DATA PATH: Differential analog inputs to data comparators, full-wave rectifier, and servo demodulator.                                                                                                                                                                                        |

| 51, 52 | <u>CLOCK PATH,</u><br>CLOCK PATH | I    | ANALOG INPUTS FOR CLOCK PATH: Differential analog inputs to the clock comparator.                                                                                                                                                                                                                               |

| 6      | PWRDN MODE                       | 1    | PWRDN MODE CONTROL: TTL compatible power control pin. Assertion shuts down all circuitry, except the serial port. Deassertion and the appropriate bit set in PD register shuts down the selected circuitry. Active low.                                                                                         |

| 4      | HOLD DATA AGC                    | I    | HOLD DATA AGC CONTROL INPUT: TTL compatible power control pin. Assertion disables the AGC charge pump and holds the input AGC amplifier gain. Active low.                                                                                                                                                       |

| 38     | HOLD SRV AGC                     | 1    | HOLD DATA AGC CONTROL INPUT: TTL compatible control pin. Assertion disables the SERVO charge pump. Active low.                                                                                                                                                                                                  |

| 47     | SERVO REF V                      | -    | SERVO REFERENCE .VOLTAGE INPUT: This voltage is set to half of the Vcc PULSE DET voltage                                                                                                                                                                                                                        |

| 37     | LATCH CAP A                      | I    | LATCH CONTROL INPUT: TTL compatible input. Switches channel A into peak acquisition mode when low. Cap voltage doesn't change when high.                                                                                                                                                                        |

| 36     | LATCH CAP B                      | I    | LATCH CONTROL INPUT: TTL compatible input. Switches channel B into peak acquisition mode when low. Cap voltage doesn't change when high.                                                                                                                                                                        |

| 35     | RESET CAP A/B                    | I    | RESET CONTROL INPUT: TTL compatible input. Enables the discharge of channel A & B hold capacitors when asserted. Active low.                                                                                                                                                                                    |

| 60, 61 | <u>FILTER IN,</u><br>FILTER IN   | I    | FILTER SIGNAL INPUTS: Self biased differential input signals to active filter.                                                                                                                                                                                                                                  |

| 11     | REFERENCE FIN                    | 1    | REFERENCE FREQUENCY INPUT: TTL input. Pin REFERENCE FIN has an internal pull up resistor. In the test mode, when frequency synthesizer is bypassed, the REFERENCE FIN frequency required is 3 times the data rate. REFERENCE FIN may be driven by a direct coupled TTL signal.                                  |

| 22     | WRT DATA NRZ<br>IN               | I    | WRITE DATA NRZ INPUT. TTL input. Connected to the READ NRZ OUTPUT pin to form a bidirectional data port. Pin WRT DATA NRZ IN has an internal pull up resistor.                                                                                                                                                  |

| 17     | READ GATE                        | - 1  | READ GATE : See clocks and Modes.                                                                                                                                                                                                                                                                               |

| 26     | WRITE CLOCK                      | 1    | WRITE CLOCK: TTL input Write mode clock. Must be synchronous with the Write Data NRZ input. For short cable delays, WRITE CLOCK may be connected directly to pin READ REF CLOCK. For long cable delays, WRITE CLOCK should be connected to a READ REF CLOCK return line matched to the NRZ data bus line delay. |

| 18     | WRITE GATE                       | - 1  | WRITE GATE: TTL input. Enables the write mode. See Clocks and Modes.                                                                                                                                                                                                                                            |

| 39     | SERVO GATE                       | 1    | SERVO GATE: TTL input. Enables the servo read mode. Active low.                                                                                                                                                                                                                                                 |

## PIN DESCRIPTION (continued)

| Pin#   | Symbol                          | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|--------|---------------------------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OUTPU  |                                 | 71.  | *** <b>F</b> ***                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 64, 63 | AGC OUT,<br>AGC OUT             | 0    | AGC AMPLIFIER OUTPUT: Differential AGC amplifier output pins.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 29     | READ DATA I/O                   | I/O  | READ DATA I/O: Bi-directional TTL pin. Output is active in the servo mode or when both READ GATE and WRITE GATE are deasserted. In test mode, this is a TTL input used to drive the data separator. The TTL input is enabled by setting RDI in the control register CB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 46     | POSITION OUT                    | 0    | POSITION ERROR SIGNAL: A Position error signal of A minus B output which is referenced to SERVO REF V.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 56, 55 | FILT NORM OUT,<br>FILT NORM OUT | 0    | FILTER DIFFERENTIAL NORMAL OUTPUTS: Low pass & boosted filter output signals. Must be AC coupled to the next stage nominally DATA PATH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 58, 57 | FILT DIFF OUT,<br>FILT DIFF OUT | 0    | FILTER DIFFERENTIAL DIFFERENTIADED OUTPUTS: Differentiated filter outputs should be AC coupled to the next stage nominally CLOCK PATH.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 28     | ADDR MARK DET                   | 0    | ADDRESS MARK DETECT: Tristate output pin with TTL output levels. It is in its high impedance state when WRITE GATE is asserted. When READ GATE is asserted and the register bit is set for soft sector, an address mark search is initiated in the soft sector operation. This output is latched low (true) when an address mark has been detected. Deasserting pin READ GATE deasserts pin ADDR MARK DET.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 25     | MULT TP1                        | 0    | MULTIPLEXED TEST POINT OUTPUT: An open emitter ECL output test point. The test point output is enabled by Setting ED in the control register CB. The controlling signal is PD_TEST in the control register CA. When PD_TEST is low, the test point output is the delayed read data DRD. The positive edges of this signal indicate the data bit position. The positive edges of the DRD and VCOREF outputs can be used to estimate window centering. The time jitter of DRD's positive edge is an indication of media bit jitter. When PD_TEST is high the test point out is the comparator of the pulse qualifier. The positive edge indicates that the input signal has exceeded the positive threshold while a negative edge indicates that the input signal has gone below the negative threshold. Two external resistors are required to use this pin. They should be removed during normal operation to reduce power dissipation. |

| 21     | READ NRZ<br>OUTPUT              | 0    | NRZ OUTPUT DATA: Tristate ouput pin with TTL output levels. It is in its high impedance state when READ GATE is deasserted. Read data output when READ GATE is asserted.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 27     | READ REF CLOCK                  | 0    | READ REFERENCE CLOCK: TTL output. A multiplexed clock source used by the controller, see Clocks and Modes. During a mode change, no glitches are generated and no more than one lost clock pulse will occur. READ REF CLOCK remains Fout/3 after READ GATE is asserted, until after synchronized bits are detected.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 24     | MULT TP2                        | 0    | MULTIPLEXED TEST POINT OUTPUT: An open emitter ECL output test point. This test point output is enabled by using the same control bit enabling the MULT TP1 output. When the controlling signal, PD_TEST is desserted, the test point output is the VCO reference input (VCOREF) to the phase detector. The positive edges are phase locked to Delayed Read Data (DRD). The negative edges of this open emitter output signal indicate the edges of the decode window. When PD_TEST is high, the test point output represents the state of the clock comparator in the pulse qualifier. The signal transitions indicate zero crossing of the differentiated signal from the electronic filter. Two external resistor are required to use this pin. They should be removed during normal operation to reduce power dissipation.                                                                                                          |

| 20     | WRITE DATA                      | 0    | WRITE DATA: TTL output. Encoded write data output. The data is automatically resynchronized (independent of the delay between READ REF CLOCK and WRITE CLOCK) to the reference clock FSout. Falling edge of the WRITE DATA is the data edge.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

| 13     | FREQ OUT TP                     | 0    | REFERENCE FREQUENCY OUTPUT: An open emitter ECL output test point. The frequency is the frequency synthesizer output frequency. This output is enabled by control register CA. Two external resistors are required to use this pin. They should be removed during normal operation to reduce power dissipation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

## PIN DESCRIPTION (continued)

| Pin#   | Symbol                        | Туре | Description                                                                                                                                                                                                                                                                                                                                                                               |

|--------|-------------------------------|------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| ANALC  | )G                            |      |                                                                                                                                                                                                                                                                                                                                                                                           |

| 50     | LEVEL REF V                   | 0    | REFERENCE VOLTAGE: Reference voltage output for LEVEL. LEVEL REF V is derived by referencing VRG (an internal signal) to Vcc PULSE DET.                                                                                                                                                                                                                                                   |

| 62     | EF IREF                       | ı    | REFERENCE RESISTOR INPUT: An external 1% resistor (RX) is connected from this pin to ground to establish a precise reference current for the filter.                                                                                                                                                                                                                                      |

| 3      | DATA BYP                      | -    | AGC INTEGRATING CAPACITOR: Connected between DATA BYP and Vcc PULSE DET. This pin is used when data read mode.                                                                                                                                                                                                                                                                            |

| 48     | SERVO BYP                     | -    | AGC INTEGRATING CAPACITOR FOR SERVO: Connected between SERVO BYP and Vcc PULSE DET. This pin is used when in servo read mode                                                                                                                                                                                                                                                              |

| 45     | HOLD CAP A                    | _    | PEAK HOLDING CAPACITOR A: Tied from this pin to GND PULSE DET.                                                                                                                                                                                                                                                                                                                            |

| 44     | HOLD CAP B                    | _    | PEAK HOLDING CAPACITOR B: Tied from this pin to GND PULSE DET.                                                                                                                                                                                                                                                                                                                            |

| 49     | LEVEL                         | 0    | HYSTERESIS LEVEL: An NPN emitter output that provides a full-wave rectified signal from LEVEL to LEVEL REF V to set the hysteresis threshold time constant in conjunction with SERVO TC RES and DATA TC RES. This level used in VTHRESHOLD DAC.                                                                                                                                           |

| 33     | DS IREF                       | I    | REFERENCE RESISTOR INPUT: An external 1% resistor (RR) is connected to this pin to establish a precise internal reference current for the data separator and Frequency Synthesizer.                                                                                                                                                                                                       |

| 42     | SERVO TC RES                  | I    | SERVO TIME CONSTANT RESISTOR INPUT: An external resistor is connected from this pin to LEVEL to establish the hysteresis threshold time constant when not in Servo mode.                                                                                                                                                                                                                  |

| 15, 16 | FREQ SYN FLT,<br>FREQ SYN FLT | -    | PLL FILTER: The two connection points for the frequency synthesizer PLL differential filter components.                                                                                                                                                                                                                                                                                   |

| 32, 31 | DATA SEP FLT,<br>DATA SEP FLT | -    | PLL FILTER: THE Two connection points for the data separatorPLL differential filter components.                                                                                                                                                                                                                                                                                           |

| 41     | DAC TP OUT                    | 0    | DAC OUTPUT: A test point for some of the on-chip DACs. The output of an internal DAC is selected by the values of TDAC1 (MSB) and TDACO (LSB) in the WS register. The selected DAc output and its corresponding select bits are as follows: FC_DAC (00), VTH_DAC (0 1), WS_DAC (1 0), and WP_DAC (1 1). When not using the DAC TP OUT pin, the preferred setting is to select the FC_DAC. |

| SERIAL | PORT                          |      |                                                                                                                                                                                                                                                                                                                                                                                           |

| 10     | SERIAL ENABLE                 | I    | SERIAL DATA ENABLE: Active high input pin to enable the serial port CMOS input levels.                                                                                                                                                                                                                                                                                                    |

| 8      | SERIAL DATA I/O               | I/O  | SERIAL DATA: Input/Output pin for serial data; 8 instruction/address bits are sent first followed by 8 data bits. CMOS Input/Output levels.                                                                                                                                                                                                                                               |

| 9      | SERIAL CLOCK+                 | I    | SERIAL DATA CLOCK: Positive edge triggered clock input for the serial data CMOS input levels. The pin has an internal pull-up resistor.                                                                                                                                                                                                                                                   |

#### SYSTEM DESCRIPTION

#### **Pulse Detector Section**

Fast attack/decay modes for rapid AGC recovery. Dual rate charge pump for fast transient recovery. Low Drift AGC hold circuitry supports programmable gain, non-AGC operation. Temperature compensated, exponential control AGC. Shorted input switch for transient recovery, during Power down & Write to read & Idle mode transitions. Wide Bandwidth, high precision full-wave rectifier. Dual mode pulse qualification circuitry allows either independent positive and negative threshold qualification to suppress error propagation or hysteresis comparison wich implements alternating polarities. Differential qualifier comparator. TTL READ DATA I/O signal output available during servo and idle modes. Timing for shorted inputs and fast decay functions set internally. 0.5 ns max. pulse pairing with sine wave input.

#### **Embedded Servo Demodulator Section**

Dual servo burst (A/B) capture with Position Error Signal Output. Servo AGC mode which holds sum of A and B bursts constant. Provision for on-chip switching of the hysteresis threshold time constant.

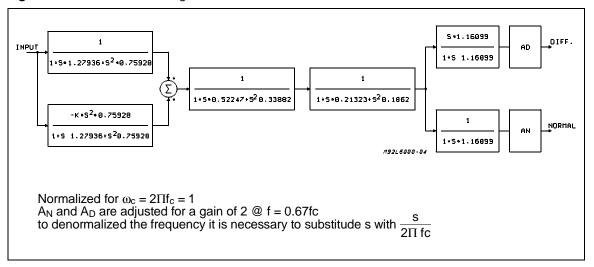

#### **Programmable Filter Section**

Programmable filter cutoff frequency (fc = 6 to 18 MHz). Programmable pulse slimming equalization (0 to 9 dB Boost at the filter cutoff frequency). Matched path timing normal and differential low-pass outputs. Differential filter input and outputs for noise rejection  $\pm 10\%$  cutoff frequency accuracy.  $\pm 2\%$  maximum group delay variation in the passband maintained over the cutoff frequency tuning range (fc=6 to 18 MHz). Total harmonic distortion less than 1.5 %. No external filter components required. Shorted input switch for transient recovery, during Power down & Write to Read & Idle mode transitions.

# Frequency Synthesizer and Data Separator Section

1% frequency resolution. Data synchronizer and 1.7 RLL ENDEC. Fast acquisition phase lock loop with zero phase restart both to data and synthesizer. Fully integrated data separator. No external delay lines or active devices required. No external active PLL components required. Active window centering symmetry control via serial port. Window shift control ±30%. Includes delayed read data and VCO clock monitor tests points. Programmable write precompensation. Hard and soft sector operation.

#### THERMAL DATA

| Symbol                 | Parameter                           | Value | Unit |

|------------------------|-------------------------------------|-------|------|

| Rth <sub>j-amb</sub>   | Thermal Resistance Junction-Ambient | 100   | °C/W |

| R <sub>th j-case</sub> | Thermal Resistance Junction-Case    | 20    | °C/W |

#### RECOMMENDED OPERATING CONDITIONS

| Vccn             | Supply Voltage                | 4.3 to 5.5 | V  |

|------------------|-------------------------------|------------|----|

| T <sub>amb</sub> | Operating Ambient temperature | 0 to 70    | °C |

| Ti               | Junction Temperature          | 25 to 125  | °C |

**ELECTRICAL CHARACTERISTICS:**  $V_{CCn}$  = 5V + 10% - 14%,  $T_{amb}$  = 0 to 70 °C,  $T_j$  = 25 to 125°C, unless otherwise specified.

| Symbol          | Parameter                     | Test Condition                            | Min.         | Тур. | Max.                       | Unit |

|-----------------|-------------------------------|-------------------------------------------|--------------|------|----------------------------|------|

| POWER SU        | IPPLY CURRENT AND POWER D     | ISSIPATION                                |              |      |                            |      |

| Icc             | Power Supply Current          | Outputs and test point pins open;         | -            | 100  | 120                        | mA   |

| Pd              | Power Dissipation             | Tamb = 27°C, 32Mbits/sec                  | ı            | 500  | 660                        | mW   |

| DIGITAL IN      | PUTS AND OUTPUTS              |                                           |              |      |                            |      |

| V <sub>IL</sub> | Low Level Input Voltage       |                                           | - 0.3        |      | 0.8                        | V    |

| V <sub>IH</sub> | High Level Input Voltage      |                                           | 2.0          |      | V <sub>CC</sub><br>I/O+0.3 | V    |

| I <sub>IL</sub> | Low Level Input Current       | V <sub>IL</sub> = 0.4V                    | _            |      | - 0.4                      | mA   |

| I <sub>IH</sub> | Low Level Input Current       | V <sub>IH</sub> = 2.4V                    | _            |      | 100                        | μΑ   |

| V <sub>OL</sub> | Low Level Output Voltage      | $I_{OL} = 4.0 \text{mA}$                  | -            |      | 0.5                        | V    |

| Vон             | High Level Output Voltage     | I <sub>OH</sub> = -400μA                  | 2.4          |      | _                          | V    |

| CMOS INPL       | JTS: SERIAL ENABLE, SERIAL DA | ATA AND SERIAL CLOCK                      |              |      |                            |      |

| $V_{IL}$        | Low level Input Voltage       | 5V and 25°C                               | ı            |      | 0.5                        | V    |

| $V_{IH}$        | High Level Input Voltage      |                                           | 4.5          |      | _                          | V    |

| t <sub>r</sub>  | Rise Time                     | 4.3V, 70°C and C = 5pF                    | ı            |      | 5.0                        | ns   |

| t <sub>f</sub>  | Fall Time                     |                                           | ı            |      | 4.5                        | ns   |

| CMOS OUT        | PUTS: SERIAL DATA I/O         |                                           |              |      |                            |      |

| V <sub>OL</sub> | Low Level Output Voltage      | 5V and 25°C; I <sub>OL</sub> = 4.07mA     | ı            |      | 0.5                        | V    |

| V <sub>OH</sub> | High Level Output Voltage     | 5V and 25°C; I <sub>OH</sub> = +4.83mA    | 4.5          |      | _                          | V    |

| t <sub>r</sub>  | Rise Time                     | 4.3V, 70°C and C = 15pF                   | ı            |      | 5.5                        | ns   |

| t <sub>f</sub>  | Fall Time                     |                                           | ı            |      | 5.0                        | ns   |

| TEST POIN       | T OUTPUT LEVELS               |                                           |              |      |                            |      |

| V <sub>IL</sub> | Test Point High Level Output  | 261Ω to Vcc DATA SEP                      | Vcc<br>DATA  |      | -                          | V    |

|                 | (MTP1, MTP2, FOUT)            | 402Ω to GND DATA SEP, Vcc DATA SEP = $5V$ | SEP-<br>1.02 |      |                            |      |

| V <sub>IH</sub> | Test Point Low Level Output   | 261Ω to Vcc DATA SEP                      | _            |      | Vcc<br>DATA                | V    |

|                 | (MTP1, MTP2, FOUT)            | 402Ω to GND DATA SEP, Vcc DATA SEP = $5V$ |              |      | SEP-<br>1.62               |      |

## PULSE DETECTOR AND SERVO DEMODULATOR CHARACTERISTICS

| Symbol                                                                                                                                                                                                                                                                                                                                                                                                                                             | Parameter         | Test Condition                                                                         | Min.  | Тур. | Max.  | Unit |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------|----------------------------------------------------------------------------------------|-------|------|-------|------|--|

| AGC Amplifier Section The input signals are AC coupled to AGC IN and AGC IN. AGC OUT and AGC OUT are AC coupled to FILTER IN and FILTER IN. FILT NORM OUT and FILT NORM OUT are AC coupled to DATA PATH and DATA PATH.  Integrating capacitor Ca = 1000pF is connected between DATA BYP and Vcc PULSE DET. Unless otherwise specified, the output is measured differentially at AGC OUT and AGC OUT, Fin = 4MHz, and the filter boost at FB = 0dB. |                   |                                                                                        |       |      |       |      |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Input range       | Filter Boost at FC = 0dB<br>(bench test condition = 2.2 to<br>18MHz)                   | 22    | -    | 240   | mVpp |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Input range       | Filter Boost at FB = 9dB<br>Fin = FC = 18MHz<br>(bench test condition = 6 to<br>18MHz) | 14    | -    | 100   | mVpp |  |

| DATA PATH/<br>DATA PATH                                                                                                                                                                                                                                                                                                                                                                                                                            | Voltage           | AGC IN-AGC IN = 0.1Vpp                                                                 | 0.945 | 1.05 | 1.155 | Vpp  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Voltage Variation | 22mV < AGC IN = AGC IN < 240mV                                                         | -8.0  | _    | +8.0  | %    |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                    | Gain Range        |                                                                                        | 1.9   | _    | 22    | V/V  |  |

SGS-THOMSON MICROELECTRONICS

## PULSE DETECTOR AND SERVO DEMODULATOR CHARACTERISTICS

| Symbol                      | Parameter                                                                     | Test Condition                                                                 | Min.                         | Тур.        | Max.                        | Unit     |

|-----------------------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------------------|------------------------------|-------------|-----------------------------|----------|

|                             | Gain Sensititivity with respect to DATA BYP or SERVO BYPS pin voltage changes |                                                                                | 27                           | 28          |                             | dB/V     |

| AGC OUT/<br>AGC OUT         | THD                                                                           | AGCOUT - $\overline{AGCOUT} = 0.75Vpp$                                         | 40                           | -           | -                           | dB       |

|                             | Differential Input Impedance                                                  | WG = low                                                                       | 4.7                          | 6           | 8.4                         | ΚΩ       |

|                             | Single Ended Input Impedance                                                  | WG = low<br>WG = High or when IN Low - Z<br>mode                               | 2.5                          | 3.5<br>0.65 | 4.5<br>0.8                  | ΚΩ<br>ΚΩ |

| VOO                         | Output Offset Voltage                                                         | Filter not connected                                                           | - 200                        | _           | +200                        | mV       |

| en                          | Input Noise Voltage                                                           | AGC OUT, Rs = $0\Omega$ , gain = 22                                            | -                            | 10          | 15                          | nV/√Hz   |

| BW                          | Bandwidth                                                                     | gain = 22 (1)                                                                  | 50                           | _           | _                           | MHz      |

| AGC OUT/<br>AGC OUT         | Single ended output resistance                                                | I <sub>O</sub> = 0                                                             |                              | 140         | 180                         | Ω        |

| PSRR                        | Power Supply Rejection Ratio                                                  | gain = 22, Fin = 5MHz                                                          | 45                           |             |                             | dB       |

| CMRR                        | Common Mode Rejection Ratio                                                   |                                                                                | 40                           | _           | _                           | dB       |

|                             | Gain Decay Time                                                               | AGC IN-AGC IN = 240mVpp to<br>120mVpp,<br>AGC OUT-AGC OUT = 0.9<br>Final Value | _                            | -           | 53                          | μs       |

|                             | Gain Attack Time                                                              | AGC IN-AGC IN = 120mVpp to<br>240mVpp,<br>AGC OUT-AGC OUT = 1.1<br>Final Value | -                            | -           | 2                           | μs       |

| AGC Contro<br>The input sig | ol Section<br>gnal are AC coupled to DATA PATH                                | H and $\overline{DATAPATH}$ , C = 1000pF.                                      |                              |             |                             |          |

| DATA PATH/<br>DATA PATH     | Signal Input range                                                            | (bench test only)                                                              | _                            | 1           | 1.5                         | Vpp      |

| ld                          | Discharge Current                                                             |                                                                                | 2.8                          | 4           | 5.2                         | μΑ       |

| ldf                         | Fast Discharge                                                                | During Fast Decay mode<br>Current                                              | 20xld<br>-30%                | 20xld       | 20xld<br>+30%               | μΑ       |

| lch                         | Charge Pump Attack Current                                                    | DATA PATH-DATA PATH = 1.15Vpp                                                  | 0.126                        | 0.18        | 0.234                       | μΑ       |

| Ichf                        | Charge Pump Fast Attack<br>Current                                            | DATA PATH-DATA PATH = 1.45V                                                    | 7xlch<br>-30%                | 7xlch       | 7xlch<br>+30%               | μΑ       |

|                             | DATA BYP Pin Leakage Current                                                  | WG = high                                                                      | -0.1                         |             | +0.1                        | μА       |

| LEVEL REF V                 | Reference Voltage                                                             |                                                                                | Vcc<br>PULSE<br>DET-<br>2.47 | _           | Vcc<br>PULSE<br>DET-<br>2.0 | V        |

|                             | LEVEL REF V Output Drive                                                      |                                                                                | -0.75                        | _           | 0.75                        | mA       |

|                             | Duration of shorted input and Fast Decay modes                                | (*)                                                                            | _                            | 1           | _                           | μs       |

|                             | Level Output Gain                                                             | DATA PATH-DATA PATH = 0.5 to 1Vpp                                              | 0.60                         | 0.67        | 0.75                        | V/Vpp    |

|                             | Level Output Bandwidth                                                        | f <sub>IN</sub> = 11MHz                                                        | _                            | _           | 2                           | dB (2)   |

|                             | Level Offset Voltage                                                          | Output - LEVEL REF V $(I_L = 40\mu A)$                                         | -40                          | ı           | +40                         | mV (2)   |

<sup>(\*)</sup> Guaranted by design.

(1) For correlation automatic test is performed at -3.8dB.

(2) Test limits under evaluation.

## PULSE DETECTOR AND SERVO DEMODULATOR CHARACTERISTICS (continued)

| Symbol                      | Parameter                                          | Test Condition                                                                                                                                  | Min.         | Тур.   | Max.         | Unit         |

|-----------------------------|----------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--------|--------------|--------------|

|                             | arator Section<br>ignals are AC coupled to DATA PA | TH and DATA DATH                                                                                                                                |              |        |              |              |

| DATA PATH/                  | i '                                                |                                                                                                                                                 |              | 4      | 1.5          | Van          |

| DATA PATH                   | Signal Range                                       |                                                                                                                                                 | _            | 1      | 1.5          | Vpp          |

|                             | Differential Input resistance                      |                                                                                                                                                 | 8            | _      | 14           | KΩ           |

|                             | Differential Input capacitance                     |                                                                                                                                                 | _            | _      | 5            | pF           |

|                             | Comparator Offset Voltage                          | (*)                                                                                                                                             | _            | _      | ±4           | mV           |

|                             | Threshold Voltage Hysteresis                       | (*)                                                                                                                                             | _            | 20Kth  | _            | %            |

| Kth                         | Threshold Voltage Gain                             | 0.3 ≤ ( LEVEL-LEVEL REF V) ≤ 0.75, Kth = VTHDAC*0.651/127, 38 < VTHDAC < 125, Vthresh = KTH*(LEVEL-LEVEL REF V), also, %hyst = VTHDAC*97.6%/127 | Kth-9%       | Kth    | Kth+9%       | V/V          |

|                             | Minimum Threshold Voltage                          | LEVEL-LEVEL REF V ≤ 0.1V,<br>Vthmin = VTHDAC*0.099/127<br>(*)                                                                                   | -            | Vthmin | -            | V            |

| Clocking So<br>(The input s | ection<br>ignals are AC coupled to CLOCK F         | PATH and CLOCKPATH)                                                                                                                             |              |        |              |              |

|                             | CLOCK PATH-CLOCK PATH<br>Signal Range              |                                                                                                                                                 | _            | -      | 1.5          | Vpp          |

|                             | Comparator Offset Voltage                          | (*)                                                                                                                                             | _            | ı      | ±4           | mV           |

|                             | Differential Input Resistance                      |                                                                                                                                                 | 8            | _      | 14           | ΚΩ           |

|                             | Differential Input Capacitance                     |                                                                                                                                                 | _            | 1      | 5            | pF           |

|                             | Pulse Paring                                       | Vs = 1Vpp, F = 4MHz                                                                                                                             | _            | _      | 0.5          | ns           |

|                             | Prpagation Delay to READ DATA I/O                  | Vs = 20mVpp sq. wave                                                                                                                            | 4            | 12     | 20           | ns           |

| Servo Secti                 | ion                                                |                                                                                                                                                 |              |        | •            |              |

|                             | SERVO REF V Voltage Range                          | 2.15V ≤ SERVO REF V ≤ 2.75V                                                                                                                     | 2.15         | 2.50   | 2.75         | V            |

|                             | SERVO REF V Input Bias<br>Current                  |                                                                                                                                                 | -1           | 0.2    | 1            | μА           |

|                             | Voltage Gain, SERVO REF V to POSITION OUT          | HOLD CAP A-HOLD CAP B  ≤ 0.4V                                                                                                                   | 0.98         | 1.0    | 1.02         | v/v          |

|                             | POSITION OUT Pin Offset<br>Voltage                 | HOLD CAP A-HOLD CAP B = 0V, SERVO REF V = 2.50V                                                                                                 | _            | 0      | ±12          | mV           |

|                             | POSITION OUT Pin High                              | HOLD CAP A-HOLD CAP B = +1.8V                                                                                                                   | Vcc<br>PULSE | _      | Vcc<br>PULSE | V            |

|                             | Level Output Voltage                               | SERVO REF V = 2.50V,<br>Isource = 0.5mA                                                                                                         | DET-<br>1.5  |        | DET-<br>0.3  |              |

|                             | POSITION OUT Pin Low                               | HOLD CAP A-HOLD CAP B = -1.8V                                                                                                                   | GND<br>PULSE | -      | GND<br>PULSE | V            |

|                             | Level Output Voltage                               | SERVO REF V = 2.50V Isink = 0.5mA                                                                                                               | DET<br>+0.3  |        | DET<br>+1.5  |              |

| RO                          | POSITION OUT Pin Output<br>Resistance              | VNG+1.5V ≤ POSITION<br>OUT ≤ VPG-1.5V                                                                                                           | _            | П      | 50           | Ω            |

|                             | POSITION OUT GAIN                                  | (POSITION OUT-SERVO REF<br>V)/Vpp                                                                                                               |              | 1.8    |              | V/Vpp<br>(2) |

|                             | HOLD CAP A/B Charge Current                        | Absolute Value                                                                                                                                  | 4            | _      | -            | mA           |

<sup>(\*)</sup> Guaranted by design.

(2) Test limits under evaluation.

# PULSE DETECTOR AND SERVO DEMODULATOR CHARACTERISTICS (continued)

| Symbol | Parameter                                 | Test Condition                                                               | Min. | Тур. | Max. | Unit   |

|--------|-------------------------------------------|------------------------------------------------------------------------------|------|------|------|--------|

| ld     | HOLD CAP A/B Disch. Current               | Absolute value                                                               | 0.8  | 1.5  | 2.2  | mA     |

| ILKG   | HOLD CAP A/B Leakage Cur.                 |                                                                              | -    | _    | ±0.5 | μА     |

| ILKG   | SERVO BYP Pin Leakage Cur.                | HOLDS = Low                                                                  | _    | _    | ±0.2 | μΑ     |

| K4     | SERVO BYP Pin<br>Charge/Discharge Current |                                                                              | 450  | 640  | 880  | μΑ/Vpp |

| K5     |                                           | Ibyps = K4 · [K5 -<br>DATAPATH <sub>App</sub> –<br>DATAPATH <sub>Bpp</sub> ] | 0.70 | 1.00 | 1.30 | V/V    |

|        | Maximum SERVO BYP Pin<br>Charge Current   |                                                                              | 190  | 300  | 490  | μΑ     |

| Tper   | READ DATA I/O Output Pulse<br>Period      | CL ≤ 15pF                                                                    | 50   | _    | _    | ns     |

| T1     | READ DATA I/O Output Pulse<br>Low Time    | RDIO ≤ 0.8V                                                                  | 9    | 23   | 33   | ns     |

| Th     | READ DATA I/O Output Pulse<br>High Time   | RDIO ≥ 0.8V                                                                  | 29   | _    | _    | ns     |

| Tf     | READ DATA I/O Output Pulse Fail Time      | CL ≤ 15pF, 2.0V to 0.8V                                                      | _    | _    | 5    | ns     |

| Tr     | READ DATA I/O Output Pulse<br>Rise Time   | CL ≤ 15pF, 0.8V to 2.0V                                                      | _    | _    | 8    | ns     |

## PROGRAMMABLE FILTER CHARACTERISTICS

| Symbol | Parameter                                                                                                                                                                                  | Test Condition                                                                   | Min.           | Тур. | Max.           | Unit     |  |  |

|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------|----------------|------|----------------|----------|--|--|

|        | <b>Test Conditions:</b> Vccn = 5V + 10% - 14%, $T_{amb} = 0$ to 70°C, $T_j = 25$ to 125°C, unless otherwise specified. The input signals are AC coupled to FILTER and FILTER IN. C ≥ 22nF. |                                                                                  |                |      |                |          |  |  |

| FC     | Filter Cutoff Frequency, f at -3dB point                                                                                                                                                   | FC = 0.141732MHz *FCDAC,<br>42 ≤ FCDAC ≤ 127, FCDAC is<br>value of frequency DAC | 6              | -    | 18             | MHz      |  |  |

| FCA    | Filter fc Accuracy                                                                                                                                                                         | FCDAC = 127                                                                      | <b>– 10</b>    | _    | +10            | %        |  |  |

| AN     | FILT NORM OUT Differential Gain                                                                                                                                                            | f = 0.67FC, FBDAC = 0                                                            | 1.6            | 2    | 2.4            | V/V      |  |  |

| AD     | FILT DIFF OUT Differential Gain                                                                                                                                                            |                                                                                  | 0.9AN          | ı    | 1.1AN          | V/V      |  |  |

| FB     | Frequency Boost @ FC                                                                                                                                                                       | FB (dB) = 20log [0.0273 (FBDAC)+1], $0 \le FBDAC \le 127$ FBDAC = 127            | _              | 13   | _              | dB       |  |  |

|        |                                                                                                                                                                                            | @6dB; FBDAC = 36<br>@13dB; FBDAC = 127                                           | - 0.75<br>-2.0 | -    | + 0.75<br>+2.0 | dB<br>dB |  |  |

| TGDO   | Group Delay Variation without Boost                                                                                                                                                        | FC = 6MHz to 18MHz,<br>f = 0.2FC to FC FBDAC = 0                                 | -3             | -    | + 3            | %<br>(2) |  |  |

|        |                                                                                                                                                                                            | FC = 6MHz to 18MHz,<br>FBDAC = 0, f = FC to 1.75FC                               | - 4            | ı    | + 4            | %<br>(2) |  |  |

| TGDB   | Group Delay Variation with<br>Maximum Boost                                                                                                                                                | FC = 6 to 18MHz,<br>f = 0.2 FC to FC, FBDAC = 127                                | -3             | ı    | +3             | %<br>(2) |  |  |

|        |                                                                                                                                                                                            | FC = 6MHz to 18MHz,<br>FBDAC = 127, f = FC to 1.75FC                             | - 4            | ı    | +4             | %<br>(2) |  |  |

| VIF    | Filter Differential Input Dynamic Range                                                                                                                                                    | THD = 1% max, f = 0.67FC,<br>FBDAC = 0                                           | 0.5            | ĺ    | -              | Vpp      |  |  |

|        |                                                                                                                                                                                            | THD = $2\%$ max, f = $0.67FC$ ,<br>FBDAC = $0$                                   | 0.75           | -    |                | Vpp      |  |  |

| RIN    | Filter Diff. Input resistance                                                                                                                                                              |                                                                                  | 5.0            |      | _              | ΚΩ       |  |  |

| RIZ    | Filter Diff. Input Resistance with Shorted Inputs                                                                                                                                          | Low – Z mode                                                                     | 100            | 300  | 500            | Ω        |  |  |

| CIN    | Filter Diff. Input Capacitance                                                                                                                                                             |                                                                                  | _              | _    | 7              | pF       |  |  |

<sup>(2)</sup> Test limits under evaluation.

## PROGRAMMABLE FILTER CHARACTERISTICS(continued)

| Symbol | Parameter                                     | Test Condition                                                 | Min. | Тур. | Max. | Unit  |

|--------|-----------------------------------------------|----------------------------------------------------------------|------|------|------|-------|

| EOUT   | Output Noise Voltage<br>Differentiated Output | BW = $100MHz$ , Rs = $50\Omega$<br>FC = $18MHz$ , DACS = $0$   | -    | 2    | 7    | mVrms |

|        | Output Noise Voltage Normal<br>Output         |                                                                | -    | 1.2  | 5    | mVrms |

|        | Output Noise Voltage<br>Differentiated Output | BW = $100MHz$ , Rs = $50\Omega$<br>FC = $18MHz$ , DACS = $127$ | -    | 4.6  | 7    | mVrms |

|        | Output Noise Voltage Normal<br>Output         |                                                                |      | 2    | 5    | mVrms |

| 10-    | Filter Output Sink Current                    |                                                                | 0.5  | _    | _    | mA    |

| IO+    | Filter Output Source Current                  |                                                                | 2.0  | _    | _    | mA    |

| RO     | Filter Output resistance Single Ended         |                                                                | _    | _    | 200  | Ω     |

Note: FBDAC is value of boost DAC (i.e., no boost)

| Filter Control Characteristics (RX = $12K\Omega$ ) |                                         |                              |   |     |   |   |  |  |  |

|----------------------------------------------------|-----------------------------------------|------------------------------|---|-----|---|---|--|--|--|

| VRX                                                | Reference Current Set Output<br>Voltage | T <sub>amb</sub> = 27°C (**) | I | 1.5 | I | V |  |  |  |

## FREQUENCY SYNTHESIZER CHARACTERISTICS (RR = $39K\Omega$ )

| FIN       | Input Frequency                |                                                               | 8                  | 20                 | MHz       |

|-----------|--------------------------------|---------------------------------------------------------------|--------------------|--------------------|-----------|

| FOUT      | Output Frequency               |                                                               | -                  | 96                 | MHz       |

| JFO       | FOUT jitter                    | TO = 1/FO; Fout = 30MHz                                       | _                  | ±400               | ps(pk)    |

|           | M Divide Number                |                                                               | 80                 | 255                | _         |

|           | N Divide Number                |                                                               | 25                 | 127                | _         |

| TVCO      | VCO Center Frequency Period    | TO = $(9.65 + 0.843 \times DR)^{-1}$<br>FLTR1-FLTR1 = 0 (***) | 0.9TO              | 1.1TO              | ns        |

|           | VCO Frequency Dynamic<br>Range | -1.5 ≤ FLTR1-FLTR1 ≤ +1.5,<br>Fout = 54.0MHz (***)            | 25                 | ±45                | %         |

| KVCO      | VCO Control Gain               | $ω = 2π/TVCO$ $-1.5 \le FLTR1-FLTR1 \le +1.5$                 | 0.14ω <sub>o</sub> | 0.26ω <sub>0</sub> | rad/(V-s) |

| KD        | Phase Detector Gain            | $KD = 0.7 + 0.43 \times DR$ (***)                             | 0.83KD             | 1.17KD             | μA/rad    |

|           | KVCO x KD Product Accuracy     |                                                               | - 28               | + 28               | %         |

| Reference | Clock Characteristics:         |                                                               |                    |                    |           |

|           | Reference Clock Low Time       |                                                               | 20                 | _                  | ns        |

|           | Reference Clock High Time      |                                                               | 20                 | _                  | ns        |

# **DATA SEPARATOR DYNAMIC CHARACTERISTICS AND TIMING** (Unless otherwise specified, recommended operating conditions apply.)

| Real Mode |                               |                           |      |     |    |

|-----------|-------------------------------|---------------------------|------|-----|----|

| TRRC      | Read Clock Rise Time          | 0.8V to 2.0V, CL ≤ 15pF   | -    | 8   | ns |

| TFRC      | Read Clock Fall time          | 2.0V to 0.8V, CL ≤ 15pF   | _    | 5   | ns |

|           | RRC Duty Cycle                | DR = 32Mbit/s             | 43   | 57  | %  |