## **FAN5235**

# **System Electronics Regulator for Mobile PCs**

#### **Features**

- · Synchronous rectification

- ±1% precision internal reference

- >90% efficiency

- · Input and output voltage feedback

- 5.4V to 24V input voltage range

- Internally set 300kHz ±15% oscillator

- 5V and 3.3V Main outputs switch out of phase

- 5V-ALWAYS and 3.3V-ALWAYS outputs

- · Adjustable boost converter for 12V

- · Boost converter slaved to 5V Main

- Input UVLO

- Outputs OVP of Buck Converters

- Precision current limit option for 5V, 3.3V Main

- · Power Good Voltage Monitor

## **Applications**

- · Notebook PCs and PDAs

- · Hand-held portable instruments

### **Description**

The FAN5235 is a high efficiency and high precision DC/DC controller for notebook converters. Utilization of both input and output voltage feedback in a current-mode control allows for fast and stable loop response over a wide range of input and output voltage variations. The two main regulators switch out of phase to minimize input ripple current.

Current sense based on MOSFET Rdson gives maximum efficiency, while also permitting use of a sense resistor for high accuracy. An externally adjustable boost converter can be set to generate 12V.

The FAN5235 is available in a 24-pin QSOP package, and in a 24-pin TSSOP package.

## **Typical Application**

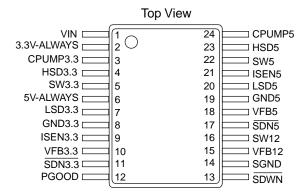

## **Pin Assignments**

## **Pin Description**

| Pin Name    | Pin Number | Pin Function Description                                                                                                                                              |

|-------------|------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VIN         | 1          | Input power.                                                                                                                                                          |

| 3.3V-ALWAYS | 2          | <b>3.3V Always on linear regulator.</b> Load current on pins 2 and 6 must not exceed 50mA total.                                                                      |

| CPUMP3.3    | 3          | <b>Charge Pump 3.3V.</b> High side Gate drive voltage for 3.3V. This pin is to be connected to SW3.3 through a 100nF cap. and to 5V-ALWAYS through a diode            |

| HSD3.3      | 4          | <b>High-side gate driver for 3.3V.</b> Connect this pin directly to the gate of an N-channel MOSFET. The trace from this pin to the MOSFET gate should be < 1".       |

| SW3.3       | 5          | <b>High side FET Source and Low Side FET Drain Switching Node.</b> Switching node for 3.3V.                                                                           |

| 5V-ALWAYS   | 6          | <b>5V Always on linear regulator output.</b> The sum of the load currents on pins 2 and 6 must not exceed 50mA total.                                                 |

| LSD3.3      | 7          | <b>Low-side gate driver for 3.3V.</b> Connect this pin directly to the gate of an N-channel MOSFET. The trace from this pin to the MOSFET gate should be < 1".        |

| GND3.3      | 8          | Ground for 3.3V MOSFET.                                                                                                                                               |

| ISEN3.3     | 9          | <b>Current sense for 3.3V.</b> This pin should be connected to the Drain of the bottom Mosfet with an appropriate resistor and an RC filter. See Application Section. |

| VFB3.3      | 10         | Voltage feedback for 3.3V.                                                                                                                                            |

| SDN3.3      | 11         | <b>Soft Start and ON/OFF for 3.3V.</b> OFF=GND. ON=open with SDWN=High. Use open collector device for control.                                                        |

| PGOOD       | 12         | <b>Power Good Flag.</b> An open collector output that will be logic low if any output voltage is not above 89% of the nominal output voltage.                         |

| SDWN        | 13         | Master Shutdown. Shutdown for all power. Off when low. When high 5V/3.3V-ALWAYS are ON while 5V/3.3V-Main are ready to turn on if SDN5, SDN3.3 go open.               |

| SGND        | 14         | Signal ground.                                                                                                                                                        |

| VFB12       | 15         | Voltage feedback for 12V.                                                                                                                                             |

| SW12        | 16         | FET driver for 12V Boost.                                                                                                                                             |

| SDN5        | 17         | Enable/Soft Start for 5V and 12V. Soft start and ON/OFF for 5V & 12V. OFF=Grounded. ON=open with SDWN=High.                                                           |

| VFB5        | 18         | Voltage feedback for 5V.                                                                                                                                              |

| GND5        | 19         | Ground for 5V MOSFET.                                                                                                                                                 |

| LSD5        | 20         | <b>Low side FET driver for 5V.</b> Connect this pin directly to the gate of an N-channel MOSFET. The trace from this pin to the MOSFET gate should be < 1".           |

## Pin Description (Continued)

| Pin Name | Pin Number | Pin Function Description                                                                                                                                                                   |  |

|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| ISEN5    | 21         | <b>Current Sense for 5V.</b> This pin should be connected to the drain of the bottom Mosfet using appropriate resistor and RC filter. See Application Section.                             |  |

| SW5      | 22         | High Side Driver Source and Low Side Driver Drain Switching Node. Switching node for 5V.                                                                                                   |  |

| HSD5     | 23         | <b>High side FET driver for 5V.</b> Connect this pin directly to the gate of an N-channel MOSFET. The trace from this pin to the MOSFET gate should be < 1".                               |  |

| CPUMP5   | 24         | <b>Charge Pump 5V.</b> High side Gate drive voltage for 5V. High side Gate drive voltage for 5V. This pin is to be connected to SW5 through a 100nF cap. and to 5V-ALWAYS through a diode. |  |

## Absolute Maximum Ratings<sup>1</sup>

| Parameter                                                               | Conditions | Min. | Тур. | Max. | Units |

|-------------------------------------------------------------------------|------------|------|------|------|-------|

| V <sub>IN</sub>                                                         |            | -0.3 |      | 27   | V     |

| SW, ISEN Pins,SDWN Pin                                                  |            | -0.3 |      | 27   | V     |

| CPUMP, HSD Pins                                                         |            | -0.3 |      | 33   | V     |

| SDN, VFB, V_always pins                                                 |            | -0.3 |      | 6.5  | V     |

| CPUMP to SW pins, and all other pins                                    |            | -0.3 |      | 6.5  | V     |

| The sum of the load currents on pins 2 and 6 must not exceed 60mA total |            |      |      |      |       |

#### Note:

## **Recommended Operating Conditions**

| Input Voltage, V <sub>IN</sub>      | +5.4V to 24V  |

|-------------------------------------|---------------|

| Ambient Temperature, T <sub>A</sub> | -20°C to 85°C |

## **Thermal Information**

| Thermal Resistance, θ <sub>JA</sub> | 88°C/W         |          |

|-------------------------------------|----------------|----------|

| Thermal Resistance, $\theta_{JC}$   | QSOP           | 28.5°C/W |

|                                     | TSSOP          | 16°C/W   |

| Maximum Junction Temperature        | 150°C          |          |

| Storage Temperature Range           | -65°C to 150°C |          |

| Maximum Lead Temperature, Solderi   | 300°C          |          |

Stresses beyond "Absolute Maximum Ratings" may cause permanent device damage. Continuous exposure to absolute

maximum rating conditions may affect device reliability. Functional operation of the device at these or any other conditions

beyond those indicated in the operational sections of the specification is not implied.

## **ELECTRICAL SPECIFICATIONS**

## **Operating Conditions**

Recommended Operating Conditions Unless Noted Refers to Block Diagrams

| Parameter                                              | ter Conditions                        |     | Тур.  | Max. | Units |

|--------------------------------------------------------|---------------------------------------|-----|-------|------|-------|

| Supply                                                 | •                                     |     | '     |      | '     |

| V <sub>IN</sub> Input Supply Voltage                   | (DC loading only) Note 1              | 5.4 |       | 24   | V     |

| Input Quiescent Current                                | H/LSD Open                            |     | 1.4   | 3    | mA    |

|                                                        | Stand-by                              |     | 300   | 400  | μΑ    |

|                                                        | Shut-down                             |     | <1    | 5    | μΑ    |

| Input UVLO Threshold                                   | Rising Vbat                           | 4.3 | 4.7   | 5.1  | V     |

|                                                        | hysteresis                            |     | 500   |      | mV    |

| 5V and 3.3V Main Regulators                            |                                       |     |       |      |       |

| Output Voltage Precision                               | 0.1 to 5.5A, 5.4 to 24V               | -2  |       | +2   | %     |

| Oscillator Frequency, f <sub>osc</sub>                 |                                       | 255 | 300   | 345  | kHz   |

| HSD On-Resistance, pull up                             |                                       |     | 7     | 12   | Ω     |

| HSD On Resistance pull down                            |                                       |     | 4     | 10   | Ω     |

| LSD On-Resistance, pull up                             |                                       |     | 6     | 9    | Ω     |

| LSD On Resistance pull down                            |                                       |     | 5     | 8    | Ω     |

| HSD On Output, V <sub>CPUMP</sub> -V <sub>GS</sub>     | I = 10μA                              |     |       | 100  | mV    |

| HSD Off Output, V <sub>GS</sub>                        | I = 10μA                              |     |       | 100  | mV    |

| LSD On Output, V <sub>5V-Always</sub> -V <sub>GS</sub> | I = 10μA                              |     |       | 100  | mV    |

| LSD Off Output, V <sub>GS</sub>                        | I = 10μA                              |     |       | 100  | mV    |

| Ramp Amplitude, pk-pk                                  | VIN = 16V                             |     | 2     |      | V     |

| Ramp Offset                                            |                                       |     | 0.5   |      | V     |

| Ramp Gain from V <sub>IN</sub>                         |                                       |     | 125   |      | mV/V  |

| Error Amplifier GBW                                    |                                       |     | 3     |      | MHz   |

| Current Limit Threshold                                | R2, R8 = 1KΩ                          | 90  | 135   | 180  | μΑ    |

| Over Voltage Threshold                                 | 2µs delay                             | 110 | 115   | 120  | %VO   |

| Under Voltage Threshold                                | 2µs delay                             | 70  | 75    | 80   | %VO   |

| SDN/SS Full On Voltage Min.                            | (End of Soft Start)                   | 4.2 |       |      | V     |

| SDN/SS Full Off Voltage Max.                           |                                       |     |       | 800  | mV    |

| Max Duty Cycle                                         |                                       |     | 94    |      | %     |

| Min PWM Time                                           |                                       |     | 200   |      | nsec  |

| VFB3.3 Input Leakage Current                           |                                       | 40  | 55    | 70   | μΑ    |

| 12V Regulator                                          | ·                                     |     | •     |      |       |

| Output Voltage Precision                               | V_5 =4.9 to 5.1V<br>and lo=0 to 150mA | -2  |       | +2   | %     |

| V <sub>FB12</sub>                                      |                                       |     | 2.472 |      | V     |

| V <sub>FB12</sub> Input Current                        | Note 2                                |     | 100   | 200  | nA    |

| Oscillator Frequency (f <sub>osc</sub> /3)             |                                       | 85  | 100   | 115  | kHz   |

| Gate Drive On-Resistance                               | High or Low                           |     | 6     | 12   | Ω     |

#### **Operating Conditions** (Continued)

Recommended Operating Conditions Unless Noted Refers to Block Diagrams

| Parameter                                          | Conditions                                  | Min. | Тур. | Max. | Units                        |

|----------------------------------------------------|---------------------------------------------|------|------|------|------------------------------|

| 12V Regulator (Continued)                          |                                             | !    |      |      |                              |

| On Output, V <sub>5V-Always</sub> -V <sub>GS</sub> | I = 10μA                                    |      |      | 100  | mV                           |

| Off Output, V <sub>GS</sub>                        | I = 10μA                                    |      |      | 100  | mV                           |

| Ramp Amplitude, pk-pk                              |                                             |      | 2    |      | V                            |

| Error Amplifier GBW                                |                                             |      | 1    |      | MHz                          |

| Under Voltage Shut Down                            | 2µs delay                                   | 70   | 76   | 80   | %V <sub>O</sub>              |

| Over Voltage Shut Down                             | Measured at VFB <sub>12</sub>               |      | 115  |      | %V <sub>O</sub>              |

| Min Duty Cycle                                     |                                             | 0    |      |      | %                            |

| Max Duty Cycle                                     | (By design)                                 | 32   | 33   | 34   | %                            |

| 5V and 3.3V Always                                 |                                             |      |      |      | •                            |

| Bypass Switch rdson                                |                                             |      | 1.3  | 1.5  | Ω                            |

| Linear Regulator Accuracy                          | 5.6 to 24V, 0 to 50mA,<br>5V Main On or Off | -3.3 |      | 2    | %                            |

| Rated Output Current                               | l <sub>3.3</sub> + l <sub>5</sub>           | 0    |      | 50   | mA                           |

| Over-current Limit                                 | 2µs delay                                   | 100  | 180  |      | mA                           |

| Under-voltage Threshold                            | 2µs delay                                   | 70   | 75   | 80   | %                            |

| Reference                                          |                                             |      |      |      |                              |

| Internal Reference Accuracy                        | 0-70°C                                      | -1   |      | 1    | %                            |

| Control Functions                                  |                                             |      |      |      |                              |

| SDWN Off Voltage Max.                              |                                             |      |      | 800  | mV                           |

| SDWN On Voltage Min.                               |                                             | 3    |      |      | V                            |

| Over-temperature Shutdown, t <sub>j</sub>          |                                             |      | 150  |      | °C                           |

| Over-temperature Hysteresis                        |                                             |      | 25   |      | °C                           |

| PGOOD Threshold                                    | PWM Buck Converters                         | -14  | -11  | -8.5 | %V <sub>O</sub> <sup>1</sup> |

| PGOOD Sink Current                                 |                                             | -4   |      |      | mA                           |

| PGOOD leakage                                      |                                             |      |      | 1    | μA                           |

| +5V Analog Softstart                               | Css=100nF                                   |      | 65   |      | msec                         |

| +3.3V Analog Softstart                             | Css=100nF                                   |      | 65   |      | msec                         |

| Soft Start Current                                 |                                             |      | 5    |      | μA                           |

| PGOOD Min Pulse Width                              | Note 2                                      | 5    | 10   |      | μs                           |

#### Notes

- 1. The minimum input voltage does not include voltage drop in the source supply due to source resistance. It is operating voltage for static load conditions. To get acceptable load transient performance, the input voltage required will be much higher, in the 7.5 to 8.5 volt range or even higher depending on the severity of dynamic load, source impedance and input and output capacitance and inductor values. The user should thoroughly test the performance at minimum input voltage using intended component values and transient loading.

- 2. Min/Max specifications are guaranteed by design.

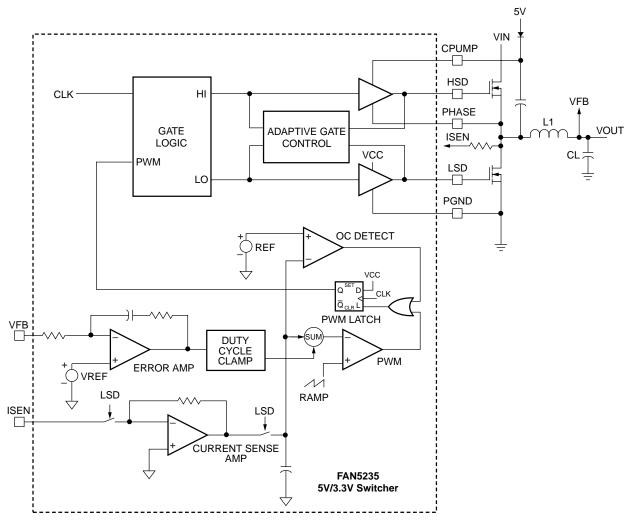

Figure 1. FAN5235 5V/3.3V Internal Block Diagram of PWM Loop

Figure 2. FAN5235 12V Internal Block Diagram

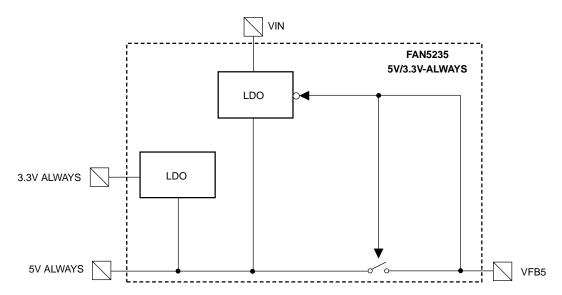

Figure 3. FAN5235 5V/3.3V—ALWAYS Internal Block Diagram

### **Functional Description**

The FAN5235 is a high efficiency and high precision DC/DC controller for notebook and other portable applications. It provides all of the voltages necessary for system electronics: 5V, 3.3V, 12V, and both 3.3V-ALWAYS and 5V-ALWAYS. Utilization of both input and output voltage feedback in a current-mode control allows for fast loop response over a wide range of input and output variations. Current sense based on MOSFET R<sub>DS,on</sub> gives maximum efficiency, while also permitting the use of a sense resistor for high accuracy.

#### 3.3V and 5V Architecture

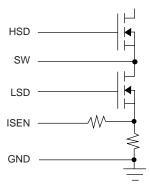

The 3.3V and 5V switching regulator outputs of the FAN5235 are generated from the unregulated input voltage using synchronous buck converters. Both high side and low-side MOSFETs are N-channel.

The 3.3V and 5V switchers have pins for current sensing and for setting of output over-current threshold using MOSFET  $R_{DS,on}$ . Each converter has a pin for voltage-sense feedback, a pin that shuts down the converter, and a pin for generating the boost voltage to drive the high-side MOSFET.

The following discussion of the FAN5235 design will be done with reference to Figures 1 through 4, showing the internal block diagram of the IC.

#### 3.3V and 5V PWM Current Sensing

Peak current sensing is done on the low side driver because of the very low duty-cycle on the high side MOSFET. The current is sampled 50ns after turn on and the value is held for current feedback and over-current limit.

#### 3.3V and 5V PWM Loop Compensation

The 3.3V and 5V control loops of the FAN5235 function as voltage mode with current feedback for stability. They each have an independent voltage feedback pin, as shown in Figure 1. They use voltage feed-forward to guarantee loop rejection of input voltage variation: that is to say that the PWM (pulse width modulation) ramp amplitude is varied as a function of the input voltage. Compensation of the control loops is done entirely internally using current-mode feedback compensation. This scheme allows the bandwidth and phase margin to be almost independent of output capacitance and ESR.

#### 3.3V and 5V PWM Current Limit

The 3.3V and 5V converters each sense the voltage across their own low-side MOSFET to determine whether to enter current limit. If an output current in excess of the current limit threshold is measured then the converter enters a pulse skipping mode where Iout is equal to the over-current (OC) set limit. After 8 clock cycles then the regulator is latched off (HSD and LSD off). This is the likely scenario in the case of a "soft" short. If the short is "hard" it will instantly trigger the under-voltage protection which again will latch the regulator off (HSD and LSD off) after a 2µs delay.

Selection of a current-limit set resistor must include the tolerance of the current-limit trip point, the MOSFET on resistance and temperature coefficient, and the ripple current, in addition to the maximum output current.

Example: Maximum DC output current on the 5V is 5A, the MOSFET  $R_{DS,on}$  is  $17m\Omega,$  and the inductor is  $5\mu H$  at a current of 5A. Because of the low  $R_{DS,on},$  the low-side MOSFET will have a maximum temperature (ambient + self-heating) of only  $75^{\circ}C,$  at which its  $R_{DS,on}$  increases to  $20m\Omega.$

Peak current is DC output current plus peak ripple current:

$$I_{pk} \approx I_{dc} + \frac{TV_0}{2L} = 5A + \frac{4\mu sec \cdot 5V}{2 \cdot 5\mu H} = 7A$$

where T is the maximum period,  $V_O$  is output voltage, and L is the inductance. This current generates a voltage on the low-side MOSFET of 7A •  $20m\Omega=140mV$ . The current limit threshold is typically 150mV (worst-case 135mV) with R2 =  $1K\Omega$ , and so this value is suitable. R2 could be increased a further 10% if additional noise margin is deemed necessary.

#### **Precision Current Limit**

Precision current limiting can be achieved by placing a discrete sense resistor between the source of the low-side MOSFET and ground.

In this case, current limit accuracy is set by the tolerance of the IC, +10%.

Figure 4. Using a Precision Current Sense Resistor

#### Shutdown (SDWN)

The SDWN pin turns off all 5 converters (+5V, +3.3V, and +12V, 5V/3.3V-ALWAYS) and puts the FAN5235 into a low-power mode (Shutdown mode).

This mode of operation implies the use of a push button switch between  $\overline{SDWN}$  and Vin. Pushing the button allows (for the duration of the contact) to power the 3.3V-ALWAYS and 5V-ALWAYS long enough for the uC to power up and in turn latch the  $\overline{SDWN}$  pin high.

Once the  $\overline{SDWN}$  is high then the ALWAYS voltages are enabled to go high if the respective  $\overline{SDN3.3}$  and  $\overline{SDN5}$  go high.

# MAIN 3.3V and 5V Softstart, Sequencing and Stand-by

Softstart of the 3.3V and 5V converters is accomplished by means of an external capacitor between pins  $\overline{SDN3.3}$  ( $\overline{SDN5}$ ) and ground.

The 3.3V (5V) main converter is turned ON if  $\overline{SDWN}$  and  $\overline{SDN3.3}$  ( $\overline{SDN5}$ ) are both high and is turned off if either  $\overline{SDWN}$  or  $\overline{SDN3.3}$  ( $\overline{SDN5}$ ) is low.

Stand-by mode is defined as the condition by which V-Mains are OFF and V-ALWAYS are ON (\$\overline{SDWN}\$=1 and \$\overline{SDN3.3}=\overline{SDN5}=0\$).

#### **ALWAYS** mode of Operation

If it is desired that 5V-ALWAYS and 3.3V-ALWAYS are always ON then the  $\overline{SDWN}$  pin must be connected to Vin permanently. This way the two ALWAYS regulators come up as soon as there is power while the state of the Main regulators can be controlled via the  $\overline{SDN5}$  and  $\overline{SDN3.3}$  pins.

#### **Sequencing Table**

| SDN5 | SDN3.3 | SDWN | 3V&5V<br>ALWAYS | 5V<br>MAIN | 3.3V<br>MAIN |

|------|--------|------|-----------------|------------|--------------|

| Х    | X      | 0    | 0               | 0          | 0            |

| 0    | 0      | 1    | 1               | 0          | 0            |

| 1    | 0      | 1    | 1               | 1          | 0            |

| 0    | 1      | 1    | 1               | 0          | 1            |

| 1    | 1      | 1    | 1               | 1          | 1            |

#### 3.3V Voltage Adjustment

The output voltage of the 3.3V converter can be increased by as much as 10% by inserting a resistor divider in the feedback line. The feedback pin impedance is about  $66K\Omega$ . Thus, for example, to increase the output of the 3.3V converter by 10%, use a  $2.21K\Omega/33.2K\Omega$  divider.

Note that the output of the 5V regulator cannot be adjusted. The feedback line of the 5V regulator is used internally as a 5V supply and, therefore, cannot tolerate any impedance in series with it.

# 3.3V and 5V Main Overvoltage Protection (Soft Crowbar)

When the output voltage of the 3.3V (or the 5V) converter exceeds approximately 115% of nominal, the converter enters the over-voltage (OV) protection mode, with the goal of protecting the load from damage. During operation, severe load dump or a short of an upper MOSFET could cause the output voltage to increase significantly over normal operation range without circuit protection. When the output exceeds the overvoltage threshold, the over-voltage comparator forces the lower gate driver high and turns the lower MOSFET on. This will pull down the output voltage and eventually may blow the battery fuse. As soon as output voltage drops below the threshold, OVP comparator is disengaged.

The OVP scheme also provides a soft crowbar function (bang-bang control followed by blow of the fuse) which helps to tackle severe load transients but does not invert output voltage when activated—a common problem for OVP schemes with a latch. The prevention of output inversion eliminates the need for a Schottky diode across the load.

#### 3.3V and 5V Under-voltage Protection

When the output voltage of either the 3.3V or 5V falls below 75% of the nominal value, both converters, go into undervoltage (UV) protection, after a 2usec delay. In undervoltage protection, the high and low side MOSFETs are turned off. Once under-voltage protection is triggered, it remains on until power is recycled or the  $\overline{\text{SDWN}}$  pin is reset.

#### 12V Architecture

The 12V converter is a traditional non-isolated fly-back (also known as a "boost" converter). The converter's input voltage is the +5V switcher output, so that +12V can only be present if +5V is present. Also, if the external MOSFET is off, the output of the +12V converter is +5V, not zero. This in turn will provide non-zero output for the 12V regulator.

For complete turn-off of the 12V regulator an external P-channel MOSFET or an LDO regulator with on/off control may be used. If an LDO is used for 12V then the boost converter should be set to 13.2V using the external resistor divider network.

#### 12V Loop Compensation

The 12V converter should be run in discontinuous conduction mode. In this mode, the converter will be stable if a capacitor with suitable ESR value is selected. A 68uF tantalum with 500mA ripple current rating and  $95m\Omega$  is recommended here.

#### 12V Protection

The 12V converter is protected against overvoltage. If the 12V feedback is more than 10–15% above the nominal set voltage, a comparator forces the MOSFET off until the voltage falls below the comparator threshold.

The 12V converter is also protected against over-current. If a short circuit pulls the output below 9V, all of the switching converters go into UV protection, after a  $2\mu s$  delay. In UV protection, all MOSFETs are turned off. Once UV protection is triggered, it remains on until the input power is recycled or the  $\overline{SDWN}$  is reset.

#### 12V Softstart and Sequencing

The 12V output is started at the same time as the 5V output. The softly rising 5V output automatically generates a softly rising 12V output. The duty cycle of the 12V PWM is limited to prevent excessive current draw.

The 12V supply must build up a voltage higher than the UVLO limit (9V) by the time the 5V is above its UVLO (3.75V) in order to avoid triggering of UV protection during soft start.

#### 5V/3.3V-ALWAYS Operation

The 5V-ALWAYS supply is generated from either the onchip linear regulator or through an internal switch from the VFB pin of the 5V switching supply.

When the 5V switching supply is off, or if its output voltage is not within tolerance, the 5V-ALWAYS switch is open, and the linear regulator is on. When the 5V switching supply is running and has an output voltage within specification, the linear regulator is off, and the switch is on. The switch has sufficiently low resistance that at maximum current draw on the 5V-ALWAYS supply, the output voltage is regulated within specifications.

The 3.3V-ALWAYS is generated from a linear regulator attached internally to the 5V-ALWAYS.

The purpose of the two ALWAYS supplies (combined current is specified to never exceed 50mA) is to provide power to the system micro-controller (8051 class) as well as other IC's needing a stand-by power. The micro-controller as well as the other IC's could be operated from either 5V or 3.3V ALWAYS, so the FAN5235 provides both.

#### 5V/3.3V-ALWAYS Protections

The two internal linear regulators are current limited and under-voltage protected. Once protection is triggered all outputs are turned off until power is cycled or the  $\overline{\text{SDWN}}$  is reset.

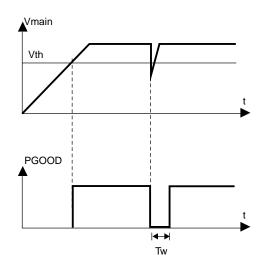

#### Power good

Power good is asserted when both PWM Buck converters are above specified threshold. No other regulators are monitored by Power good. When PGOOD goes low it will stay low for at least 10µsec (Tw). See fig. 5.

Figure 5. PGOOD Timing Diagram

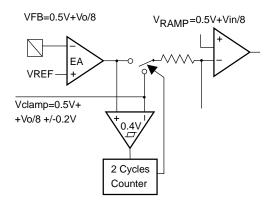

#### **Error Amplifier output voltage clamp**

During a load transient the error amplifier voltage is allowed full swing. After two clock cycles, if the amplifier is still out of range the voltage and consequently the duty cycle (DC) is clamped. The DC clamp automatically limits the build up of over-currents during abnormal conditions, including short circuits:

Figure 6. Duty-Cycle Clamp

#### Thermal shutdown

If the die temperature of the FAN5235 exceeds safe limits, the IC shuts itself off. When the over-temperature (OT) event ends, the IC comes back to normal operation. There is a 25°C thermal hysteresis between shutdown and start up.

#### **Input UVLO**

If the input voltage falls below the UVLO threshold, the FAN5235 turns itself off and stays off as long as Input voltage is below threshold.

#### **IC Protections Table**

|                  | HSD<br>Buck | LSD<br>Buck     | LDO       | LSD<br>Boost |

|------------------|-------------|-----------------|-----------|--------------|

| OC/UV<br>(Bucks) | OFF-LATCH   | OFF-LATCH       | ON        | OFF-LATCH    |

| OC/UV<br>(LDO)   | "           | II              | OFF-LATCH | "            |

| OV (Buck)*       | OFF         | SOFT<br>CROWBAR | ON        | ON           |

| OV (Boost)       | ON          | ON              | ON        | OFF          |

| SDWN=0           | OFF         | OFF             | OFF       | OFF          |

| ОТ               | OFF         | OFF             | OFF       | OFF          |

| UV (Boost)       | OFF-LATCH   | OFF-LATCH       | ON        | OFF-LATCH    |

| OC (Boost)       | ON          | ON              | ON        | 33% DC       |

<sup>\*</sup> Only the converter in Over-Voltage goes in SOFT CROW-BAR mode.

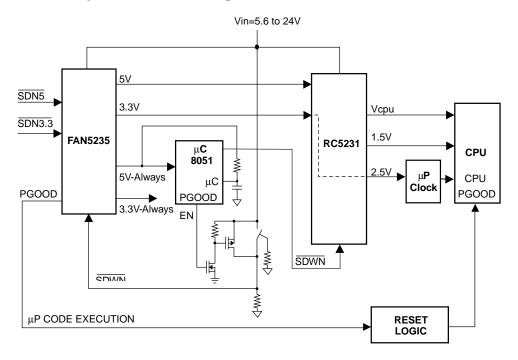

## **Generic Mobile System Block Diagram**

Figure 7. System Block Diagram

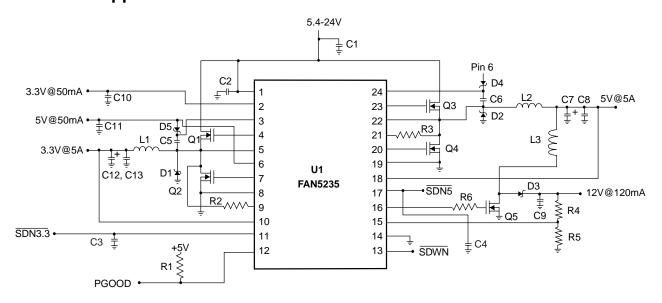

## **Notebook Application Circuit**

Figure 8. FAN5235 Notebook Application Circuit

**Table 1. FAN5235 Application Bill of Materials**

| Reference      | Manufacturer, Part #      | Quantity | Description            | Comments                                         |

|----------------|---------------------------|----------|------------------------|--------------------------------------------------|

| C1             | SANYO<br>25SP33M          | 1        | 33μF, 25V              | OSCON,<br>I <sub>rms</sub> = 3A,<br>19V adapter. |

| C2-6           | Any                       | 5        | 100nF, 50V             | Ceramic                                          |

| C7-8<br>C12-13 | KEMET<br>T510X337(1)010AS | 2<br>2   | 330μF, 10V             | Tantalum,<br>ESR=35mΩ                            |

| C10-11         | AVX*020R1800TPSA475       | 2        | 4.7μF, 20V             | Tantalum, ESR=1.8Ω                               |

| C9             | AVX<br>TPSV68*025R0095    | 1        | 68μF, 25V,<br>ESR=95mΩ | Tantalum,<br>I <sub>rms</sub> = 0.5A             |

| R1             | Any                       | 1        | 10ΚΩ, 1%               |                                                  |

| R2, R3         | Any                       | 2        | 1ΚΩ, 1%                |                                                  |

| R4, R5         | Any                       | 1        | 380ΚΩ, 100ΚΩ           | 1%                                               |

| R6             | Any                       | 1        | 10Ω                    |                                                  |

| D1-3           | Fairchild SS22            | 3        | 2A, 40V Schottky       |                                                  |

| D4-5           | Fairchild MBR0520L        | 2        | 500mA, 20V Schottky    |                                                  |

| L1-2           | Any                       | 2        | 6.4µH, 5A              | R < 25mΩ                                         |

| L3             | Any                       | 1        | 5.6µH, 2A              |                                                  |

| Q1-4           | Fairchild FDS6690A        | 4        | 30V N-channel MOSFET   | $R = 17m\Omega$                                  |

| Q5             | Fairchild NDC631N         | 1        | 20V N-channel MOSFET   | $R = 60m\Omega$                                  |

| U1             | Fairchild FAN5235         | 1        | SER Controller         |                                                  |

#### **MOSFET Selection**

The notebook application circuit shown in Figure 1 is designed to run with an input voltage operating range of 5.4-24V. This wide input range helps determine the selection of the MOSFETs for the 3.3V and 5V converters, since the high-side MOSFET is on  $(V_{out} \, / \, V_{in})$  of the time, and the low-side MOSFET  $1 - (V_{out} \, / \, V_{in})$  of the time. The maxima and minima are tabulated in Table 2:

#### **Table 2. MOSFET Duty Cycles**

#### **High-side FET**

|                  | V <sub>in</sub> |     |  |

|------------------|-----------------|-----|--|

| V <sub>out</sub> | 5.4V            | 24V |  |

| 3.3V             | .61             | .14 |  |

| 5V               | .43             | .21 |  |

#### Low-side FET

|                  | V <sub>in</sub> |     |  |  |

|------------------|-----------------|-----|--|--|

| V <sub>out</sub> | 5.4V            | 24V |  |  |

| 3.3V             | .39             | .86 |  |  |

| 5V               | .07             | .79 |  |  |

All four MOSFETs have maximum duty cycles greater than 50%. Thus, it is necessary to size all four approximately the same.

#### 3.3V and 5V Schottky Selection

The maximum current at which the converters operate in PFM mode determines selection of a Schottky. In the application shown in Figure 8, since the transition can occur at a current as high as  $28\text{mV}*(17.5\text{K}\Omega/10\text{K}\Omega)/35\text{m}\Omega=1.4\text{A}$ , the diode (with 24V input) will be conducting 86% of the period (from Table 2). It thus has an average current of 1.4A\*0.86=1.2A, which requires a Schottky current rating >1A.

#### 3.3V and 5V Inductor Selection

See Table 1.

#### 3.3V and 5V Output Cap Selection

See Table 1.

#### **12V Component Selection**

Calculation of the inductor, diode and output capacitor for the +12V output fly-back is complex, depending on output power and efficiency. See Applications Bulletin AB-19 for an Excel spreadsheet calculation tool. See Table 1 also.

#### **Input Capacitor Selection**

Input capacitor selection is determined by ripple current rating. With two converters operating in parallel at differing duty cycles, calculation of input ripple current is complex; see Applications Bulletin AB-19 for an Excel spreadsheet calculation tool.

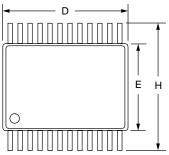

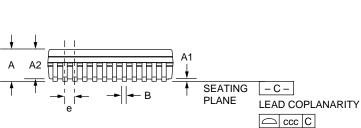

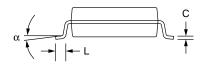

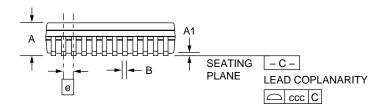

## **Mechanical Dimensions**

#### **QSOP 24-Lead**

| Symbol | Inches    |        | Millimeters |      | Notes |

|--------|-----------|--------|-------------|------|-------|

|        | Min.      | Max.   | Min.        | Max. | Notes |

| А      | 0.0532    | 0.0668 | 1.35        | 1.75 |       |

| A1     | 0.0040    | 0.0098 | 0.1         | 0.25 |       |

| A2     | 0.054     | 0.062  | 1.37        | 1.57 |       |

| b      | 0.008     | 0.012  | 0.20        | 0.30 | 5     |

| С      | 0.0075    | 0.0098 | 0.19        | 0.25 | 5     |

| D      | 0.337     | 0.344  | 8.55        | 8.74 | 2, 4  |

| Е      | 0.150     | 0.157  | 3.81        | 3.99 | 2     |

| е      | 0.025 BSC |        | 0.635 BSC   |      |       |

| Н      | 0.228     | 0.244  | 5.79        | 6.20 |       |

| L      | 0.016     | 0.050  | 0.40        | 1.27 | 3     |

| N      | 24        |        | 24          |      | 6     |

| α      | 0°        | 8°     | 0°          | 8°   |       |

| CCC    | _         | .004   | _           | 0.10 |       |

#### Notes:

- 1. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- "D" and "E" do not include mold flash. Mold flash or protrusions shall not exceed .006 inch (0.15mm).

- 3. "L" is the length of terminal for soldering to a substrate.

- 4. Terminal numbers are shown for reference only.

- 5. "b" and "c" dimensions include solder finish thickness.

- 6. Symbol "N" is the maximum number of terminals.

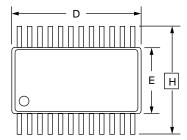

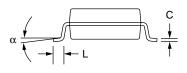

## **Mechanical Dimensions**

#### **TSSOP 24-Lead**

| Symbol | Inches   |      | Millimeters |      | Netes |

|--------|----------|------|-------------|------|-------|

|        | Min.     | Max. | Min.        | Max. | Notes |

| Α      | _        | .047 | _           | 1.20 |       |

| A1     | .002     | .006 | 0.05        | 0.15 |       |

| В      | .007     | .012 | 0.19        | 0.30 |       |

| С      | .004     | .008 | 0.09        | 0.20 |       |

| D      | .303     | .316 | 7.70        | 7.90 | 2     |

| Е      | .169     | .177 | 4.30        | 4.50 | 2     |

| е      | .026 BSC |      | 0.65 BSC    |      |       |

| Н      | .252 BSC |      | 6.40 BSC    |      |       |

| L      | .018     | .030 | 0.45        | 0.75 | 3     |

| N      | 24       |      | 24          |      | 5     |

| α      | 0°       | 8°   | 0°          | 8°   |       |

| CCC    | _        | .004 | _           | 0.10 |       |

#### Notes:

- 1. Dimensioning and tolerancing per ANSI Y14.5M-1982.

- "D" and "E" do not include mold flash. Mold flash or protrusions shall not exceed .006 inch (0.15mm).

- 3. "L" is the length of terminal for soldering to a substrate.

- 4. Terminal numbers are shown for reference only.

- 5. Symbol "N" is the maximum number of terminals.

## **Ordering Information**

| Product Number | Package       |  |  |

|----------------|---------------|--|--|

| FAN5235QSC     | 24 Lead QSOP  |  |  |

| FAN5235MTC     | 24 Lead TSSOP |  |  |

#### **DISCLAIMER**

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, or (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com