## **SmartSwitch™**

## **General Description**

AAT4626 SmartSwitch™ is part AnalogicTech's Application Specific Power MOSFET™ (ASPM™) product family. It is a dualchannel 500mA current-limited P-channel MOSFET power switch designed for high-side load-switching applications. This switch operates with inputs ranging from 2.7V to 5.5V, making it ideal for both 3V and 5V systems. An integrated current-limiting circuit protects the input supply against large changes in load current which may cause the supply to fall out of regulation. The AAT4626 is also protected from thermal overload which limits power dissipation and junction temperatures. The current limit threshold is factory programmed at 1.0A, with a maximum of 1.5A. The guiescent supply current is typically a low 20µA. In shutdown mode, the supply current decreases to less than 1µA.

The AAT4626 is available in 8 pin SOP or TSSOP specified over a -40 to 85°C temperature range.

The AAT4600 Series is a family of adjustable and fixed SmartSwitch™ products with a range of current handling capabilities. Single versions with adjustable current limit (AAT4601) or fixed current limit (AAT4625) as well as dual versions with fixed current limit (AAT4626) are also available.

## **Features**

- Compliant to USB 1.1 and 2.0 specifications

- 2.7V to 5.5V Input voltage range

- 500mA (min) continuous current per channel

- 1.25A (max) current limit per channel

- 90mΩ typical R<sub>DS(ON)</sub>

- Low quiescent current

- Typically 20µA

- 1µA max with Switches off

- Thermal shutdown

- Slew rate limited turn on

- Fault flag with 2ms blanking

- Undervoltage Lockout

- Temp range -40 to 85°C

- UL Approved—File No. E217765

- 8 pin SOP or TSSOP package

## **Applications**

- USB ports and peripherals

- Notebook computers

- Hot swap supplies

- General purpose power switching

**UL Recognized Component**

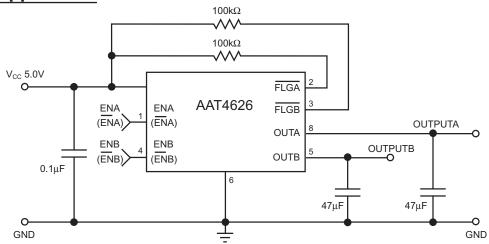

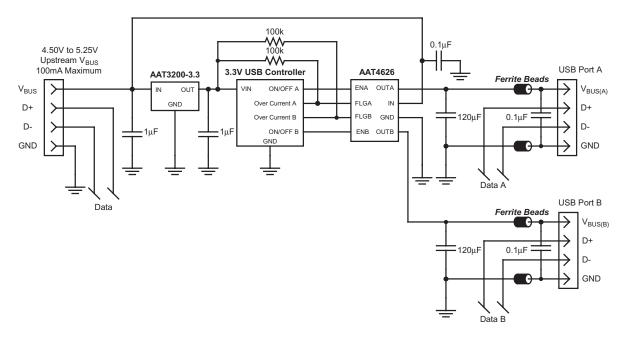

## **Typical Application**

## **Pin Descriptions**

| Pin # | Symbol               | Function                                                                                                                                                                             |

|-------|----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 / 4 | EN(A/B)<br>(EN(A/B)) | Enable Inputs: Logic-compatible enable input. High input > 2.1V typical. Low input < 1.9V typical. Active high or active low option available; see Ordering Information for details. |

| 2/3   | FLG(A/B)             | Fault Flag Outputs: Active-low, open-drain output. Indicates over current, UVLO and thermal shutdown.                                                                                |

| 6     | GND                  | Ground connection                                                                                                                                                                    |

| 7     | IN                   | Supply Input: This pin is the P-channel MOSFETs' source connections. Also supplies the IC's internal circuitry.                                                                      |

| 8 / 5 | OUT(A/B)             | Switch Outputs: These pins are the P-channel MOSFET drain connection.                                                                                                                |

## **Pin Configuration**

SOP-8 TSSOP-8 (Top View) (Top View) ENA (ENA) ENA (ENA) □OUTA **■OUTA** FLGA□ FLGA 2 ⊅IN ⊐IN FLGB □ □GND FLGB 3 **□** GND ENB (ENB) □ □ OUTB ENB (ENB) ₫ **□**OUTB

## **Absolute Maximum Ratings** (T<sub>A</sub>=25°C unless otherwise noted)

| Symbol            | Description                              | Value                        | Units |

|-------------------|------------------------------------------|------------------------------|-------|

| V <sub>IN</sub>   | IN to GND                                | -0.3 to 6                    | V     |

| $V_{FLG}$         | FLGA, FLGB to GND                        | -0.3 to 6                    | V     |

| I <sub>FLG</sub>  | FLGA, FLGB Current                       | 50                           | mA    |

| V <sub>OUT</sub>  | OUTA, OUTB to GND                        | -0.3 to V <sub>IN</sub> +0.3 | V     |

| I <sub>OUT</sub>  | Output Current                           | Internally Limited           |       |

| $V_{EN}$          | EN (EN) to GND                           | -0.3 to 6                    | V     |

| T <sub>S</sub>    | Storage Temperature                      | 150                          | °C    |

| T <sub>LEAD</sub> | Maximum Soldering Temperature (at Leads) | 300                          | °C    |

Note: Stresses above those listed in Absolute Maximum Ratings may cause permanent damage to the device. Functional operation at conditions other than the operating conditions specified is not implied. Only one Absolute Maximum rating should be applied at any one time.

## **Thermal Information**

| Symbol         | Description                                     | Value | Units |

|----------------|-------------------------------------------------|-------|-------|

| $\Theta_{JA}$  | Maximum Thermal Resistance (SOP-8) <sup>1</sup> | 100   | °C/W  |

| P <sub>D</sub> | Maximum Power Dissipation (SOP-8) <sup>1</sup>  | 1.25  | W     |

Note 1: Mounted on an FR4 printed circuit board with 1 oz. copper ground plane.

# **Electrical Characteristics** ( $V_{IN} = 5V$ , $T_A = -40$ to $85^{\circ}$ C unless otherwise noted. Typical values are at $T_A = 25^{\circ}$ C; **bold** values designate full temperature range)

| Symbol                | Description                  | Conditions                                                | Min  | Тур  | Max  | Units |

|-----------------------|------------------------------|-----------------------------------------------------------|------|------|------|-------|

| Iq                    | Quiescent Current            | V <sub>IN</sub> =5V, ENA and ENB active                   |      | 20   | 40   | μΑ    |

|                       | Enable Input Threshold       | Low-to-high transition                                    |      |      | 2.4  | V     |

| V <sub>IN-THRSH</sub> | Enable Input Threshold       | High-to-low transition                                    | 0.8  |      |      | V     |

| I <sub>EN</sub>       | Enable Input Current         | V <sub>EN</sub> = 0V to 5.5V                              |      | 0.01 | 1    | μΑ    |

| C <sub>EN</sub>       | Enable Input Capacitance     |                                                           |      | 1    |      | pF    |

|                       | On-Resistance                | V <sub>IN</sub> =5V, each switch, T <sub>A</sub> = 25°C   |      | 90   | 130  | mΩ    |

| R <sub>ds(ON)</sub>   | On-Resistance                | V <sub>IN</sub> =3.0V, each switch, T <sub>A</sub> = 25°C |      | 100  | 150  | mΩ    |

| T <sub>ON</sub>       | Output Turn-On Delay         | $V_{IN}$ =5V, $R_L$ = $10\Omega$                          |      | 0.25 |      | ms    |

| T <sub>ON-RISE</sub>  | Output Turn-On Rise Time     | $R_L = 10\Omega$                                          |      | 0.2  |      | ms    |

| T <sub>OFF</sub>      | Output Turn-Off Delay        | $V_{IN}$ =5V, $R_L$ = $10\Omega$                          |      | 5    | 20   | μs    |

| T <sub>OFF-FALL</sub> | Output Turn-Off Fall Time    | $R_L = 10\Omega$                                          |      |      | 20   | μs    |

| I <sub>SD(OFF)</sub>  | Output Leakage Current       | EN=inactive, V <sub>IN</sub> =5.5V, V <sub>OUT</sub> =0V  |      | 0.03 | 1    | μΑ    |

| I <sub>LIMIT</sub>    | Current Limit Threshold      | ramped load applied to enable                             | 0.75 | 1.0  | 1.50 | Α     |

|                       |                              | output, V <sub>OUT</sub> < 4.0V                           |      |      |      |       |

| OTMP                  | Over Temperature Shut Down   | T <sub>J</sub> increasing                                 |      | 125  |      | °C    |

| OTIVII                | Over remperature shut bown   | T <sub>J</sub> decreasing                                 |      | 115  |      | °C    |

| $R_{FLG}$             | Error Flag Output Resistance | V <sub>IN</sub> =5V, IL = 1mA                             |      | 30   |      | Ω     |

| I <sub>SINK</sub>     | Error Flag Off Current       | V <sub>FLG</sub> = 5.5V                                   |      | 0.05 | 1    | μA    |

| $V_{UVLO}$            | Under voltage Lockout        | V <sub>IN</sub> =increasing, 1% hysterisis                | 2.0  | 2.3  | 2.7  | V     |

| T <sub>BLANK</sub>    | Fault blanking               |                                                           |      | 2    |      | ms    |

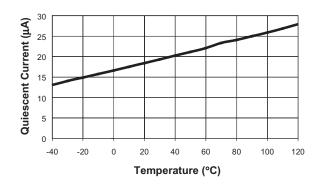

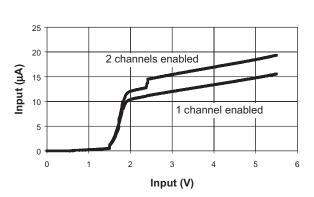

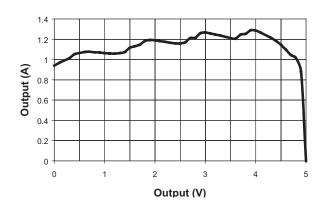

# $\frac{\textbf{Typical Characteristics}}{(\text{Unless otherwise noted, V}_{\text{IN}} = 5\text{V}, T_{\text{A}} = 25^{\circ}\text{C})}$

### **Quiescent Current vs. Temperature**

#### **Quiescent Current**

#### **Current Limit**

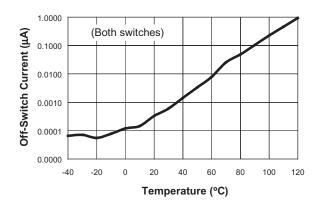

Off-Supply Current vs. Temperature

#### Off-Switch Current vs. Temperature

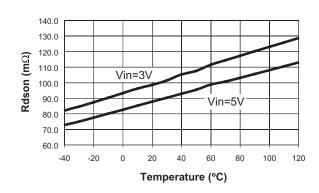

#### Rdson vs. Temperature

(Unless otherwise noted,  $V_{IN}$  = 5V,  $T_A$  = 25°C)

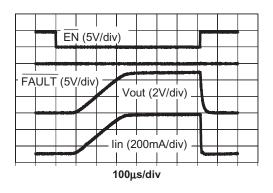

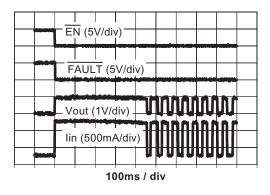

# Turn-ON/OFF Response with 10 Ohm 1μF load

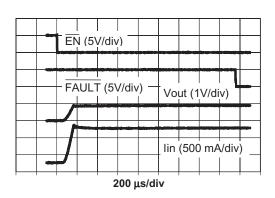

#### Start Into 1 Ohm load

## Thermal Shutdown Response

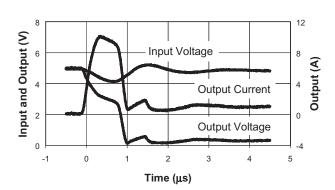

## **Short Circuit Through 0.3 Ohm**

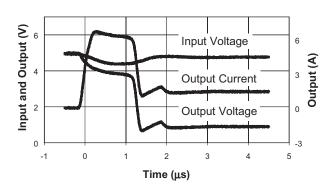

## **Short Circuit Through 0.6 Ohm**

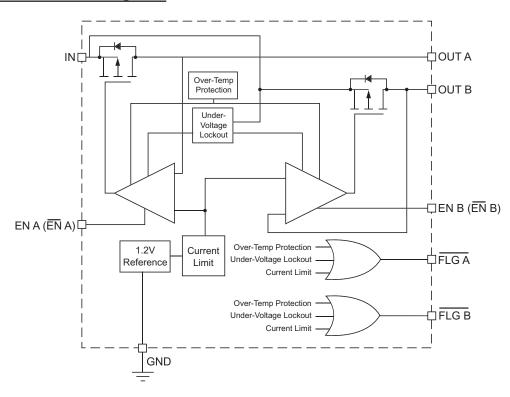

## **Functional Block Diagram**

## **Functional Description**

The AAT4626 is a dual integrated MOSFET load switch with a fixed level current limit, over temperature protection, level shifted inputs and a fault flag for each switch. The current limit control is combined with an over temperature thermal limit circuit to provide a comprehensive system to protect the load switch under short circuit or other adverse operating conditions. The AAT4626 is ideally suited for control and protection of peripheral ports such as USB, RS232 and parallel ports.

The current limit and over temperature circuits will act independently. The device current limit is activated when the output load current exceeds a preset internal threshold level. The minimum current limit threshold characteristic is specified by I<sub>LIM(MIN)</sub>. If the load switch ambient temperature becomes excessive or if a short circuit condition persists, the die temperature will rise causing the over temperature protection circuit to activate.

If the current limit or over temperature protection circuits are active for more then ten milliseconds.

the system will be informed via the FAULT Flag. The ten millisecond fault blanking delay allows the AAT4626 to be turned on into large capacitive loads without activating the FAULT Flags. The open drain FAULT outputs can be connected directly to system controllers driven by voltage levels less than the IN pin voltage without additional level shifting circuitry.

Each of the two load switches is turned on and off by applying a logic level signal to the EN(A/B) pin. The AAT4626 enable function is available in both active high and active low logic level versions. The AAT4626 typically consumes 20µA when operating, when off, the device draws less then 1µA. In the off state, current is prevented from flowing between the input and output on each respective channel. The EN(A/B) function has logic level thresholds that allow the AAT4626 to be TTL compatible and may also be controlled by 2.5V to 5.0V CMOS circuits. The voltage level on either EN(A/B) or FAULT(A/B) should not exceed the input supply level present on the IN pin.

## **Applications Information**

## **Operation in Current Limit**

If an excessive load is applied to the either output of an AAT4626, the load current will be limited by the AAT4626's current limit circuitry. Refer to the "Current Limit" figure in the typical characteristics section of this data sheet. If a short circuit were to occur on the load applied to either the A or B output, there would be a demand for more current than what is allowed by the internal current limiting circuit and the voltage at the device output will drop. This causes the AAT4626 to dissipate more power than in normal operation, causing the die temperature to increase. When die temperature exceeds the internal over temperature threshold, the AAT4626 will shut down both the A and B output channels. After shutting down, the AAT4626 cools to a level below the over temperature threshold, at which point it will start up again. The AAT4626 will continue to cycle off and on until one of the following events occurs; the load current of the offending output is reduced to a level below the AAT4626's current limit setting, the input power is removed, or until the output is turned off by a logic high level applied to the EN pin of the fault channel.

#### **Thermal Considerations**

Since the AAT4626 has internal current limit and over temperature protection, junction temperature is rarely a concern. If an application requires a large load current in a high temperature operating environment, there is the possibility that the over temperature protection circuit rather than the current limit circuit from one of the two outputs will regulate the current available to the load. In these applications, the maximum current available without risk of activation of the over temperature circuit can be calculated. The maximum internal temperature while current limit is not active can be calculated using Equation 1.

$$T_{J(MAX)} = I_{MAX}^2 \times R_{DS(ON)}(MAX) \times R_{\theta JA} + T_A(MAX)$$

In Equation 1,  $I_{MAX}$  is the maximum current required by the load.  $R_{DS(ON)}(MAX)$  is the maximum rated  $R_{DS(ON)}$  of the AAT4626 at high temperature.  $R_{\theta JA}$  is the thermal resistance between the device die and the board onto which it is mounted.  $T_A(MAX)$  is the maximum ambient temperature for

the printed circuit board assembly under the AAT4626 when the load switch is not dissipating power. Equation 1 can be transformed to provide  $I_{MAX}$ ; Refer to Equation 2.

$$I_{MAX} = \sqrt{\frac{T_{SD}(MIN) - T_{A}(MAX)}{R_{DS(ON)}(MAX) \times R_{\theta JA}}}$$

$T_{SD}(MIN)$  is the minimum temperature required to activate the device over temperature protection. The typical thermal limit temperature specification is 125°C for the AAT4626, for calculations, 115°C is a safe minimum value to use.

For example, a portable device is specified to operate in a 50°C environment. The printed circuit board assembly will operate at temperatures as high as 85°C. This portable device has a sealed case and the area of the printed board assembly is relatively small causing  $R_{\theta JA}$  to be approximately 100°C/W.  $R_{DS(ON)}(MAX) = 130W$ . Using Equation 2,

$$I_{MAX} = \sqrt{\frac{115^{\circ}\text{C} - 85^{\circ}\text{C}}{130\text{W} \times 120^{\circ}\text{C/W}}} = 1.4 \text{ A}$$

If this system requires less than 1.4 A, the thermal limit will not activate during normal operation.

#### **Input Capacitor**

The input capacitor serves two purposes. First, it protects the source power supply from transient current effects generated by the application load circuits. If a short circuit is suddenly applied to either output of an AAT4626, there is a microsecond long period during which a large current can flow before the current limit circuit becomes active. Refer to the characteristic curve named "Short Circuit Through  $0.3\Omega$ ." A properly sized input capacitor can dramatically reduce the load switch input transient response effects seen by the power supply and other circuitry upstream from the AAT4626.

The second purpose of the input capacitor is to prevent transient events generated by the load circuits from effecting the operation of the AAT4626. For example, if an AAT4626 is used in a circuit that operates from a 5 volt power supply with poor step load response, it is possible that turning on the load switch could cause the input power supply to droop below the AAT4626's under voltage lockout threshold. This drop in voltage would cause the AAT4626 to turn off until the input power supply voltage levels

recovers. Since this cycle would be self-perpetuating, the entire circuit could be seen to be unstable. In the very rare case where capacitor cost is prohibitive and the input capacitor is omitted, the output load circuit should be slew rate limited when turned on.

## **Output Capacitor**

In order to insure stability while the device current limit is active, a small capacitance of approximately 1µF should be used on each output. When either output of the AAT4626 is activated using the EN(A/B) function, there are no momentary current transients as in the case of when a short circuit suddenly applied to a device that is already on. Refer to the characteristic curve named "Turn-On/OFF Response". Regardless of output capacitor size, output current on either output is limited to the value allowed by the threshold determined by the internal current limit threshold specifications stated in the electrical characteristics section of this datasheet. This permits very large output capacitors to be used.

For example, USB ports are specified to have at least 120µF of down stream capacitance from their controlling power switch. An output capacitance as large as 1000µF would not disturb the input power supply to an AAT4626 used to control a USB port.

## **EN Inputs**

The AAT4626 has two enable inputs, ENA and ENB. These two enable inputs allow the AAT4626 to independently control each respective output. The device is available in both active high EN enable and active low (EN) enable versions. For specific part numbers, refer to the ordering information section. When both the A and B outputs of the AAT4626 are in the off state, the respective outputs are an open circuit and the device guiescent current consumption is reduced to less than 1µA. The ENA and ENB threshold voltages are set to allow the AAT4626 to be controlled by 5 volt TTL levels as well as CMOS compatible levels ranging from 2.5 volts to 5 volts. The ENA or ENB function control voltage levels should not exceed the input supply level applied to the IN pin.

#### **Fault Flag Output**

The AAT4626 features an active low fault flag (FLGA and FLGB) output for each A and B output channel. The fault flags are provided to alert the system if the over current or over temperature circuits become active or if the load switch is not receiving a sufficient voltage level to operate properly. If either the current limit or over temperature circuits in any combination are constantly active for more than approximately ten milliseconds, the FLG(A/B) pin is pulled to ground internally through an open drain device. The 10 millisecond delay on the fault function is intended to prevent capacitive loads connected to one of the load switch outputs from activating it's respective flag when the device is turned on. The placement of a pull up resistor between the FLGA or FLGB pin and the IN pin is recommended. Reasonable values for the pull up resistor should range from  $10k\Omega$  to  $100k\Omega$ . Since the fault flags are open drain terminals, they may be pulled up to any voltage that is not greater than the level present on the IN pin. This is done to allow the AAT4625 to signal ancillary circuitry that is powered by voltage levels less than the level on the IN pin.

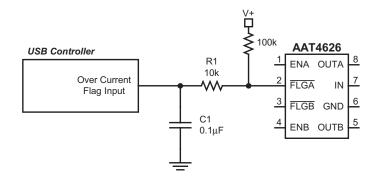

If a fault flag delay greater then 10ms is required, addition delay may be added by use of an RC filter. Referencing to Figure 1, an RC filter can be added to the fault flag output.

#### **Reverse Voltage**

The AAT4626 is designed to control current flowing from IN to OUT. If a voltage is applied to OUT which is greater than that on IN, a large resulting reverse current may flow, potentially damaging the AAT4626.

#### **Under Voltage Lockout**

The AAT4626 has been designed with an under voltage lockout (UVLO) control circuit. The under voltage lockout prevents the output MOSFET devices from turning on until VIN exceeds the typical UVLO threshold of 2.3 volts. During operation, the device will automatically shutdown if VIN falls below the UVLO threshold and the fault flags will be toggled.

Figure 1: Fault Flag delay RC filter.

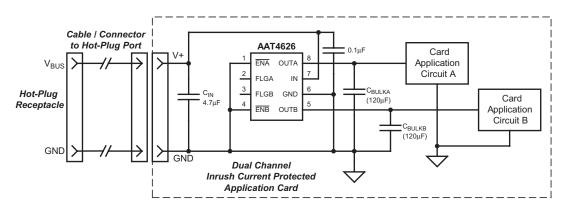

## **Hot-Plug Applications**

Application circuit cards with a high in-rush current potential can be limited by use of the AAT4626. The AAT4626 has both slew rate limited turn on characteristics and current limit controlled outputs, which make it ideally suited for power port hot-plug applications. A host power back plane or hot plug receptacle may be sensitive to short duration high

power surges. The AAT4626 will turn on in a linear ramping fashion and regulate the inrush current with in the specified current limit for the device. The error flag usually will not be effected during application turn on since the 10ms fault flag blanking time is intended for these types of events. If an application turn on current surge exceeds 10ms, an RC delay filter may be added to the Flag output to prevent the system from receiving an error during the start up sequence.

Figure 2: AAT4626 Input Inrush Current Protected Dual Output Application

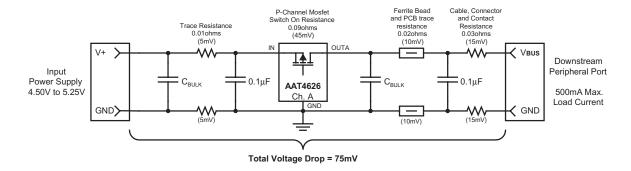

## **PCB Layout Information**

In order to obtain the maximum performance from the AAT4626, very careful attention must be considered in regard to the printed circuit board layout. In most port power switch and port protection applications, high voltage and current transient events will occur. Proper printed circuit board (PCB) layout can help reduce the effects of transient events. PCB trace resistance will effect over all circuit transient response, in addition small voltage drops will be incurred.

Refer to the following guidelines for power port PCB layout:

PCB traces should be kept as short and direct as possible to minimize the effects of the PCB on circuit performance.

- Make component solder pads large to minimize contact resistance

- The AAT4626 output bulk capacitors and ferrite beads should be placed as close to the device as possible. PCB traces to the output connector should be kept as short as possible to minimized trace resistance and the associated voltage drop (I2R loss).

- 4. If ferrite beads are used in the circuit, select ferrite beads with a minimum series resistance.

- The use of PCB trace vias should be avoided on all traces that conduct high currents. If vias are necessary, make the vias as large as possible and use multiple vias connected in parallel to minimize their effect.

Figure 3: Summary of typical circuit voltage drops caused by AAT4626 circuit components and PCB trace resistance.

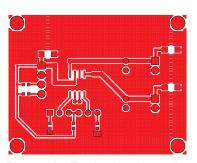

## **Evaluation Board Layout**

The AAT4626 evaluation layout follows the recommend printed circuit board layout procedures and can be used as an example for good application

layouts. Note that ferrite beards are not used on this simple device evaluation board. The board layout shown is not to scale.

Figure 4: Evaluation board component side layout

Figure 5: Evaluation board solder side layout

Figure 6: Evaluation board top side silk screen layout / assembly drawing

## **Application Circuits**

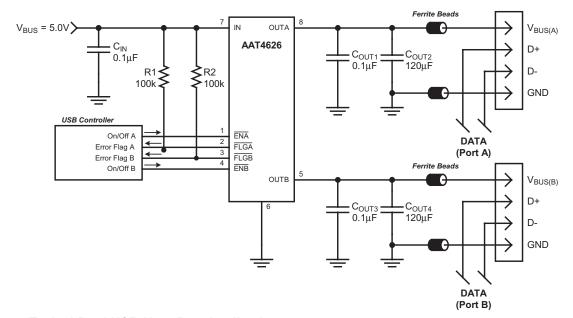

Figure 7: Typical Dual USB Host Port Application

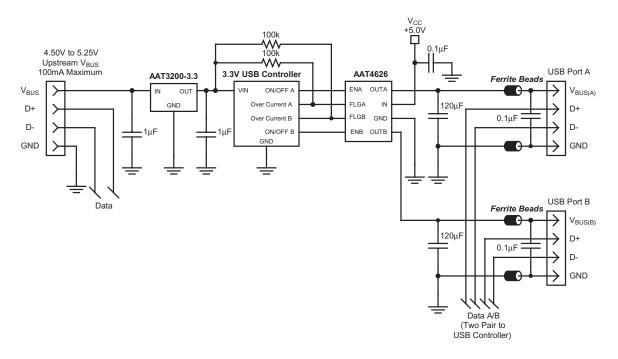

Figure 8: Self-Powered Dual Port USB Hub

Figure 9: USB Bus Powered Dual Port USB Hub

## **Ordering Information**

| Dookogo | Enable           | Marking | Part Number     |                 |  |

|---------|------------------|---------|-----------------|-----------------|--|

| Package |                  |         | Bulk            | Tape and Reel   |  |

| SOP8    | EN (Active-high) |         | AAT4626IAS-1-B1 | AAT4626IAS-1-T1 |  |

| SOP8    | EN (Active-low)  |         | AAT4626IAS-B1   | AAT4626IAS-T1   |  |

| TSSOP8  | EN (Active-high) |         | AAT4626IHS-1-B1 | AAT4626IHS-1-T1 |  |

| TSSOP8  | EN (Active-low)  |         | AAT4626IHS-B1   | AAT4626IHS-T1   |  |

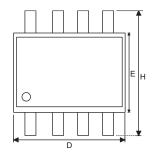

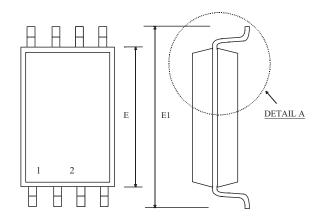

## **Package Information**

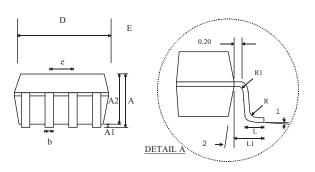

SOP-8

| Dim    | Millim | eters | Inches |       |  |

|--------|--------|-------|--------|-------|--|

|        | Min    | Max   | Min    | Max   |  |

| Α      | 1.35   | 1.75  | 0.053  | 0.069 |  |

| A1     | 0.10   | 0.25  | 0.004  | 0.010 |  |

| A2     | 1.4    | 5     | 0.0    | 0.057 |  |

| В      | 0.33   | 0.51  | 0.013  | 0.020 |  |

| С      | 0.19   | 0.25  | 0.007  | 0.010 |  |

| D      | 4.80   | 5.00  | 0.189  | 0.197 |  |

| Е      | 3.80   | 4.00  | 0.150  | 0.157 |  |

| е      | 1.27   |       | 0.050  |       |  |

| Н      | 5.80   | 6.20  | 0.228  | 0.244 |  |

| L      | 0.40   | 1.27  | 0.016  | 0.050 |  |

| Υ      | 0.00   | 0.10  | 0.000  | 0.004 |  |

| θ1     | 0°     | 8°    | 0°     | 8°    |  |

| NI - C |        |       |        |       |  |

#### Note:

- 1. PACKAGE BODY SIZES EXCLUDE MOLD FLASH PROTRUSIONS OR GATE BURRS.

- 2. TOLERANCE 0.1000mm (4mil) UNLESS

- OTHERWISE SPECIFIED

- 3. COPLANARITY: 0.1000mm

- 4. DIMENSION L IS MEASURED IN GAGE PLANE.

- 5. CONTROLLING DIMENSION IS MILLIMETER; CONVERTED INCH DIMENSIONS ARE NOT

NECESSARILY EXACT.

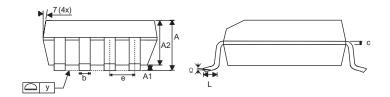

#### TSSOP-8

| D:   | Millimeters |      | Inches    |       |  |

|------|-------------|------|-----------|-------|--|

| Dim  | Min         | Max  | Min       | Max   |  |

| Α    | 1.05        | 1.20 | 0.041     | 0.047 |  |

| A1   | 0.05        | 0.15 | 0.002     | 0.006 |  |

| A2   | -           | 1.05 | -         | 0.041 |  |

| b    | 0.25        | 0.30 | 0.010     | 0.012 |  |

| С    | 0.12        | 27   | 0.00      | 0.005 |  |

| D-8  | 2.90        | 3.10 | 0.114     | 0.122 |  |

| D-28 | 9.60        | 9.80 | 0.378     | 0.386 |  |

| Е    | 4.30        | 4.50 | 0.170     | 0.177 |  |

| E1   | 6.20        | 6.60 | 0.244     | 0.260 |  |

| е    | 0.65 BSC    |      | 0.025 BSC |       |  |

| L    | 0.50        | 0.70 | 0.20      | 0.028 |  |

| L1   | 1.0         |      | 0.039     |       |  |

| R    | 0.09        | -    | 0.004     | -     |  |

| R1   | 0.09        | -    | 0.004     | -     |  |

| θ1   | 0°          | 8°   | 0°        | 8°    |  |

| θ2   | 12°         |      |           |       |  |

Advanced Analogic Technologies, Inc. 1250 Oakmead Parkway, Suite 310, Sunnyvale, CA 94086 Phone (408) 524-9684 Fax (408) 524-9689