S3049

#### **FEATURES**

- · 2.5 Gbps data rate

- Automatic Laser Power Control

- Laser Bias Enable Input

- Differential PECL Inputs

- Temperature Compensated Reference Voltage

- · Laser Fault and Fail indicators

- · Selectable on-chip Re-Clocking

- 60 mA Modulation Current, 90 mA Bias Current

- 32 Pin TQFP Package

### **APPLICATIONS**

- WDM for SONET OC-48

- OC-48 Fiber optic modules

- OC-48 Line termination equipment

### **GENERAL DESCRIPTION**

The S3049 has three main sections: a reference generator, a high speed current modulation driver, and a laser bias block with automatic power control.

The reference generator generates a temperature stabilized reference voltage,  $V_{\text{REF}}$ , which can be used to program the bias and the modulation currents.

The high-speed modulation driver can switch up to 60 mA swing through the laser. The CLKSEL pin can be used to select whether or not to re-clock the input data.

The laser bias block sets the bias current of the laser and has an Automatic Power Control (APC) system, which keeps the current through the laser constant by monitoring the current through the monitor photo-diode.

The APC loop is also used to detect excessive laser power and low laser power. These conditions are flagged on the LSFAULT and LSFAIL output pins respectively.

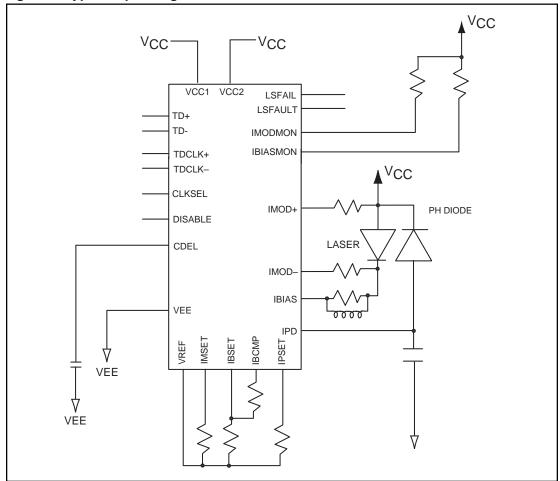

Figure 1. Typical Operating Circuit

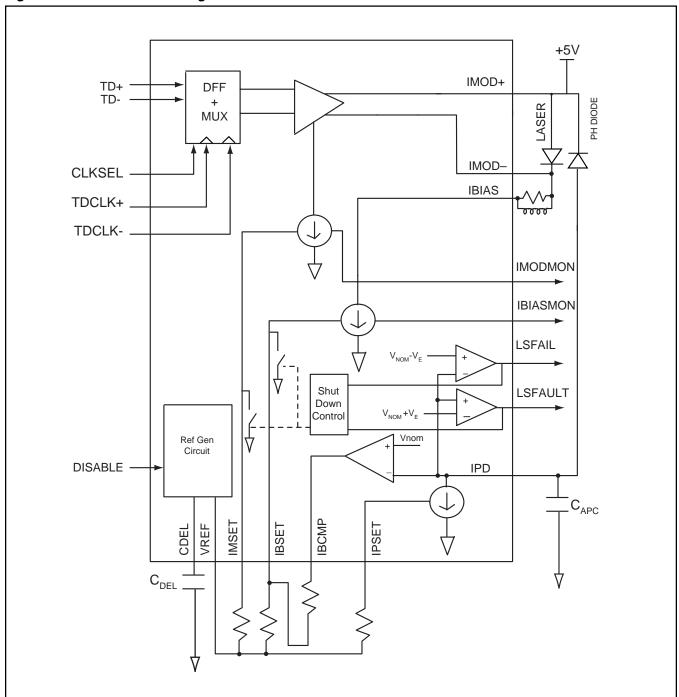

Figure 2. Functional Block Diagram

### **DETAILED DESCRIPTION**

### **Reference Generator**

The reference generator provides temperature compensated reference voltage, VREF, which is used to program the laser diode bias current,  $I_{BIAS}$ , the modulation current,  $I_{MOD}$ , and the photo-diode reference current,  $I_{PD}$ . The currents are set by connecting a resistor between VREF and the respective current source pin.

### Laser Bias Block with Automatic Power Control

The laser bias current,  $I_{BIAS}$ , is set by connecting a resistor between the IBSET pin and VREF. The current through the resistor is amplified by a gain factor,  $A_{IBSET}$ , to generate  $I_{BIAS}$ .

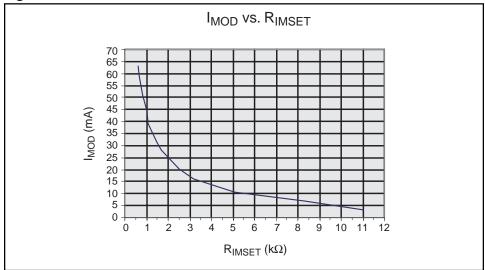

There is a feedback configuration to adjust the laser bias current to maintain constant laser power as laser efficiency changes with temperature and age. Light produced by the laser diode produces an average current in the monitor photo-diode. This current flows into the IPD pin. The IPSET current source, whose current is set by the IPSET resistor, draws current away from the IPD node. When the two currents are equal, the voltage at that node is set by the nominal reference voltage, V<sub>NOM</sub> of a differential amplifier. When the currents are not equal a voltage change is generated across the capacitor, CAPC which the differential amplifier translates to a voltage which generates a current through the IBCMP resistor. This current is summed with current through the IBSET resistor which adjusts IBIAS until the monitor photo-diode current equals the nominal monitor photo-diode current, IPD.

#### **Modulation Driver**

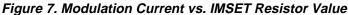

The modulation driver consists of a high speed input buffer and a differential output stage. The modulation current,  $I_{MOD}$ , is programmed by connecting a resistor between the IMSET pin and VREF.

The current through the resistor is amplified by a gain factor,  $A_{\text{IMSET}}$ , to generate  $I_{\text{MOD}}$ .

If the CLKSEL input is set Low, the data input, TD+/TD-, is clocked at the input by TDCLK to provide low jitter. If CLKSEL is High, TD+/TD- will be passed through to the modulation driver with no re-clocking.

### **Monitor Pins**

I<sub>BIAS</sub> and I<sub>MOD</sub> are mirrored and brought out on the IBIASMON and IMODMON pins respectively. The monitor currents are a specified fraction of the actual currents and are converted to a voltage by connecting the pins to VCC through a resistor.

### **FAULT Detection**

If the monitor photo-diode current increases beyond the point which can be controlled by the APC loop, the LSFAULT signal is asserted, indicating excessive laser power (a FAULT condition). This condition occurs when the voltage at the IPD node exceeds  $V_{\text{NOM}}$  by more than 400mv.

LSFAULT is also asserted if  $V_{REF}$  is detected to exceed 3.8V, as this will generate excessively high laser current.

#### **FAIL Detection**

If the monitor photo-diode current decreases beyond the point which can be controlled by the APC loop, LSFAIL is asserted, indicating low laser power (FAIL condition). This condition occurs when the voltage at the IPD pin drops below  $V_{NOM}$  by more than 400mv.

### **Laser Shutdown**

If a FAULT or FAIL condition is detected the laser bias and modulation currents will be turned off.

The laser can be enabled only by toggling the DIS-ABLE input or by initiating a power-on cycle. LSFAULT and LSFAIL will be reset on DISABLE deassert or  $V_{CC} > 4.4V$ .

If the CDEL pin is grounded, the shutdown of the laser currents on a FAULT or FAIL detection is disabled, and LSFAIL or LSFAULT will de-assert when the FAULT or FAIL condition no longer exists.

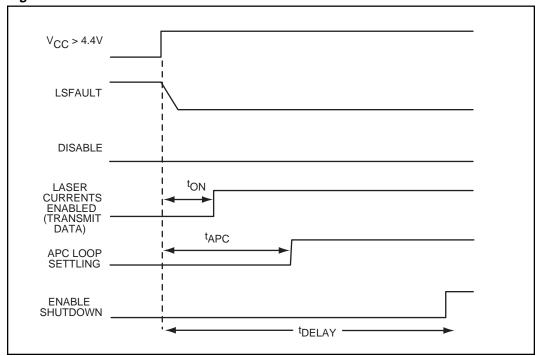

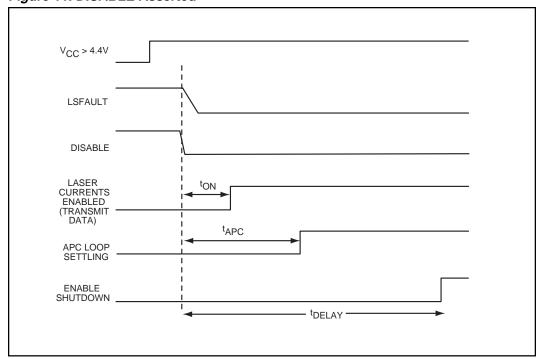

### Start-up Sequence

The laser bias and modulation currents are turned on within a time  $t_{ON}$  from when  $V_{CC}$  exceeds 4.4V or from when the DISABLE input is de-asserted. During the period  $t_{DELAY}$ , set by the capacitor  $C_{DEL}$ , the shutdown of the laser is disabled in order to allow the APC loop time to settle. During this time if a FAULT or FAIL condition is detected the laser will not be shut down as it could be caused by the APC loop transient state.  $C_{DEL}$  should be chosen such that  $t_{DELAY}$  is much longer than the APC loop settling time. LSFAULT and LSFAIL will not assert during  $t_{DELAY}$ .

### Table 1. Pin Assignment and Descriptions

| Pin Name | Level         | I/O | Pin # | Description                                                                                                                                                                                                                |

|----------|---------------|-----|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TD+      | Diff.<br>PECL | I   | 10    | Positive PECL Data Input.                                                                                                                                                                                                  |

| TD-      | Diff.<br>PECL | I   | 12    | Negative PECL Data Input.                                                                                                                                                                                                  |

| TDCLK+   | Diff.<br>PECL | I   | 14    | Positive clock input.                                                                                                                                                                                                      |

| TDCLK-   | Diff.<br>PECL | I   | 16    | Negative clock input.                                                                                                                                                                                                      |

| CLKSEL   | TTL           | I   | 9     | A Low selects re-clocking of TD+, TD A High will pass the data through without re-clocking.                                                                                                                                |

| DISABLE  | TTL           | I   | 17    | High level disables bias and modulation currents. If left open it will default to a low state.                                                                                                                             |

| CDEL     |               |     | 3     | A capacitor to ground sets the time for $t_{\rm DELAY}$ , the time during which laser shutdown is disabled after Disable is de-asserted or $V_{\rm CC} > 4.4 \rm V$ . If this pin is grounded, laser shutdown is disabled. |

| IMSET    |               |     | 24    | A resistor to VREF sets the modulation current. (See Figure 7.)                                                                                                                                                            |

| IBSET    |               |     | 23    | A resistor to VREF sets the bias current. (See Figure 6.)                                                                                                                                                                  |

| IPSET    |               |     | 6     | A resistor to VREF sets the monitor photo-diode reference current. (See Figure 8.)                                                                                                                                         |

| IBCMP    |               |     | 22    | A resistor to IBSET pin sets the maximum APC loop compensation bias current. (See Figure 9.)                                                                                                                               |

| IPD      | Current       | I   | 2     | Monitor photo-diode current input.                                                                                                                                                                                         |

| IMOD-    | Current       | 0   | 27    | Secondary Laser Modulation Current output. When TD+ is High, current is driven through this pin.                                                                                                                           |

| IMOD+    | Current       | 0   | 29    | Primary Laser Modulation Current output. When TD+ is Low, current is driven through this pin.                                                                                                                              |

### Table 1. Pin Assignment and Descriptions (Continued)

| Pin Name | Level             | I/O | Pin #      | Description                                                                                                                           |

|----------|-------------------|-----|------------|---------------------------------------------------------------------------------------------------------------------------------------|

| IBIAS    | Current           | 0   | 25         | Laser Bias Current output.                                                                                                            |

| LSFAULT  | Open<br>Collector | 0   | 8          | Active High output. Asserts when excessively high laser power is detected or $\rm V_{\rm REF}$ exceeds 3.8V.                          |

| LSFAIL   | Open<br>Collector | 0   | 7          | Active High output. Asserts when excessively low laser power is detected.                                                             |

| IMODMON  | Open<br>Collector | 0   | 20         | Modulation current monitor output. It can be used to monitor $I_{\text{MOD}}$ by connecting it to $V_{\text{CC}}$ through a resistor. |

| IBIASMON | Open<br>Collector | 0   | 19         | Bias current monitor output. It can be used to monitor $I_{\text{BIAS}}$ by connecting it to $V_{\text{CC}}$ through a resistor.      |

| VREF     |                   | 0   | 5, 21      | Temperature compensated reference.                                                                                                    |

| VCC1     |                   |     | 18         | Positve supply for low frequency circuitry.                                                                                           |

| VCC2     |                   |     | 31, 32     | Positve supply for high frequency circuitry.                                                                                          |

| VEE1     |                   |     | 4          | Ground for low frequency circuitry.                                                                                                   |

| VEE2     |                   |     | 1, 28, 30  | Ground for high frequency circuitry.                                                                                                  |

| VEE3     |                   |     | 26         | Ground for I <sub>BIAS</sub> circuitry.                                                                                               |

| VEE4     |                   |     | 11, 13, 15 | Ground for high frequency input shield.                                                                                               |

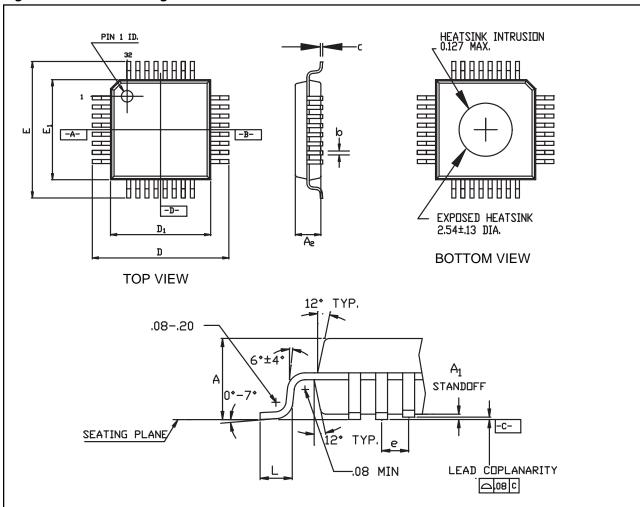

Figure 3. 32 TQPF Package

### DIMENSIONS (are in millimeters)

| UNIT | Α    | Aı   | A <sub>2</sub> | D    | $D_1$ | E    | E <sub>1</sub> | L    | b    | е                   | С             |

|------|------|------|----------------|------|-------|------|----------------|------|------|---------------------|---------------|

| MIN  |      | 0.05 | 1.35           | 6.80 | 4.90  | 6.80 | 4.90           | 0.50 | 0.17 |                     |               |

| NDM  |      |      | 1.40           | 7.00 | 5.00  | 7.00 | 5.00           | 0.60 | 0.22 | 0.50<br><b>BSC.</b> | 0.127<br>BSC. |

| MAX  | 1.60 | 0.15 | 1.45           | 7.20 | 5.10  | 7.20 | 5.10           | 0.75 | 0.27 |                     |               |

### Thermal Management

| Device | Max Power | ⊖ја     |

|--------|-----------|---------|

| S3049  | 0.64 W    | 70° C/W |

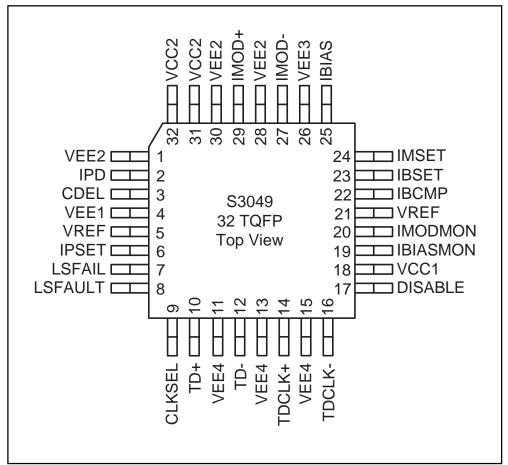

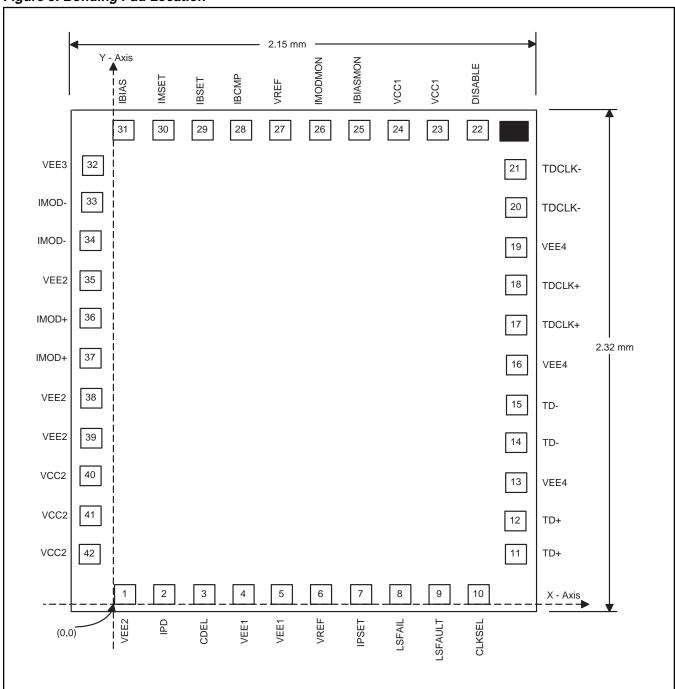

Figure 4. S3049 Pinout

Figure 5. Bonding Pad Location

Table 2. Pad Assignment and Description

| Pin Name | Level             | I/O | Pad #    | Coordinates [X,Y] <sup>1</sup>                                                                                      | Description                                                                                                                                                                                                                       |

|----------|-------------------|-----|----------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| TD+      | Diff. PECL        | I   | 11<br>12 | [1772.5, 247.375]<br>[1775.5, 419.375]                                                                              | Positive PECL Data Input.                                                                                                                                                                                                         |

| TD-      | Diff. PECL        | I   | 14<br>15 | [1772.5, 763.375]<br>[1772.5, 935.375]                                                                              | Negative PECL Data Input.                                                                                                                                                                                                         |

| TDCLK+   | Diff. PECL        | I   | 17<br>18 | [1772.5, 1279.375]<br>[1772.5, 1451.375]                                                                            | Positve Clock Input.                                                                                                                                                                                                              |

| TDCLK-   | Diff. PECL        | I   | 20<br>21 | [1772.5, 1795.375]<br>[1772.5, 1967.375]                                                                            | Negative Clock Input.                                                                                                                                                                                                             |

| CLKSEL   | TTL               | I   | 10       | [1592.375, 45]                                                                                                      | A Low selects re-clocking of TD+,<br>TD A High will pass the data<br>through without re-clocking.                                                                                                                                 |

| DISABLE  | TTL               | I   | 22       | [1592.625, 2170]                                                                                                    | High level disables Bias and Modulation currents. If left open it will default to a low state.                                                                                                                                    |

| CDEL     |                   |     | 3        | [388.375, 45]                                                                                                       | A capacitor ground sets the time for $t_{\text{DELAY}}$ , the time during which laser shutdown is disabled after DISABLE is de-asserted, or $V_{\text{CC}} > 4.4 \text{V}$ . If this pin is grounded, laser shutdown is disabled. |

| IMSET    |                   |     | 30       | [216.625, 2170]                                                                                                     | A resistor to VREF sets the Modulation current. (See Figure 7.)                                                                                                                                                                   |

| IBSET    |                   |     | 29       | [388.625, 2170]                                                                                                     | A resistor to VREF sets the Bias current. (See Figure 6.)                                                                                                                                                                         |

| IPSET    |                   |     | 7        | [1076.375, 45]                                                                                                      | A resistor to VREF sets the monitor photo-diode reference current. (See Figure 8.)                                                                                                                                                |

| IBCMP    |                   |     | 28       | [560.625, 2170]                                                                                                     | A resistor to IBSET pin sets the maximum APC loop compensation bias current. (See Figure 9.)                                                                                                                                      |

| IPD      | Current           | I   | 2        | [216.375, 45]                                                                                                       | Monitor photo-diode current input.                                                                                                                                                                                                |

| IMOD-    | Current           | 0   | 33<br>34 | [-180.5, 1795.625]<br>[-180.5, 1623.625]                                                                            | Secondary Laser Modulation Current output. When TD+ is High, current is driven through this pin.                                                                                                                                  |

| IMOD+    | Current           | 0   | 36<br>37 | [-180.5, 1279.625] [-180.5, 1107.625] Primary Laser Modulation output. When TD+ is Low, is driven through this pin. |                                                                                                                                                                                                                                   |

| IBIAS    | Current           | 0   | 31       | [44.625, 2170]                                                                                                      | Laser Bias Current output.                                                                                                                                                                                                        |

| LSFAULT  | Open<br>Collector | 0   | 9        | [1420.375, 45]                                                                                                      | Active High output. Asserts when excessively high laser power is detected or V <sub>REF</sub> exceeds 3.8V.                                                                                                                       |

Table 2. Pad Assignment and Description (Continued)

| Pin Name | Level             | I/O | Pad #               | Coordinates [X,Y] <sup>1</sup>                                            | Description                                                                                                                           |  |

|----------|-------------------|-----|---------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|

| LSFAIL   | Open<br>Collector | 0   | 8                   | [1248.375, 45]                                                            | Active High output. Asserts when excessively low laser power is detected.                                                             |  |

| IMODMON  | Open<br>Collector | 0   | 26                  | [904.625, 2170]                                                           | Modulation current monitor output. It can be used to monitor $I_{\text{MOD}}$ by connecting it to $V_{\text{CC}}$ through a resistor. |  |

| IBIASMON | Open<br>Collector | 0   | 25                  | [1076.625, 2170]                                                          | Bias current monitor output. It can be used to monitor $I_{\text{BIAS}}$ by connecting it to $V_{\text{CC}}$ through a resistor.      |  |

| VREF     |                   | 0   | 6<br>27             | [904.375, 45]<br>[732.625, 2170]                                          | Temperature compensated reference.                                                                                                    |  |

| VCC1     |                   |     | 23<br>24            | [1420.625, 2170]<br>[1248.625, 2170]                                      | Positive supply for low frequency circuitry.                                                                                          |  |

| VCC2     |                   |     | 40<br>41<br>42      | [-180.5, 591.625]<br>[-180.5, 419.625]<br>[-180.5, 247.625]               | Positive supply for high frequency circuitry.                                                                                         |  |

| VEE1     |                   |     | 4<br>5              | [560.375, 45]<br>[732.375, 45]                                            | Ground for low frequency circuitry.                                                                                                   |  |

| VEE2     |                   |     | 1<br>35<br>38<br>39 | [44.375, 45]<br>[180.5, 1451.625]<br>[180.5, 935.625]<br>[180.5, 763.625] | Ground for high frequency circuitry.                                                                                                  |  |

| VEE3     |                   |     | 32                  | [-180.5, 1967.625]                                                        | Ground for I <sub>BIAS</sub> circuitry.                                                                                               |  |

| VEE4     |                   |     | 13<br>16<br>19      | [1772.5, 591.375]<br>[1772.5, 1107.375]<br>[1772.5, 1623.375]             | Ground for high frequency input shield.                                                                                               |  |

### Notes

<sup>1.</sup> The coordinates represent the position of the center of the pad, in  $\mu m$ , with respect to the lower left corner of Pad 1.

<sup>2.</sup> Pad size: 90 x 90  $\mu$ m.

Table 3. Absolute Maximum Ratings

| Parameter                                      | Min                | Тур | Max             | Units |

|------------------------------------------------|--------------------|-----|-----------------|-------|

| Storage temperature range                      | -55                |     | +175            | °C    |

| Processing temperature                         |                    |     | +400            | °C    |

| Voltage on V <sub>cc</sub> with respect to GND | -0.5               |     | +5.5            | V     |

| Voltage on any TTL input pin                   | -0.5               |     | +5.5            | V     |

| Voltage on any PECL input pin                  | V <sub>cc</sub> -2 |     | V <sub>cc</sub> | V     |

| ESD Sensitivity <sup>1</sup>                   | 300                |     |                 | V     |

<sup>1.</sup> Human body model.

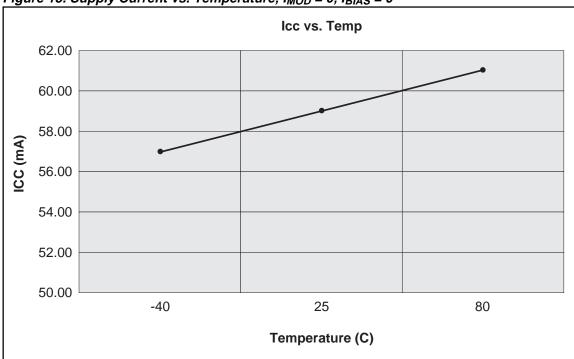

### Table 4. Power and References

(VCC-VEE =  $5V\pm5\%$ , TA =  $-40^{\circ}$ C to  $85^{\circ}$ C,  $25^{\circ}$  C for die)

| Parameter        | Description       | Min | Тур | Max | Units | Conditions                                 |

|------------------|-------------------|-----|-----|-----|-------|--------------------------------------------|

| I <sub>cc</sub>  | Supply Current    |     |     | 76  | mA    | $I_{MOD} = 0, I_{BIAS} = 0, R_{LOAD} = 25$ |

| V <sub>REF</sub> | Reference Voltage |     | 3.3 |     | V     |                                            |

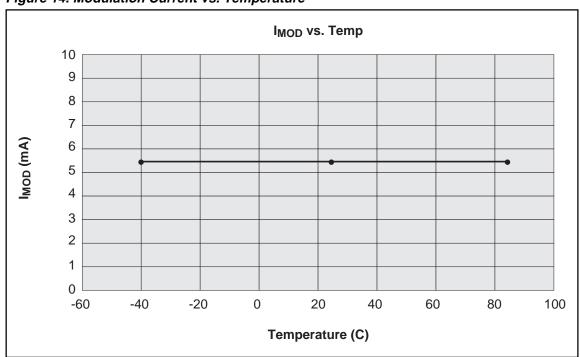

Table 5. Laser Modulation (R $_{LOAD}$  = 25 $\Omega$ ) (VCC-VEE = 5V±5%, TA = -40°C to 85°C, 25° C for die)

| Parameter                                | Description                                          | Min                  | Тур | Max | Units | Conditions                                                       |

|------------------------------------------|------------------------------------------------------|----------------------|-----|-----|-------|------------------------------------------------------------------|

| I <sub>MOD</sub>                         | Range of programmable<br>Laser Modulation<br>Current | 1                    |     | 60  | mA    |                                                                  |

| $T_{r,}T_{f}$                            | Modulation Current Rise and Fall Time                |                      |     | 150 | ps    | I <sub>MOD</sub> = 30mA, I <sub>BIAS</sub> = 50mA,<br>20% to 80% |

| F <sub>max</sub>                         | Maximum Operating Frequency                          | 2.5                  |     |     | Gbps  |                                                                  |

| PWD                                      | Modulation current pulse width distortation          |                      |     | 40  | ps    | $I_{MOD} = 30$ mA, $I_{BIAS} = 50$ mA                            |

| V <sub>IMSET</sub>                       | IMSET Pin Voltage                                    |                      | 1.5 |     |       | T <sub>A</sub> = 25° C                                           |

| A <sub>IMSET</sub>                       | I <sub>MOD</sub> Current Source<br>Gain              |                      | 32  |     |       |                                                                  |

| V <sub>IMOD</sub>                        | IMOD, IMOD- Pin<br>minimum voltage<br>requirement    | V <sub>cc</sub> -2.5 |     |     | V     |                                                                  |

| I <sub>MOD</sub> V                       | Modulation current drift over full voltage range     |                      |     | 4   | %     |                                                                  |

| I <sub>MOD</sub> T                       | Modulation current drift over temperature            |                      |     | 4   | %     |                                                                  |

| V <sub>IMODMON</sub>                     | IMODMON Pin<br>minimum voltage<br>requirement        | V <sub>cc</sub> -3   |     |     | V     |                                                                  |

| I <sub>MOD/</sub><br>I <sub>MODMON</sub> | Ratio $I_{\text{MOD}}$ to $I_{\text{MODMON}}$        |                      | 32  |     |       |                                                                  |

### Table 6. Laser Bias

(VCC-VEE =  $5V\pm5\%$ , TA =  $-40^{\circ}$ C to  $85^{\circ}$ C,  $25^{\circ}$ C for die)

| Parameter           | Description                                          | Min                | Тур | Max | Units | Conditions             |

|---------------------|------------------------------------------------------|--------------------|-----|-----|-------|------------------------|

| I <sub>BIAS</sub>   | Range of programmable<br>Laser Bias current          | 1                  |     | 50  | mA    |                        |

| V <sub>IBSET</sub>  | IBSET pin voltage                                    |                    | 1.5 |     | V     | T <sub>A</sub> = 25° C |

| A <sub>IBIAS</sub>  | I <sub>BIAS</sub> Current Source gain                |                    | 50  |     |       |                        |

| V <sub>IBIAS</sub>  | I <sub>BIAS</sub> pin minimum voltage requirement    | 1                  |     |     | V     |                        |

| V <sub>IBIASM</sub> | I <sub>BIASMON</sub> pin minimum voltage requirement | V <sub>cc</sub> -3 |     |     | V     |                        |

| I <sub>BIAS</sub> / | Ratio I <sub>BIAS</sub> to I <sub>BIASMON</sub>      |                    | 50  |     |       |                        |

### Table 7. Automatic Power Control

(VCC-VEE =  $5V\pm5\%$ , TA =  $-40^{\circ}$ C to  $85^{\circ}$ C,  $25^{\circ}$ C for die)

| Parameter          | Description                                                             | Min | Тур | Max | Units | Conditions             |

|--------------------|-------------------------------------------------------------------------|-----|-----|-----|-------|------------------------|

| V <sub>IPSET</sub> | IPSET Pin Voltage                                                       |     | 1.5 |     | V     | T <sub>A</sub> = 25° C |

| A <sub>IPD</sub>   | I <sub>PD</sub> Current Souce Gain                                      |     | 1   |     |       |                        |

| I <sub>PD</sub>    | Range of monitor photo diode current                                    | 20  |     | 900 | μA    |                        |

| I <sub>BCMP</sub>  | Maximum Compensation Bias current generated by APC circuit (up or down) | 40  |     |     | mA    |                        |

### Table 8. Power Initialization and Latched Shutdown

(VCC-VEE =  $5V\pm5\%$ , TA =  $-40^{\circ}$ C to  $85^{\circ}$ C,  $25^{\circ}$ C for die)

| Parameter           | Description                                                                                | Min | Тур | Max | Units | Conditions                 |

|---------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|-------|----------------------------|

| VCCI <sub>ON</sub>  | Internal power turn-on threshold                                                           |     | 4.4 |     | V     |                            |

| VCCI <sub>OFF</sub> | Internal power turn-off threshold                                                          |     | 4.3 |     | V     |                            |

| t <sub>DELAY</sub>  | Programmable delay for disabling laser shutdown after Vcc > 4.4V or Disable deasserted     | 1   |     | 20  | ms    |                            |

| t <sub>on</sub>     | Laser currrent turn on delay from DISABLE de-assert                                        |     |     | 1   | μS    |                            |

| t <sub>reset</sub>  | Minimum DISABLE assert time (or power-off time) required to discharge C <sub>DEL</sub> cap | 100 |     |     | μS    | C <sub>DEL</sub> = 0.1 μF. |

### Table 9. PECL and TTL Input/Outputs

$(VCC-VEE = 5V\pm5\%, TA = -40^{\circ}C \text{ to } 85^{\circ}C, 25^{\circ}C \text{ for die})$

| Parameter        | Description                                                | Min                  | Тур | Max                  | Units | Conditions               |

|------------------|------------------------------------------------------------|----------------------|-----|----------------------|-------|--------------------------|

| V <sub>IN</sub>  | Single-ended Input<br>Voltage Swing<br>(TD ±, TDCLK ±)     | 250                  |     | 1400                 | mv    |                          |

| V <sub>CM</sub>  | Differential Input<br>Common Mode range<br>(TD ±, TDCLK ±) | V <sub>cc</sub> -1.5 |     | V <sub>cc</sub> -1.1 | V     |                          |

| V <sub>IL</sub>  | TTL Input Low Voltage                                      |                      |     | VEE +0.8             | V     |                          |

| V <sub>IH</sub>  | TTL Input High Voltage                                     | V <sub>cc</sub> -3   |     |                      | V     |                          |

| V <sub>oc</sub>  | Open Collector Outputs,<br>Low Voltage                     |                      |     | 0.5                  | V     | $I_{OUT} = 1 \text{ mA}$ |

| tS <sub>TD</sub> | TD+/TD- Setup time w.r.t. clock                            | 70                   |     |                      | ps    |                          |

| tH <sub>TD</sub> | TD+/TD- Hold time w.r.t. clock                             | 10                   |     |                      | ps    |                          |

### **Resistor and Capacitor Values**

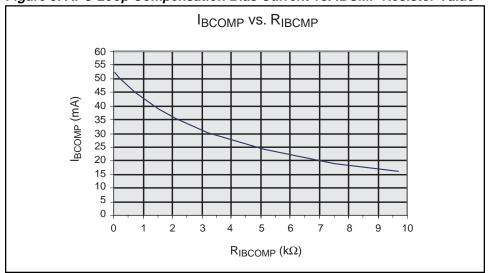

The resistors and capacitors can be selected using the following plots and formula.

I<sub>BIAS</sub> vs. R<sub>IBSET</sub> 70 65 60 55 50 45 40 35 30 25 20 15 I<sub>BIAS</sub> (mA) 10 5 0  $R_{IBSET}(k\Omega)$

Figure 6. Bias Current vs. IBSET Resistor Value

Figure 8. Photo Diode Current vs. IPSET Resistor Value

Figure 9. APC Loop Compensation Bias Current vs. IBCMP Resistor Value

Programming t<sub>DELAY</sub>

$$t_{DELAY} = (100k\Omega) (C_{DEL})$$

### **Timing for Start Up Sequence**

Figure 10. DISABLE Unasserted

Figure 11. DISABLE Asserted

### APPLICATION INFORMATION

### **Power Dissipation Across Device**

The power dissipation in the package must be kept below 640mW. Quiescent power is 399mW. Therefore, power dissipation due to the laser currents must be kept below 240mW.

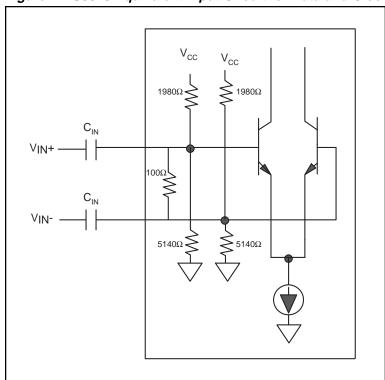

### Connecting to the Input of S3049

The equivalent input circuit of S3049 is shown in Figure 12. Both DC biasing and 50 ohm line termination have been implemented internally.

Figure 12. S3049 Equivalent Input Circuit for Data and Clock

### **Typical Operating Characteristics**

Figure 14. Modulation Current vs. Temperature

100 mV/DIV

50 ps/DIV

Figure 15. Eye Diagram, I<sub>MOD</sub> = 30mA, 2.5 Gbps, 2<sup>23</sup>–1 Pattern

### Ordering Information

| PREFIX                 | DEVICE                         | PACKAGE                    |

|------------------------|--------------------------------|----------------------------|

| S – Integrated Circuit | 3049                           | A – 32 Pin TQFP<br>B – Die |

|                        | X XXXX X Prefix Device Package | e                          |

# Applied Micro Circuits Corporation • 6290 Sequence Dr., San Diego, CA 92121 Phone: (858) 450-9333 • (800) 755-2622 • Fax: (858) 450-9885 http://www.amcc.com

AMCC reserves the right to make changes to its products or to discontinue any semiconductor product or service without notice, and advises its customers to obtain the latest version of relevant information to verify, before placing orders, that the information being relied on is current.

AMCC does not assume any liability arising out of the application or use of any product or circuit described herein, neither does it convey any license under its patent rights nor the rights of others.

AMCC reserves the right to ship devices of higher grade in place of those of lower grade.

AMCC SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, INTENDED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT APPLICATIONS, DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS.

AMCC is a registered trademark of Applied Micro Circuits Corporation.

Copyright ® 1999 Applied Micro Circuits Corporation