## INTRODUCTION

The S1M8653B is a baseband analog processing IC for dual-mode CDMA/FM portable cellular telephones. The S1M8653B interfaces between the analog RF and digital processing sections of the cellular phone. The receive circuit functions primarily to translate analog IF signals to the baseband frequency range and convert analog baseband signals into digital signals. Transmit circuits convert digital data into analog baseband signals which are then up-converted to the IF frequency band. The analog inputs and outputs of the S1M8653B interface with IF transmit/receive circuitry of telephones; the digital inputs and outputs interface directly with the Mobile Station Modem (MSM).

## FEATURES

- Dual-mode for CDMA/FM operation

- Receive signal path includes:

- IF to baseband down converter

- Built-in low pass filter

- Two 4-bit ADCs

- Local Oscillator

- General purpose 8-bit ADC for system monitoring

- Power saving modes

- Single 3.3V power supply

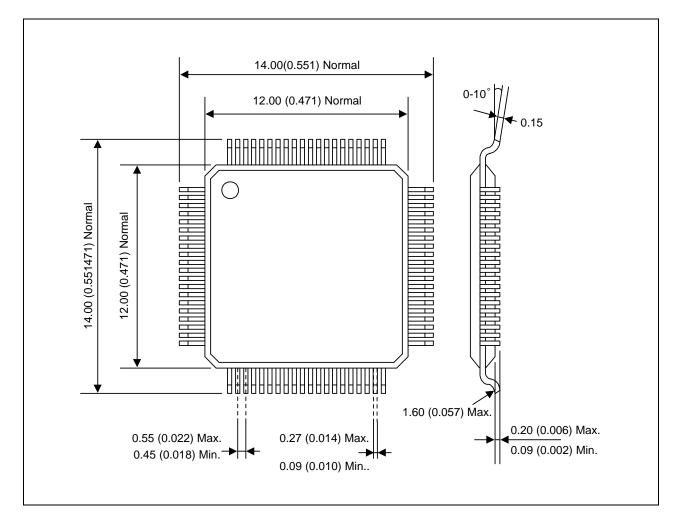

- 80 pin LQFP package

- S1M8653BQ: CDMA/FM Dual

## **APPLICATIONS**

• Dual-mode CDMA/FM cellular telephones

## **ORDERING INFORMATION**

| Device    | Package     | Operating Temperature |

|-----------|-------------|-----------------------|

| S1M8653BQ | 80-QFP-1212 | -40 to +85°C          |

- 80-LQFP-1212

- Transmit signal path includes:

- Two 8-bit DACs

- Base-band to IF up converter

- Local Oscillator

- Built-in low pass filter

## SYSTEM BLOCK DIAGRAM

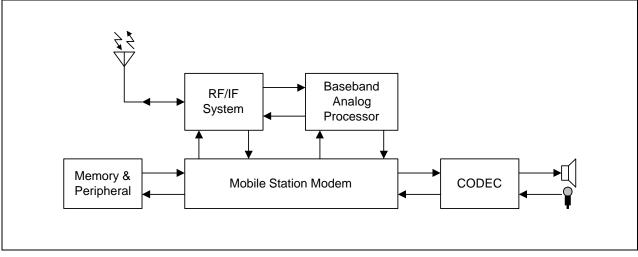

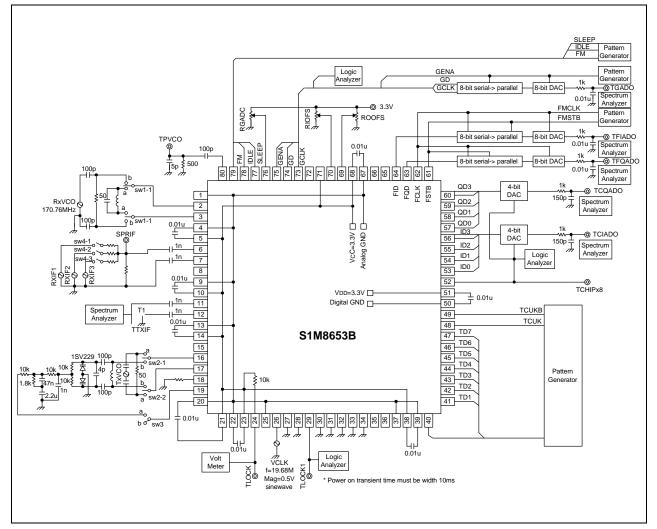

Figure 1. Dual Mode CDMA/FM Cellular Telephone Block

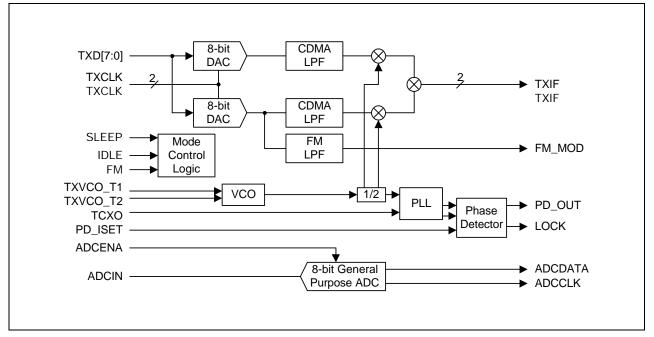

### **BLOCK DIAGRAM**

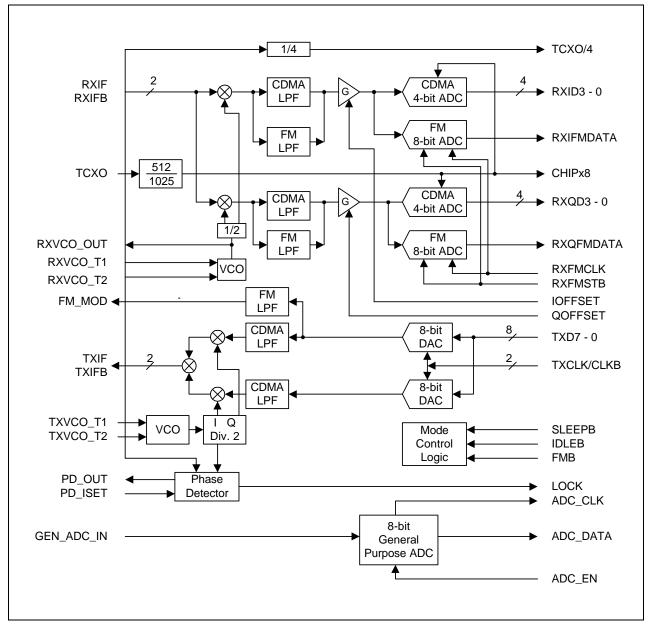

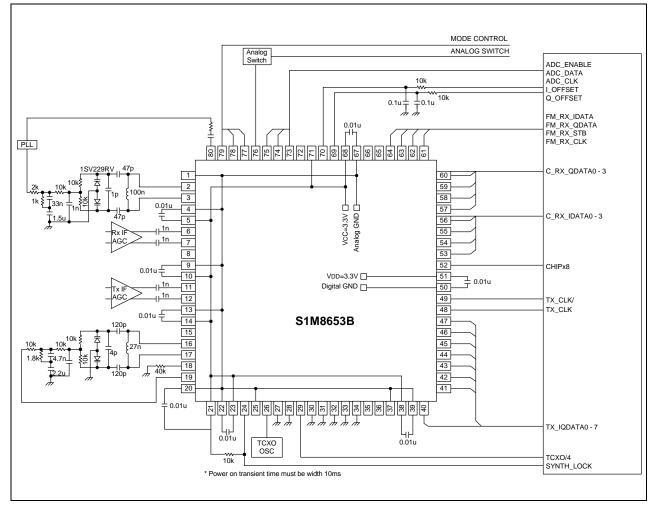

Figure 2. Block Diagram

### **PIN CONFIGURATION**

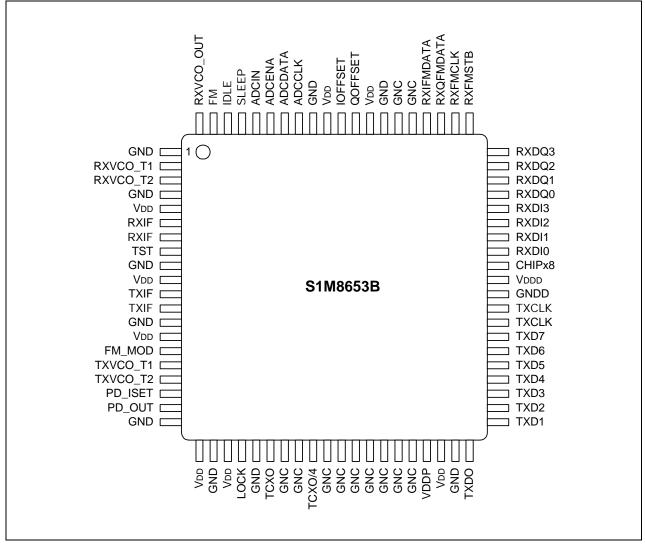

Figure 3. Pin Configuration

# **PIN DESCRIPTION**

| Pin No.  | Symbol   | Туре | Equivalent Circuit | Description                                                                                                                                                               |

|----------|----------|------|--------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1,4,9,13 | GND      | Р    |                    | Analog Ground                                                                                                                                                             |

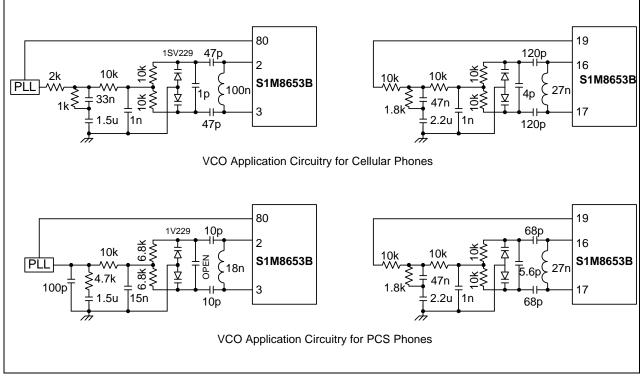

| 2        | RXVCO_T1 | Ι    |                    | The receive VCO tuning pins connect to an external LC tank circuit for precise setting of the receive VCO frequency. The receive VCO is active in RXTX and IDLE modes for |

| 3        | RXVCO_T2 | -    |                    | CDMA and FM. In SLEEP mode, these pins are pulled high.                                                                                                                   |

| 5,10,14  | VDD      | Р    |                    | Analog Power (+3.3V).                                                                                                                                                     |

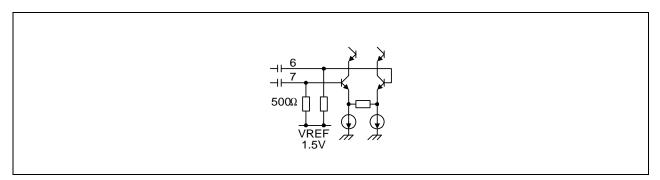

| 6        | RXIF     | Ι    |                    | Analog differential receive IF inputs. These<br>pins are active in RXTX and IDLE modes<br>for CDMA and FM. In SLEEP mode, these<br>pins are pulled low.                   |

| 7        | RXIF     | Ι    |                    |                                                                                                                                                                           |

| 8        | TST      | I    |                    | This pin is used during testing. Connect to analog GND.                                                                                                                   |

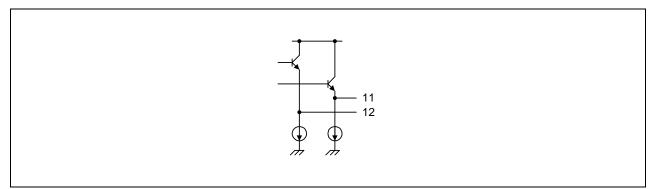

| 11       | TXIF     | 0    |                    | Analog differential transmit IF outputs.<br>These pins are active in CDMA and FM<br>RXTX modes. In all other modes, these<br>pins are pulled high.                        |

| 12       | TXIF     | Ο    |                    |                                                                                                                                                                           |

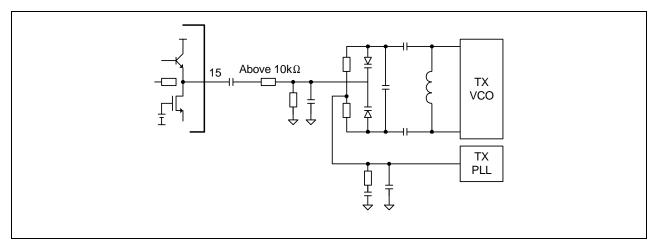

| 15       | FM_MOD   | 0    |                    | Analog FM modulation signal output. It is<br>active in FM RXTX mode only.<br>When inactive, it is pulled low.                                                             |

| Pin No.  | Symbol          | Туре | Equivalent Circuit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | Description                                                                                                                                                                                                                           |

|----------|-----------------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 16       | TXVCO_T1        |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | The transmit VCO tuning pins connect to<br>an external LC tank circuit for precise<br>setting of the transmit VCO frequency. The<br>transmit VCO is active in CDMA and FM<br>RXTX modes.<br>In all other modes, these pins are pulled |

|          |                 |      | in the second se | high.                                                                                                                                                                                                                                 |

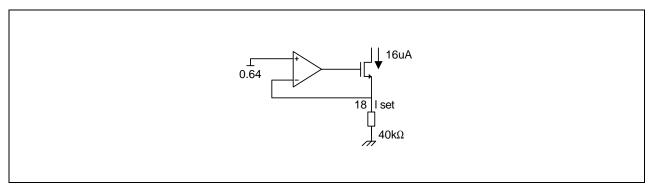

| 18       | PD_ISET         | I    | 0.64                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Sets PD_OUT current level.                                                                                                                                                                                                            |

| 19       | PD_OUT          | 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Transmit synthesizer phase detector<br>charge pump output. When inactive, goes<br>to high impedance state.                                                                                                                            |

| 20,22,25 | GND             | Р    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Analog Ground.                                                                                                                                                                                                                        |

| 21,23    | V <sub>DD</sub> | Р    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Analog Power.                                                                                                                                                                                                                         |

| 24       | LOCK            | 0    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Transmit IF synthesizer lock detector<br>output. Active in CDMA and FM RXTX<br>modes. LOCK is an open drain, pulled high<br>by an external pull-up resistor when<br>inactive.                                                         |

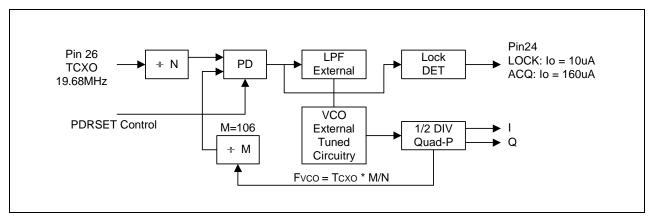

| 26       | тсхо            | Ι    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | An externally generated 19.68MHz clock<br>frequency is applied to this pin. It is active<br>in all modes.                                                                                                                             |

| Pin No.                         | Symbol          | Туре | Equivalent Circuit                                                                  | Description                                                                                                                                                                                                                                                                                                                                           |

|---------------------------------|-----------------|------|-------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27, 28                          | GNC             | -    |                                                                                     | These pins are used during testing.<br>Connect to analog GND.                                                                                                                                                                                                                                                                                         |

| 29                              | TCXO/4          | 0    | 29<br>                                                                              | A clock frequency equal to 1/4 of the TCXO frequency is output on this pin in all operating modes.                                                                                                                                                                                                                                                    |

| 30,31,32,3<br>3,34,35,36,<br>37 | GND             | Ρ    |                                                                                     | These pins are used during testing.<br>Connect to analog GND.                                                                                                                                                                                                                                                                                         |

| 38                              | V <sub>DD</sub> | Р    |                                                                                     | Digital Power.                                                                                                                                                                                                                                                                                                                                        |

| 39                              | GND             | Р    |                                                                                     | Digital GND.                                                                                                                                                                                                                                                                                                                                          |

| 40–47                           | TXD0-TXD7       | I    |                                                                                     | Transmit data input pins for transmit 8-bit D/A converter TXD7 is the MSB.                                                                                                                                                                                                                                                                            |

| 48                              | TXCLK           | I    | $\begin{array}{c c} 43 \\ 44 \\ 45 \\ 46 \\ 46 \\ 46 \\ 46 \\ 46 \\ 46 \\ 46 \\ 46$ | Complementary inputs to transmit D/A converter.                                                                                                                                                                                                                                                                                                       |

| 49                              | TXCLK           | I    | 47<br>48<br>49                                                                      |                                                                                                                                                                                                                                                                                                                                                       |

| 50                              | GND             | Р    |                                                                                     | Digital Ground.                                                                                                                                                                                                                                                                                                                                       |

| 51                              | V <sub>DD</sub> | Р    |                                                                                     | Digital Power.                                                                                                                                                                                                                                                                                                                                        |

| 52                              | CHIPx8          | 0    |                                                                                     | The CHIPx8 synthesizer is a digital divider<br>with a ratio of 512/1025 times the TCXO<br>input frequency. As such, it will have an<br>average output frequency of 9.8304MHz,<br>but will not have an exact 50% duty cycle.<br>When the CHIPx8 synthesizer is disabled<br>(CDMA SLEEP and FM RX modes) the<br>CHIPx8 signal is pulled to a logic low. |

| Pin No. | Symbol          | Туре | Equivalent Circuit | Description                                                                                                                                                                             |

|---------|-----------------|------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 53–56   | RXDI0-RXDI3     | 0    |                    | CDMA I receive data is output to the MSM<br>on this 4-bit port. RXDI3 is the MSB.<br>Active in CDMA RXTX and CDMA IDLE,<br>otherwise logic low.<br>CDMA Q receive data is output to the |

| 57-60   | RXDQ0-RXDQ3     | 0    |                    | MSM on this 4-bit port. RXDQ3 is the<br>MSB. Active in CDMA RXTX and CDMA<br>IDLE, otherwise logic low.                                                                                 |

| 61      | RXFMSTB         | I    |                    | Receive FM data strobe. Active in FM<br>RXTX and FM IDLE modes. Pulled high if<br>left unconnected.                                                                                     |

| 62      | RXFMCLK         | I    |                    | Receive FM data clock. Active in FM<br>RXTX and FM IDLE modes. Pulled high if<br>left unconnected.                                                                                      |

| 63      | RXQFMDATA       | 0    |                    | Receive FM Q serial data output. Active in FM RXTX and FM IDLE modes. High when inactivated.                                                                                            |

| 64      | RXIFMDATA       | 0    |                    | Receive FM I serial data output. Active in FM RXTX and FM IDLE modes. High when inactivated.                                                                                            |

| 65, 66  | GNC             | Ι    |                    | These pins are used during testing.<br>Connect to analog ground                                                                                                                         |

| 67      | GND             | Р    |                    | Analog Ground.                                                                                                                                                                          |

| 68      | V <sub>DD</sub> | Р    |                    | Analog Power.                                                                                                                                                                           |

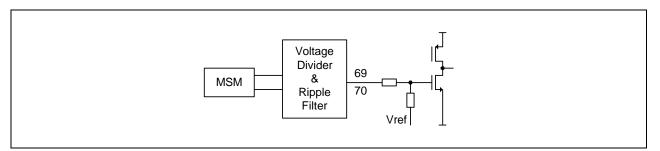

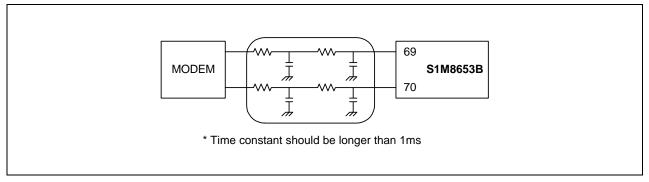

| 69      | QOFFSET         | Ι    |                    | Q channel offset adjust input for CDMA<br>and RXTX and IDLE modes. The MSM<br>derives a PDM signal which is filtered by<br>an external RC at the pin.                                   |

| 70      | IOFFSET         | Ι    | 70<br>VREF         | I channel offset adjust input for CDMA and<br>RXTX and IDLE modes. The MSM derives<br>a PDM signal which is filtered by an<br>external RC at the pin.                                   |

| Pin No. | Symbol          | Туре | Equivalent Circuit   | Description                                                                                                                                   |

|---------|-----------------|------|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|

| 71      | V <sub>DD</sub> | Р    |                      | Analog Power.                                                                                                                                 |

| 72      | NC              |      |                      | No connection.                                                                                                                                |

| 73      | ADCCLK          | 0    |                      | General Purpose ADC clock output. When<br>high, valid data is available on ADCDATA.<br>Low when inactive.                                     |

| 74      | ADCDATA         | 0    |                      | General Purpose ADC serial data output.<br>Valid data is available when ADCCLK is<br>high. Low when inactive.                                 |

| 75      | ADCENA          | I    | Т                    | The General Purpose ADC is enabled and<br>a conversion is initiated by a positive-<br>going pulse on this input. Pulled low when<br>inactive. |

| 76      | ADCIN           | I    | 75<br>77<br>78<br>79 | General Purpose A/D analog input. The voltage applied to this input is digitized by 8-bit general Purpose ADC when ADCENA is pulsed high.     |

| 77      | SLEEP           | I    |                      | CDMA SLEEP mode is invoked when this<br>pin is low and FM is high. Pulled low if left<br>unconnected.                                         |

| 78      | IDLE            | I    |                      | CDMA IDLE or FM IDLE modes are<br>invoked when this input is low and SLEEP<br>is high. Pulled low if left unconnected.                        |

| 79      | FM              | I    |                      | FM or CDMA mode select. Pulled low if left unconnected.                                                                                       |

| 80      | RXVCO_OUT       | 0    |                      | Receive VCO output. Active in CDMA and<br>FM RXTX and IDLE modes. Pulled low<br>when inactive.                                                |

### FUNCTIONAL DESCRIPTION

The Samsung S1M8653B is an IC that bridges the gap between the analog RF and digital processing sections of the cellular telephone as shown in Figure 1. The S1M8653B receive signal path translates the acquired IF signal centered at 85.38 MHz (or 220.38MHz) to base-band where it is then converted to digital data. The digital baseband signals are sent to the MSM for demodulation. When transmitting, the MSM sends modulated digital baseband signals to the S1M8653B for up conversion to analog IF signals centered at 130.38MHz.

The MSM handles various digital data according to the CDMA/AMPS standards. It directly interfaces with the RF/IF sections of the telephone for automatic gain control (AGC) and calibration of the RF signal paths for receive and transmit. In addition, the MSM performs other miscellaneous digital processing in the CDMA/FM cellular telephone.

### **RECEIVE SIGNAL PATH**

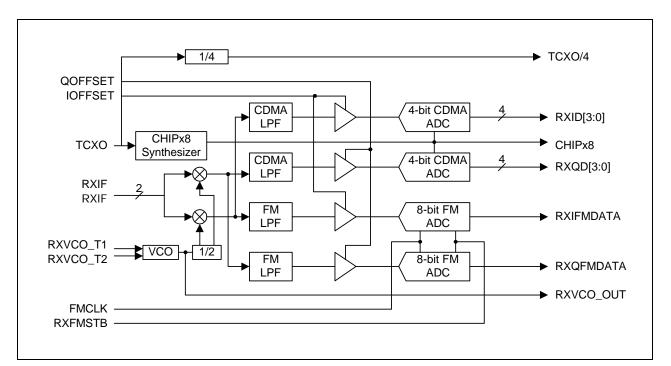

The S1M8653B receive signal path(see Figure 3) is designed to accept differential IF signals with CDMA spread spectrum modulation extending  $\pm$  630kHz from the IF center frequency of 85.38MHz(or 220.38MHz). The incoming IF signal is reduced to I and Q base-band components by mixing with 85.38MHz local oscillator (LO) signals in quadrature followed by low pass filtering.

The 85.38MHz I and Q LO signals are generated on the S1M8653B. The receive VCO is set to 170.76MHz (or 440.76MHz) by an external varactor tuned resonant tank circuit (inductor L and capacitor C connected in parallel). An external phase lock loop and loop filter network provide the feedback to varactors which tune the VCO to

170.76MHz. A master-slave divide-by-two circuit generates I and Q signals in precise quadrature for the mixers.

The receive signal path splits into CDMA and FM sections from the mixer output. For CDMA, the base-band signal extends from 1kHz to 630kHz. Frequency components above 750kHz are out-of-band for CDMA operation. The mixers and the subsequent CDMA low-pass filters combine to form the down converter which outputs the CDMA base-band signals. The pass-band, transition band, and rejection band characteristics of these low pass filters, in conjunction with external IF band-pass filtering, contribute to the ability of the receiver to select the desired base-band signals from the jamming effects of unwanted signals.

The offset control inputs, IOFFSET and QOFFSET, are used to control the offset at the inputs of the ADCs. The MSM senses the offset of the digital base-band data and creates a pulse density modulated (PDM) signal for compensation through long time-constant RC filters. It makes sure that the number of occurrence of symbols, "1"s and "0"s, in the transmitted data stream is equal. The numbers of the two symbols will differ when DC offset is introduced in the signal path. The MSM eliminates the unwanted offset by applying appropriate compensating control signals to IOFFSET and QOFFSET pins.

The down converted base-band analog signal, generated after passing through analog filters, will be sampled at the falling edges of CHIPx8 clock by two 4 bit flash ADCs, the outputs of which are fed to the MSM as the digital receive data.

The receive signal path for FM operation is similar to that for CDMA operation. Differences lie in the characteristics of the I and Q low pass filters and the ADCs. The IF frequency is the same as in CDMA (85.38MHz or 220.38MHz) but the modulation can only extend ±15kHz from the IF center frequency, forming a 30kHz wide channel. The low pass filters for FM operation have a much lower bandwidth than those used in CDMA. The offset of the FM low pass filters is controlled just like the CDMA low-pass filters by the IOFFSET and QOFFSET input pins.

The lower bandwidth of the FM base-band signal gives rise to the use of very low power 8 bit algorithmic type ADCs. The FM I and Q analog base-band signals are sampled and held during the analog to digital (A/D) conversion process. The A/D conversion is initiated with a strobe from the MSM. A serial data stream is output beginning with the most significant bit(MSB) of the result.

Figure 3. Receive Section Block Diagram

### **Transmit Signal Path**

The S1M8653B transmit signal path accepts eight bits of I and Q baseband transmit data from the MSM and outputs modulated IF signal centered at 130.38MHz to the RF transmitter(See Figure 4). The rising edge of the transmit clock latches incoming data into the I DAC while the falling edge latches data into the Q DAC. The MSM compensates I and Q data values to account for their half cycle time difference.

Undesirable frequency components are found in the spectrum at the output of the DACs due to output transition edges and transients, and the transmit clock. To reduce them, each DAC is followed by an anti-aliasing low pass filter with a bandwidth of 630kHz. Unlike the low pass filters in the receive signal path, these do not require off-set controls.

The S1M8653B outputs differential IF signals with CDMA spread spectrum modulation extending  $\pm$  630kHz from the transmit IF center frequency of 130.38MHz. The analog I and Q baseband components from the CDMA low-pass filters are mixed in quadrature with local oscillator(LO) signals at 130.38MHz. The result is summed and output differentially. The 130.38MHz I and Q LO signals are generated from the transmit VCO running at 260.76MHz. The VCO frequency is set by an external varactor-tuned resonant tank circuit, and the feedback is provided by an internal phase-lock loop and external loop filter network. A master-slave divide-by-two circuit generates I and Q signals in precise quadrature for the mixers.

An analog FM modulation signal is constructed from 8-bit digital data supplied by the MSM. Only the Q-channel DAC is used in the S1M8653B in FM mode, all other CDMA circuits are disabled. The DAC output is filtered by a low pass anti-aliasing filter and output as the analog FM modulation signal, FM\_MOD.

A low speed, 8-bit resolution, successive approximation General Purpose(GP) ADC provides DC measurement capability to the telephone. It digitizes DC voltages applied to the ADCIN pin from battery level, temperature, and other low frequency control or monitoring sensors.

The GP ADC is in a power-down state during normal S1M8653B operation. It is activated by a positive-going pulse on ADCENA. When this input is driven high, it powers up, samples and holds the voltage applied to ADCIN, and begins a conversion. The ADC output is available from a serial digital interface. Each of the eight data bits is valid(MSM first) during the rising edge of the ADCCLK output. When the LSB of the conversion has been clocked out, the conversion is complete and the ADC returns to a power-down condition. The ADCCLK and ADCDATA outputs will be low before and after a conversion. Conversions can only be started when the ADC is inactive after a conversion has been completed. A rising edge of ADCENA during a conversion will be ignored. ADCENA must be low and a conversion completed before a new conversion can be started.

The S1M8653B has several modes of operation. The CDMA RXTX or FM RXTX modes are in effect when the telephone is making a call. IDLE mode is in effect when no call is in progress but the telephone receive is active (ready to answer a call). SLEEP mode is a low-power mode in which the telephone can not receive a call but the digital processor and keypad are enabled. In Slotted Paging mode, the MSM toggles itself and the S1M8653B between SLEEP and IDLE modes using a programmable timing interval. This mode allows the telephone to be contacted by the base station without requiring the telephone to be continuously in IDLE mode. Slotted Paging mode consumes much less power than IDLE mode.

The states of three digital inputs, FM, IDLE, SLEEP, define the operating modes of the S1M8653B (see Table 1). These logic signals come directly from the MSM and minimize the power consumed by the S1M8653B by disabling unused circuits.

Figure 4. Transmit Section Block Diagram

### MODES OF OPERATION

|       | Mode   | SLEEP | IDLE | FM |

|-------|--------|-------|------|----|

| Sleep | (CDMA) | 0     | Х    | Х  |

| Idle  | (CDMA) | 1     | 0    | 1  |

| RXTX  | (CDMA) | 1     | 1    | 1  |

| Idle  | (FM)   | 1     | 0    | 0  |

| RXTX  | (FM)   | 1     | 1    | 0  |

### ABSOLUTE MAXIMUM RATINGS

| Characteristic            | Symbol           | Value                 | Unit |

|---------------------------|------------------|-----------------------|------|

| Power supply voltage      | V <sub>CC</sub>  | 5.0                   | V    |

| Voltage applied to inputs | V <sub>A</sub>   | V <sub>DD</sub> + 0.5 | V    |

| Operating temperature     | T <sub>OPR</sub> | -40 to +85            | °C   |

| Storage temperature       | T <sub>STG</sub> | -55 to +125           | °C   |

### **RECOMMENDED OPERATING CONDITIONS**

| Characteristic                | Symbol          | Test Conditions | Min. | Тур | Max. | Units |

|-------------------------------|-----------------|-----------------|------|-----|------|-------|

| Power supply voltage          | V <sub>CC</sub> |                 | 3.0  | -   | 3.6  | V     |

| Ambient operating temperature | Та              |                 | -40  | -   | 85   | °C    |

# ELECTRICAL CHARACTERISTICS (V<sub>CC</sub> = 3.3V, T<sub>a</sub> = 25°C)

| Characteristic               | Symbol           | Test Conditions        | Min.                 | Тур | Max. | Units |

|------------------------------|------------------|------------------------|----------------------|-----|------|-------|

| Power supply current         | I <sub>CC1</sub> | CDMA RXTX mode         | -                    | 35  | 50   | mA    |

| Power supply current         | I <sub>CC2</sub> | CDMA IDLE mode         | -                    | 20  | 30   | mA    |

| Power supply current         | I <sub>CC3</sub> | CDMA SLEEP mode        | -                    | 0.5 | 1.4  | mA    |

| Power supply current         | I <sub>CC4</sub> | FM RXTX mode           | -                    | 25  | -    | mA    |

| Power supply current         | I <sub>CC5</sub> | FM IDLE mode           | -                    | 13  | -    | mA    |

| Power supply rejection ratio | PSRR             |                        | -                    | TBD | -    | dB    |

| Logic high input voltage     | V <sub>IH</sub>  |                        | V <sub>DD</sub> -0.7 | -   | -    | V     |

| Logic low input voltage      | V <sub>IL</sub>  |                        | -                    | -   | 0.3  | V     |

| Logic high output voltage    | V <sub>OH</sub>  | V <sub>DD</sub> = 3.0V | 2.7                  | -   | -    | V     |

| Logic low output voltage     | V <sub>OL</sub>  | V <sub>DD</sub> = 3.6V | -                    | -   | 0.4  | V     |

# ELECTRICAL CHARACTERISTICS (Continued) ( $V_{CC} = 3.3V$ , Ta = 25°C)

| Characteristic                           | Symbol             | Test Conditions                                      | Min. | Тур | Max.  | Units |

|------------------------------------------|--------------------|------------------------------------------------------|------|-----|-------|-------|

| Logic input leakage current              | I <sub>LC</sub>    | $V_{DD} = MAX.$<br>$V_{IN} = GND \text{ to } V_{DD}$ | -    | -   | ± 100 | μΑ    |

| Input capacitance, digital input         | C <sub>ID</sub>    |                                                      | -    | 4   | -     | pF    |

| Digital output load capacitance          | C <sub>LD</sub>    |                                                      | -    | 5   | -     | pF    |

| Digital output load resistance           | R <sub>LD</sub>    |                                                      | 100K | -   | -     | Ω     |

| Input resistance of RX IF input pins     | R <sub>IRXI</sub>  | RXIF to RXIF,<br>differential                        | -    | 500 | -     | Ω     |

| Input capacitance of RX IF input pins    | C <sub>IRXI</sub>  | RXIF and RXIF to ground                              | -    | 4   | -     | pF    |

| Input impedance of offset adjust pins    | Z <sub>IOFF</sub>  | IOFFSET, QOFFSET                                     | 200K | -   | -     | Ω     |

| Load resistance of TX IF output-<br>pins | R <sub>LTXI</sub>  | TXIF to TXIF, differential                           | -    | 500 | -     | Ω     |

| Load capacitance of TX IF<br>output pins | C <sub>LTXI</sub>  | TXIF, TXIF to ground                                 | -    | 4   | -     | pF    |

| Output impedance of TX IF output pins    | Z <sub>OTXI</sub>  | TXIF to TXIF differential                            | -    | 50  | -     | Ω     |

| VCO tuning circuit input<br>impedance    | Z <sub>IVCO</sub>  | RXVCO_T1,<br>RXVCO_T2,<br>TXVCO_T1, TXVCO_T2         | -    | 2K  | -     | Ω     |

| PD_OUT output impedance                  | Z <sub>OPD</sub>   | Within compliance range                              | 1M   | -   | -     | Ω     |

| LOCK output logic low voltage            | V <sub>OLLK</sub>  | $R_{LD} \ge 10\mu$ to $V_{DD}$                       | -    | -   | 0.4   | V     |

| LOCK output leakage current              | I <sub>LLK</sub>   | Vout = V <sub>DD</sub>                               | -    | -   | 1     | μΑ    |

| TCXO input impedance                     | ZITCX              |                                                      | -    | 4K  | -     | Ω     |

| General purpose ADC input impedance      | Z <sub>IGADC</sub> | ADCIN                                                | 20K  | 50K | -     | Ω     |

| General purpose ADC input signal range   | V <sub>SGADC</sub> |                                                      | 0.5  | -   | 2.5   | V     |

| SWITCHING CHARACTERISTICS | $S(V_{CC} = 3.3V, Ta = 25^{\circ}C)$ |

|---------------------------|--------------------------------------|

|---------------------------|--------------------------------------|

| Characteristic                           | Symbol             | Test Conditions                    | Min. | Тур   | Max. | Units                                   |

|------------------------------------------|--------------------|------------------------------------|------|-------|------|-----------------------------------------|

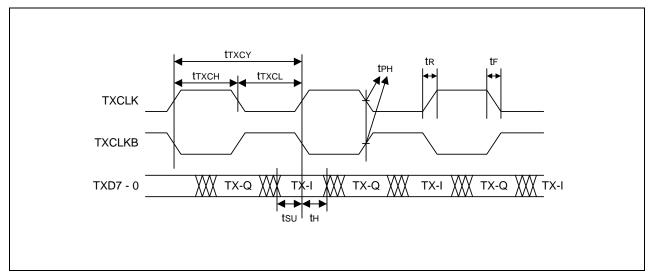

| TXCLK high time                          | t <sub>TXCH</sub>  | CDMA transmit, figure 5            | -    | 50.8  | -    | ns                                      |

| TXCLK low time                           | t <sub>TXCL</sub>  | CDMA transmit, figure 5            | -    | 50.8  | -    | ns                                      |

| TXCLK period                             | t <sub>TXCY</sub>  | CDMA transmit, figure 5            | -    | 101.6 | -    | ns                                      |

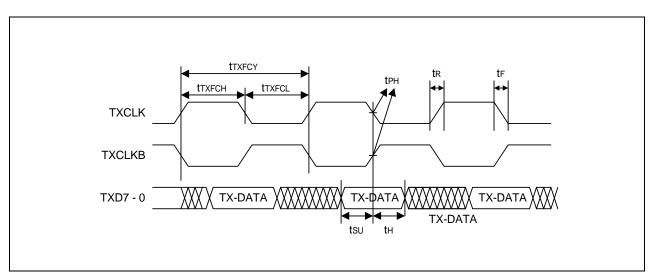

| Data set-up to TXCLK transition          | t <sub>SU</sub>    | CDMA and FM TX, figure 5, 6        | 20   | -     | -    | ns                                      |

| Data hold after TXCLK transition         | t <sub>H</sub>     | CDMA and FM TX, figure 5, 6        | 3    | -     | -    | ns                                      |

| 10% to 90% rise time                     | t <sub>R</sub>     | CDMA and FM TX, figure 5, 6        | -    | -     | 12   | ns                                      |

| 90% to 10% fall time                     | t <sub>F</sub>     | CDMA and FM TX, figure 5, 6        | -    | -     | 12   | ns                                      |

| TXCLK to TXCLK phase delay               | t <sub>PH</sub>    | CDMA and FM TX, figure 5, 6        | -    | -     | 10   | % of<br>t <sub>F</sub> , t <sub>R</sub> |

| TXCLK high time                          | t <sub>TXFCH</sub> | FM transmit, figure 6              | -    | 1.39  | -    | ns                                      |

| TXCLK low time                           | t <sub>TXFCL</sub> | FM transmit, figure 6              | -    | 1.39  | -    | ns                                      |

| TXCLK period                             | t <sub>TXFCY</sub> | FM transmit, figure 6              | -    | 2.78  | -    | ns                                      |

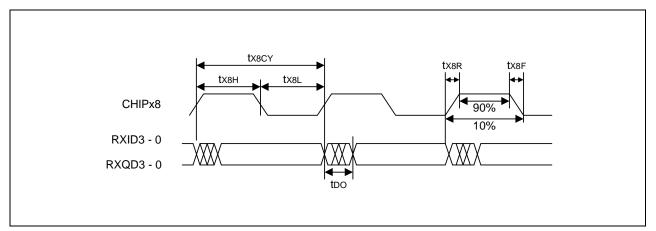

| CHIPx8 high time                         | t <sub>x8H</sub>   | Figure 7, 10                       | -    | 50.8  | -    | ns                                      |

| CHIPx8 low time                          | t <sub>x8L</sub>   | Figure 7, 10                       | -    | 50.8  | -    | ns                                      |

| CHIPx8 period                            | t <sub>x8BCY</sub> | Figure 7, 10                       | -    | 101.6 | -    | ns                                      |

| Digital output delay after CHIPx8 fall   | t <sub>DO</sub>    | Figure 7                           | -    | -     | 20   | ns                                      |

| 10% to 90% rise time                     | t <sub>x8R</sub>   | Figure 7                           | 3    | -     | 12   | ns                                      |

| 90% to 10% fall time                     | t <sub>x8F</sub>   | Figure 7                           | 3    | -     | 12   | ns                                      |

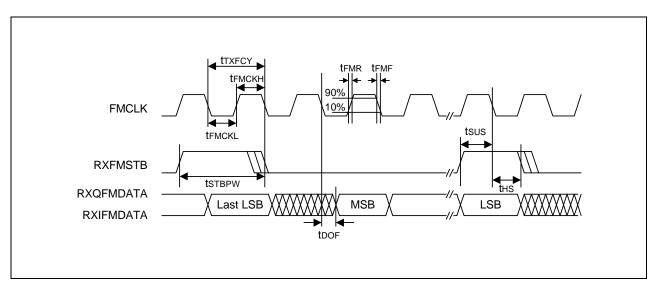

| FMCLK high time                          | t <sub>FMCKH</sub> | FM receive ADC, figure 8           | 1    | 1.39  | -    | μs                                      |

| FMCLK low time                           | t <sub>FMCKL</sub> | FM receive ADC, 1                  |      | 1.39  | -    | μs                                      |

| FMCLK period                             | t <sub>FMCKY</sub> | FM receive ADC, - 2.78<br>figure 8 |      | -     | μs   |                                         |

| RXFMSTB pulse width high                 | t <sub>STBPW</sub> |                                    |      | -     | μs   |                                         |

| Strobe input valid to FMCLK falling edge | t <sub>SUS</sub>   | FM receive ADC, figure 8           | 50   | -     | -    | ns                                      |

# SWITCHING CHARACTERISTICS (Continued) (V<sub>CC</sub> = 3.3V, Ta = 25°C)

| Characteristic                                 | Symbol             | Test Conditions                                         | Min. | Тур   | Max. | Units |

|------------------------------------------------|--------------------|---------------------------------------------------------|------|-------|------|-------|

| Strobe input valid after<br>FMCLK falling edge | t <sub>HS</sub>    | FM receive ADC, figure 8                                | 50   | -     | -    | ns    |

| 10% to 90% rise time                           | t <sub>FMR</sub>   | FM receive ADC, figure 8                                | -    | -     | 12   | ns    |

| 90% to 10% falling time                        | t <sub>FMF</sub>   | FM receive ADC, figure 8                                | -    | -     | 12   | ns    |

| Output delay after FMCLK rising edge           | t <sub>DOF</sub>   | RXQFMDATA,<br>RXIFMDATA,<br>FM receive ADC,<br>figure 8 | -    | -     | 50   | ns    |

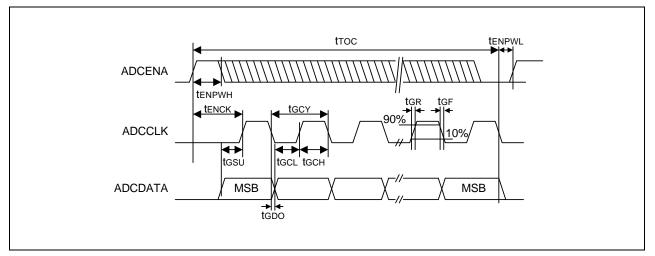

| Enable pulse width high                        | t <sub>ENPWH</sub> | Figure 9                                                | 100  | -     | -    | ns    |

| Enable pulse width low                         | t <sub>ENPWL</sub> | Figure 9                                                | 100  | -     | -    | ns    |

| ADCENA high to ADCCLK                          | t <sub>ENCK</sub>  | Figure 9                                                | -    | 20    | -    | μs    |

| ADCCLK low                                     | t <sub>GCL</sub>   | Figure 9                                                | -    | 1.22  | -    | μs    |

| ADCCLK high                                    | t <sub>GCH</sub>   | Figure 9                                                | -    | 1.22  | -    | μs    |

| ADCCLK period                                  | t <sub>GCY</sub>   | Figure 9                                                | -    | 2.44  | -    | μs    |

| 10% to 90% rise time                           | t <sub>GR</sub>    | Figure 9                                                | -    | -     | 12   | ns    |

| 90% to 10% fall time                           | t <sub>GF</sub>    | Figure 9                                                | -    | -     | 12   | ns    |

| ADCENA high to conversion end                  | t <sub>TOC</sub>   | Figure 9                                                | -    | -     | 40   | μs    |

| ADCDATA delay after<br>ADCCLK falling edge     | t <sub>GDO</sub>   | Figure 9                                                | -    | 20    | -    | ns    |

| ADCDATA valid before<br>ADCCLK rising edge     | t <sub>GSU</sub>   | Figure 9                                                | -    | 1     | -    | μs    |

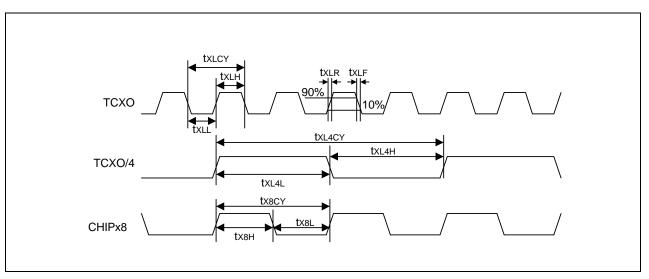

| TCXO low time                                  | t <sub>XLCL</sub>  | Figure 10                                               | -    | 25.4  | -    | ns    |

| TCXO high time                                 | t <sub>XLCH</sub>  | Figure 10                                               | -    | 25.4  | -    | ns    |

| TCXO period                                    | t <sub>XLCY</sub>  | Figure 10                                               | -    | 50.8  | -    | ns    |

| 10% to 90% rise time                           | t <sub>XLR</sub>   | Figure 10                                               | -    | -     | 10   | ns    |

| 90% to 10% fall time                           | t <sub>XLF</sub>   | Figure 10                                               | -    | -     | 10   | ns    |

| TCXO/4 low time                                | t <sub>XL4CL</sub> | Figure 10                                               | -    | 50.8  | -    | ns    |

| TCXO/4 high time                               | t <sub>XL4CF</sub> | Figure 10                                               | -    | 50.8  | -    | ns    |

| TCXO/4 period                                  | t <sub>XL4CY</sub> | Figure 10                                               | -    | 101.6 | -    | ns    |

### TIMING DIAGRAM

Figure 5. CDMA Transmit DAC Timing

Figure 6. FM Transmit DAC Timing

# **TIMING DIAGRAM (Continued)**

Figure 7. CDMA Receive ADC Timing

Figure 8. FM Receive ADC Timing

## **TIMING DIAGRAM (Continued)**

Figure 9. General Purpose ADC Timing

Figure 10. TCXO and CHIPx8 Timing

## SYSTEM PERFORMANCE PARAMETERS

| Characteristic                                            | Symbol | Test Conditions                                        | Min. | Тур | Max. | Units     |

|-----------------------------------------------------------|--------|--------------------------------------------------------|------|-----|------|-----------|

| Rx full-path gain                                         | GRX    | Overall full path gain                                 |      | 38  | -    | dB        |

| Rx input sensitivity                                      | SENRX  | Differential full scale,<br>input level                | -    | 1.8 | -    | mVrms     |

| Rx input dynamic range<br>(Input desense check)           | DYNRX  | Need two-tone signal<br>source<br>Check desense level  | -    | -   | 1    | dB        |

| Maximum available IF frequency                            | MAXIF  | Check ADC output                                       | 240  | -   | -    | MHz       |

| Rx output total harmonic distortion (ADC linearity check) | THDRX  | Check ADC output                                       | -    | -   | 5    | %         |

| Offset Adjust gain                                        | GOFF C | IOFFSET, QOFFSET                                       | 210  | 270 | 330  | %<br>FS/V |

| Signal path gain variation                                | GCSCR  | with part to part or V <sub>DD</sub><br>or Temperature | -2   | -   | 2    | dB        |

| Signal path out-of-band frequency attenuation             | ATTCR  | ≥ 900kHz                                               | 42   | 60  | -    | dB        |

|                                                           |        | ≥ 1.2MHz                                               | 48   | 70  | -    | dB        |

| Overall full-path in-band ripple                          | FTCR   | 1kHz to 630kHz                                         | -1.5 | 0.4 | 1.5  | dB        |

| Rx filter I.Q Gain mismatch                               | MGIQCR | 1kHz to 615kHz                                         | -    | 0.4 | 1.5  | dB        |

| I.Q Phase mismatch                                        | MPIQCR |                                                        |      | -   | 10   | degree    |

CDMA Rx Performance ( $V_{CC} = 3.3V$ , Ta = 25°C)

# FM Rx Performance (V<sub>CC</sub> = 3.3V, Ta = 25°C)

| Characteristic                            | Symbol | Test Conditions                                                                                                                                       | Min. | Тур | Max. | Units |

|-------------------------------------------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|-------|

| FM receive IF input level                 | VIFI   | sinusoidal, differential                                                                                                                              | -    | 2   | -    | mVrms |

| FM receive IF single tone<br>jammer level | VJSF   | ≥ 60kHz,<br>offset differential                                                                                                                       | -    | 300 | -    | mVpp  |

| Input referred noise                      | NIRF   | I or Q, measured across<br>FM bandwidth                                                                                                               | -    | 35  | 45   | μVrms |

| Spurious Content                          | SCRF   | Sum of harmonic and<br>non-harmonics power<br>measured at A/D<br>outputs. Two in-band<br>tones, each one half of<br>the maximum input<br>signal level | -    | -44 | -40  | dBc   |

| Characteristic                            | Symbol | Test Conditions                                                                                                                                                                   | Min. | Тур | Max.  | Units |

|-------------------------------------------|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|-------|-------|

| Spurious content related to jammer        | SCRFJ  | Peak in-band spurious<br>products measured at A/D<br>outputs. Two-tone Jammer,<br>50mVrms<br>@60kHz offset and 6.5mVrms<br>@122.5kHz offset<br>+0.733mVrms signal @1kHz<br>offset | -    | -28 | -18.4 | dBc   |

| Offset Adjust gain                        | GOFFF  | IOFFSET, QOFFSET                                                                                                                                                                  | 210  | 270 | 300   | %FS/V |

| Signal path gain variation                | GCSFR  | With part to part or V <sub>DD</sub> or<br>Temperature                                                                                                                            | -    | -   | ± 1.2 | dB    |

| Signal path out-of-band                   | ATTFR  | ≥ 45kHz                                                                                                                                                                           | 48   | 63  | -     | dB    |

| frequency attenuation                     |        | ≥ 60kHz                                                                                                                                                                           | 60   | 70  | -     | dB    |

| Signal path in-band<br>frequency flatness | FTCR   | 0.1kHz to 12.2kHz                                                                                                                                                                 | -    | 0.6 | 1.0   | dBpp  |

| Group delay deviation                     | DGFC   | 0.1kHz to 12.2kHz                                                                                                                                                                 | -    | -   | 30    | μSpp  |

| Residual sideband suppression             | SRFR   |                                                                                                                                                                                   | 28   | -   | -     | dB    |

FM Rx Performance (V<sub>CC</sub> = 3.3V, Ta = 25°C)

# CDMA Tx Performance (V<sub>CC</sub> = 3.3V, Ta = 25 °C)

| Characteristic                                                      | Symbol | Test Conditions                                                                                     | Min. | Тур    | Max. | Units  |

|---------------------------------------------------------------------|--------|-----------------------------------------------------------------------------------------------------|------|--------|------|--------|

| IF Output amplitude                                                 | VTXCT  | Requires full scale quad-<br>phase signals.                                                         | 250  | 300    | 380  | mVpp   |

| Carrier suppression<br>(Related DC offset)                          | SCCT   | Requires full scale quad-<br>phase signals.                                                         | 20   | 32     |      | dBc    |

| Upper side band suppression<br>(Related I-Q Phase/gain<br>mismatch) | USBS   | Requires full scale quad-<br>phase signals.                                                         | 18   | 25     |      | dBc    |

| Spurious free dynamic range:                                        | SIFCT  | Even harmonics.                                                                                     | 20   |        |      | dBc    |

| IF harmonics                                                        |        | Odd harmonics                                                                                       | 9.5  |        |      | dBc    |

| IF SNR, Noise band 1                                                | SNRCT1 | For all frequencies from $f_{IF}$<br>= ± 0.1MHz to $f_{IF} < \pm$<br>2MHz except at IF<br>harmonics | 104  |        |      | dBc/Hz |

| Output carrier frequency                                            | CODT   |                                                                                                     |      | 130.38 |      | MHz    |

| In-band filter ripple                                               | FTACT  | Measured across the<br>CDMA bandwidth                                                               |      |        | 1.5  | dBpp   |

| Filter total harmonic distortion                                    | THDFLT |                                                                                                     |      |        | 4    | %      |

| Signal path out-of-band                                             | ATTCR  | ≥ 1.2MHz                                                                                            | -4   |        |      | dB     |

| frequency attenuation                                               |        | ≥ 10MHz                                                                                             | -58  |        |      | dB     |

| Characteristic                     | Symbol | Test Conditions                                                                                                                                        | Min. | Тур | Max. | Units  |

|------------------------------------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------|------|-----|------|--------|

| IF Output amplitude                | VTXFT  | Full scale signals.<br>At nominal V <sub>DD</sub> and room<br>temperature                                                                              | -    | 120 | -    | mVpp   |

| IF SNR, Noise band 1               | SNRFT1 | For all frequencies from<br>$f_{IF} = \pm 0.1$ kHz to<br>$f_{IF} < \pm 44$ MHz.<br>Exclude frequencies within<br>$\pm 100$ kHz $f_{IF}$ .              | 110  | -   | -    | dBc/Hz |

| IF SNR, Noise band 2               | SNRFT2 | For all frequencies from $f_{IF} = \pm 44MHz$ .                                                                                                        | TBD  | -   | -    | dBc/Hz |

| Output Amplitude variation         | VOFT   | Part to part, over V <sub>DD</sub> , temperature                                                                                                       | 1.6  | -   | 1.6  | dB     |

| Spurious free dynamic range:       | SIFFT  | Even harmonics.                                                                                                                                        | 20   | 12  |      | dBc    |

| IF harmonics                       |        | Odd harmonics SFDR is the ratio in dB of the power in a 30kHz band around the harmonics of the $f_{IF}$ to the power in a 30kHz band around $f_{IF}$ . | 10   | -   | -    | dBc    |

| FM_MOD output voltage              | VFMOD  | Full scale. RL>10kΩ                                                                                                                                    | 470  | 550 | 630  | mVpp   |

| FM_MOD amplitude variation         |        | Part to part, over V <sub>DD</sub> , temperature and aging.                                                                                            | -    | -   | 15   | %      |

| FM_MOD spurious free dynamic range | SFMOD  | Two tone inputs, to 120kHz                                                                                                                             | 42   | 54  | -    | dB     |

| FM_MOD SNR                         | SNRFM  | Single tone, full scale to 15kHz                                                                                                                       | 87   | 90  | -    | dBc/Hz |

| FM_MOD amplitude flatness          | FTAFT  | DC to 10kHz                                                                                                                                            | -    | 0.4 | 0.6  | dBpp   |

# FM Tx Performance (V<sub>CC</sub> = 3.3V, Ta = 25°C)

| Characteristic                      | Symbol | Test Conditions                                                                     | Min. | Тур    | Max.                     | Units                         |

|-------------------------------------|--------|-------------------------------------------------------------------------------------|------|--------|--------------------------|-------------------------------|

| TCXO reference input<br>frequency   | FTCXO  |                                                                                     | -    | 19.68  | -                        | MHz                           |

| TCXO input amplitude                | VTCXO  | AC coupled                                                                          | 0.5  | -      | 2.0                      | Vpp                           |

| RXVCO_OUT output<br>frequency range | FRVCO  | Depends upon external<br>components                                                 | -    | -      | 500                      | MHz                           |

| RXVCO_OUT phase noise               | NPRVCO | Measured at RXVCO_OUT.<br>The external tank<br>component have a<br>minimum Q of 20. | -    | -100   | -                        | dBc/Hz<br>@100<br>kHz<br>o.s. |

| RXVCO_OUT output voltage swing      | VRVCO  | AC coupled; measured at 170.76MHz.                                                  | -20  | -      | -                        | dBm                           |

| TXVCO output frequency<br>range     | FTVCO  | Depends upon external<br>components                                                 | -    | 260.76 | -                        | MHz                           |

| Lock mode output current            | ILOCK  | Ris=40KOhms                                                                         | 10   | 16     | 20                       | μA                            |

| Acquisition mode output current     | IACQ   | Ris=40KOhms                                                                         | 128  | 160    | 200                      | μΑ                            |

| Maximum IOUT adjustment range       | IMIOUT | Using Ris to vary nominal output current.                                           | -50  | -      | +50                      | %                             |

| PD_OUT compliance voltage           | VCPD   |                                                                                     | 04   | -      | V <sub>DD</sub> -<br>0.4 | V                             |

| Reference spurious                  | SREF   |                                                                                     | -    | -      | 70                       | dBc                           |

| Open loop LO phase noise<br>(VCO/2) | NLO    | CDMA mode, TX IF<br>outputs, full scale DC<br>inputs to I and Q. Tank Q ><br>20     | -    | -100   | -                        | dBc/Hz<br>@100<br>kHz<br>o.s. |

# Receive and Transmit VCO Performance (V<sub>CC</sub> = 3.3V, Ta = 25°C)

# General Purpose ADC Performance ( $V_{CC}$ = 3.3V, Ta = 25°C)

| Characteristic | Symbol | Test Conditions                     | Min. | Тур  | Max. | Units |

|----------------|--------|-------------------------------------|------|------|------|-------|

| Offset voltage | GOFF   | Mid-scale code referred to +1.5Volt | -    | ± 10 | -    | mV    |

| Gain error     | GERR   |                                     | -    | ± 2  | -    | %     |

| DLE            | GDLE   |                                     | -    | 0.5  | 1.25 | LSB   |

| ILE            | GILE   |                                     | -    | 0.5  | 1.25 | LSB   |

### **APPLICATION INFORMATION**

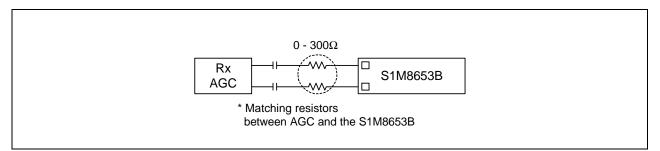

#### **Receive IF Inputs**

The receive IF inputs, RXIF and RXIF, differentially drive an input stage within the S1M8653B, where the input impedance is nominally equal to 500 Ohms. These pins are biased at a DC level of 1.6 Volts and require AC coupling. AC coupling capacitor values should be chosen to maximize the power transfer from receive IF circuitry into the S1M8653B. The internal ground and power rails associated with the receive IF input circuitry are pins 4(GND) and 5 (Vcc) respectively.

Figure 11.

Figure 12.

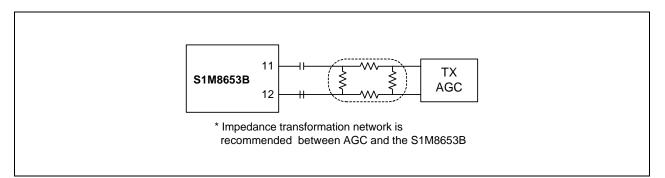

### Transmitting IF Outputs (Use Differential only)

The transmit IF outputs, TXIF and TXIF, are differential emitter-follower outputs with nominal output impedance of 50 ohms. The DC bias on these outputs necessitates AC coupling to the subsequent transmit IF signal path in order to maximize the power transferred from the S1M8653B. The internal ground and power rails associated with the transmit IF output circuitry are pins 13(GND) and 14( $V_{DD}$ ), respectively.

Figure 14.

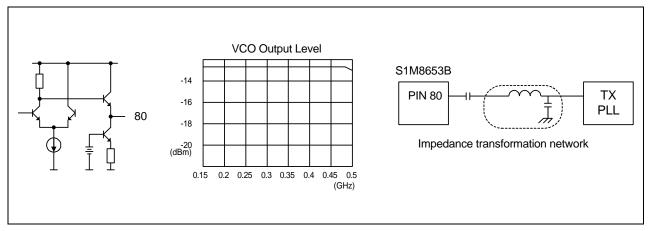

### **Rx VCO Output**

A single-ended receive VCO signal is output from the RXVCO\_OUT(pin 80). The frequency response curve, shown below, indicates that the output signal levels are about -12dBm in cellular band(170.76 MHz) and -12dBm in PCS band(440.76 MHz). The IF input sensitivity of typical PLL for the mobile phone applications range from - 25dBm to -30dBm at 450 MHz, well below the receive VCO output levels of the S1M8653B.

The receive VCO circuitry uses two ground pins; one pin is dedicated to the single-ended output drive stage(pin 1) but the other pin(pin 4) is shared by rest of the circuitry. However, a single power pin (pin 5) serves the whole

Figure 15. Receive VCO Output Drive Stage

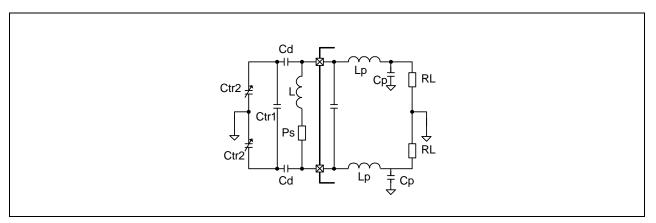

#### **Rx / Tx Tank Circuit**

The frequency of oscillation for any LC resonant tank circuit is determined by, where L and C are the equivalent inductance and capacitance, respectively, of the tank circuit and parasitics of the S1M8653B. The parasitic capacitance between the RXVCO\_T1 and RXVCO\_T2 pins of the S1M8653B has been measured to be about 4 pF. Recommended Q factor of the resonant tank circuit is any value greater than 20.

$$fo = \frac{1}{\frac{2p}{LC}}$$