# **GRAPHICS**

## S1D13712

### **S1D13712 Mobile Graphics Engine**

March 2003

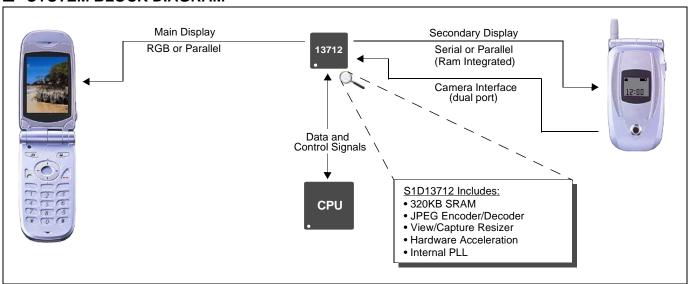

The S1D13712 is an LCD solution designed with support for the digital video revolution in mobile products. The S1D13712 contains an integrated dual port camera interface, hardware JPEG encoder/decoder and can be interfaced to an external MPEG codec. Seamlessly connecting to both direct and indirect CPU interfaces, it provides support for up to two LCD panels. The LCD controller supports all standard TFT panel types and many extended TFT types, eliminating the need for an external timing control IC. The S1D13712 with it's 320K bytes of embedded SRAM and rich feature set provides a low cost, low power, single chip solution to meet the demands of embedded markets requiring Digital Video, such as Mobile Communications devices and Palm-size PCs.

Additionally, products requiring a rotated display can take advantage of the SwivelView™ feature which provides hardware rotation of the display memory transparent to the software application. The S1D13712 also provides support for "Picture-in-Picture Plus" (a variable size window with overlay functions). Higher performance is provided by the Hardware Acceleration Engine which provides 2D BitBLT functions.

The S1D13712 provides impressive support for cellular and other mobile solutions requiring Digital Video support. However, its impartiality to CPU type or operating system makes it an ideal display solution for a wide variety of applications.

#### ■ FEATURES

- Embedded 320K byte SRAM Display Buffer

- Low Operating Voltage

- Direct and Indirect CPU interfaces

- Programmable resolutions and color depths

- Support for 2 panels (LCD2 must be RAM integrated)

- Support for RGB, Serial and Parallel I/F Panels

- Extended TFT interfaces including HR-TFT

- Internal PLL or digital clock input

- Dual port Camera interface w/resize function

- Hardware JPEG encoder/decoder

- YUV to RGB converter

- SwivelView<sup>TM</sup> (90°, 180°, 270° hardware rotation of displayed image)

- (Patent # 5,734,875 Patent # 5,956,049 Patent #6,262,751)

- "Picture-in-Picture Plus"

- 2D Hardware Acceleration Engine

- Software Initiated Power Save Mode

### SYSTEM BLOCK DIAGRAM

X44B-C-001-02 Revision 2.0

## S1D13712

#### DESCRIPTION

### **Integrated Display Buffer**

- 320K bytes of embedded SRAM

- Addressable as a single linear address space

#### **CPU Interface**

- 16-bit Generic Asynchronous CPU interface

- Direct and Indirect addressing

#### **Panel Support**

- Supports up to 2 LCD panels

- LCD1: 9/12/18/24-bit RGB panel LCD2: 8/9-bit Serial Ram Integrated panel

- LCD1: 8/16/18/24-bit Parallel Ram Integrated panel LCD2: 8/9-bit Serial Ram Integrated panel

- LCD1: 8/16/18/24-bit Parallel Ram Integrated panel LCD2: 8/16/18/24-bit Parallel Ram Integrated panel

- TFT, HR-TFT, Casio TFT, ND-TFD, Extended TFT

- Maximum resolution of: up to 320x480 at 16 bpp up to 320x240 at 32 bpp

#### Acceleration

- 2D BitBLT Engine

- SwivelView: 90°, 180°, 270° hardware rotation of displayed image

#### **Display Features**

- 8/16/32 bit-per-pixel (bpp) support

- Picture-in-Picture Plus: displays a variable size window overlaid over the background image

- Overlay Functions

- Pixel Doubling: doubles the effective resolution

- Video Invert: inverts display data

#### **Digital Video**

- Dual port Camera Interface (YUV 4:2:2)

- Hardware JPEG Encoder (YUV 4:2:2, YUV 4:1:1, YUV 4:2:0, YUV 4:4:4)

- Hardware JPEG Decoder (YUV 4:2:2, YUV 4:1:1, YUV 4:2:0)

- YUV Capture (YUV 4:2:2, YUV 4:2:0)

- View and Capture hardware resizer with trimming and reduction functions

- YUV to RGB converter

- Support for external MPEG codec interface

#### Miscellaneous

- Internal PLL or digital clock input

- Software initiated power save mode

- Multiple General Purpose IO pins

- CORE<sub>VDD</sub> 1.8 volts and IO<sub>VDD</sub> 1.8/2.7/3.0 volts

- PFBGA and FCBGA 160-pin packages

#### CONTACT YOUR SALES REPRESENTATIVE FOR THESE COMPREHENSIVE DESIGN TOOLS

Royalty Free source level

S1D13712 Technical Documentation

Seiko Epson Corporation

421-8, Hino, Hino-shi

Tel: 042-587-5812

Fax: 042-587-5564

**Hong Kong**

Tokyo 191-8501, Japan

http://www.epson.co.jp/

Epson Hong Kong Ltd.

20/F., Harbour Centre

Wanchai, Hong Kong

http://www.epson.com.hk/

25 Harbour Road

Tel: 2585-4600

Fax: 2827-4346

Japan

- S1D13712 Evaluation Boards

- **CPU Independent Software** Utilities

**Electronic Devices Marketing Division**

driver code

North America Epson Electronics America, Inc. 150 River Oaks Parkway San Jose, CA 95134, USA Tel: (408) 922-0200 Fax: (408) 922-0238 http://www.eea.epson.com/

Europe

Epson Europe Electronics GmbH Riesstrasse 15 80992 Munich, Germany Tel: 089-14005-0 Fax: 089-14005-110 http://www.epson-electronics.de/

symbian

Epson Taiwan Technology & Trading Ltd. 10F, No. 287 Nanking East Road Sec. 3, Taipei, Taiwan Tel: 02-2717-7360 Fax: 02-2712-9164 http://www.epson.com.tw/

Singapore

Epson Singapore Pte., Ltd. No. 1 Temasek Avenue #36-00 Millenia Tower Singapore, 039192

Copyright © 2002, 2003 Epson Research and Development, Inc. All rights reserved. Information in this document is subject to change without notice. You may download and use this document, but only for your own use in evaluating Seiko Epson/EPSON products. You may not modify the document. Epson Research and Development, Inc. disclaims any representation that the contents of this document are accurate or current. The Programs/Technologies described in this document may contain material protected under U.S. and/or International Patent laws.

EPSON is a registered trademark of Seiko Epson Corporation. All other trademarks are the property of their respective owners