# **FMS9884A Graphics Digitizer** 3x8-Bit, 108/140/175 Ms/s Triple Video A/D Converter with Clamps

## Features

- 3-channels

- 100/140/175 Ms/s conversion rate

- Programmable Clamps

- Adjustable Gain and offset

AIRCHIL

SEMICONDUCTOR

- Internal Reference Voltage

- I<sup>2</sup>C/SMBus compatible Serial Port

- Pin Compatible with AD9884A

## Applications

- Flat panel displays and projectors

- RGB Graphics Processing

## Description

As a fully integrated analog interface, the FMS9884A can digitize RGB graphics with resolutions up to 1600 x 1200/65Hz refresh or 1600 x 1200/85Hz using alternate pixel sampling. ADC sampling clock can be derived from either an external source or incoming horizontal sync signal using the internal PLL. Output data is released through either one port at full rate or both ports, each running at half-rate. Setup and control

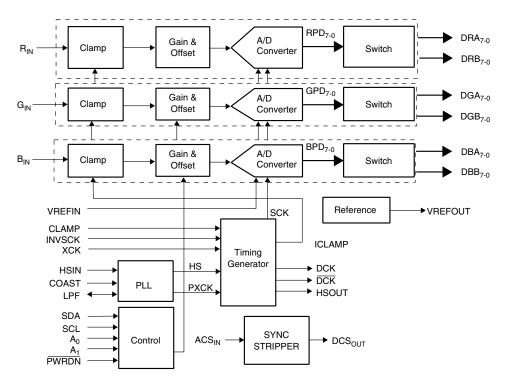

Block Diagram

is via registers, accessible through an SMBus/I<sup>2</sup>C compatible serial port.

Input amplitude range is 500–1000mV with either DC or AC coupling. Lower reference of AC coupled inputs is established with input clamps that are either internally generated or externally provided.

Common to the three channels are clamp pulses, a bandgap reference voltage and clocks derived from a PLL or an external source. Digital data levels are 2.5–3.3 volt CMOS compliant.

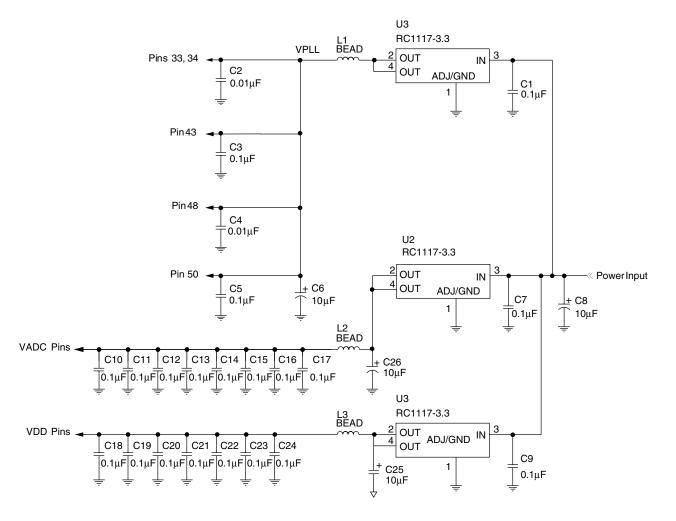

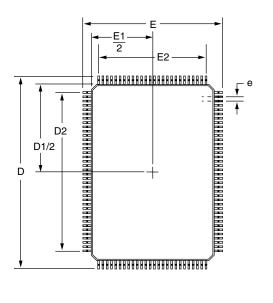

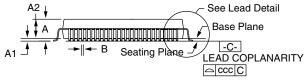

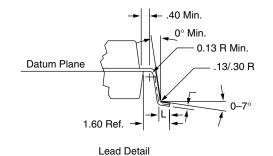

Power can be derived from a single +3.3 Volt power supply. For 175 MHz applications see special  $V_{PLL}$  requirements. Package is a 128-lead MQFP. Performance specifications are guaranteed over 0°C to 70°C range.

| Product Number | Speed    |

|----------------|----------|

| FMS9884AKAC100 | 108 Ms/s |

| FMS9884AKAC140 | 140 Ms/s |

| FMS9884AKAC175 | 175 Ms/s |

## **Architectural Overview**

Three separate digitizer channels are controlled by common timing signals derived from the Timing Generator. A/D clock signals can be derived from either a PLL or an external clock XCK. With the PLL selected, A/D clocks track the incoming horizontal sync signal connected to the HSIN input. Setup is controlled by registers that are accessible through the serial interface.

## **Conversion Channels**

Typical RGB graphics signals,  $R_{IN}$ ,  $G_{IN}$ ,  $B_{IN}$  are ground referenced with 700mV amplitude. If a sync signal is embedded then the usual format is sync on green with the sync tip at ground, the black level elevated to 300mV and peak green at 1000mV.

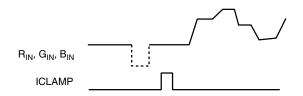

AC coupled video signals must be level shifted to establish the lower level of the conversion range by clamping to the black level of the back porch (see Figure 1). Clamp pulses are derived from internal Timing and Control logic or from the external CLAMP input.

Figure 1. Clamping to the back-porch

### Gain and Offset

Gain and Offset registers serve two functions: adjustment of contrast and brightness by setting RGB values in tandem; matching the gain and offsets between channels, by setting RGB values individually to obtain the same output levels.

A/D conversion range can be matched to the amplitude of the incoming video signal by programming Gain Registers GR, GG and GB, which vary sensitivity (LSB/volt) over a 2:1 range. Incoming video signal amplitudes varying from 0.5 to 1.0 volt can be accommodated.

Input offset voltage of each converter is programmable in 1 LSB steps through the 6-bit OSR, OSG and OSB registers. Range of adjustment is equivalent to -31 to +32 LSB.

### A/D Converter

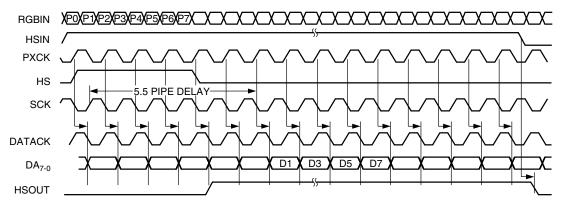

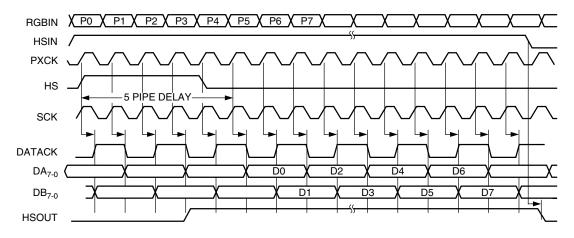

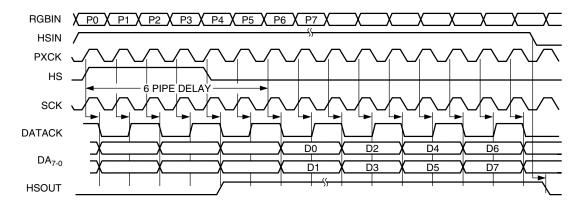

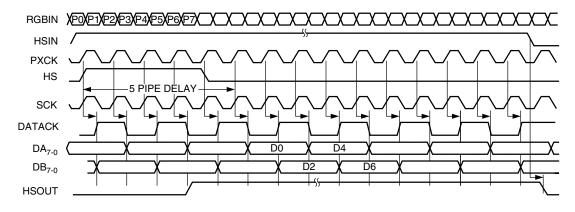

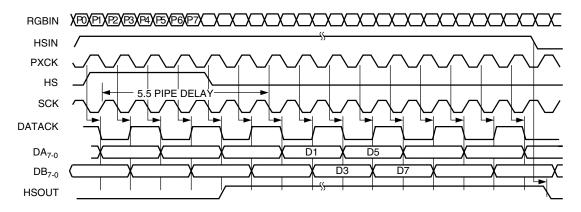

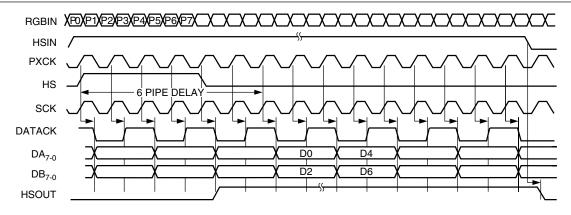

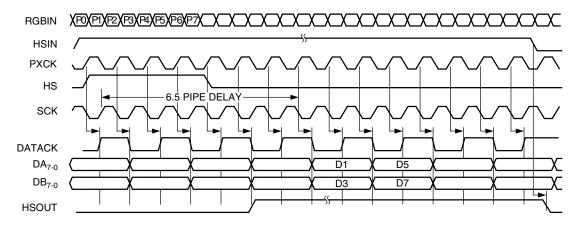

Each A/D converter digitizes the analog input into 8-bit data words. Latency is  $5-6^{1}/_{2}$  clock cycles, depending upon the data out format.

$V_{REFIN}$  is the source of reference voltage for the three A/D converters.  $V_{REFIN}$  can be connected to either the internal bandgap voltage,  $V_{REFOUT}$  or an external voltage.

### **Output Data Configuration**

Output data number format for each channel is binary: 00 corresponds to the lowest input; FF corresponds to the highest input. Data can be released in either of two timing formats:

- 1. Single 8-bit port at pixel rates up to 175Ms/s.

- Dual 8-bit ports, each running at half the conversion rate. Maximum rate is 88Ms/s per port. Data streams may be parallel or interleaved.

### **Timing and Control**

Timing and Control logic encompasses the Timing Generator, PLL and Serial Interface.

### **Timing Generator**

All internal clock and synchronization signals are generated by the Timing Generator. Master Clock source is either the PLL or the external clock input, XCK. Bit XCKSEL selects the Master Clock source. Two clocks are generated.

Sampling clock, SCK is supplied to all three A/D converters. Phase of SCK can be adjusted in 32 11.25 degree phase increments using the 5-bit PHASE register.

DCK is the output data clock. DCK and  $\overline{\text{DCK}}$  are supplied as outputs for synchronizing data transfer from the digitizer outputs.

Horizontal sync applied to the input,  $HS_{IN}$  is propagated by the Timing and Control to the  $HS_{OUT}$  output with a delay that aligns leading and trailing edges with the output data.

#### **Phase Locked Loop**

With a horizontal sync signal connected to the HSIN input pin, the PLL generates a high frequency internal clock signal, PXCK that is fed to the Timing and Control logic. Frequency of PXCK is set by the register programmable PLL divide ratio, PLLN.

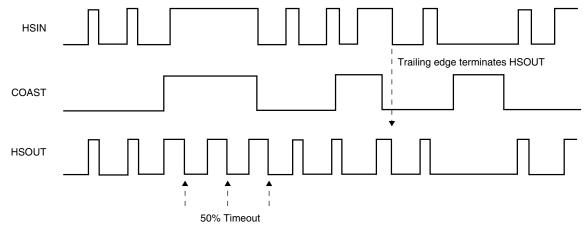

COAST is an input that disables the PLL lock to the horizontal sync input, HSIN. If HSIN is to be disregarded for a period such as the vertical sync interval, COAST allows the VCO frequency to be maintained. Omission of horizontal sync pulses during the vertical interval can cause tearing at the top of a picture, if COAST is not used.

Two pixels per clock mode is set by programming the PLL to half the pixel rate. By toggling the INVCK pin between frames, even and odd pixels can be read on alternate frames.

#### **Serial Interface**

Registers are accessed through an I<sup>2</sup>C/SMBus compatible serial port. Four serial addresses are pin selectable.

GND \_\_\_\_\_ 119

GND 🗖 122

VDDA 124

PWRDN -125

VREFIN 127

VREFOUT

118

120

121

123

126

128

Ο

0 0 4 5 9 7 8 0

HSOUT III

VDDO

GND 🗖

Ħ

64

63

62

61

60

59

58

57

56

55

54

53

52

51

50

49

48

47

46

45

44

43

42

41

40

39

GND

DBB2

DBB3

DBB4

DBB6

DBB7

GND

💷 GND

💷 GND

DDP

GND

IIII LPF

I XCK

HSIN

GND

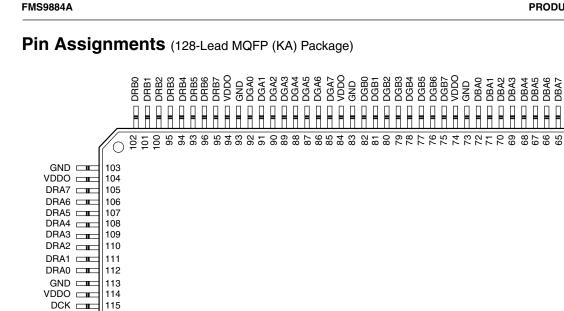

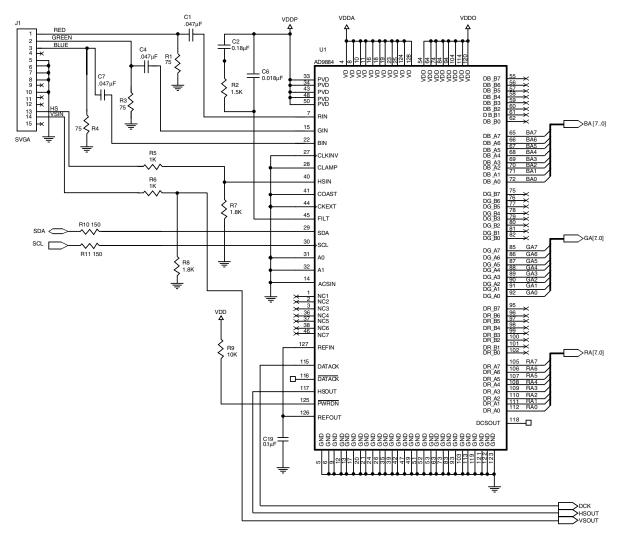

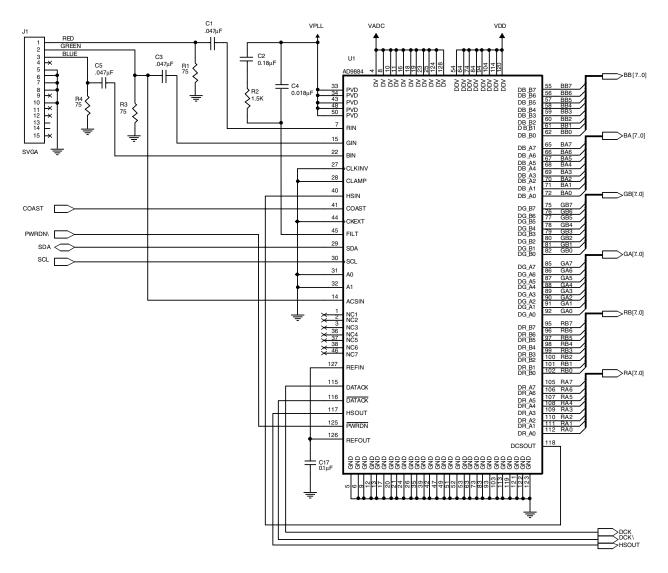

# **Pin Assignments**

| No. | Name              | No. | Name             | No. | Name             | No. | Name                |

|-----|-------------------|-----|------------------|-----|------------------|-----|---------------------|

| 1   | NC                | 33  | V <sub>DDP</sub> | 65  | DBA <sub>7</sub> | 97  | DRB <sub>5</sub>    |

| 2   | NC                | 34  | V <sub>DDP</sub> | 66  | DBA <sub>6</sub> | 98  | DRB <sub>4</sub>    |

| 3   | NC                | 35  | GND              | 67  | DBA <sub>5</sub> | 99  | DRB <sub>3</sub>    |

| 4   | V <sub>DDA</sub>  | 36  | NC               | 68  | DBA <sub>4</sub> | 100 | DRB <sub>2</sub>    |

| 5   | GND               | 37  | NC               | 69  | DBA <sub>3</sub> | 101 | DRB <sub>1</sub>    |

| 6   | GND               | 38  | NC               | 70  | DBA <sub>2</sub> | 102 | DRB <sub>0</sub>    |

| 7   | R <sub>IN</sub>   | 39  | GND              | 71  | DBA <sub>1</sub> | 103 | GND                 |

| 8   | V <sub>DDA</sub>  | 40  | HSIN             | 72  | DBA <sub>0</sub> | 104 | V <sub>DDO</sub>    |

| 9   | GND               | 41  | COAST            | 73  | GND              | 105 | DRA <sub>7</sub>    |

| 10  | V <sub>DDA</sub>  | 42  | GND              | 74  | V <sub>DDO</sub> | 106 | DRA <sub>6</sub>    |

| 11  | V <sub>DDA</sub>  | 43  | V <sub>DDP</sub> | 75  | DGB <sub>7</sub> | 107 | DRA <sub>5</sub>    |

| 12  | GND               | 44  | ХСК              | 76  | DGB <sub>6</sub> | 108 | DRA <sub>4</sub>    |

| 13  | GND               | 45  | LPF              | 77  | DGB <sub>5</sub> | 109 | DRA <sub>3</sub>    |

| 14  | ACS <sub>IN</sub> | 46  | NC               | 78  | DGB <sub>4</sub> | 110 | DRA <sub>2</sub>    |

| 15  | G <sub>IN</sub>   | 47  | GND              | 79  | DGB <sub>3</sub> | 111 | DRA <sub>1</sub>    |

| 16  | V <sub>DDA</sub>  | 48  | V <sub>DDP</sub> | 80  | DGB <sub>2</sub> | 112 | DRA <sub>0</sub>    |

| 17  | GND               | 49  | GND              | 81  | DGB <sub>1</sub> | 113 | GND                 |

| 18  | V <sub>DDA</sub>  | 50  | V <sub>DDP</sub> | 82  | DGB <sub>0</sub> | 114 | V <sub>DDO</sub>    |

| 19  | V <sub>DDA</sub>  | 51  | GND              | 83  | GND              | 115 | DCK                 |

| 20  | GND               | 52  | GND              | 84  | V <sub>DDO</sub> | 116 | DCK                 |

| 21  | GND               | 53  | GND              | 85  | DGA <sub>7</sub> | 117 | HS <sub>OUT</sub>   |

| 22  | B <sub>IN</sub>   | 54  | V <sub>DDO</sub> | 86  | DGA <sub>6</sub> | 118 | DCS <sub>OUT</sub>  |

| 23  | V <sub>DDA</sub>  | 55  | DBB <sub>7</sub> | 87  | DGA <sub>5</sub> | 119 | GND                 |

| 24  | GND               | 56  | DBB <sub>6</sub> | 88  | DGA <sub>4</sub> | 120 | V <sub>DDO</sub>    |

| 25  | V <sub>DDA</sub>  | 57  | DBB <sub>5</sub> | 89  | DGA <sub>3</sub> | 121 | GND                 |

| 26  | GND               | 58  | DBB <sub>4</sub> | 90  | DGA <sub>2</sub> | 122 | GND                 |

| 27  | INVSCK            | 59  | DBB <sub>3</sub> | 91  | DGA <sub>1</sub> | 123 | GND                 |

| 28  | CLAMP             | 60  | DBB <sub>2</sub> | 92  | DGA <sub>0</sub> | 124 | V <sub>DDA</sub>    |

| 29  | SDA               | 61  | DBB <sub>1</sub> | 93  | GND              | 125 | PWRDN               |

| 30  | SCL               | 62  | DBB <sub>0</sub> | 94  | V <sub>DDO</sub> | 126 | V <sub>REFOUT</sub> |

| 31  | A <sub>0</sub>    | 63  | GND              | 95  | DRB <sub>7</sub> | 127 | V <sub>REFIN</sub>  |

| 32  | A <sub>1</sub>    | 64  | V <sub>DDO</sub> | 96  | DRB <sub>6</sub> | 128 | V <sub>DDA</sub>    |

# **Pin Descriptions**

| Pin Name                                            | Pin No.   | Type/Value            | Pin Function Description                                                                                                                                                                                      |

|-----------------------------------------------------|-----------|-----------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Converter Cha                                       | annels    |                       |                                                                                                                                                                                                               |

| R <sub>IN</sub> , G <sub>IN</sub> , B <sub>IN</sub> | 7, 15, 22 | Input                 | Analog Inputs.                                                                                                                                                                                                |

| DRA <sub>7-0</sub>                                  | 105–112   | Output                | <b>Red Channel Port A Data Output.</b> Full rate/half rate, interleaved/<br>parallel data depending upon selected mode.                                                                                       |

| DRB <sub>7-0</sub>                                  | 95–102    | Output                | <b>Red Channel Port B Data Output.</b> Active for dual port mode only with interleaved/parallel outputs. High impedance when inactive.                                                                        |

| DGA <sub>7-0</sub>                                  | 85–92     | Output                | Green Channel Port A Data Output. See red channel port A.                                                                                                                                                     |

| DGB <sub>7-0</sub>                                  | 75–82     | Output                | Green Channel Port B Data Output. See red channel port B.                                                                                                                                                     |

| DBA <sub>7-0</sub>                                  | 65–72     | Output                | Blue Channel Port A Data Output. See red channel port A.                                                                                                                                                      |

| DBB <sub>7-0</sub>                                  | 55–62     | Output                | Blue Channel Port B Data Output. See red channel port B.                                                                                                                                                      |

| Timing Gener                                        | ator      |                       |                                                                                                                                                                                                               |

| CLAMP                                               | 28        | Input                 | External Clamp Input.                                                                                                                                                                                         |

| INVSCK                                              | 27        | Input                 | <b>Invert Sampling Clock.</b> Inverts SCK, the internal clock sampling the analog inputs. Supports Alternate Pixel Sampling mode for capture pixel rates up to 350Ms/s.                                       |

| ХСК                                                 | 44        | Input                 | <b>External Clock input.</b> Enabled if register bit, XCKSEL = H. Replaces PXCK clock generated by PLL. If unused, connect to ground through a $10k\Omega$ resistor.                                          |

| DCK                                                 | 115       | Output                | Output Data Clock. Clock for strobing output data to external logic.                                                                                                                                          |

| DCK                                                 | 116       | Output                | <b>Output Data Clock Inverted.</b> Inverted clock for strobing output data to external logic.                                                                                                                 |

| HSOUT                                               | 117       | Output                | <b>Horizontal Sync Output.</b> Reconstructed HSYNC delayed by FMS9884A latency and synchronized with DCK. Leading edge is synchronized to start of data output. Polarity is always active HIGH.               |

| Phase Locked                                        | d Loop    |                       |                                                                                                                                                                                                               |

| HSIN                                                | 40        | Schmitt               | <b>Horizontal Sync input.</b> Schmitt trigger threshold is 1.5V. A 5V source should be clamped at 3.3V or current limited to prevent overdriving ESD protection diodes.                                       |

| COAST                                               | 41        | Input                 | <b>PLL Coast.</b> Maintain frequency of PLL output clock PXCK, disregarding HSIN. If horizontal sync is missing during the vertical sync interval, PXCK clock frequency can be maintained by asserting COAST. |

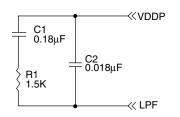

| LPF                                                 | 45        | Passive               | <b>PLL Low Pass Filter.</b> Connect recommended PLL filter to LPF pin. (see Figure 19.)                                                                                                                       |

| Sync Stripper                                       |           |                       |                                                                                                                                                                                                               |

| ACS <sub>IN</sub>                                   | 14        |                       | Analog Composite Sync Input. Input to sync stripper with 150mV threshold.                                                                                                                                     |

| DCS <sub>OUT</sub>                                  | 118       |                       | Digital Composite Sync Output. Output from sync stripper.                                                                                                                                                     |

| Control                                             |           |                       |                                                                                                                                                                                                               |

| SDA                                                 | 29        | <b>Bi-directional</b> | Serial Port Data. Bi-directional data.                                                                                                                                                                        |

| SCL                                                 | 30        | Input                 | Serial Port Clock. Clock input.                                                                                                                                                                               |

| A <sub>0</sub>                                      | 31        | Input                 | Address bit 0. Lower bit of serial port address.                                                                                                                                                              |

| A <sub>1</sub>                                      | 32        | Input                 | Address bit 1. Upper bit of serial port address.                                                                                                                                                              |

| PWRDN                                               | 125       | Input                 | <b>Power Down/Output Control.</b> Powers down the FMS9884A and tri-states the outputs.                                                                                                                        |

# Pin Descriptions (Continued)

| Pin<br>Name         | Pin No.                                                                                                                   | Pin Function Description                                                                                              |

|---------------------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Power ar            | nd Ground                                                                                                                 |                                                                                                                       |

| V <sub>DDA</sub>    | 4, 8, 10, 11, 16, 18, 19, 23,<br>25, 124, 128                                                                             | ADC Supply Voltages. Provide a quiet noise free voltage.                                                              |

| V <sub>DDP</sub>    | 33,34,43,48,50                                                                                                            | <b>PLL Supply Voltage.</b> Most sensitive supply voltage. Provide a very quiet noise free voltage.                    |

| V <sub>DDO</sub>    | 54, 64, 74, 84, 94, 104, 114,<br>120                                                                                      | <b>Digital Output Supply Voltage.</b> Decouple judiciously to avoid propagation of switching noise.                   |

| GND                 | 5, 6, 9,12, 13, 17, 20, 21, 24,<br>26, 35, 39, 42, 47, 49, 51, 52,<br>53, 63, 73, 83, 93, 103, 113,<br>119, 121, 122, 123 | <b>Ground.</b> Returns for all power supplies. Connect ground pins to a solid ground plane.                           |

| V <sub>REFIN</sub>  | 127                                                                                                                       | Voltage Reference Input. Common reference input to RGB converters. Connect to VREFOUT, if internal reference is used. |

| V <sub>REFOUT</sub> | 126                                                                                                                       | Voltage Reference Output. Internal band-gap reference output. Tie to ground through a $0.1\mu F$ capacitor.           |

# Addressable Memory

## **Register Map**

| Name                 | Address | Function                                                                                                                                              | Default (hex) |

|----------------------|---------|-------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| PLLN <sub>11-4</sub> | 00      | <b>PLL divide ratio, MSBs.</b> PLLN + 1 = total number of pixels per horixontal line.                                                                 | 69 (1693)     |

| PLLN <sub>3-0</sub>  | 01      | PLL divide ratio, LSBs. PLLN + 1 = total number of pixelsper horizontal line. PLLN3-0 stored in the four upperregister bits 7-4. $PLLN_{3-0}$ XXXXX   | D0 (1693)     |

| GR <sub>7-0</sub>    | 02      | Gain, red channel. Adjustable from 70 to 140%.                                                                                                        | 80            |

| GG <sub>7-0</sub>    | 02      | Gain, green channel. Adjustable from 70 to 140%.                                                                                                      | 80            |

| GB <sub>7-0</sub>    | 04      | Gain, blue channel. Adjustable from 70 to 140%.                                                                                                       | 80            |

| OSR <sub>5-0</sub>   | 05      | Offset, red channel. $OSR_{5-0}$ stored in the six upper<br>register bits 7-2. Default value is decimal 32. $OSR_{5-0}$ X                             | 80            |

| OSG <sub>5-0</sub>   | 06      | Offset, green channel. $OSG_{5-0}$ stored in the six upper register bits 7-2. Default value is decimal 32.                                            | 80            |

| OSB <sub>5-0</sub>   | 07      | OSG <sub>5-0</sub> X     X       Offset, blue channel.     OSB <sub>5-0</sub> stored in the six upper register bits 7-2. Default value is decimal 32. | 80            |

|                      |         | OSB <sub>5-0</sub> X X                                                                                                                                |               |

| CD <sub>7-0</sub>    | 08      | Clamp delay. Delay in pixels from trailing edge of horizontal sync.                                                                                   | 80            |

| CW <sub>7-0</sub>    | 09      | Clamp width. Width of clamp pulse in pixels.                                                                                                          | 80            |

| CONFIG1              | 0A      | Configuration Register No. 1                                                                                                                          | F4            |

| Name                 | Address | Function                                                                                                                                                            | Default (hex) |

|----------------------|---------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

| PHASE <sub>7-0</sub> | 0B      | Sampling clock phase.PHASE_{4-0} stored in upperregister bits 7-3.PHASE sets the sampling clock phase in11.25° increments.Default value is decimal 16.PHASE_{4-0}XX | 80            |

| PLLCTRL              | 0C      | PLL Control                                                                                                                                                         | 24            |

| CONFIG2              | 0D      | Configuration                                                                                                                                                       | 00            |

|                      | 0E      | Reserved                                                                                                                                                            | 0X            |

|                      | 0F      | Reserved                                                                                                                                                            | 00            |

## **Register Definitions**

## Configuration Register 1 (0A)

| Bit no. | Name     | Туре | Description                                                                                                                                                                                                                                        |

|---------|----------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       |          |      |                                                                                                                                                                                                                                                    |

| 1       | XCKSEL   | R/W  | External Clock Select. Select internal clock source.<br>0: Internal PLL<br>1: XCK input.                                                                                                                                                           |

| 2       | XCLAMPOL | R/W  | <ul><li>External Clamp Polarity. Select clamp polarity.</li><li>0: Active L.</li><li>1: Active H.</li></ul>                                                                                                                                        |

| 3       | XCLAMP   | R/W  | <ul><li>External Clamp Select. Select clamp source.</li><li>0: Internally generated by PLL referenced to HSIN.</li><li>1: External CLAMP input.</li></ul>                                                                                          |

| 4       | COASTPOL | R/W  | <ul><li>Coast Polarity. Select COAST input polarity.</li><li>0: Active L.</li><li>1: Active H.</li></ul>                                                                                                                                           |

| 5       | HSPOL    | R/W  | <ul> <li>HSIN Polarity. Select horizontal sync input polarity. PLL is locked to selected edge:</li> <li>6: Falling edge.</li> <li>1: Rising edge.</li> </ul>                                                                                       |

| 6       | PARALLEL | R/W  | <ul> <li>Output Data Format. Select format of data outputs.</li> <li>0: Interleaved. DCK rising edge strobes port A data. DCK rising edge strobes port B data.</li> <li>1: Parallel. Rising edge of DCK strobes port A and port B data.</li> </ul> |

| 7       | DEMUX    | R/W  | <ul> <li>Output Data Porting. Data released at full rate through one port or through two half-rate ports.</li> <li>0: Single 8-bit port.</li> <li>1: Dual 8-bit ports.</li> </ul>                                                                  |

## PLL Configuration Register (0C)

| Bit no. | Name                 | Туре | Description                                                                                                                                                                                        |

|---------|----------------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1-0     | —                    |      |                                                                                                                                                                                                    |

| 4-2     | IPUMP <sub>2-0</sub> | R/W  | Charge Pump Current. Selects Charge Pump current (μA).<br>(see Table 5. Charge Pump Current Codes)<br>000: 50<br>001: 100<br>010: 150<br>011: 250<br>100: 350<br>101: 500<br>110: 750<br>111: 1500 |

| Bit no. | Name                | Туре | Description                                                                                                    |

|---------|---------------------|------|----------------------------------------------------------------------------------------------------------------|

| 6-5     | FVCO <sub>1-0</sub> | R/W  | VCO Frequency Range. Selects VCO frequency range (MHz).<br>00: 20–90<br>01: 20–90<br>10: 80–120<br>11: 110–175 |

| 7       |                     | R/W  | Reserved.<br>0: Run.<br>1: (reserved).                                                                         |

### **Configuration Register 2 (0D)**

| Bit no. | Name     | Туре | Description                                                                                                                                                                                                                                                                                             |

|---------|----------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       |          | _    | Reserved. Set to 0.                                                                                                                                                                                                                                                                                     |

| 3-1     | REV      | R    | Revision Number. Die revision number.                                                                                                                                                                                                                                                                   |

| 4       | OUTPHASE | R/W  | <ul> <li>Output Data Phase. In the dual port mode, selects either odd (1, 3, 5,) or even (2, 4, 6) samples following the HSYNC leading edge to be emitted from Port 1.</li> <li>O: Even samples to Port A, odd samples to Port B.</li> <li>1: Odd samples to Port A, even samples to Port B.</li> </ul> |

| 7-5     |          | R/W  | Reserved. Set to 00.                                                                                                                                                                                                                                                                                    |

## Test Register (0F)

| Bit no. | Name | Туре | Description                                                                                                                                                                                                                    |

|---------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7-0     |      | R/W  | <b>Reserved.</b> After power-up, initialize this register with the default value 0x00.<br>Register 0F does not respond with an acknowledge during serial bus access.<br>Consequently, ACK remains H instead of being pulled H. |

## **Functional Description**

There are two major sections within the FMS9884A Digitizer:

- 1. Analog-to-digital Converter Channels, one for each channel, RGB and the voltage reference.

- 2. Timing and Control comprising the PLL, Timing Generator, Sync Stripper and Serial Interface.

## A/D Converter Channels

Each of the three RGB channels consists of:

- 1. A clamp to set the lower reference level of an AC coupled input.

- 2. Gain and offset stages to tune the converter to input signal levels.

- 3. An Analog-to-Digital Converter to digitize the analog input.

- 4. A commutating switch for dual port operation.

## **Analog Inputs**

Input signal range is 500 to 1000mV to support conversion of single-ended signals with a typical amplitude of 700mV p-p. With the clamp active, each input accommodates a negative 300mV excursion.

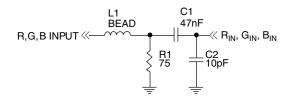

Inputs are optimized for a source resistance of 37.5 to 75 $\Omega$ . To reduce noise sensitivity, the ultra-wide 500MHz input bandwidth may be reduced by adding a small series inductor prior to the 75 $\Omega$  terminating resistor. See Applications Section.

## Clamps

If the incoming signals are not ground referenced, a clamp must be used to set the incoming video range relative to ground. Prior to each A/D converter, each channel includes a clamp that allows a capacitively coupled input to be referenced to the A/D converter bottom reference voltage when the clamp pulse is active. Source of the clamp signal is determined by the XCLAMP bit.

Internal clamp timing is generated by the Timing and Control Block. Position and width of the internal clamp pulse, ICLAMP are programmable through registers CD and CW. External clamp input is selected by register bit XCLAMP and the external clamp polarity selected through register bit XCLAMPOL. To disable the clamp for DC coupled inputs, set XCLAMP = 1 with either of these conditions:

- 1. XCLAMPOL = 0 with input CLAMP = H.

- 2. XCLAMPOL = 1 with CLAMP = L.

Best performance will be achieved with the clamp set active for most of the black signal level interval between the trailing edge of horizontal sync and the start of active video. Insufficient clamping can cause brightness changes at the top of the image and slow recovery from large changes in Average Picture Level (APL). Recommended value of CD is 0x10 to 0x20 for most standard video sources.

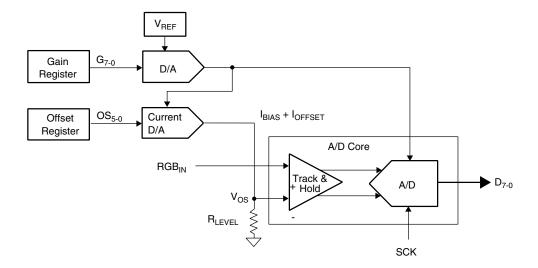

#### Analog-to-Digital Converter

Figure 2 is a block diagram of the ADC core with gain and offset functions.  $G_{7-0}$ ,  $OS_{5-0}$ ,  $RGB_{IN}$  and  $PD_{7-0}$  generically refer to the gain and offset register values, analog input and parallel data output of any RGB channel.

Core of the ADC block is a high speed A/D encoder with differential inputs. Within the A/D converter core are the following elements:

- 1. Differential track and hold.

- 2. Differential analog-to-digital converter.

Setting the gain register value  $G_{7-0}$  (GR<sub>7-0</sub>, GG<sub>7-0</sub>, GB<sub>7-0</sub>), establishes the gain D/A converter voltage which is the A/D reference voltage. Increasing video gain reduces the contrast of the picture since the number of output codes is reduced. Conversion range is defined by the gain setting according to Table 1.

#### Table 1. Gain Calibration

| G <sub>7-0</sub> | Conversion Range (mV) |

|------------------|-----------------------|

| 0                | 500                   |

| 66 <sub>h</sub>  | 700                   |

| FF <sub>h</sub>  | 1000                  |

A/D Converter sensitivity is:

$$S = \frac{255}{500} \cdot \frac{255}{255 + G_{7-0}} LSB/mV$$

Offset is set through the Single-Ended to Differential Amplifier which translates the ground referenced input to a differential voltage centered around A/D common mode bias voltage.

The 6-bit Offset D/A converter injects a current into  $R_{LEVEL}$  with two components:

- 1. I<sub>BIAS</sub> to establish the A/D common mode voltage.

- 2. I<sub>OFFSET</sub> to set the offset from the common mode level.

Voltage offset from the common mode voltage at the inverting input of the Track and Hold is:

$$V_{OS} = (OS_{5-0} - 31) \bullet \frac{255 + G_{7-0}}{255} \bullet \frac{500}{255}$$

D/A converter gain tracks A/D gain with 1 LSB of offset corresponding to 1 LSB of gain. Increasing  $OSR_{5-0}$ ,  $OSG_{5-0}$ , or  $OSB_{5-0}$  reduces brightness in the selected channel. Data output from the A/D converter is:

$$D_{7-0} = S \bullet V_{IN} - (OS_{5-0} - 31)$$

Impact of the offset values  $OSR_{5-0}$ ,  $OSG_{5-0}$ , and  $OSB_{5-0}$  is shown in Table 2.

#### Table 2. Offset Calibration

| OS <sub>5-0</sub> | Output Offset (decimal) |

|-------------------|-------------------------|

| 0                 | +31                     |

| 1F <sub>h</sub>   | 0                       |

| 3F <sub>h</sub>   | -32                     |

#### Sampling Clock PHASE Adjustment

Picture quality is strongly impacted by the  $PHASE_{4-0}$  value. If PHASE is not set correctly, any section of an image consisting of vertical lines may exhibit tearing.

Figure 2. A/D Converter Architecture

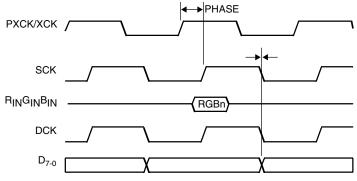

Figure 3. Internal Sampling Clock, SCK Timing

Figure 3 shows how an analog input,  $R_{IN}G_{IN}B_{IN}$  is sampled by the rising edge of SCK after a delay PHASE from the rising edge of either PXCK or XCK. SCK can be delayed up to 32 steps in 11.25° increments by adjusting the register value, PHASE<sub>4-0</sub>.

Output data, DCK and  $\overline{DCK}$  are delayed in tandem with SCK relative to PXCK or XCK. There is a 5-5<sup>1</sup>/<sub>2</sub> clock latency between the data sample RGB<sub>n</sub> and the corresponding data out D<sub>7-0</sub>.

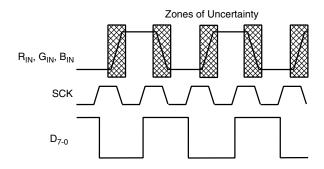

Ideally, incoming pixels would be trapezoidal with fast risetimes and the sampling edge of the A/D clock, SCK would be positioned along the level section of the incoming pixel waveform as shown in Figure 4. There is a narrow zone of uncertainly where sampling during pixel rise time would cause an error in the value of the A/D data output,  $D_{7}$ , 0, which is shown as a value, 0-255.

Figure 4. Ideal Pixel Sampling

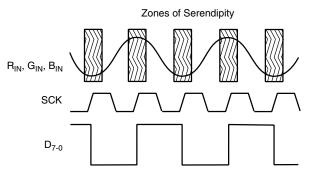

In practice, high-resolution pixels have long rise-times. As shown in Figure 5, there are narrow zones of serendipity when the pixel amplitude is level. Samples are valid in these zones.

Figure 5. Acceptable Pixel Sampling

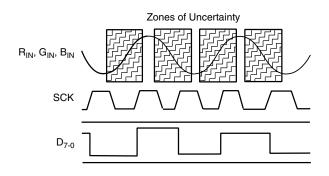

Referring to Figure 6, when the sample clock, SCK has some jitter, if the sampling edge occurs anywhere within the zone of uncertainty where the pixel rise time is steep, there will be amplitude modulation of the digitized data,  $D_{7-0}$ , due to the sampling clock jitter. To avoid corruption of the image, setting the value PHASE<sub>7-0</sub> is critical. PHASE<sub>4-0</sub> should be trimmed to position the sampling edge of SCK within the zone of serendipity.

Figure 6. Improper Pixel Sampling

#### Voltage References

An on-chip voltage reference is generated from a bandgap source.  $V_{REFOUT}$  is the buffered output of this source that can be connected to  $V_{REFIN}$  to supply a voltage reference that is common to the three converter channels.

$V_{REFIN}$ , with a nominal voltage of 1.25V, is the source of the differential reference voltages for each A/D converter. Reference voltages supplied to the differential inputs of the comparators in the A/D converters are derived from  $V_{REFIN}$ .

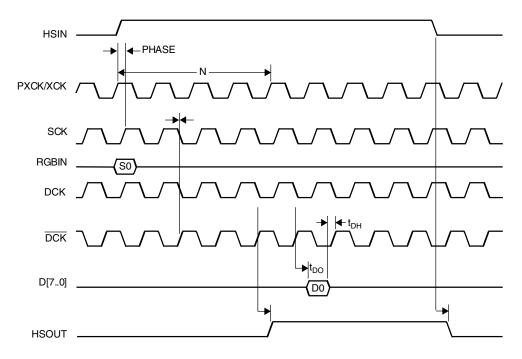

## **Digital Data Outputs**

Input horizontal sync, HSIN and outgoing data, D[7..0] are resynchronized to the delayed sample clock, SCK. Output timing characteristics are defined in Figure 7. Latency of the first pixel, N varies according to the mode:

- 1. Single or dual output port.

- 2. Interleaved or parallel output data.

- 3. 1-pixel or 2-pixel.

Levels are 3.3 volt CMOS with the output supply variable between 2.5 and 3.3 V.  $\overline{PWRDN}$  = L sets the outputs high-impedance.  $\overline{PWRDN}$  = H enables the outputs.

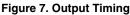

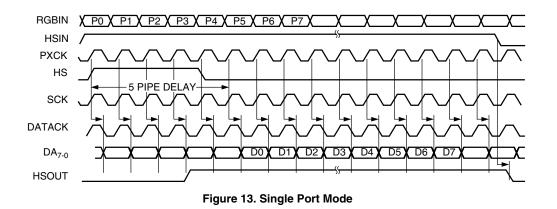

Figures 13 through 21 depict data output timing relative to the sampling clock and inputs for all modes. Timing is referenced to the leading edge of HSIN when the first sample is taken at the rising edge of SCK. Status of register bit OUT-PHASE, determines if even samples are directed the A-port and odd samples are directed to the B-port; or vice versa.

Note the timing of the HSOUT waveform:

- 1. HSOUT is always active HIGH.

- 2. Only the leading edge of HSOUT is active or selected by the HSPOL register bit.

- 3. HSOUT is aligned with DCK.

- 4. Trailing edge is linked to HSIN.

- 5. If HSIN does not terminate before mid-line, HSOUT is forced low. A 50% duty cycle indicates that HSPOL is incorrectly set.

HS is the internal sync pulse generated from HSYNC. SCK is the internal A/D converter sampling clock.

Output data transitions are synchronized with the falling edge of DCK. Output data should be strobed on the rising edge of DCK. A 5 to 6.5 clock cycle delay must be flushed before valid data is available.

## **Alternate Pixel Sampling Mode**

A logic H on the CKINV pin inverts the sampling phase of SCK. In the Alternate Pixel Sampling Mode:

- 1. PLL is run at half rate. SCK, DCK and  $\overline{DCK}$  are half rate.

- 2. CKINV is toggled between frames. (see Figure 18)

| 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е |

|---|---|---|---|---|---|---|---|---|---|---|---|

| 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е |

| 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е |

| 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е |

| 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е |

| 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е |

| 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е |

| 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е |

| 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е |

| 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е |

| 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е | 0 | Е |

|   |   |   |   |   |   |   |   |   |   |   |   |

Figure 8. Odd and Even Pixels in a Frame

On one frame, even pixels are sampled. On the other, odd pixels are sampled.

Alternate Pixel Sampling is similar to interlacing used in broadcast video, except that the columns of pixels are interlaced instead of lines.

| 01E101E101E101E101E101E101E1 |

|------------------------------|

| 01E101E101E101E101E101E101E1 |

Figure 9. Odd Pixels from Frame 1

|                                          | _ |

|------------------------------------------|---|

| 01 E2 01 E2 01 E2 01 E2 01 E2 01 E2 01 E | 2 |

| 01 E2 01 E2 01 E2 01 E2 01 E2 01 E2 01 E | 2 |

| 01 E2 01 E2 01 E2 01 E2 01 E2 01 E2 01 E | 2 |

| 01 E2 01 E2 01 E2 01 E2 01 E2 01 E2 01 E | 2 |

| 01 E201 E201 E201 E201 E201 E201 E201 E2 | 2 |

| 01 E201 E201 E201 E201 E201 E201 E201 E2 | 2 |

| 01 E201 E201 E201 E201 E201 E201 E201 E2 | 2 |

| 01 E201 E201 E201 E201 E201 E201 E201 E2 | 2 |

| 01 E201 E201 E201 E201 E201 E201 E201 E2 | 2 |

| 01 E201 E201 E201 E201 E201 E201 E201 E2 | 2 |

| 01E201E201E201E201E201E201E              | 2 |

Figure 10. Even Pixels from Frame 2

| 01 E2 |

|-------------------------------------------|

| O1 E2 |

| O1 E2 |

| O1 E2 |

| O1 E2 |

| O1 E2 |

| O1 E2 |

| O1 E2 |

| O1 E2 |

| O1 E2 |

| O1 E2 |

| O1 E2 |

| O1 E2 |

|                                           |

Figure 11. Combined Frames 1 and 2 Output.

| O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 | E2 |

|----------------------------------------|----|

| O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 |    |

| O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 | E2 |

| O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 | E2 |

| O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 | E2 |

| O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 |    |

| O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 | E2 |

| O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 | E2 |

| O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 | E2 |

| O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3 | E2 |

| O3 E2 O3 E2 O3 E2 O3 E2 O3 E2 O3       | E2 |

Figure 12. Subsequent Output Combining Frames 2 and 3

Figure 15. Single Port Mode, Alternate Pixel Sampling, (Odd Pixels)

Figure 16. Dual Port Mode, Interleaved Outputs

Figure 18. Dual Port Mode, Interleaved Outputs, Alternate Pixel Sampling, (Even Pixels)

Figure 19. Dual Port Mode, Interleaved Outputs, Alternate Pixel Sampling, (Odd Pixels)

Figure 20. Dual Port Mode, Parallel Outputs, Alternate Pixel Sampling, (Even Pixels)

Figure 21. Dual Port Mode, Parallel Outputs, Alternate Pixel Sampling, (Odd Pixels)

### **Timing and Control**

Timing and Control logic encompasses the PLL, Timing Generator and Sync Stripper.

#### Phase Locked Loop

Two clock types originate in the PLL:

- 1. Data clocks DCK and  $\overline{\text{DCK}}$ .

- 2. Internal sampling clock SCK.

DCK and  $\overline{\text{DCK}}$  are used to strobe data from the FMS9884A to following digital circuits. SCK is the ADC sample clock which has adjustable phase controlled through the PHASE register. DCK and  $\overline{\text{DCK}}$  are phase aligned with SCK.

Reference for the PLL is the horizontal sync input, HSIN with polarity selected by the HSPOL bit.

Frequency of the  $HS_{IN}$  input is multiplied by the value PLLN + 1 derived from the PLLN<sub>11-4</sub> and PLLN<sub>3-0</sub> registers. PLLN + 1 should equal the number of pixels per horizontal line including active and blanked sections. Typically blanking is 20–30% of active pixels. Divide ratios from 2–4095 are supported. SCK, DCK and  $\overline{DCK}$  run at a rate PLLN + 1 times the HS<sub>IN</sub> frequency.

The PLL consists of a phase comparator, charge pump VCO and ÷N counter, with the charge pump connected through the LPF pin to an external filter. These elements must be programmed to match the incoming video source to be captured.

Values of IPUMP and FVCO for Standard VESA timing parameters are shown in Table 3. Timing of many computer video outputs does not comply with VESA recommendations. PLLN should be optimized to avoid vertical noise bars on the displayed image.

Modes marked 2X are 2X-oversampled modes where the number of samples per horizontal line is doubled. To select this mode, the Phase-locked Loop Divide Ratio value must changed from  $PLL_{1x}$  to:

$$PLL_{2x} = 2 \bullet (PLL_{1x} + 1) - 1$$

Values of IPUMP and FVCO are set through the PLL Configuration Register (0x0C). Recommended external filter components are shown in Figure 22. RF Quality  $\pm 10\%$ ceramic capacitors with X7R dielectrc are recommended.

| Standard | Resolution  | Refresh Rate | Horizontal<br>Frequency | Sample Rate  | FVCO <sub>1-0</sub> | IPUMP <sub>2-0</sub> |

|----------|-------------|--------------|-------------------------|--------------|---------------------|----------------------|

| VGA      | 640 X 480   | 60 Hz        | 31.5 kHz                | 25.175 MHz   | 01                  | 100                  |

|          |             | 72 Hz        | 37.7 kHz                | 31.500 MHz   | 01                  | 100                  |

|          |             | 75 Hz        | 37.5 kHz                | 31.500 MHz   | 01                  | 100                  |

|          |             | 85 Hz        | 43.3 kHz                | 36.000 MHz   | 01                  | 100                  |

| 2X       | 640 X 480   | 60 Hz        | 31.5 kHz                | 50 MHz       | 01                  | 100                  |

|          |             | 67 Hz        | 35 kHz                  | 31 MHz       | 01                  | 100                  |

|          |             | 72 Hz        | 37.7 kHz                | 63 MHz       | 01                  | 100                  |

|          |             | 75 Hz        | 37.5 kHz                | 72 MHz       | 01                  | 100                  |

|          | 720 X 400   | 70 Hz        | 31.5 kHz                | 56.6 MHz     | 01                  | 100                  |

| SVGA     | 800 X 600   | 56 Hz        | 35.1 kHz                | 36.000 MHz   | 01                  | 100                  |

|          |             | 60 Hz        | 37.9 kHz                | 40.000 MHz   | 01                  | 100                  |

|          |             | 72 Hz        | 48.1 kHz                | 50.000 MHz   | 01                  | 110                  |

|          |             | 75 Hz        | 46.9 kHz                | 49.500 MHz   | 01                  | 110                  |

|          |             | 85 Hz        | 53.7 kHz                | 56.250 MHz   |                     |                      |

| XGA      | 1024 X 768  | 60 Hz        | 48.4 kHz                | 65.000 MHz   | 01                  | 111                  |

|          |             | 70 Hz        | 56.5 kHz                | 75.000 MHz   | 01                  | 111                  |

|          |             | 75 Hz        | 60.0 kHz                | 78.750 MHz   | 10                  | 111                  |

|          |             | 80 Hz        | 64.0 kHz                | 85.500 MHz   |                     |                      |

|          |             | 85 Hz        | 68.3 kHz                | 94.500 MHz   |                     |                      |

| Mac      | 1024 X 768  | 60 Hz        | 48 kHz                  | 64 MHz       | 01                  | 111                  |

|          |             | 75 Hz        | 60 kHz                  | 80 MHz       | 10                  | 111                  |

|          | 1152 X 870  | 75 Hz        | 69 kHz                  | 100 MHz      | 10                  | 111                  |

| Sun      | 1152 X 900  | 66 Hz        | 62 kHz                  | 93 MHz       | 10                  | 111                  |

| HP       | 1280 X 1024 | 60 Hz        | 63 kHz                  | 108 MHz      | 10                  | 111                  |

| SXGA     | 1280 X 1024 | 60 Hz        | 64.0 kHz                | 108.000 MHz  | 10                  | 111                  |

|          |             | 72 Hz        | 78.1 kHz                | 135.000 MHz  | 11                  | 111                  |

|          |             | 75 Hz        | 80.0 kHz                | 135.000 MHz  | 11                  | 111                  |

|          |             | 85 Hz        | 91.1 kHz                | 157.500 MHz  | 11                  | 111                  |

| UXGA     | 1600 X 1200 | 60 Hz        | 75.0 kHz                | 162.000 MHz  | 11                  | 111                  |

|          |             | 65 Hz        | 81.3 kHz                | 175.500 MHz  | 11                  | 111                  |

|          |             | 70 Hz        | 87.5 kHz                | 189.000 MHz* |                     |                      |

|          |             | 75 Hz        | 93.8 kHz                | 202.500 MHz* |                     |                      |

|          |             | 85 Hz        | 106.3 kHz               | 229.500 MHz* |                     |                      |

| Table 3. Recommended IPUMP and FVCO values for Standard Display Forma |

|-----------------------------------------------------------------------|

|-----------------------------------------------------------------------|

VESA Monitor Timing Standards and Guidelines, September 17, 1998

\* Graphics sampled at  $1/_2$  incoming pixel rate using Alternate Pixel Sampling mode.

Figure 22. Schematic, PLL Filter.

Loop performance is established by setting:

- 1. VCO frequency range through FVCO<sub>1-0</sub>. (see Table 4)

- 2. Charge Pump Current through IPUMP<sub>2-0</sub>. (see Table 5)

- 3. External loop filter component values.

#### **Table 4. VCO Frequency Bands**

| FVCO <sub>2-0</sub> | Frequency Range (MHz) | KVCO (MHz/V) |  |

|---------------------|-----------------------|--------------|--|

| 00                  | 20–90                 | 60           |  |

| 01                  | 20-90                 | 00           |  |

| 10                  | 80–120                | 90           |  |

| 11                  | 110–175               | 100          |  |

#### **Table 5. Charge Pump Current Levels**

| IPUMP <sub>2-0</sub> | Current (µA) |

|----------------------|--------------|

| 000                  | 50           |

| 001                  | 100          |

| 010                  | 150          |

| 011                  | 250          |

| 100                  | 350          |

| 101                  | 500          |

| 110                  | 750          |

| 111                  | 1500         |

Setting SPHASE<sub>4-0</sub> selects the sampling phase of SCK relative to PXCK in 32 steps of 11.25°. Phase of the output data, DCK and  $\overline{\text{DCK}}$  is slaved to the SCK phase.

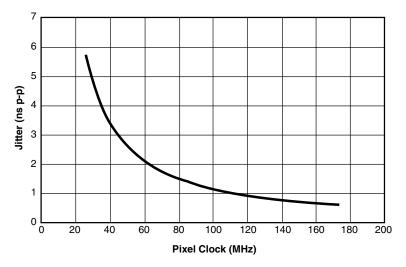

Clock jitter is less than 5% of pixel period in all operating modes. At lower frequencies below 40MHz, the jitter rises but can be reduced by over-sampling at a 2X clock rate. Data should be read out of one port using the dual port mode. See Performance section for jitter specifications and plots.

## COAST

COAST = H disables PLL lock to HSIN, while the VCO frequency is retained. VCO frequency remains stable over several lines without updates from HSIN. COAST can be connected directly to the vertical sync signal or supplied by the graphics controller.

Operation of COAST is depicted in Figure 23. HSOUT polarity is always positive. When COAST = L, HSOUT tracks HSIN (shown with postive polarity in Figure 23):

- 1. HSOUT rising edge tracks HSIN delayed by a few pixels.

- 2. HSOUT falling edge tracks the trailing edge of HSIN with no delay.

When COAST = H, the PLL flywheels, disregarding the incoming HSIN references, while the HSOUT waveform depends upon the state of HSIN.

- 1. If HSIN = H:

- a.) HSOUT rising edge remains locked to the PLL.

- b.) HSOUT trailing edge falls after 50% of the HSOUT period has expired.

- 2. HSIN transitions:

- a.) HSOUT rising edge remains locked to the PLL.

- b.) HSOUT falling edge is terminated by the trailing edge of HSIN.

- 3. If HSIN = L, then HSOUT = L

### **Timing Generator**

Timing and Control logic generates:

- 1. Internal sampling clock, SCK.

- 2. Output data clocks, DCK and  $\overline{\text{DCK}}$ .

- 3. Output horizontal sync, HS<sub>OUT</sub>.

- 4. Internal clamp pulse, ICLAMP.

With HSPOL set correctly, ICLAMP delay follows the trailing edge of horizontal sync in (HSIN). Delay is set by the CD register. Width of ICLAMP is set by the CW register. Range of CD and CW values is 1–255 pixels.

### Sync Stripper

Some video signals include embedded composite sync rather than separate horizontal and vertical sync signals, typically sync on green. Composite sync is extracted from Composite Video at the ACS<sub>IN</sub> pin.

When the ACS<sub>IN</sub> signal falls below a 150mV ground referenced threshold, sync is detected. Composite Sync Output, DCS<sub>OUT</sub> reflects the ACS<sub>IN</sub> sync timing with non-inverted CMOS digital levels.

### **Power Down**

$\overline{\text{PWRDN}}$  = L minimizes FMS9884A power consumption. Data outputs become high impedance. Clocks generation is stopped. Register contents are maintained. Sync stripping and the internal voltage reference function.

### **Serial Interface**

Register access is via a 2-wire I<sup>2</sup>C/SMBus compatible interface. As a slave device, the 7-bit address is selected by the  $A_{1-0}$  pins (see Table 6). Serial port pins SDA and SCL communicate with the host SMBus/I<sup>2</sup>C controller which act as a master. Since the serial control port is design to interface with 3.3V logic, the pins must be protected by series connected  $150\Omega$  resistors if SDA and SCL signals originate from 5V logic. (See Applications Section)

#### Table 6. Serial Interface Address Codes

| A <sub>1-0</sub> | 7-bit Address |

|------------------|---------------|

| 00               | 4C            |

| 01               | 4D            |

| 10               | 4E            |

| 11               | 4F            |

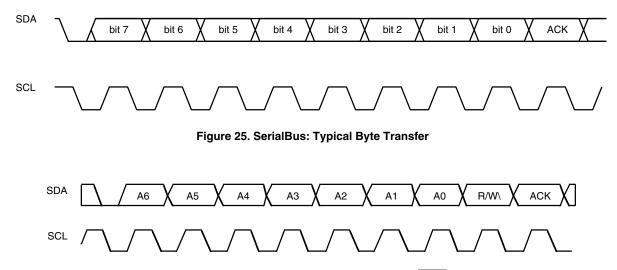

Two signals comprise the bus: clock (SCL) and bi-directional data (SDA). When receiving and transmitting data through the serial interface, the FMS9884A acts as a slave, responding only to commands by the I<sup>2</sup>C/SMBus master.

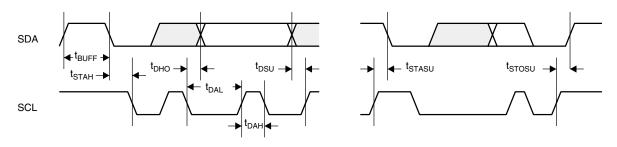

Data received or transmitted on the SDA line must be stable for the duration of the positive-going SCL pulse. Data on SDA may change only when SCL = L. An SDA transition while SCL = H is interpreted as a start or stop signal.

Figure 24. Serial Bus: Read/Write Timing

There are five steps within an  $I^2C/SMBus$  cycle:

- 1. Start signal

- 2. Slave address byte

- 3. Pointer register address byte

- 4. Data byte to read or write

- 5. Stop signal

When the Serial Bus interface is inactive, SCL = H and SDA = H. Communications are initiated by sending a start signal (Figure 24, left waveform) that is a HIGH-to-LOW transition on SDA while SCL is HIGH. A start signal alerts all slaved devices that a data transfer sequence is imminent.

As shown in Figure 26, after a start signal, the first eight bits of data comprise a seven bit slave address followed a single R/W bit (Read = H, Write = L) to set the direction of data transfer: read from; or write to the slave device. If the transmitted slave address matches the address of the FMS9884A which set by the state of the ADD pin, the FMS9884A acknowledges by pulling SDA LOW on the 9th SCL pulse (see Figure 26). If the addresses do not match or the register being accessed is 0x0F, the FMS9884A does not acknowledge.

For each byte of data read or written, the MSB is the first bit of the sequence.

### Data Transfer via Serial Interface

If a slave device, such as the FMS9884A does not acknowledge the master device during a write sequence, SDA remains HIGH so the master can generate a stop signal. During a read sequence, if the master device does not acknowledge by bringing SDA = L, the FMS9884A interprets SDA = H as "end of data." SDA remains HIGH so the master can generate a stop signal (Figure 24, right waveform).

To write data to a specific FMS9884A control register, three bytes are sent:

- 1. Write the slave address byte with bit  $R/\overline{W} = L$ .

- 2. Write the pointer byte.

- 3. Write to the control register indexed by the pointer.

After each byte is written, the pointer auto-increments to allow multiple data byte transfers within one write cycle.

Data is read from the control registers of the FMS9884A in a similar manner, except that two data transfer operations are required:

- 1. Write the slave address byte with bit  $R/\overline{W} = L$ .

- 2. Write the pointer byte.

- 3. Write the slave address byte with bit  $R/\overline{W} = H$

- 4. Read the control register indexed by the pointer.

After each byte is read, the pointer auto-increments to allow multiple data byte transfers within one read cycle.

Preceding each slave write, there must be a start cycle. Following the pointer byte there should be a stop cycle. After the last read, there must be a stop cycle comprising a LOW-to-HIGH transition of SDA while SCL is HIGH. (see Figure 24, right waveform)

A repeated start signal occurs when the master device driving the serial interface generates a start signal without first generating a stop signal to terminate the current communication. This is used to change the mode of communication (read, write) between the slave and master without releasing the serial interface lines.

## Serial Interface Read/Write Examples

Examples below show how serial bus cycles can be linked together for multiple register read and write access cycles. For sequential register accesses, each ACK handshake initiates further SCL clock cycles from the master to transfer the next data byte.

#### Write to one register

- 1. Start signal

- 2. Slave Address byte ( $R/\overline{W}$  bit = LOW)

- 3. Pointer byte

- 4. Data byte to base address

- 5. Stop signal

#### Write to four consecutive registers

- 1. Start signal

- 2. Slave Address byte ( $R/\overline{W}$  bit = LOW)

- 3. Pointer byte

- 4. Data byte to base address

- 5. Data byte to (base address + 1)

- 6. Data byte to (base address + 2)

- 7. Data byte to (base address + 3)

- 8. Stop signal

### Read from one register

- 1. Start signal

- 2. Slave Address byte ( $R/\overline{W}$  bit = LOW)

- 3. Pointer byte (= base address)

- 4. Stop signal (optional)

- 5. Start signal

- 6. Slave Address byte ( $R/\overline{W}$  bit = HIGH)

- 7. Data byte from base address

- 8. Stop signal

### Read from four registers

- 1. Start signal

- 2. Slave Address byte ( $R/\overline{W}$  bit = LOW)

- 3. Pointer byte (= base address)

- 4. Stop signal (optional)

- 5. Start signal

- 6. Slave Address byte ( $R/\overline{W}$  bit = HIGH)

- 7. Data byte from base address

- 8. Data byte from (base address + 1)

- 9. Data byte from (base address + 2)

- 10. Data byte from (base address + 3)

- 11. Stop signal

## **Absolute Maximum Ratings**

(beyond which the device may be damaged)<sup>1</sup>

| Parameter                                                      | Min.  | Тур. | Max.             | Unit     |

|----------------------------------------------------------------|-------|------|------------------|----------|

| Power Supply Voltages                                          |       |      |                  |          |

| V <sub>CC</sub> (Measured to GND)                              | -0.5  |      | 4                | V        |

| Digital Inputs                                                 |       |      |                  |          |

| Applied voltage (Measured to GND) <sup>2</sup>                 | -0.3  |      | V <sub>DDA</sub> | V        |

| Forced current <sup>3, 4</sup>                                 | -5.0  |      | 5.0              | mA       |

| Analog Inputs                                                  |       |      |                  |          |

| Applied Voltage (Measured to GND) <sup>2</sup>                 | -0.5  |      | V <sub>DDA</sub> | V        |

| Forced current <sup>3, 4</sup>                                 | -10.0 |      | 10.0             | mA       |

| Digital Outputs                                                |       |      |                  |          |

| Applied voltage (Measured to GND) <sup>2</sup>                 | -0.5  |      |                  | V        |

| Forced current <sup>3, 4</sup>                                 | -6.0  |      | 6.0              | mA       |

| Forced current <sup>3, 4</sup>                                 | -8.0  |      | 8.0              | mA       |

| Short circuit duration (single output in HIGH state to ground) |       |      | 1                | second   |

| Temperature                                                    |       |      |                  | <b>I</b> |

| Junction                                                       |       |      | 150              | °C       |

| Lead Soldering (10 seconds)                                    |       |      | 300              | °C       |

| Vapor Phase Soldering (1 minute)                               |       |      | 220              | °C       |

| Storage                                                        | -65   |      | 150              | °C       |

| Electrostatic Discharge <sup>5</sup>                           |       |      | ±150             | V        |

Notes:

1. Functional operation under any of these conditions is NOT implied. Performance and reliability are guaranteed only if Operating Conditions are not exceeded.

2. Applied voltage must be current limited to specified range.

3. Forcing voltage must be limited to specified range.

4. Current is specified as conventional current flowing into the device.

5. EIAJ test method.

## **Operating Conditions**

| Parameter        |                                                              |            | Min. | Nom.    | Max. | Units  |

|------------------|--------------------------------------------------------------|------------|------|---------|------|--------|

| V <sub>DDA</sub> | ADC Power Supply Voltage                                     |            | 3.0  | 3.3     | 3.6  | V      |

| V <sub>DDP</sub> | PLL Power Supply Voltage                                     | ≤ 140 Ms/s | 3.0  | 3.3     | 3.6  | V      |

|                  |                                                              | > 140 Ms/s | 3.4  | 3.5     | 3.6  | V      |

| V <sub>DDO</sub> | Output Power Supply Voltage                                  |            | 2.2  | 2.5–3.3 | 3.6  | V      |

| T <sub>A</sub>   | Ambient Temperature, Still Air                               | r          | 0    |         | 70   | °C     |

|                  | A/D analog input range, min.<br>A/D analog input range, max. |            |      |         | 500  | mV p-p |

|                  |                                                              |            | 1000 |         |      | mV p-p |

# **Electrical Characteristics**<sup>1</sup>

| Parameter         |                                              | Conditions                        | Min.                  | Тур. | Max. | Unit   |

|-------------------|----------------------------------------------|-----------------------------------|-----------------------|------|------|--------|

| Power             | Supply Currents                              |                                   |                       |      |      |        |

| I <sub>DDA</sub>  | Supply current, ADC                          | Operating, 25°C                   |                       | 210  | 270  | mA     |

| I <sub>DDD</sub>  | Supply current <sup>2</sup> , Digital Output | Operating, 25°C                   |                       | 30   | 40   | mA     |

| I <sub>DDP</sub>  | Supply current, PLL                          | Operating, 25°C                   |                       | 50   | 65   | mA     |

| PD                | Power dissipation                            | 0 to 70°C                         |                       | 950  | 1300 | mW     |

| I <sub>PD</sub>   | Power-down current                           | 0 to 70°C                         |                       | 15   | 20   | mA     |

| P <sub>DD</sub>   | Powered-down disspation                      | 0 to 70°C                         |                       | 50   | 70   | mW     |

| Digital           | Inputs/Outputs                               |                                   |                       |      |      |        |

| CI                | Input Capacitance                            | 25°C                              |                       | 3    |      | pF     |

| Co                | Output Capacitance                           | 25°C                              |                       | 7    |      | pF     |

| I <sub>IH</sub>   | Input Current, HIGH                          | 0 to 70°C                         | -1                    |      | +1   | μA     |

| IIL               | Input Current, LOW                           | 0 to 70°C                         | -1                    |      | +1   | μA     |

| V <sub>IH</sub>   | Input Voltage, HIGH                          | 0 to 70°C                         | 2.5                   |      |      | V      |

| V <sub>IL</sub>   | Input Voltage, LOW                           | 0 to 70°C                         |                       |      | 0.8  | V      |

| I <sub>OHD</sub>  | Output Current, HIGH, data                   | 0 to 70°C                         |                       | 4    |      | mA     |

| I <sub>OHC</sub>  | Output Current, HIGH, clock                  | 0 to 70°C                         |                       | 8    |      | mA     |

| I <sub>OLD</sub>  | Output Current, LOW, data                    | 0 to 70°C                         |                       | 4    |      | mA     |

| I <sub>OLC</sub>  | Output Current, LOW, clock                   | 0 to 70°C                         |                       | 8    |      | mA     |

| V <sub>OH</sub>   | Output Voltage, HIGH                         | I <sub>OH</sub> = max., 0 to 70°C | V <sub>DDO</sub> -0.1 |      |      | V      |

| V <sub>OL</sub>   | Output Voltage, LOW (V <sub>DD3</sub> )      | I <sub>OL</sub> = max., 0 to 70°C |                       |      | 0.1  | V      |

| Serial I          | Bus I/O                                      |                                   |                       |      |      |        |

| V <sub>SMIH</sub> | Input Voltage, HIGH                          | 0 to 70°C                         | 2.5                   |      |      | V      |

| V <sub>SMIL</sub> | Input Voltage, LOW                           | 0 to 70°C                         |                       |      | 0.8  | V      |

| V <sub>SMOL</sub> | Output Voltage, LOW                          | I <sub>SMOL</sub> = max.          |                       |      | 0.1  | V      |

| I <sub>SMOH</sub> | Output Current, HIGH (Open Drain)            | 0 to 70°C                         | -1                    |      | +1   | μA     |

| I <sub>SMOL</sub> | Output Current, LOW                          | 0 to 70°C                         |                       | 4    |      | mA     |

| Analog            | Inputs                                       | ·                                 | ·                     |      |      |        |

| I <sub>B</sub>    | Input bias current                           | 0 to 70°C                         | -1                    |      | 1    | μA     |

| E <sub>OS</sub>   | Input Offset Voltage <sup>3</sup>            | 0 to 70°C                         |                       | 11   |      | mV     |

|                   | nce Output                                   |                                   |                       |      |      |        |

|                   | Output Voltage                               | 0 to 70°C                         | 1.15                  | 1.25 | 1.35 | V      |

|                   | Temperature Coefficient                      | 0 to 70°C                         |                       | ±50  |      | ppm/°0 |

Notes:

1. Unless otherwise stated, 0 to 70°C

2. DEMUX = 1; DCK,  $\overline{DCK}$  load = 15 pF; data load = 5 pF.

3. For optimum performance, null the input offset by calibrating gain and offset (see Firmware section under Applications Information).

# **Switching Characteristics**

| Parameter          |                               |                | Conditions | Min. | Тур. | Max. | Unit |

|--------------------|-------------------------------|----------------|------------|------|------|------|------|

| Analog-te          | o-Digital Converters          |                |            |      | ļ    |      |      |

|                    | Conversion rate               |                | 0 to 70°C  | 10   |      | 175  | Ms/s |

| t <sub>SKEW</sub>  | Data to clock skew            |                | 0 to 70°C  | -0.5 |      | 2.0  | ns   |

| Timing G           | enerator                      |                |            |      |      |      |      |

|                    | HSIN input frequency          |                | 0 to 70°C  | 15   |      | 110  | kHz  |

|                    | Maximum PLL clock rate        | FMS9884AKAC100 | 0 to 70°C  | 108  |      |      | MHz  |

|                    |                               | FMS9884AKAC140 |            | 140  |      |      |      |

|                    |                               | FMS9884AKAC175 |            | 175  |      |      |      |

|                    | Minimum PLL clock rate        |                | 0 to 70°C  |      |      | 20   | MHz  |

| Serial Bu          | s Interface                   |                | 1          |      |      | - I  |      |

| t <sub>DAL</sub>   | SCL Pulse Width, LOW          |                | 0 to 70°C  | 4.7  |      |      | μs   |

| t <sub>DAH</sub>   | SCL Pulse Width, HIGH         |                | 0 to 70°C  | 4.0  |      |      | μs   |

| t <sub>STAH</sub>  | SDA Start Hold Time           |                | 0 to 70°C  | 4.0  |      |      | μs   |

| t <sub>STASU</sub> | SCL to SDA Setup Time (Start) |                | 0 to 70°C  | 4.7  |      |      | μs   |

| t <sub>STOSU</sub> | SCL to SDA Setup Time (Stop)  |                | 0 to 70°C  | 4.0  |      |      | μs   |

| t <sub>BUFF</sub>  | SDA Stop Hold Time Setup      |                | 0 to 70°C  | 4.7  |      |      | μs   |

| t <sub>DSU</sub>   | SDA to SCL Data Setup Time    |                | 0 to 70°C  | 250  |      |      | ns   |

| t <sub>DHO</sub>   | SDA to SCL Data Hold Time     |                | 0 to 70°C  | 0    |      |      | ns   |

# **System Performance Characteristics**

| Paran           | Parameter                                 |        |           | Min. | Тур. | Max. | Unit             |

|-----------------|-------------------------------------------|--------|-----------|------|------|------|------------------|

| Analo           | og to Digital Converter                   |        |           |      |      |      |                  |

| E <sub>LI</sub> | Integral Linearity Error <sup>1</sup>     |        | 0 to 70°C | -2.5 |      | 2.5  | LSB              |

| E <sub>LD</sub> | Differential Linearity Error <sup>1</sup> |        | 0 to 70°C | -1.0 |      | +1.0 | LSB              |

|                 | Missing Codes                             |        | 0 to 70°C |      |      | 0    |                  |

|                 | Input full scale matching                 |        | 0 to 70°C |      | 2    | 6    | %FS <sup>2</sup> |

|                 | Offset adjustment range                   |        | 0 to 70°C | 22   | 23.5 | 25   | %FS <sup>2</sup> |

|                 | Gain tempco                               |        | 25°C      |      | 280  |      | ppm/°C           |

| B <sub>W</sub>  | Analog bandwidth, full power              |        | 25°C      |      | 500  |      | MHz              |

|                 | Transient response                        |        | 25°C      |      | 2    |      | ns               |

| t <sub>OV</sub> | Over-voltage recovery time                |        | 25°C      |      | 1.5  |      | ns               |

| Phase           | e Locked Loop                             |        | 1         |      |      |      |                  |

| t <sub>PP</sub> | Peak-to-peak PLL Jitter @                 | 25.175 | 25°C      |      | 6.5  |      | ns               |

|                 | MHz                                       | 31.5   |           |      | 4.1  |      |                  |

|                 |                                           | 40     |           |      | 3.3  |      |                  |

|                 |                                           | 49.5   |           |      | 2.3  |      |                  |

|                 |                                           | 78.75  | _         |      | 1.5  |      |                  |

|                 |                                           | 108    |           |      | 1.0  |      |                  |

|                 |                                           | 135    |           |      | 0.8  |      |                  |

|                 |                                           | 162    | 1         |      | 0.7  |      |                  |

|                 |                                           | 175    | ]         |      | 0.8  |      |                  |

## System Performance Characteristics (continued)